4 4 4 00 СП 05

Изобретение относится к автоматике, телемеханике и вьмислительной технике и может быть использовано дл приема и обработки информации, пере- даваемой как в безрегистровых, так и многорегистровых кодах.

Цель изобретения - расширение области применения путем обеспечения приема и обработки информации как

в безрегистровых, так и в многорегистровых кодах с последующим преоб- разбвани ем ее в многорегистровые и безрегистровые коры соответственно.

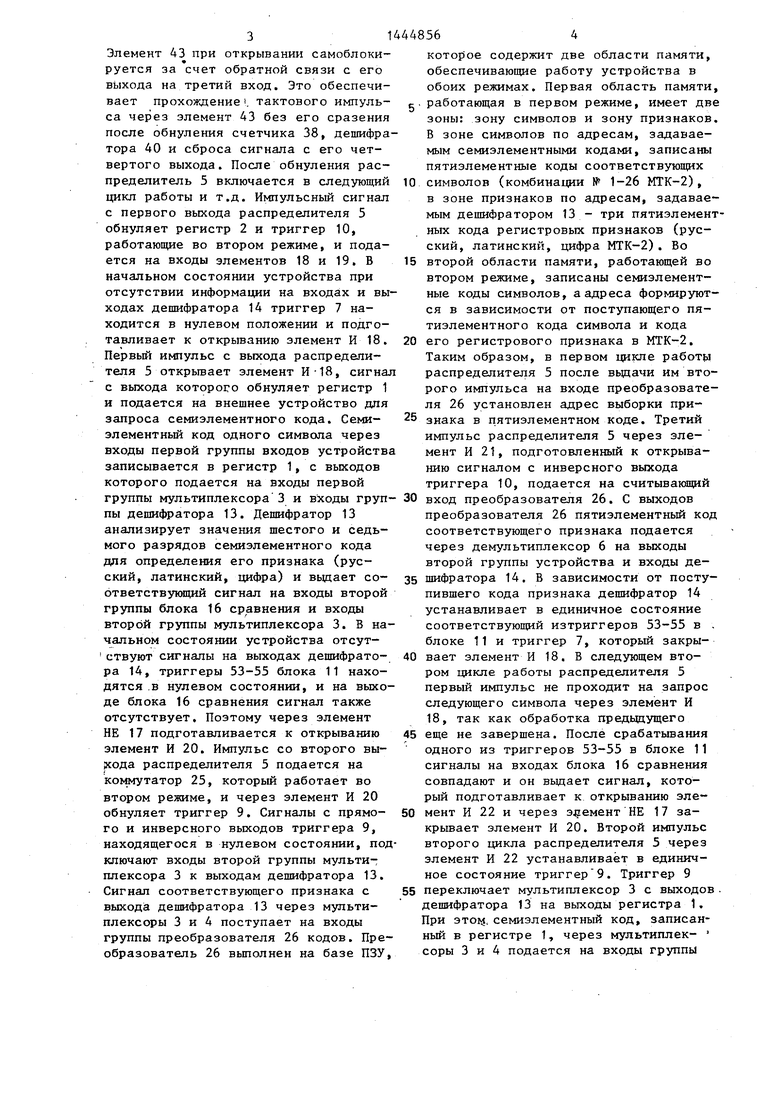

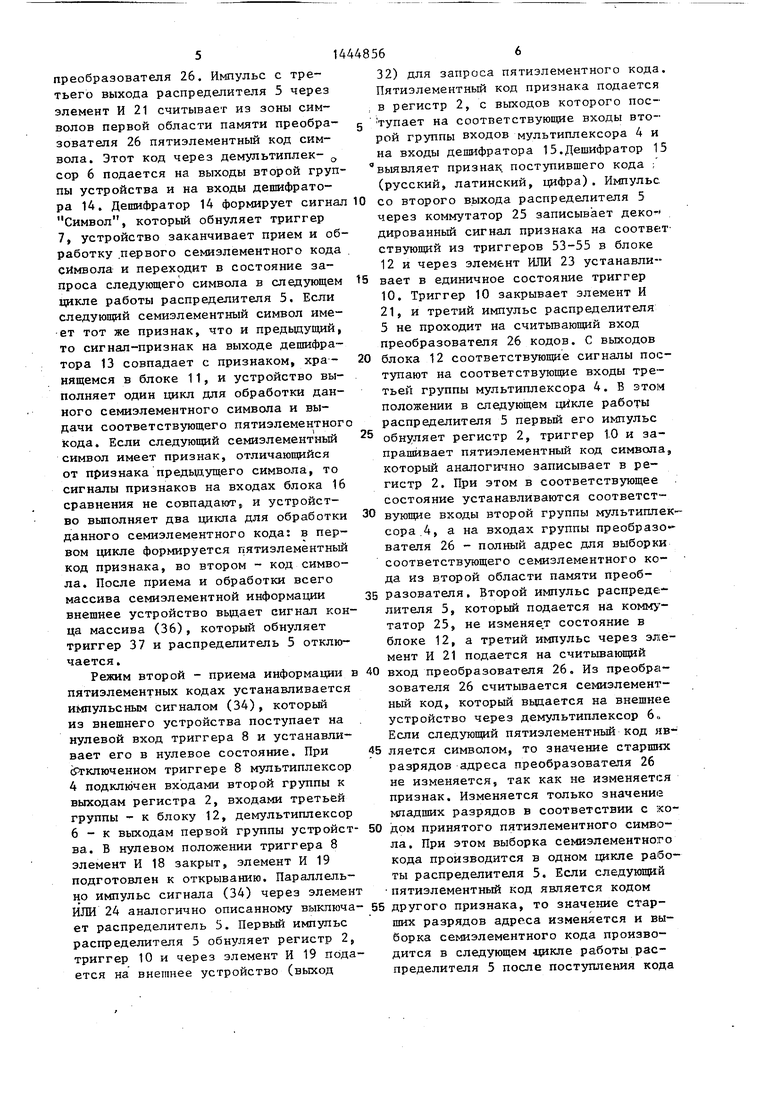

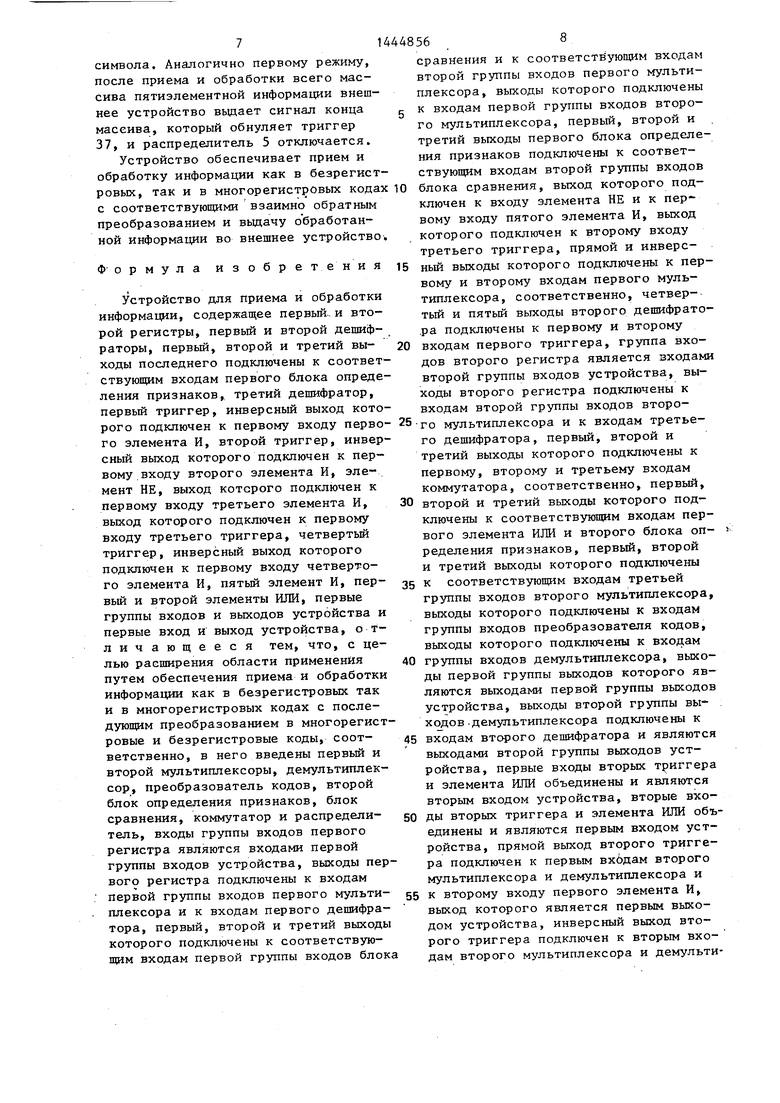

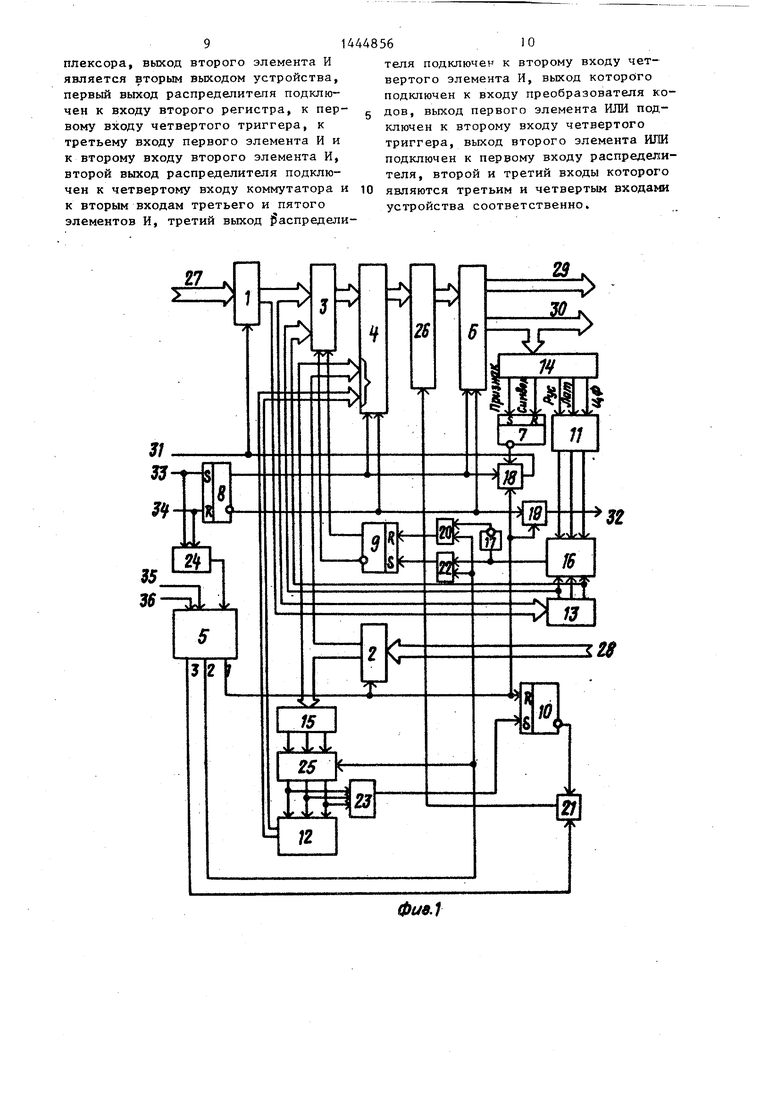

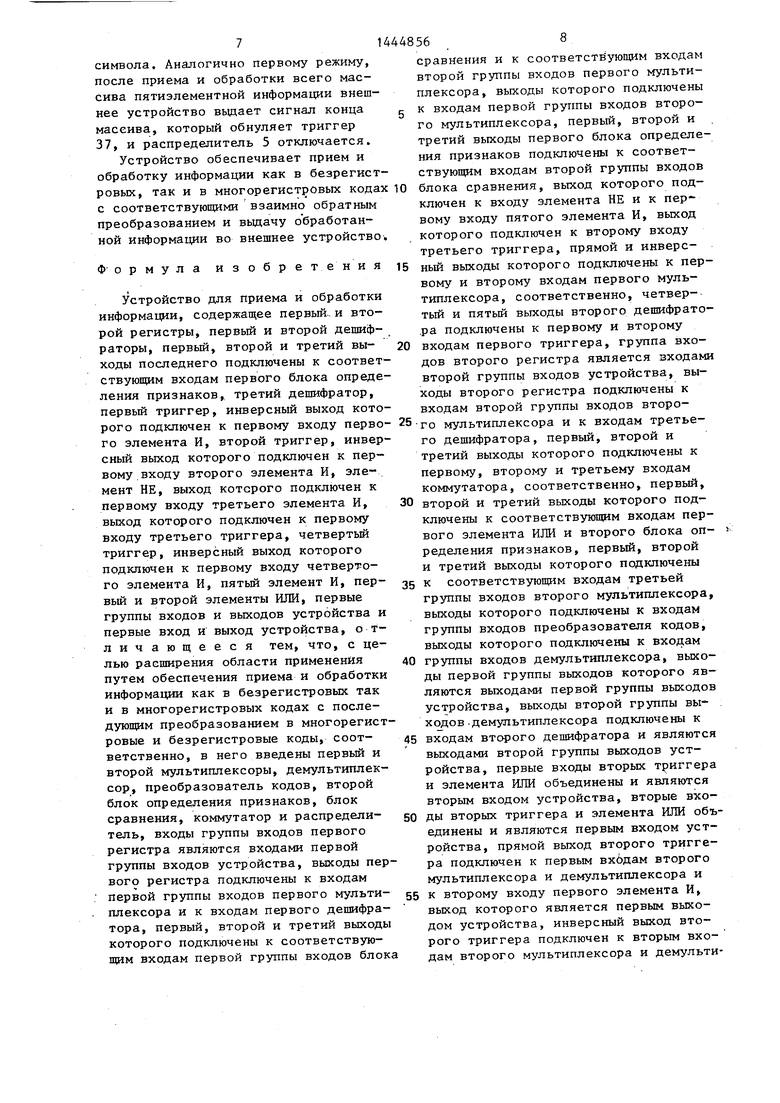

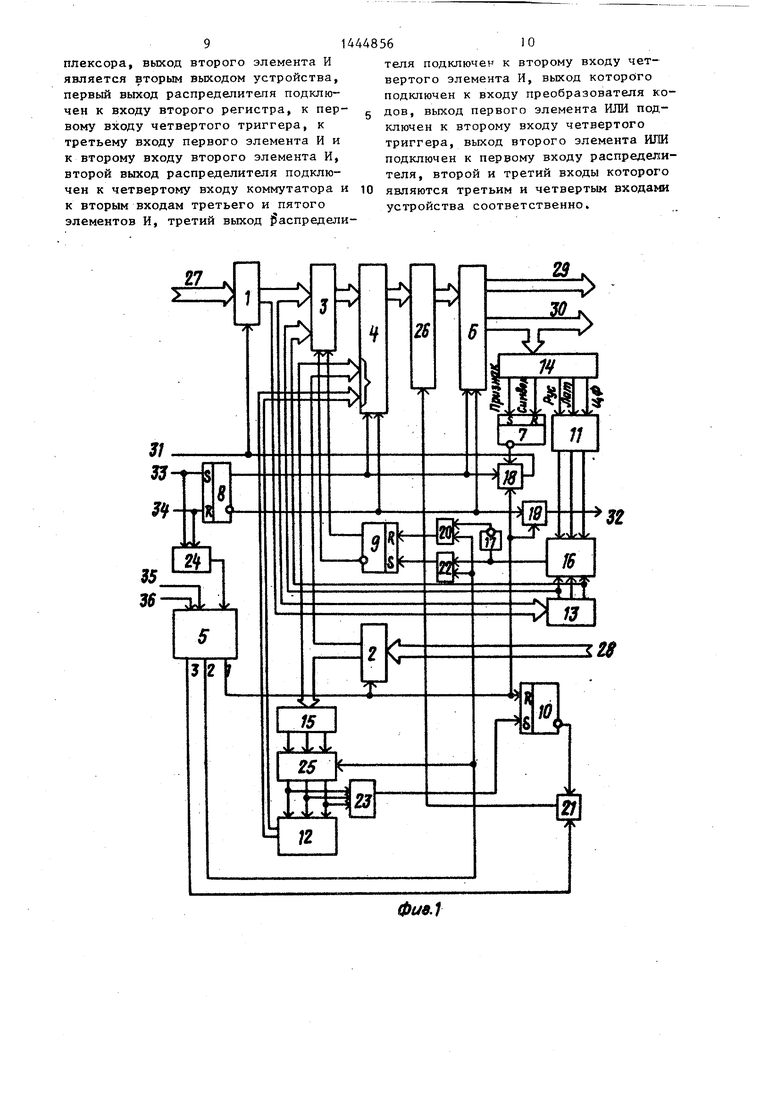

На фиг. 1 представлена функцио- нальная схема предлагаемого устройства} на фиг. 2 - функциональная схема распределителя импульсовJ на фиг. 3 - функциональная схема блока определения признаков} на фиг. 4 и 5 - функциональные схемы первого и второго дешифраторов соответственно.

Устройство содержит первый и второй регистры 1 и 2, первый и второй мультиплексоры 3 и 4, распределитель 5 импульсов, демультиплексор 6, пер- вый-четвертый триггеры 7-10, первьш 11 и второй 12 блоки определения признаков, первый-третий дешифраторы 113-15, блок 16 сравнения, элемент НЕ 17, первый-пятый элементы И 18-22 первый 23 и второй 24 злементы ИЛИ, коммутатор 25 и преобразователь 26 кодов, первую 27 и вторую 28 группы входов устройства, первую 29 и вто- рую 30 группы выходов устройства, первьш 31 и второй 32 выходы устройства, первый-четвертый входы устройства 33-36 соответственно.

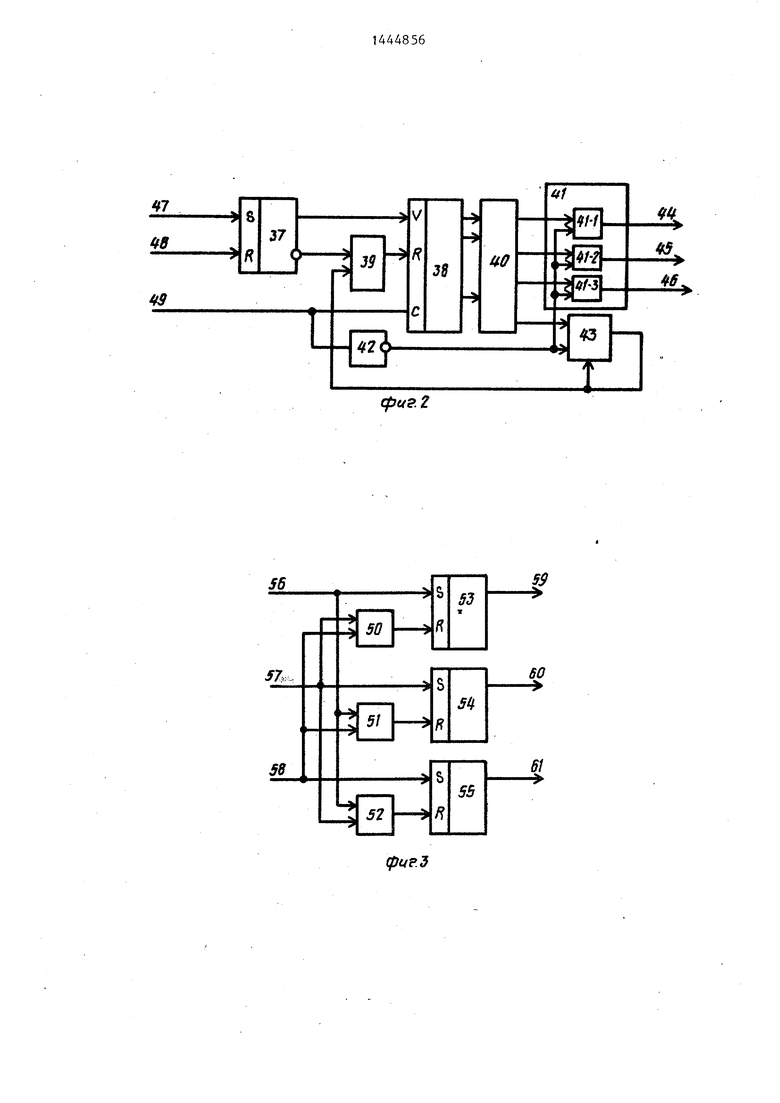

Распределитель 5 импульсов содер- жит триггер 37, счетчик 38, элемент ИЛИ 39, дешифратор 40, коммутатор 41, элемент НЕ 42 и мажоритарный элемент 43, причем 44-46 - первый-трети выходы распределителя импульсов, а 47-49 - первый-третий входы распределителя импульсов.

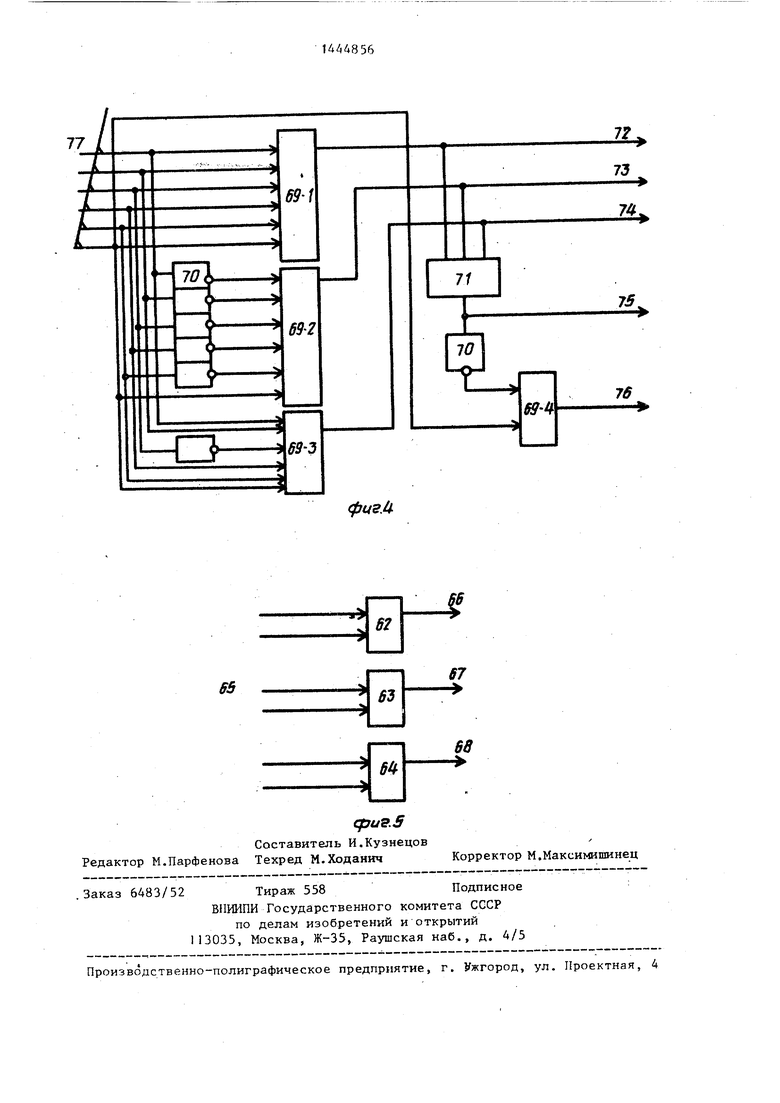

Кпоки 11 и 12 определения признаков содержат первый-третий элементы ИЛИ 50-52, первый-третий триггеры 53 55, причем 56-58 - первый-третий входы блоков, а 59-61 - первый-третий рыходы блоков.

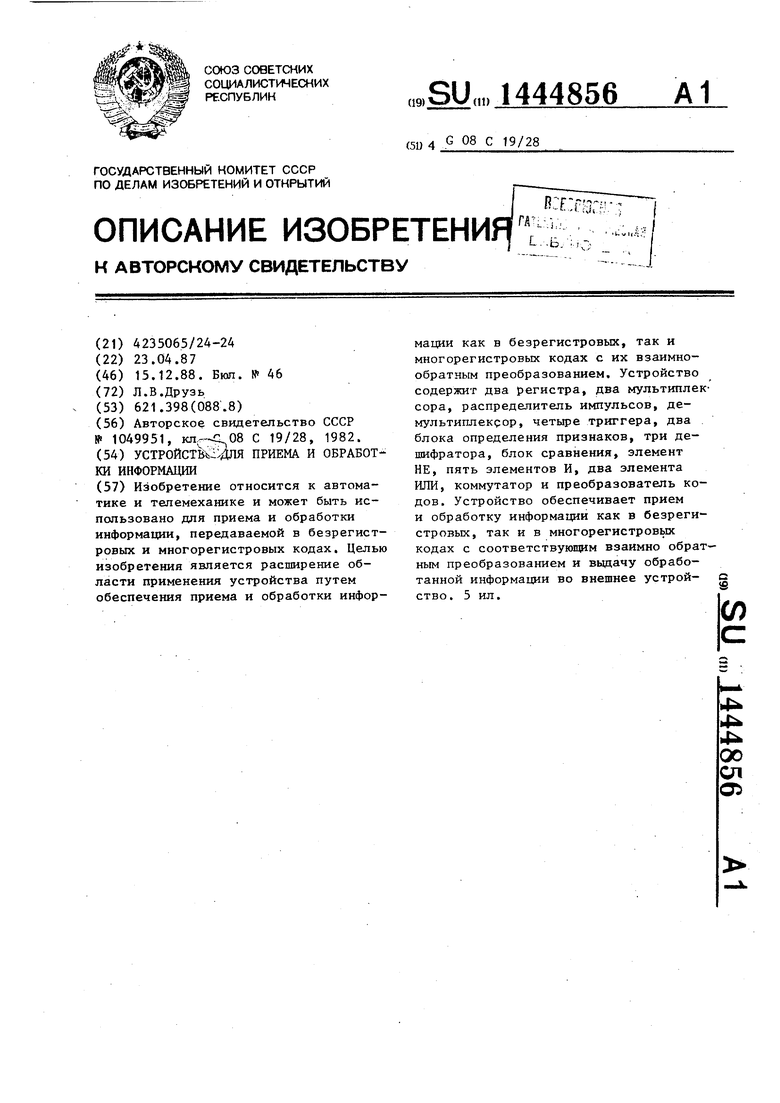

Первьш дешифратор 13 содержит пер вый-третий элементы И 62-64, причем 65 - группа входов первого дешифратора, а 66-68 - первый-третий выходы первого дешифратора.

Второй деамфратор 14 содержит neip- вый-четвертый элементы И ,, группу элементов НЕ 70, элемент ИЛИ 71, причем 72-76 - выходы второго дешифратора, а 71 - группа входов второго дешифратора.

Устройство работает в двух режимах: в режиме приема информации в се- миэлементных безрегистровых кодах, обработка ее и вьщача в пятиэлемент- ных трехрегистровых кодах (МТК-2) и в режиме приема информации в пятиэле- ментных кодах трехрегистровых (МТК-2) обработка ее и вьщача в семиэлемент- ных безрегистровых кодах во внешнее устройство.

Режим приема информации в семи- элементных кодах устанавливается импульсным сигналом 33, который из внешнего устройства поступает на единичный вход триггера 9 и устанавлизза- ет его в единичное состояние. Сигналы с прямого и инверсного выходов триггера 8 управляют состояниями второго мультиплексора 4 и демультиплек- сора 6. При включенном триггере 8 мультиплексор 4 подключен входами первой группы к выходам мультиплексора 3, демультилпексор 6 - выхода1чи второй группы к входам группы дешифратора 14 и к выходам второй группы выходов устройства. Кроме того, триггер 8 подготавливает к открыванию элемент И 18 и закрывает элемент И 19 Параллельно импульс сигнала 33 через элемент ИЛИ 24 устанавливает в единичное состояние триггер 37 распределителя 5, на второй вход которого подается последовательность тактовьк импульсов, триггер 37 снимает через элемент ИЛИ 39 сигнал сброса в нупъ со счетчика 38 и подает на него сигнал разрешения счета тактовых импульсов. Состояния счетчика 38, декодируются дешифратором 40, которы14 формирует в одном цикле работы три управляющих сигнала. Выходы дешифратора 40 стробируются через коммутатор 41 инверсным тактовым импульсом с выхода элемента НЕ 42. Сигнал с четвертого выхода дешифратора 40 обнуляет через мажоритарный элемент 43 и элемент ИЛИ 39 счетчик 38. Мажоритарный элемент 43 открывается при совпадении двух сигналов на его входах - сигнала с четвертого выхода дешифратора 40 и инверсного тактового импульса с вьпсода элемента НЕ 42.

Элемент 43 при открывании самоблокируется за счет обратной связи с его вь1хода на третий вход. Это обеспечивает прохождение . тактового импульса через элемент 43 без его сразения после обнуления счетчика 38, дешифратора 40 и сброса сигнала с его четвертого выхода. После обнуления распределитель 5 включается в следующий цикл работы и т.д. Импульсный сигнал с первого выхода распределителя 5 обнуляет регистр 2 и триггер 10, работающие во втором режиме, и подается на входы элементов 18 и 19. В начальном состоянии устройства при отсутствии информации на входах и выходах дешифратора 14 триггер 7 находится в нулевом положении и подготавливает к открыванию элемент И 18. Первый импульс с выхода распределителя 5 открьгоает элемент И-18, сигнал с выхода которого обнуляет регистр 1 и подается на внешнее устройство для запроса семиэлементного кода. Семи- элементный код одного символа через входы первой группы входов устройства записывается в регистр 1, с выходов которого подается на входы первой

группы мультиплексора 3 и входы груп- 30 вход преобразователя 26. С выходов

которое содержит две области памяти, обеспечивающие работу устройства в обоих режимах. Первая область памяти, работающая в первом режиме, имеет две зоны: зону символов и зону признаков. В зоне символов по адресам, задаваемым семиэлементными кодами, записаны пятиэлементные коды соответствующих

символов (комбинации № 1-26 МТК-2), в зоне признаков по адресам, задаваемым дешифратором 13 - три пятиэлемент- ных кода регистровых признаков (русский, латинский, цифра МТК-2). Во

второй области памяти, работающей во втором режиме, записаны семиэлемент- ные коды символов, а адреса формируются в зависимости от поступающего пя- тиэлементного кода символа и кода

его регистрового признака в МТК-2. Таким образом, в первом цикле работы распределителя 5 после вьщачи им второго импульса на входе преобразователя 26 установлен адрес выборки при-

знака в пятиэлементном коде. Третий импульс распределителя 5 через элемент И 21, подготовленный к открыванию сигналом с инверсного выхода триггера 10, подается на считывающий

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для приема и обработки информации | 1989 |

|

SU1603418A1 |

| Буферное запоминающее устройство | 1986 |

|

SU1374279A1 |

| Устройство для обмена данными | 1985 |

|

SU1297067A1 |

| Устройство для формирования тестов в многорегистровых кодах | 1980 |

|

SU888126A1 |

| Устройство для приема и обработки информации в многорегистровых кодах | 1982 |

|

SU1049951A1 |

| Преобразователь кодов | 1987 |

|

SU1547075A1 |

| Устройство для преобразования кодов | 1983 |

|

SU1131033A1 |

| Устройство для ввода информации | 1983 |

|

SU1157545A1 |

| Трехканальное резервированное устройство для приема и передачи информации | 1990 |

|

SU1758646A1 |

| Многоканальный преобразователь последовательного кода в параллельный | 1990 |

|

SU1751859A1 |

Изобретение относится к автоматике и телемеханике и может быть использовано для приема и обработки информации, передаваемой в безрегистровых и многорегистровых кодах. Целью изобретения является расширение области применения устройства путем обеспечения приема и обработки информации как в безрегистровых, так и многорегистровых кодах с их взаимно- обратным преобразованием. Устройство содержит два регистра, два мультиплексора, распределитель импульсов, де- мультиплекрор, четыре триггера, два блока определения признаков, три дешифратора, блок сравнения, элемент НЕ, пять элементов И, два элемента ИЛИ, коммутатор и преобразователь кодов. Устройство обеспечивает прием и обработку информации как в безрегистровых, так и в многорегистровьк кодах с соответствующим взаимно обратным преобразованием и выдачу обработанной информации во внешнее устройство. 5 ил. (Л

пы дешифратора 13. Дешифратор 13 анализирует значения шестого и седьмого разрядов семиэлементного кода для определения его признака (русский, латинский, цифра) и вьщает соответствующий сигнал на входы второй группы блока 16 сравнения и входы второй группы мультиплексора 3. В начальном состоянии устройства отсут- ствуют сигналы на выходах дешифратора 14, триггеры 53-55 блока 11 находятся .в нулевом состоянии, и на выходе блока 16 сравнения сигнал также отсутствует. Поэтому через элемент НЕ 17 подготавливается к открыванию элемент И 20. Импульс со второго вы- рсода распределителя 5 подается на коммутатор 25, который работает во втором режиме, и через элемент И 20 обнуляет триггер 9. Сигналы с прямого и инверсного выходов триггера 9, находящегося в нулевом состоянии, подключают входы второй группы мультиплексора 3 к выходам дешифратора 13. Сигнал соответствующего признака с выхода дешифратора 13 через мультиплексоры 3 и 4 поступает на входы группы преобразователя 26 кодов. Преобразователь 26 выполнен на базе ПЗУ,

преобразователя 26 пятиэлементньй код соответствующего признака подается через демультиплексор 6 на выходы второй группы устройства и входы де-

шифратора 14. В зависимости от поступившего кода признака дешифратор 14 устанавливает в единичное состояние соответствующий изтриггеров 53-55 в . блоке 11 и триггер 7, который закрывает элемент И 18. В следующем втором цикле работы распределителя 5 первый импульс не проходит на запрос следующего символа через элемент И 18, так как обработка предьщущего

еще не завершена. После срабатывания одного из триггеров 53-55 в блоке 11 сигналы на входах блока 16 сравнения совпадают и он выдает сигнал, который подготавливает к открыванию элемент И 22 к через эдемент НЕ 17 закрывает элемент И 20. Второй импульс второго цикла распределителя 5 через элемент И 22 устанавливает в единичное состояние триггер 9. Триггер 9

переключает мультиплексор 3 с выходов . ешифратора 13 на выходы регистра 1. ри sTOfti. семиэлементный код, записаный в регистре 1, через мультиплек- оры 3 и 4 подается на входы группы

14448566

32) для запроса пятиэлементного кода. Пятиэлементный код признака подается в регистр 2, с выходов которого пос- тупает на соответствующие входы второй группы входов мультиплексора 4 и на входы дешифратора 15.Дешифратор 15 выявляет признак, поступившего кода ; (русский, латинский, цифра). Импульс ра 14. Дешифратор 14 формирует сигнал 10 со второго выхода распределителя 5 Символ, который обнуляет триггер через коммутатор 25 записывает

преобразователя 26. Импульс с третьего выхода распределителя 5 через элемент И 21 считывает из зоны символов первой области памяти преобразователя 26 Пятиэлементный код символа. Этот код через демультиплек- сор 6 подается на выходы второй группы устройства и на входы дешифрато7, устройство заканчивает прием и обработку .первого семиэлементного кода Символа и переходит в состояние запроса следующего символа в следующем цикле работы распределителя 5, Если следующий семиэлементный символ имеет тот же признак, что и предьиущий, то сигнал-признак на выходе дешифратора 13 совпадает с признаком, хранящемся в блоке 11, и устройство выполняет один цикл для обработки данного семиэлементного символа и выдачи соответствующего пятиэлементного кода. Если следующий семиэлементный символ имеет признак, отличающийся от признака предьщущего символа, то сигналы признаков на входах блока 16 сравнения не совпадают, и устройство вьшолняет два цикла для обработки 30 вующие входы второй группы мультиплекданного семиэлементного кода: в первом цикле формируется Пятиэлементный код признака, во втором - код символа. После приема и обработки всего массива семиэлементной информации внешнее устройство вьщает сигнал конца массива (36), который обнуляет триггер 37 и распределитель 5 отключается .

Режим второй - приема информации в 40 вход преобразователя 26, Из npeo6pctпятиэлементных кодах устанавливается импульсным сигналом (34), который из внешнего устройства поступает на нулевой вход триггера 8 и устанавливает его в нулевое состояние. При (Ргключенном триггере 8 мультиплексор 4 подключен входами второй группы к выходам регистра 2, входами третьей группы - к блоку 12, демультиплексор

зователя 26 считывается семиэлемент- ный код, который выдается на внешнее устройство через демультиплексор 6,. Если следуюш 1й Пятиэлементный код яв 45 ляется символом, то значение старших разрядов адреса преобразователя 26 не изменяется, так как не изменяется признак. Изменяется только значение младших разрядов в соответствии с ;ко- 6 - к выходам первой группы устройст- 50 дом принятого пятиэлементного симво- ва. В нулевом положении триггера 8 ла. При этом выборка семиэлементного элемент И 18 закрыт, элемент И 19 кода производится в одном цикле рабо- подготовлен к открыванию. Параллель- ты распределителя 5. Если следующий но импульс сигнала (34) через элемент Пятиэлементный код является кодом ИЛИ 24 аналогично описанному выключа- 55 другого признака, то значение стар- ет распределитель 5. Первый импульс ших разрядов адреса изменяется и вы- распределителя 5 обнуляет регистр 2, борка семиэлементного кода произво- триггер 10 и через элемент И 19 пода- дится в следующем цикле работы рас- ется на внешнее устройство (выход пределителя 5 после поступления кода

дированный сигнал признака на соответствующий из триггеров 53-55 в блоке 12 и через элемент ИЛИ 23 устанавливает в единичное состояние триггер 10. Триггер 10 закрывает элемент И 21, и третий импульс распределителя 5 не проходит на считьгоающий вход преобразователя 26 кодов. С выходов блока 12 соответствующие сигналы поступают на соответствующие входы третьей группы мультиплексора 4. В этом положении в следующем цикле работы распределителя 5 первый его импульс обнуляет регистр 2, триггер 1.0 и запрашивает Пятиэлементный код символа, который аналогично записывает в регистр 2, При этом в соответствующее состояние устанавливаются соответстсора.4, а на входах группы преобразо вателя 26 - полный адрес для выборки соответствующего семизлементного кода из второй области памяти преоб- 35 разователя. Второй импульс распределителя 5, который подается на коммутатор 25, не изменяе.т состояние в блоке 12, а третий импульс через элемент И 21 подается на считывающий

символа. Аналогично первому режиму, после приема и обработки всего массива пятиэлементной информации внешнее устройство выдает сигнал конца массива, который обнуляет триггер 37, и распределитель 5 отключается. Устройство обеспечивает прием и обработку информации как в безрегистровых, так и в многорегистровых кодах с соответствующими взаимно обратным преобразованием и вьщачу обработанной информации во внешнее устройство.

Формула изобретения

Устройство для приема и обработки информации, содержащее первый.и второй регистры, первый и второй дешифраторы, первый, второй и третий вы- 20 ходы последнего подключены к соответ ствующим входам первого блока определения признаков, третий дешифратор, первый триггер, инверсный выход которого подключен к первому входу перво- 25.ro мультиплексора и к входам третьего элемента И, второй триггер, инвер- го дешифратора, первый, второй и

сравнения и к соответстйующим входам второй группы входов первого мультиплексора, выходы которого подключены к входам первой группы входов второго мультиплексора, первый, второй и третий выходы первого блока определе ния признаков подключены к соответствующим входам второй группы входов блока сравнения, выход которого подключен к входу элемента НЕ и к первому входу пятого элемента И, выход которого подключен к второму входу третьего триггера, прямой и инверсный выходы которого подключены к пер вому и второму входам первого мультиплексора, соответственно, четвертый и пятый выходы второго дешифрато ра подключены к первому и второму входам первого триггера, группа входов второго регистра является входам второй группы входов устройства, выходы второго регистра подключены к входам второй группы входов второсный выход которого подключен к первому, входу второго элемента И, эле-. мент НЕ, выход которого подключен к первому входу третьего элемента И, вькод которого подключен к первому входу третьего триггера, четвертый триггер, инверсный выход которого подютючен к первому входу четвертого элемента И, пятьй элемент И, первый и второй элементы ИЛИ, первые группы входов и выходов устройства и первые вход и выход устройства, отличающееся тем, что, с целью расширения области применения путем обеспечения приема и обработки информации как в безрегистровых так и в многорегистровых кодах с последующим преобразованием в многорегистровые и безрегистровые коды, соответственно, в него введены первый и второй мультиплексоры, демультиплек- сор, преобразователь кодов, второй блок опреде;ления признаков, блок сравнения, коммутатор и распределитель, входы группы входов первого регистра являются входами первой группы входов устройства, выходы первого регистра подключены к входам первой группы входов первого мультиплексора и к входам первого дешифратора, первый, второй и третий выходы которого подключены к соответствующим входам первой группы входов блока

третий выходы которого подключены к первому, второму и третьему входам коммутатора, соответственно, первый,

30 второй и третий выходы которого подключены к соответствующим входам первого элемента ИЛИ и второго блока определения признаков, первый, второй и третий выходы которого подключены

35 к соответствующим входам третьей группы входов второго мультиплексора выходы которого подключены к входам группы входов преобразователя кодов, выходы которого подключены к BXOftaM

40 группы входов демультиплексора, выходы первой группы выходов которого являются выходами первой группы выходов устройства, выходы второй группы выходов .демультиплексора подключены к

45 входам второго дешифратора и являются выходами второй группы выходов устройства, первые входы вторых триггера и элемента ИЛИ объединены и являются вторым входом устройства, вторые вхо-

50 ДЬ1 вторых триггера и элемента ИЛИ объ единены и являются первым входом устройства, прямой выход второго триггера подключен к первым вхбдам второго мультиплексора и демультиплексора и

55 к второму входу первого элемента И, выход которого является первым выходом устройства, инверсный выход второго триггера подключен к вторым входам второго мультиплексора и демульти

ro мультиплексора и к входам третьего дешифратора, первый, второй и

сравнения и к соответстйующим входам второй группы входов первого мультиплексора, выходы которого подключены к входам первой группы входов второго мультиплексора, первый, второй и третий выходы первого блока определения признаков подключены к соответствующим входам второй группы входов блока сравнения, выход которого подключен к входу элемента НЕ и к первому входу пятого элемента И, выход которого подключен к второму входу третьего триггера, прямой и инверсный выходы которого подключены к первому и второму входам первого мультиплексора, соответственно, четвертый и пятый выходы второго дешифратора подключены к первому и второму входам первого триггера, группа входов второго регистра является входам второй группы входов устройства, выходы второго регистра подключены к входам второй группы входов второтретий выходы которого подключены к первому, второму и третьему входам коммутатора, соответственно, первый,

второй и третий выходы которого подключены к соответствующим входам первого элемента ИЛИ и второго блока определения признаков, первый, второй и третий выходы которого подключены

к соответствующим входам третьей группы входов второго мультиплексора, выходы которого подключены к входам группы входов преобразователя кодов, выходы которого подключены к BXOftaM

группы входов демультиплексора, выходы первой группы выходов которого являются выходами первой группы выходов устройства, выходы второй группы выходов .демультиплексора подключены к

входам второго дешифратора и являются выходами второй группы выходов устройства, первые входы вторых триггера и элемента ИЛИ объединены и являются вторым входом устройства, вторые вхо-

ДЬ1 вторых триггера и элемента ИЛИ объединены и являются первым входом устройства, прямой выход второго триггера подключен к первым вхбдам второго мультиплексора и демультиплексора и

к второму входу первого элемента И, выход которого является первым выходом устройства, инверсный выход второго триггера подключен к вторым входам второго мультиплексора и демультиплексора, выход второго элемента И является вторым Выходом устройства, первый выход распределитепя подключен к входу второго регистра, к первому входу четвертого триггера, к третьему входу первого элемента И и к второму входу второго элемента И, второй выход распределителя подключен к четвертому входу коммутатора и к вторым входам третьего и пятого элементов И, третий выход аспредели

теля подключен к второму входу четвертого элемента И, выход KOTOpoiro подключен к входу преобразователя кодов, выход первого элемента ИЛИ подключен к второму входу четвертого триггера, выход второго элемента И1М подключен к первому входу распределителя, второй и третий входы которого являются третьим и четвертым входами устройства соответственно.

Фи9,Т

сриг2

Cpt4P.S

| Устройство для приема и обработки информации в многорегистровых кодах | 1982 |

|

SU1049951A1 |

Авторы

Даты

1988-12-15—Публикация

1987-04-23—Подача