Изобретение относится к вычислительной технике и может быть использовано для организации межмашинного обмена в вычислительных системах реального времени.

Цель изобретения - повышение быстродействия устройства.

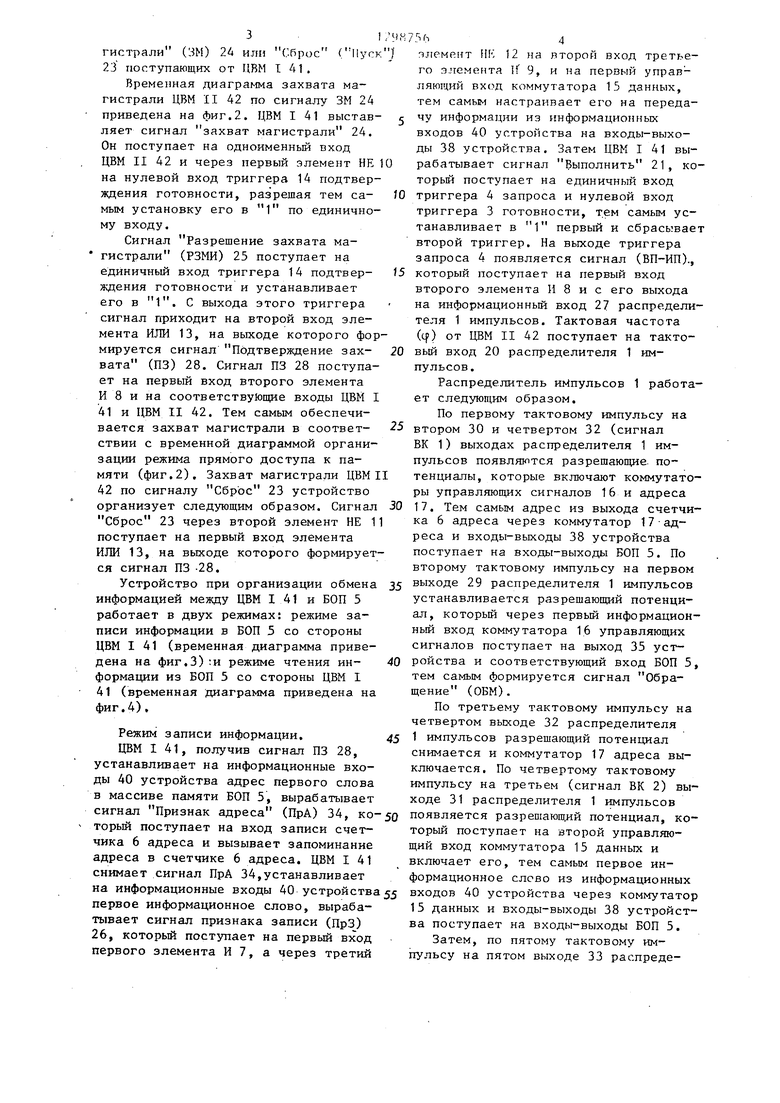

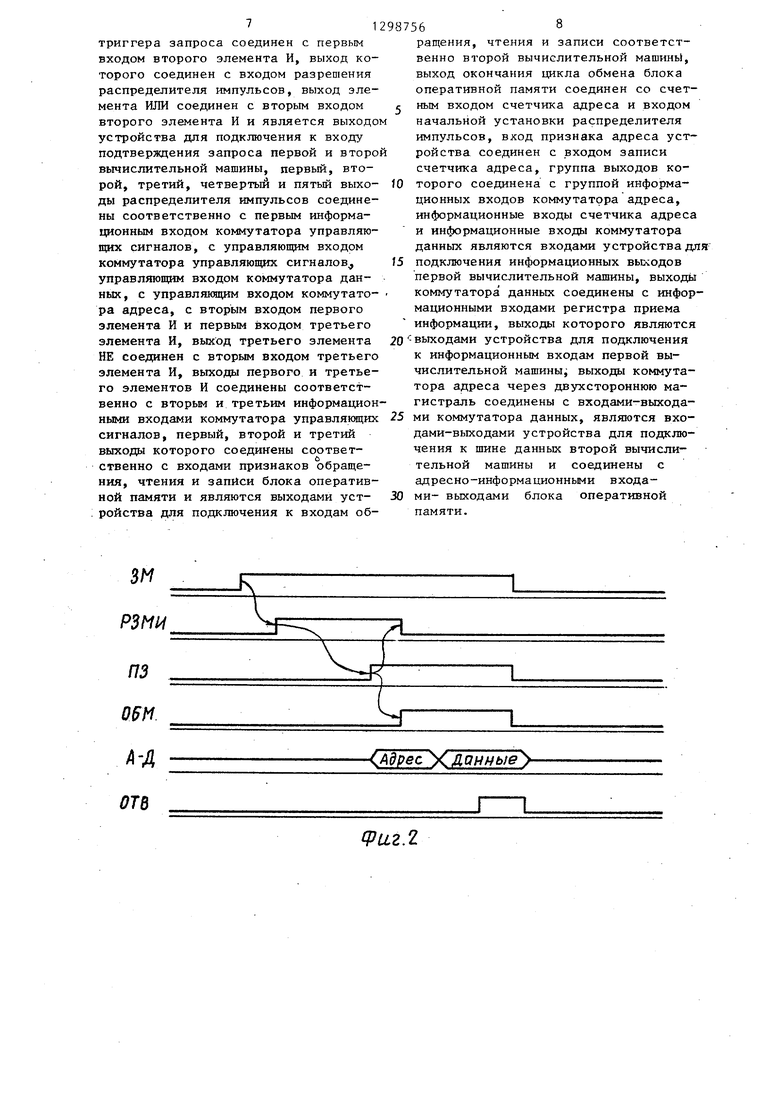

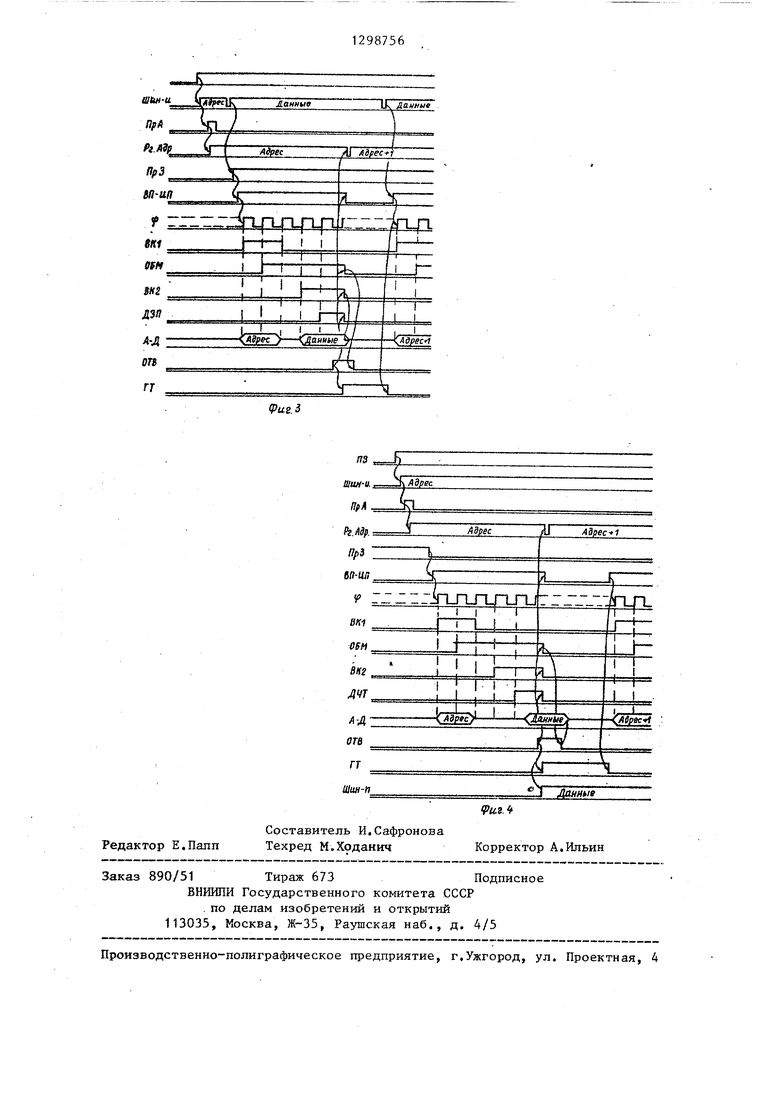

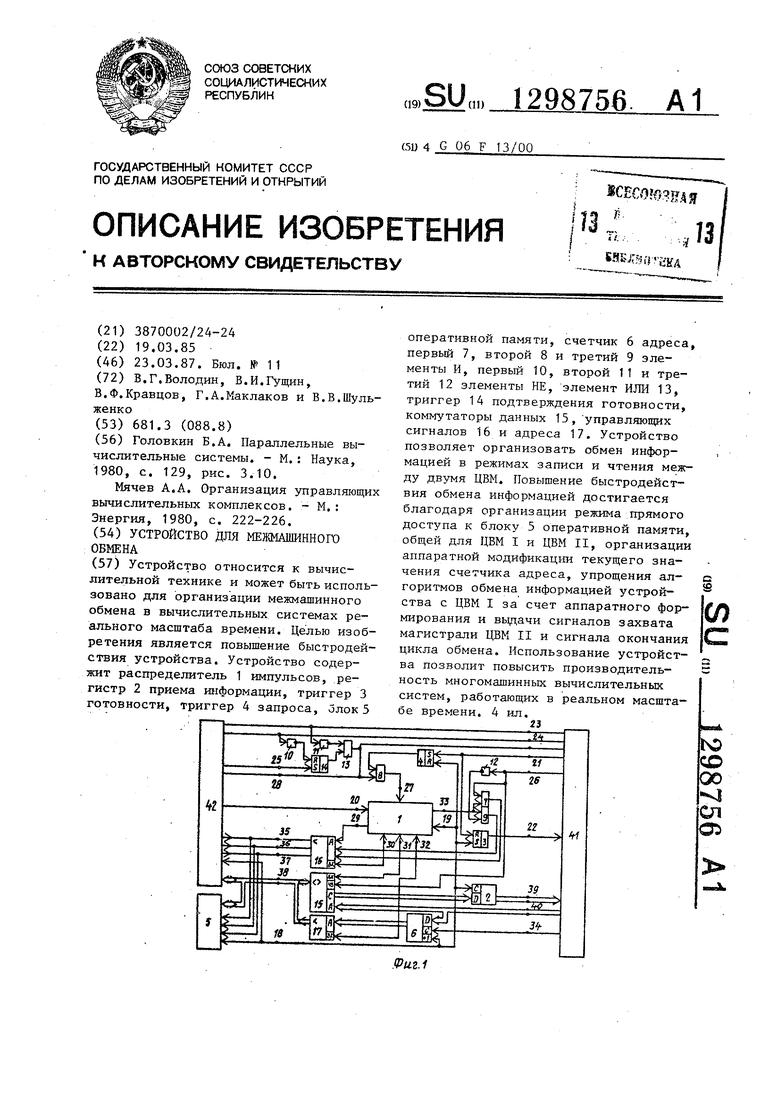

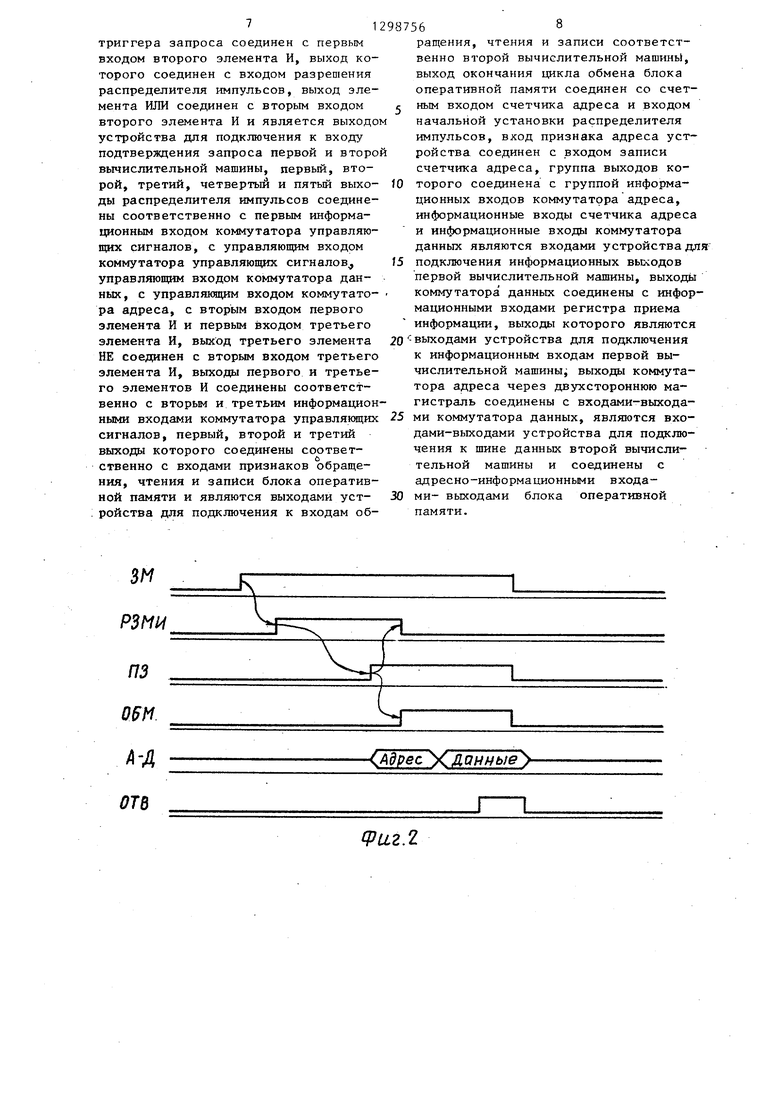

Иа фиг.1 представлена структурная схема устройства для межмашинного обмена; на фиг.2-4 - временные диаграммы работы устройства соответственно в р.ежимах захвата магистрали записи и чтения.

Устройство содержит распределитель 1 импульсов, регистр 2 приема информации, триггер 3 готовности, триггер 4. запроса, блок 5 оперативной памяти (БОП), счетчик 6 адреса, первый 7, второй 8, третий 9 элементы И, первый 10, второй 11, третий 12 элементы НЕ, элемент ИЛИ 13, триггер 14 подтверждения готовности, коммутаторы данных 15, управляющих сигналов 16 и адреса 17, причем выход 18 окончания цикла обращения . блока 5 оперативной памяти соединен с единичным входом триггера 3 готовности, нулевым входом триггера 4 запроса, тактовьм входом регистра 2 приема информации, с счетным входом счетчика 6 адреса и входом 19 начальной установки распределителя 1 импульсов, тактовый вход устройства соединен с тактовым входом 20 распределителя 1 импульсов, вход 21 требования обмена устройства соединен с единичным входом триггера 4 запроса и нулевым входом триггера 3 готовности, выход которого является вы- ходом 22 окончания цикла обмена устройства, входы пуска 23 и захвата магистрали 24 соединены с первым 10 и вторым 11 элементами НЕ, вход 25 разрешения захвата магистрали устройства соединен с единичным входом триггера 14 подтверждения готовности вход, 26 признака записи устройства соединен с первым входом первого элемента И 7, с первым управляющим входом коммутатора 15 данных и с входом третьего элемента НЕ 12, выход второго элемента И 8 соединен с входом 27 разрешения распределителя 1 импульсов, выход элемента ИЛИ 13 соединен с вторым входом второго элемента И 8 и является выходом подтверждения запроса устройства 28, первый 29, второй 30, третий 31 и

четвертый 32 выходы распределителя импульсов 1 соединены соответственно с первым информационным входом и управляющим входом коммутатора 16 управляющих сигналов, с управляющим входом коммутатора 15 данных и с управляющим входом коммутатора 17 адреса, пятый выход 33 распределителя 1 импульсов соединен с вторым входом

первого элемента И 7 и первым входом третьего элемента И 9, вход признака адреса 34 устройства соединен с входом записи счетчика 6 адреса, первый 35, второй 36, третий 37 выходы коммутатора 16 управляющих сигналов являются выходами соответственно обращения, чтения и записи устройства и соединены с соот детствующими входами блока 5 оперативной памяти, выходы коммутатора 17 адреса через двухстороннюю магистраль соединены с входами-выходами коммутатора данных, являются адресно-информационными входами-выходами 38 блока 5 оперативной памяти, выходы регистра 2 приема iffiформации являются информационными выходами 39 устройства, информационные входы 40 устройства сое- диненьР с информационными входами счетчика 6 адреса и коммутатора 15 данных. Кроме того, на фиг.1 показаны первая цифровая вычислительная машина (ЦВМ I) 41 и вторая цифровая вычислительная машина (ЦВМ II) 42, выходы 28, 22, 39 и входы 23, 24, 21, 26, 34, 40 устройства соединены с со- ответствуюшрими входами и выходами ЦВМ I 41, а выходы 23, 24, 28, 35-37, входы 20, 18 и входы-выходы 38 устройства соединены с соответствуюшрми входами, выходами и входами-выходами ЦВМ II 42.

ЦВМ I 41 и ЦВМ II 42 в состав уст- ройства не входят, а служат лишь для .пояснения его работы.

Устройство работает следующим образом.

Инициатором обмена информацией является ЦВМ I 41. Для осуществления обмена информацией между ЦВМ I 41 и БОП 5 предлагаемое устройство использует режим захвата магистрали

ЦВМ II 42, т.е. выполняется приоста- нов ЦВМ II 42 на время обмена информацией между ЦВМ I 41 и БОП 5. Захват магистрали ЦВМ II 42 может осуществляться по сигналам Захват ма31, ЧН

гистрали ) 2 или Сброс С. 23 поступающих от ЦВМ Т 41.

Временная диаграмма захвата магистрали ЦВМ II 42 по сигналу ЗМ 24 приведена на фиг,2. ЦВМ I 41 выстав- ляет сигнал захват магистрали 24. Он поступает на одноименный вход ЦВМ II 42 и через первый элемент НЕ 10 на нулевой вход триггера 14 подтверждения готовности, разрешая тем са- W мым установку его в 1 по единичному входу.

Сигнал Разрешение захвата ма- гистрали (РЗМИ) 25 поступает на единичный вход триггера 14 подтвер- 5 ждения готовности и устанавливает его в 1. С выхода этого триггера сигнал приходит на второй вход элемента ИЛИ 13, на выходе которого формируется сигнал Подтверждение зах- 20 вата (ПЗ) 28. Сигнал ПЗ 28 поступает на первый вход второго элемента И 8 и на соответствующие входы ЦВМ I

41и ЦВМ II 42. Тем самым обеспечивается захват магистрали в соответ- 25 ствии с временной диаграммой организации режима прямого доступа к памяти (фиг.2). Захват магистрали ЦВМ II

42по сигналу Сброс 23 устройство организует следующим образом. Сигнал 30 Сброс 23 через второй элемент НЕ 11 поступает на первый вход элемента

ИЛИ 13, на выходе которого формируется сигнал ПЗ -28.

Устройство при организации обмена 35 информацией между ЦВМ I 41 и БОП 5 работает в двух режимах: режиме записи информации в БОП 5 со стороны ЦВМ I 41 (временная диаграмма приведена на фиг.З):и режиме чтения ин- 40 формации из БОП 5 со стороны ЦВМ 1 41 (временная диаграмма приведена на фиг.4),

Режим записи информации, 45 ЦВМ I 41, получив сигнал ПЗ 28, устанавливает на информационные вхоы 40 устройства адрес первого слова в массиве памяти БОП 5, вырабатывает сигнал Признак адреса (ПрА) 34, ко-50 торый поступает на вход записи счетика 6 адреса и вызывает запоминание адреса в счетчике 6 адреса. ЦВМ I 41 снимает сигнал ПрА 34,устанавливает а информационные входы 40 устройства 55 ервое информационное слово, вырабаывает сигнал признака записи (ПрЗ) 6, который поступает на первый вход ервого элемента И 7, а через третий

3 h4

njieMRi-TT ПК 12 на BTOpofi вход третьего элемента If 9, и на первый управляющий вход коммутатора 15 данных, тем самым настраивает его на передачу информации из информационных входов 40 устройства на входы-выходы 38 устройства. Затем ЦВМ I 41 вырабатывает сигнал Выполнить 21, ко- торьй поступает на единичный вход триггера 4 запроса и нулевой вход триггера 3 готовности, тем самым устанавливает в 1 первый и сбрасывает второй триггер. На выходе триггера запроса 4 появляется сигнал (ВП-ИП)., который поступает на первый вход второго элемента И 8 и с его выхода на информационный вход 2 распределителя 1 импульсов. Тактовая частота (q) от ЦВМ II 42 поступает на тактовый вход 20 распределителя 1 импульсов.

Распределитель иМпульсов 1 работает следующим образом.

По первому тактовому импульсу на втором 30 и четвертом 32 (сигнал ВК 1) выходах распределителя 1 импульсов появляются разрешающие потенциалы, которые включают коммутаторы управляющих сигналов 16 и адреса 17. Тем самым адрес из выхода счетчика 6 адреса через коммутатор 17адреса и входы-выходы 38 устройства поступает на входы-выходы БОП 5. По второму тактовому импульсу на первом выходе 29 распределителя 1 импульсов устанавливается разрешающий потенциал, который через первый информационный вход коммутатора 16 управляющих сигналов поступает на выход 35 устройства и соответствующий вход БОП 5, тем самым формируется сигнал Обращение (ОБМ).

По третьему тактовому импульсу на четвертом выходе 32 распределителя 1 импульсов разрешающий потенциал снимается и коммутатор 17 адреса выключается. По четвертому тактовому импульсу на третьем (сигнал ВК 2) выходе 31 распределителя 1 импульсов появляется разрешаюш,ий потенциал, который поступает на второй управляющий вход коммутатора 15 данных и включает его, тем самым первое информационное слово из информационных входов 40 устройства через коммутатор 15 данных и входы-выходы 38 устройства поступает на входы-выходы БОП 5.

Затем, по пятому тактовому импульсу на пятом выходе 33 распределителя 1 импульсов появляется разрешающий потенциал, который поступает на второй вход первого элемента И 7 и первый вход третьего элемента И 9. На выходе первого элемента И 7 появ- г ляется единичный потенциал, который через третий информационньй вход коммутатора 16 управляющих сигналов, выход 37 устройства поступает на вход записи БОП 5, тем самым вырабатьшает- W ся сигнал записи (ДЗП). БОП 5 об окончании цикла записи информации сообщает сигналом ОТВ 18, который поступает на единичный вход триггера 3 готовности, нулевой вход триггера 4 15 запроса, тактовый вход регистра приема информации 2, счетный вход счетчика 6 адреса на вход 19 начальной установки распределителя 1 импульсов. По сигналу ОТВ 18 выходы 29-33 рас- 20 пределителя 1 импульсов устанавлива-, ются в исходное состояние, сбрасывается триггер 4 запроса, модифицируется счетчик 6 адреса и устанавливается триггер 3 готовности (ГТ), выход 22 25 которого является, выходом сигнала готовности устройства к следующему циклу обмена информацией в БОП 5.

Режим чтения информации.

Этот режим реализуется следующим 30 образом. Запись адреса в счетчик адреса осуществляется аналогично режиму записи информации. ЦВМ I 41 не выставляет сигнала ПрЗ 26, тем самым коммутатор 15 данных перестраивается на 35 передачу информации из входов-выхоов 38 устройства на входы регистра 2 приема информации. Циклограмма работы по первым четырем тактам тактовой частоты распределителя 1 импуль- Q сов аналогична режиму записи инфор- . мации. По пятому тактовому импульсу единичный потенциал с выхода третьего элемента И 9 поступает на второй информационный вход коммутатора 16 5 управляющих сигналов, выход 36 устройства и на вход сигнала чтения БОП 5, Тем самым вырабатывается сигнал чтения (ДЧТ). БОП 5 об окончании цика чтения информации сообщает уст- о ройству сигналом ОТВ 18. По сигналу ОТВ 18 устройство записывает в регистр 2 приема принятую из БОП 5 через входы-выходы 38 и коммутатор 15 анных информацию и устанавливает ее .55 ерез информационные выходы 39 устойства на соответствующие входы ВМ I 41, По сигналу готовности 22 ВМ I 41 считывает информацию.

г W15 20 25

В режимах загшси (чтения) информации в (из) БОП 5 объем массива контролирует ЦВМ 141.

Формула изобретения

Устройство дг:я межма1т;1нного обмена, содержащее распределитель импульсов, регистр приема информации, триггер готовности, триггер запроса и блок оперативной памяти, причем выход окончания цикла обращения блока оперативной памяти соединен с единичным входом триггера готовности, с нулевым входом триггера запроса и с .i тактовым входом регистра приема информации, тактовьй вход устройства соединен с тактовым входом распределителя импульсов, единичный вход триггера запроса объединен с нулевым входом триггера .готовности и является входом устройства для подключения к выходу требования обмена первой вычислительной машины, выход триггера готовности является выходом устройства для подключения к входу окончания цикла обмена первой вычислительной машины,, отличающее- с я тем, что, с целью повышения быстродействия, в устройство введены счетчик адреса, три элемента И, три элемента НЕ, элемент ИЛИ, триггер подтверждения готовности, коммутатбр данных, коммутатор управляющих сигналов и коммутатор адреса, причем входы первого и второго элементов НЕ являются входами устройства для под- , ключения к выходам пуска и захвата магистрали первой вычислительной ма- тины и к соответствующим входам второй вычислительной машины, выходы первого и второго элементов НЕ соединены соответственно с первым входом элемента ИЛИ и нулевым входом триггера подтверждения готовности, прямой выход которого соединен с вторым входом элемента ИЛИ, единичный вход триггера подтверждения готовности является входом устройства для подключения к выходу разрешения захвата магистрали второй вычислительной машины, первый вход первого элемента И является входом устройства для подключения к выходу признака записи первой вычислительной машины и объединен с первым управляющим входом коммутатора данных и с входом третьего элемента НЕ, прямой выход

триггера запроса соединен с первым входом второго элемента И, выход которого соединен с входом разрешения распределителя импульсов, выход элемента ИЛИ соединен с вторым входом второго элемента И и является выходо устройства для подключения к входу подтверждения запроса первой и второ вычислительной машины, первый, второй, третий, четвертый и пятый выходы распределителя импульсов соединены соответственно с первым информационным входом коммутатора управляющих сигналов, с управляющим входом коммутатора управляющих сигналов управляющим входом коммутатора данных, с управлякяцим входом коммутато-

ра адреса, с вторым входом первого элемента И и первым входом третьего элемента И, выход третьего элемента НЕ соединен с вторым входом третьего элемента И, выходы первого и третьего элементов И соединены соответственно с вторым и третьим информационными входами коммутатора управлякнцих сигналов, первый, второй и третий выходы которого соединены ственно

НИН, чтения и записи блока оперативной памяти и являются выходами устройства для подключения к входам обсоответU

С входами признаков обраще

98756 5

ращения, чтения и записи соответственно второй вычислительной машинь, выход окончания цикла обмена блока оперативной памяти соединен со счетс ным входом счетчика адреса и входом начальной установки распределителя импульсов, вход признака адреса устройства соединен с входом записи счетчика адреса, группа выходов коJO торого соединена с группой информационных входов коммутатора адреса, информационные входы счетчика адреса и информационные входы коммутатора данных являются входами устройства для

15 подключения информационных выходов первой вычислительной машины, выходь: коммутатора данных соединены с информационными входами регистра приема информации, выходы которого являются

20 выходами устройства для подключения к информационным входам первой вычислительной машины выходы коммутатора адреса через двухстороннюю магистраль соединены с входами-выхода25 ми коммутатора данных, являются входами-выходами устройства для подключения к шине данных второй вычислительной машины и соединены с адресно-информационными входа30 ми- выходами блока оперативной памяти.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения цифровой вычислительной машины с периферийными устройствами | 1980 |

|

SU962899A1 |

| Имитатор абонентов | 1983 |

|

SU1291987A1 |

| Устройство для обмена информацией между ЦВМ и внешними устройствами | 1980 |

|

SU907537A1 |

| Аналого-цифровая вычислительная система и аналоговая вычислительная машина (ее варианты) | 1983 |

|

SU1259300A1 |

| Устройство для обмена информацией между ЭВМ | 1990 |

|

SU1784990A1 |

| Устройство для контроля ЦВМ | 1987 |

|

SU1509908A1 |

| Устройство для обмена информацией | 1982 |

|

SU1048468A1 |

| Устройство для сопряжения цифровой вычислительной машины (ЦВМ) с абонентами | 1984 |

|

SU1234843A1 |

| Устройство для сопряжения цифровых вычислительных машин с каналами связи | 1985 |

|

SU1287171A1 |

| Устройство для сопряжения цифровой вычислительной машины с общей магистралью | 1980 |

|

SU907536A1 |

Устройство относится к вычислительной технике и может быть использовано для организации межмашинного обмена в вычислительных системах реального масштаба времени. Целью изобретения является повышение быстродействия устройства. Устройство содержит распределитель 1 импульсов, регистр 2 приема информации, триггер 3 готовности, триггер 4 запроса, олок 5 оперативной памяти, счетчик 6 адреса, первый 7, второй 8 и третий 9 элементы И, первый 10, второй 11 и третий 12 элементы НЕ, элемент ИЛИ 13, триггер 14 подтверждения готовности, коммутаторы данных 15, управляющих сигналов 16 и адреса 17. Устройство позволяет организовать обмен информацией в режимах записи и чтения между двумя ЦВМ. Повышение быстродействия обмена информацией достигается благодаря организации режима прямого доступа к блоку 5 оперативной памяти, общей для ЦВМ I и ЦВМ II, организации аппаратной модификации текущего значения счетчика адреса, упрощения алгоритмов обмена информацией устройства с ЦВМ I за счет аппаратного формирования и выдачи сигналов захвата магистрали ЦВМ II и сигнала окончания цикла обмена. Использование устройства позволит повысить производительность многомашинных вычислительных систем, работающих в реальном масштабе времени. 4 ил. 23 i СЛ ю CD 00 ел О5

(Адрес Сланные

сриг.г

| Головкин Б.А | |||

| Параллельные вычислительные системы | |||

| - М.: Наука, 1980, с | |||

| Способ применения резонанс конденсатора, подключенного известным уже образом параллельно к обмотке трансформатора, дающего напряжение на анод генераторных ламп | 1922 |

|

SU129A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Мячев А.А | |||

| Организация управляющих вычислительных комплексов | |||

| - М.: Энергия, 1980, с | |||

| Камневыбирательная машина | 1921 |

|

SU222A1 |

Авторы

Даты

1987-03-23—Публикация

1985-03-19—Подача