Изобретение относится к вычислительной технике и может быть использовано для тестирования ЦВМ..

Целью изобретения является повышение эффективности проверки и быстродействия.

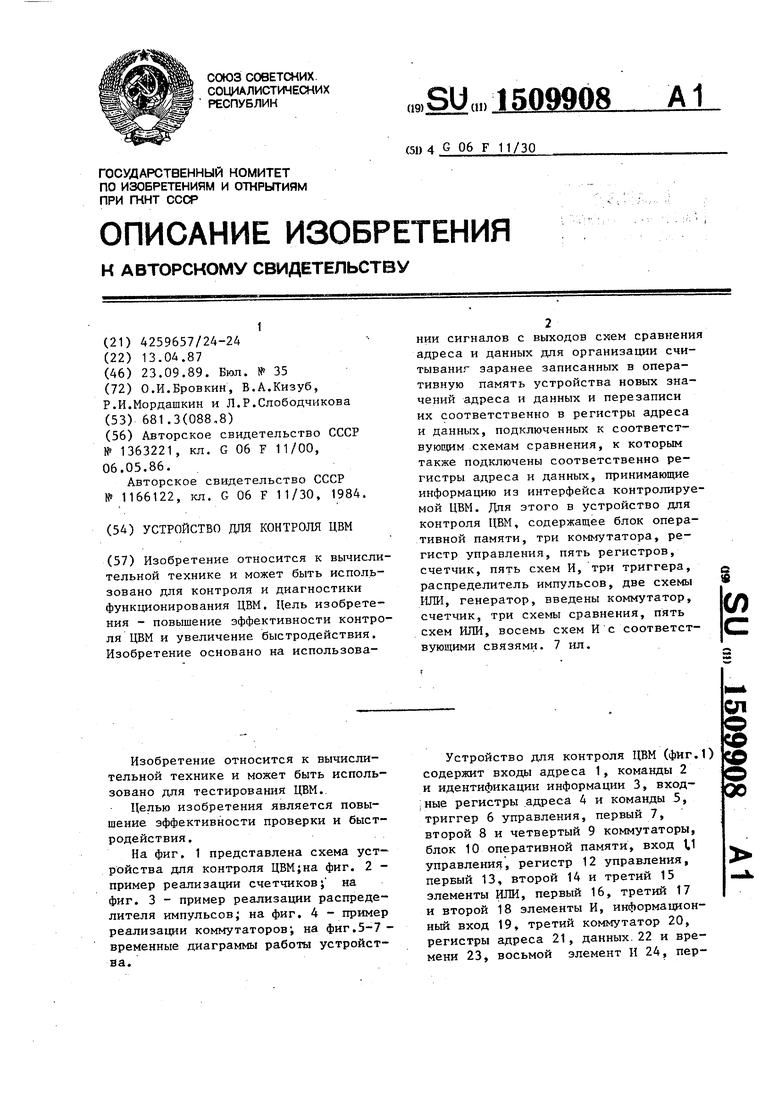

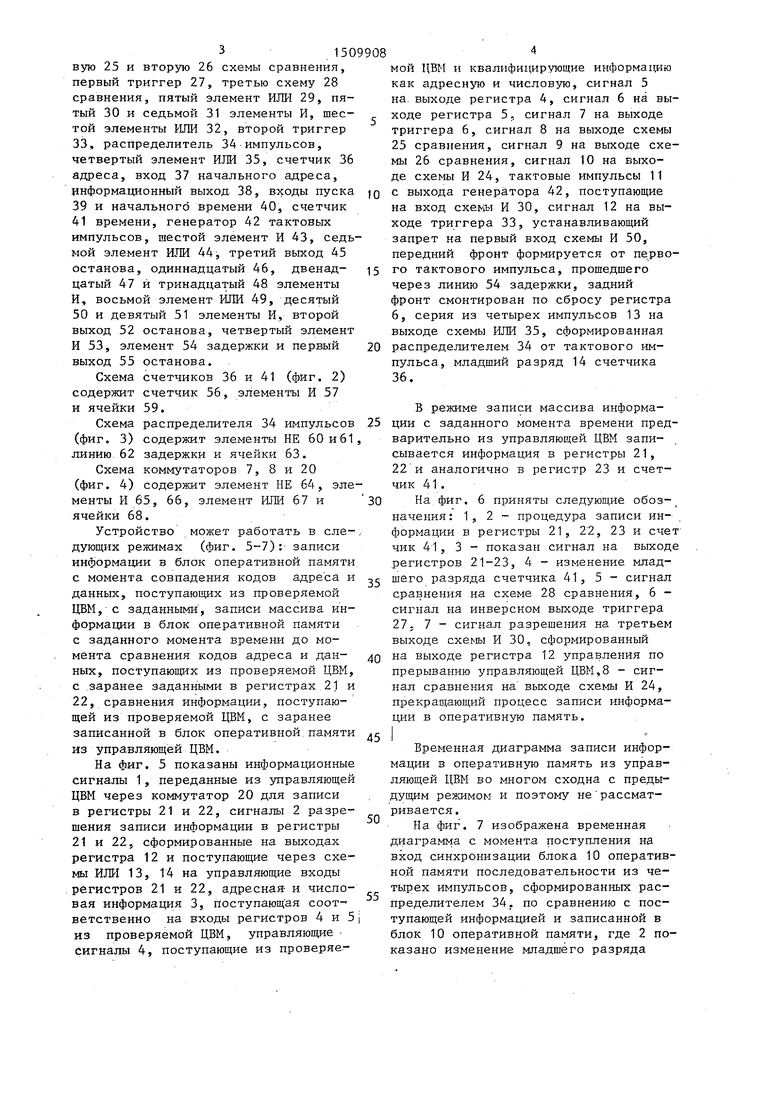

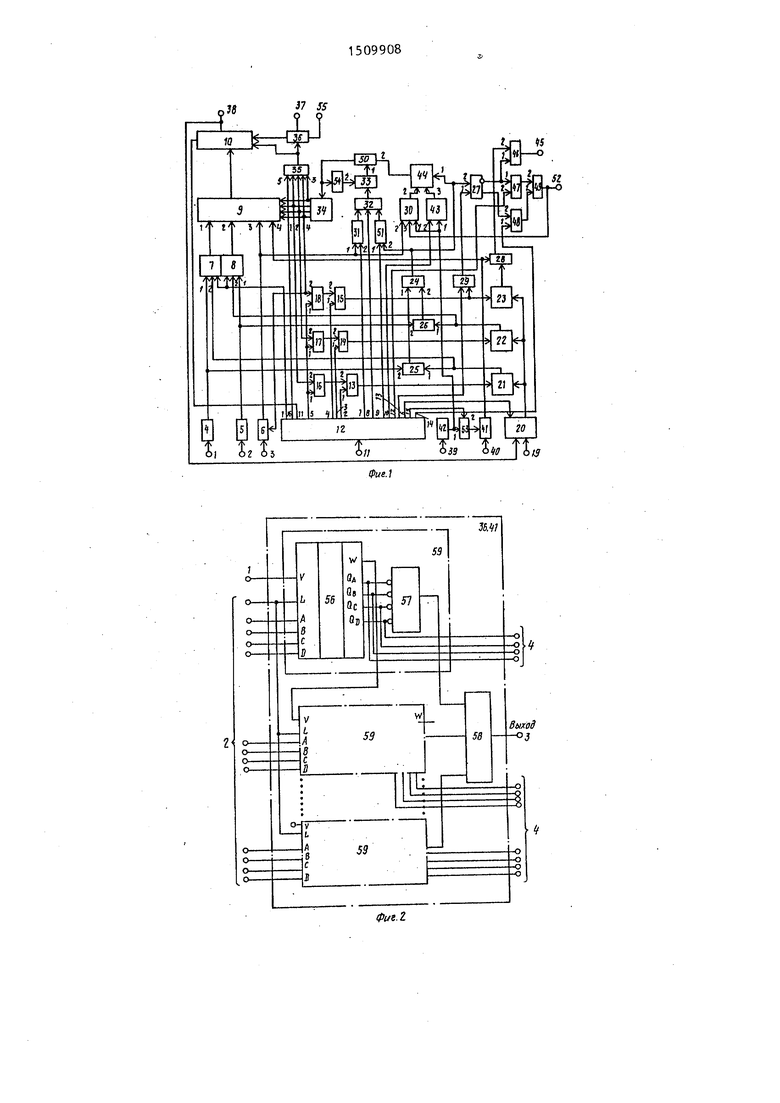

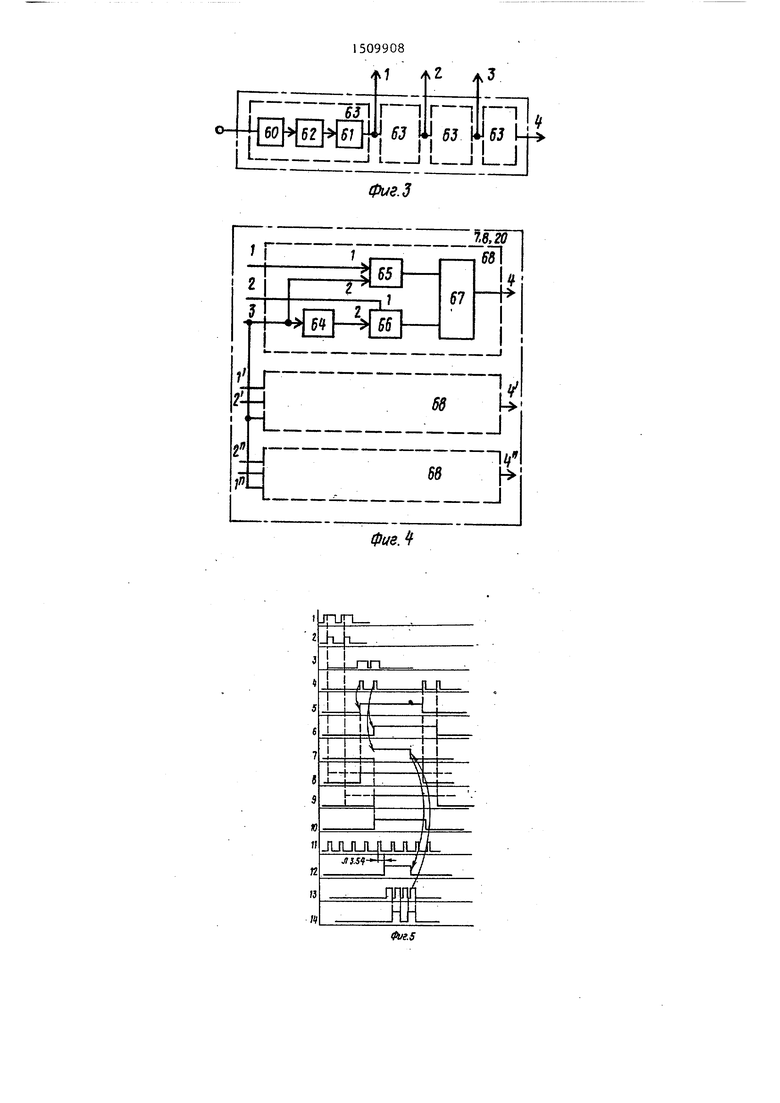

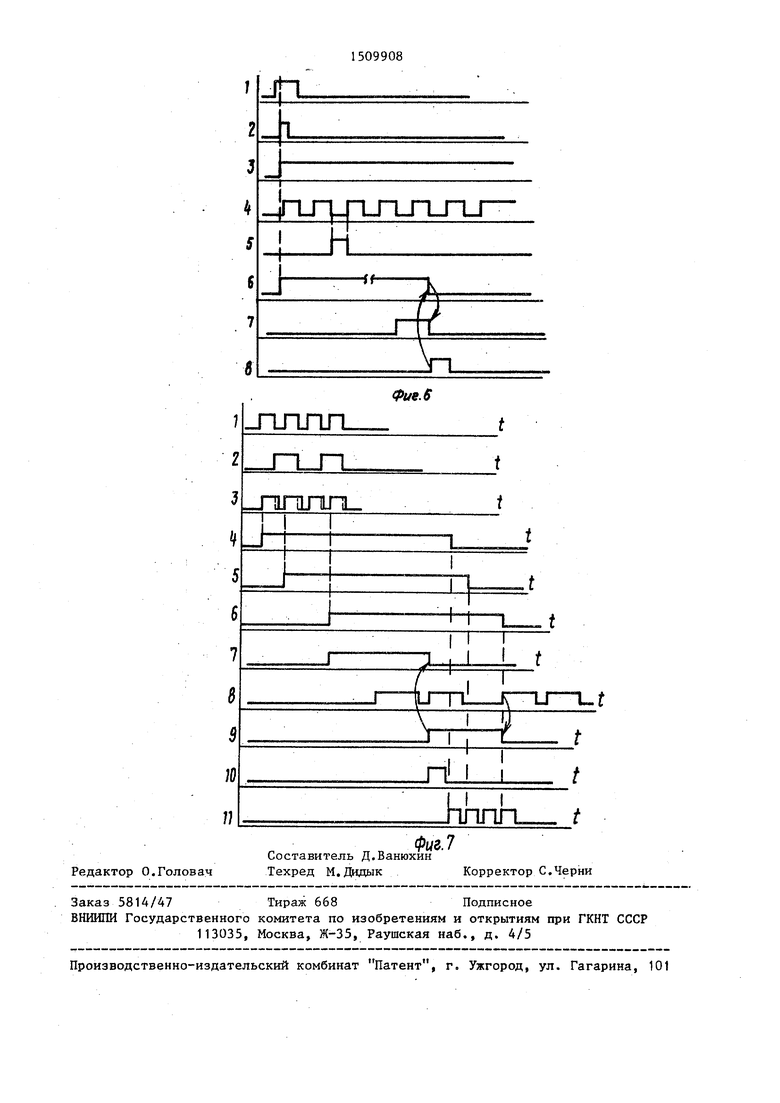

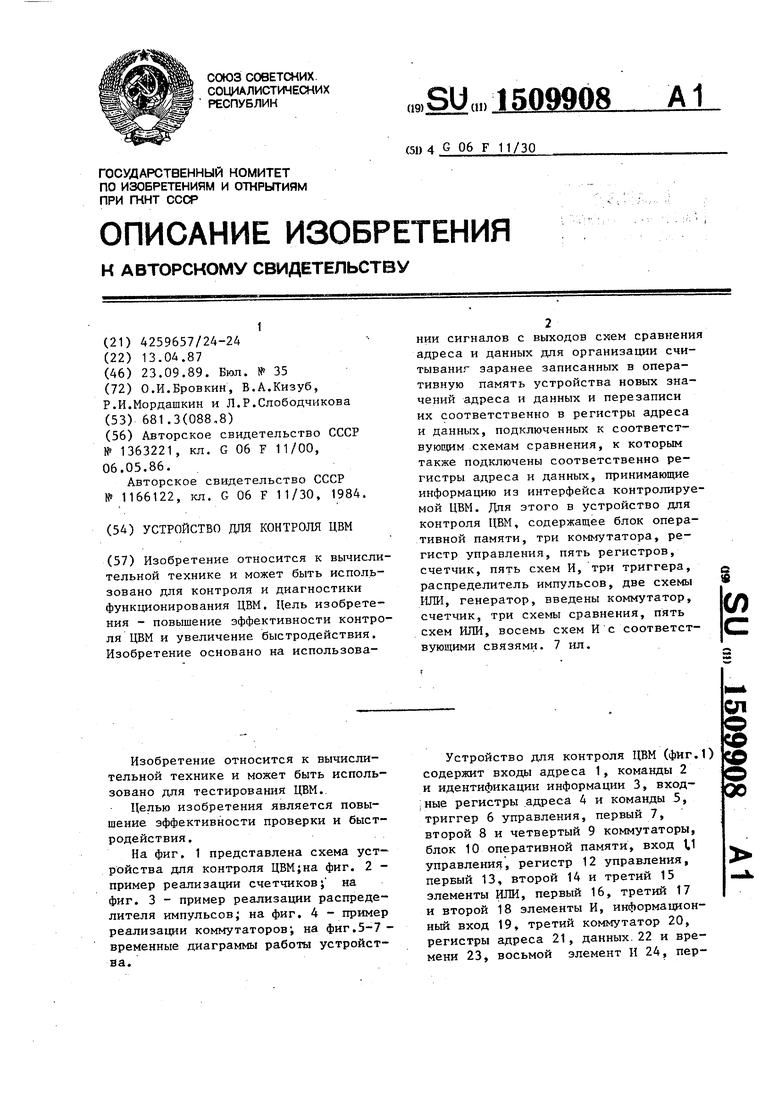

На фиг. 1 представлена схема устройства для контроля ЦВМ;на фиг. 2 - пример реализации счетчиков j на фиг. 3 - пример реализации распределителя импульсов; на фиг, 4 - пример реализации коммутаторов , на фиг.5-7- временные диаграммы работы устройства.

Устройство для контроля ЦВМ (фИг.1) содержит входы адреса 1, команды 2 и идентификации информации 3, вход- :ные регистры адреса 4 и команды 5, триггер 6 управления, первый 7, второй 8 и четвертый 9 коммутаторы, блок 10 оперативной памяти, вход 1,1 управления, регистр 12 управления, первый 13, второй 14 и третий 15 элементы ИЛИ, первый 16, третий 17 и второй 18 элементы И, информационный вход 19, третий коммутатор 20, регистры адреса 21, данных.22 и времени 23, восьмой элемент И 24, пер3150

вую 25 и вторую 26 схемы сравнения, первый триггер 27, третью схему 28 сравнения, пятый элемент ИЛИ 29, пятый 30 и седьмой 31 элементы И, шестой элементы ИЛИ 32, второй триггер 33, распределитель 34 импульсов, четвертый элемент ИЛИ 35, счетчик 36 адреса, вход 37 начального адреса, информационный выход 38, входы пуска 39 и начального времени 40, счетчик 41 времени, генератор 42 тактовых импульсов, шестой элемент И 43, седьмой элемент ИЛИ 44, третий выход 45 останова, одиннадцатый 46, двенад- цатый 47 и тринадцатый 48 элементы И, восьмой элемент ИЛИ 49, десятый 50 и девятый 51 элементы И, второй выход 52 останова, четвертый элемент И 53, элемент 54 задержки и первый выход 55 останова.

Схема счетчиков 36 и 41 (фиг. 2) содержит счетчик 56, элементы И 57 и ячейки 59.

Схема распределителя 34 импульсов (фиг. 3) содержит элементы НЕ 60и61 линию 62 задержки и ячейки 63.

Схема коммутаторов 7, 8 и 20 (фиг. 4) содержит элемент НЕ 64, элементы И 65, 66, элемент ИЛИ 67 и ячейки 68.

Устройство может работать в еледующих режимах (фиг. 5-7):- записи информации в блок оперативной памяти с момента совпадения кодов адреса и данных, поступающих из проверяемой ЦВМ,-с заданными , записи массива информации в блок оперативной памяти с заданного момента времени до момента сравнения кодов адреса и дан- ных, поступающих из проверяемой ЦВМ, с .заранее заданными в регистрах 21 и 22, сравнения информации, поступающей из проверяемой ЦВМ, с заранее записанной в блок оперативной памяти из управляющей ЦВМ.

На фиг. 5 показаны информационные сигналы 1, переданные из управляющей ЦВМ через коммутатор 20 для записи в регистры 21 и 22, сигналы 2 разрешения записи информации в регистры 21 и 22, сформированные на выходах регистра 12 и поступающие через схемы ИЛИ 13, 14 на управляющие входы регистров 21 и 22, адресная- и числовая информация 3, поступающая соот- ветственно на входы регистров 4 и 5 из проверяемой ЦВМ, управляющие сигналы 4, поступающие из проверяе

д 5 0

5

30

с 0 ,г

0

мой ЦВМ и квалифицирующие информацию как адресную и числовую, сигнал 5 на. выходе регистра 4, сигнал 6 на выходе регистра 5. сигнал 7 на выходе триггера 6, сигнал 8 на выходе схемы 25 сравнения, сигнал 9 на выходе схемы 26 сравнения, сигнал 10 на выходе схемы И 24, тактовые импульсы 11 с выхода генератора 42, поступающие на вход схегФ И 30, сигнал 12 на выходе триггера 33, устанавливающий запрет на первый вход схемы И 50, передний фронт формируется от первого тактового импульса, прошедшего через линию 54 задержки, задний фронт смонтирован по сбросу регистра 6, серия из четырех импульсов 13 на выходе схемы ИЛИ 35, сформированная распределителем 34 от тактового им- цульса, младший разряд 14 счетчика 36.

В режиме записи массива информации с заданного момента времени предварительно из управляющей ЦВМ записывается информация в регистры 21, 22 н аналогично в регистр 23 и счетчик 41.

На фиг. 6 приняты следующие обоз-, начения: 1,2- процедура записи информации в регистры 21, 22, 23 и счет чик 41, 3 - показан сигнал на выходе регистров 21-23, 4 - изменение младшего разряда счетчика 41, 5 - сигнал сравнения на схеме 28 сравнения, 6 - сигнал на инверсном выходе триггера 27. 7 - сигнал разрешения на третьем выходе схемы И 30, сформированный на выходе регистра 12 управления по прерыванию управляющей ЦВМ,8 - сигнал сравнения на выходе схемы И 24, прекращающий процесс записи информации в оперативную память.

Временная диаграмма записи информации в оперативную память из управляющей ЦВМ во многом сходна с предыдущим режимом и поэтому не рассматривается.

На фиг. 7 изображена временная диаграмма с момента цоступления на вход синхронизации блока 10 оператив- нрй памяти последовательности из четырех импульсов, сформированных распределителем 34. по сравнению с поступающей информацией и записанной в блок 10 оперативной памяти, где 2 показано изменение младшего разряда

515099086

счетчика 30, 3 - информация на выходе формации в регистры 21 и 22 соответкоммутатора 20, поступившая из блока 10 оперативной памяти, 4-6 - сигналы соответственно на выходах регистров 21-23, 7 - сигнал разрешения на пер- |вом входе схемы И 46 с инверсного выхода триггера 27, 8 - адресная и числовая информации, поступающие на входы регистров 4 и 5 соответственно, 9 - сигнал сравнения на выходе схемы И 24, 10 - сигнал с выхода схемы И 50, 11 - последовательность сигналов на выходе схемы И 35, сформированная распределителем 34.

Устройство может работать в режиме записи информации в блок оперативной памяти из проверяемой ЦВМ без нарушения в ней хода вычислительного процесса, режима записи информации в блок оперативной памяти из ЦВМ управляющей проверкой, в режиме считывания информации из блока оператив- ной памяти и в режиме сравнения поступающей в реальном масштабе времени информации из интерфейса проверяемой ЦВМ и заранее записанной в блок оперативной памяти.

Режим работы определяется текущими задачами проверки и устанавливается кодом на выходах регистра 12 управления, который через вход 11 подключен к ЦВМ, управляющей проверкой.

Запись информации в блок оперативной памяти может начинаться с момента совпадения кодов адреса и данных, поступающих через входы 1 и 2 устройства с заданными в регистрах 21, 22 соответственно и продолжаются до переполнения счетчика 36.

Для организации этого режима управляющей ЦВМ через вход 11 устройства записывает в регистр 12 управления код, который на выходе формирует сигнал, разрешающий подключение выходов регистров 4 и 5 соответственно к первым канальным входам коммутаторов 7 и 8, формирует сигналы разрешения на схемы И 31, сигналы запрета на схемы И 51, 43, сигнал, разрешающий подк5пючение к первому канальному входу коммутатора 20 входа 19 устройства, режима записи информации в блок оперативной памяти. Управляющая ЦВМ через вход 19 устройства последова20

25

ственно. Через вход 37 устройства управляющая ЦВМ записывает в счетчик 36 код, соответствующий начальному адресу блока 10 оперативной памяти. В регистры 4 и 5 через входы 1 и 2 устройства соответственно подаются из проверяемой ЦВМ коды адресов

1Q и коды числовой и командной информации. В триггер 6 через вход 3 устройства подаются управляю1цие сигналы, сопутствукнцие информационным кодам (например, сигналы, квалифицирующие

15 их на адрес, число записываемое в ОЗУ или считываемое из ОЗУ, вектор прерывания и т.д.).

КогДа содержимое регистров 4 и 5 совпадает соответственно с содержимым регистров 21 и 22, схемы 25 к 26 сравнения формируют с помощью схемы И 24 сигнал, который переводит триггер 27 в единичное состояние, при этом с прямого выхода триггера сигнал через схемы И 48 и ИЛИ 49 дает разрешение на вход схемы И 30. Цри наличии на входе схемь: И 30 разрешающего потенциала через нее и схему ИЛИ 44 на вход схемы И 50 поступают импульсы с выхода генератора 42 тактовых импульсов. Разрешающий сигнал на входе схемы И 30 формируется от одного из управляющих сигналов, характеризующего наличие в интерфейсе проверяемой ЦВМ информации, записываемой в регистры 4 и 5. Таким образом, на второй вход схемы И 30 поступает сигнал, когда в регистрах 4 и 5 находится соответствующая ему информация. Цервый импульс на выходе схемы И 50 перебрасывает триггер 33 в противоположное состояние и триггер выдает запрет на вход схемы И 50..

Таким образом, на вход распределителя 34 поступает импульс, который преобразуется в последовательность из четырех импульсов на выходах распределителя. Импульс на первом выходе распределителя подключает на время длительности через первый управляющий вход коммутатора 9 его второй канальный вход к числовому входу блока 10 оперативной памяти. Кроме того, первый импульс поступает через

30

35

40

45

50

ее

тельно в регистры 21 н 22 записываетсхему ИЛИ 35 на вход синхронизации

информацию, предварительно записываяблока 10 оперативной памяти и произв регистр 12 коды, формирующие на вы-водит запись информации по адресу,

ходах сигналы, разрешаюпще запись ни-установленному в счетчике 36, затем ,

0

5

ственно. Через вход 37 устройства управляющая ЦВМ записывает в счетчик 36 код, соответствующий начальному адресу блока 10 оперативной памяти. В регистры 4 и 5 через входы 1 и 2 устройства соответственно подаются из проверяемой ЦВМ коды адресов

и коды числовой и командной информации. В триггер 6 через вход 3 устройства подаются управляю1цие сигналы, сопутствукнцие информационным кодам (например, сигналы, квалифицирующие

5 их на адрес, число записываемое в ОЗУ или считываемое из ОЗУ, вектор прерывания и т.д.).

КогДа содержимое регистров 4 и 5 совпадает соответственно с содержимым регистров 21 и 22, схемы 25 к 26 сравнения формируют с помощью схемы И 24 сигнал, который переводит триггер 27 в единичное состояние, при этом с прямого выхода триггера сигнал через схемы И 48 и ИЛИ 49 дает разрешение на вход схемы И 30. Цри наличии на входе схемь: И 30 разрешающего потенциала через нее и схему ИЛИ 44 на вход схемы И 50 поступают импульсы с выхода генератора 42 тактовых импульсов. Разрешающий сигнал на входе схемы И 30 формируется от одного из управляющих сигналов, характеризующего наличие в интерфейсе проверяемой ЦВМ информации, записываемой в регистры 4 и 5. Таким образом, на второй вход схемы И 30 поступает сигнал, когда в регистрах 4 и 5 находится соответствующая ему информация. Цервый импульс на выходе схемы И 50 перебрасывает триггер 33 в противоположное состояние и триггер выдает запрет на вход схемы И 50..

Таким образом, на вход распределителя 34 поступает импульс, который преобразуется в последовательность из четырех импульсов на выходах распределителя. Импульс на первом выходе распределителя подключает на время длительности через первый управляющий вход коммутатора 9 его второй канальный вход к числовому входу блока 10 оперативной памяти. Кроме того, первый импульс поступает через

0

5

0

5

0

е

71509908

задним фронтом увеличивает содержимое

счетчика 36 на единицу и тем самь1м, подготавливает его для записи следующей информации от второго импульса. Второй импульс подключает третий канальный вход коммутатора 9 к блоку 10 оперативной памяти и производит запись информации. Аналогичные действия производят третий и четвертый импульсы. Кроме того, четвертый импульс обнуляет триггер 6 управляющих сигналов, поэтому на вход схемы И 30 выдаётся запрет, а на выход - разрешающий сигнал, который через схему ИЛИ 32 переводит триггер 33 в исходное состояние. С приходом следующего управляющего сигнала процесс повторяется.

В блок 10 оперативной памяти можно записать массив информации из прог веряемой ЦВМ с заранее заданного момента времени до момента сравнения содержимого регистров 4 и 5 с регистрами 21 и 22 соответственно либо по переполнению счетчика 36. При этом после записи информации из управляющей ЦВМ в регистры 21 и 22 в регистр 12 управления записывается код, при котором с выхода регистра 12 через схему ИЛИ 15 на управляющий вход регистра 23 поступает сигнал, разрешающий в него запись информации, а на установочный вход триггера 27 через схему ИЛИ 29 поступает сигнал исходной установки, с инверсного выхода триггера на входы схем И 46, 47 выдается сигнал разрешения. Цосле записи информации в регистр 23 в регистр-12 управления записывается код, снимающий с выхода сигнал, разрешающий запись в -регистр 23. В счетчик 41 из управляющей ЦВМ через вход 40 устройства записывается исходный код и в генератор 42 тактовых импульсов через вход 39 устройства вы- .дается запуск с началом вычислений проверяемой ЦВМ, при этом содержимое счетчика 41 начинает увеличиваться на единицу. При совпадении содержи10

15

Далее схема работает как в преды дущем режиме до момента сравнения содержимого регистров 4 и 5 с регис рами 21 и 22, при этом сигналом от схем 25, 26 сравнения через схему И 24 триггер 27 переводится в едини ное состояние, при котором на инвер ном его выходе будет запрещающий си нал на вход схемы И 47. Этот сигнал через схемы И 47 и ИЛИ 49 выдает з,а рет на вход схемы И 30. При этом че рез выход 52 устройства вьщается си нал, который можно использовать для организации прерывания в управляюще ЦВМ или Останова в проверяемой ЦВМ

Для организации записи массива информации из управляющей ЦВМ в бло 10 оперативной памяти в регистр 12

20 управления записывается код, которы формирует на первом выходе регистра сигнал, подключающий вторые канальн входы на коммутаторах 7 и 8 к выход регистров 21 и 22. соответственно,

25 сигнал, устанавливающей триггер 33 через схему ИЛИ 32 в исходное состо ние. Затем в регистр 12 управления последовательно записываются коды, которые на выходе регистра формирую через схему ИЛИ 13 сигнал разрешения записи информации в регистр 21, после чего производит ся запись из управ ляющей ЦВМ в этот регистр. Затем фор мируется на выходе регистра 12 управления сигнал, разрешающий запись в регистр 22, и производится запись в этот регистр информации из ynpiaB- ляющей ЦВМ. Затем производится через вход 40 устройства запись информации в счетчик 41. В этом режиме с выхода регистра 12 формируется сигнал, запрещающий через схему И 53 прохождени импульсов из генератора 42 в счетчик 41, с выхода 10 - сигнал, разрешающи прохождение импульсов генератора-че рез схему И 43. После того через схе му И 50 на распределитель поступает импульс, который организует запись в блок 10 оперативной памяти информа ции последовательно из регистров 21

30

35

40

45

мого регистра 23 со счетчиком 41 схе-5 22 и счетчика 41, начиная с адреса.

8

0

5

Далее схема работает как в предыдущем режиме до момента сравнения содержимого регистров 4 и 5 с регистрами 21 и 22, при этом сигналом от схем 25, 26 сравнения через схему И 24 триггер 27 переводится в единичное состояние, при котором на инверсном его выходе будет запрещающий сигнал на вход схемы И 47. Этот сигнал через схемы И 47 и ИЛИ 49 выдает з,ап- рет на вход схемы И 30. При этом через выход 52 устройства вьщается сигнал, который можно использовать для организации прерывания в управляющей ЦВМ или Останова в проверяемой ЦВМ.

Для организации записи массива информации из управляющей ЦВМ в блок 10 оперативной памяти в регистр 12

0 управления записывается код, который формирует на первом выходе регистра сигнал, подключающий вторые канальные входы на коммутаторах 7 и 8 к выходам регистров 21 и 22. соответственно,

5 сигнал, устанавливающей триггер 33 через схему ИЛИ 32 в исходное состоя-, ние. Затем в регистр 12 управления последовательно записываются коды, которые на выходе регистра формируют через схему ИЛИ 13 сигнал разрешения записи информации в регистр 21, после чего производит ся запись из управляющей ЦВМ в этот регистр. Затем формируется на выходе регистра 12 управления сигнал, разрешающий запись в регистр 22, и производится запись в этот регистр информации из ynpiaB- ляющей ЦВМ. Затем производится через вход 40 устройства запись информации в счетчик 41. В этом режиме с выхода регистра 12 формируется сигнал, запрещающий через схему И 53 прохождение импульсов из генератора 42 в счетчик 41, с выхода 10 - сигнал, разрешающий прохождение импульсов генератора-через схему И 43. После того через схему И 50 на распределитель поступает импульс, который организует запись в блок 10 оперативной памяти информации последовательно из регистров 21,

0

5

0

5

22 и счетчика 41, начиная с адреса.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для отладки программ | 1986 |

|

SU1363221A1 |

| Устройство для сопряжения цифровой вычислительной машины с периферийными устройствами | 1980 |

|

SU962899A1 |

| Устройство для отладки программ | 1984 |

|

SU1166122A1 |

| Устройство для модификации адреса зон памяти при отладке программ | 1983 |

|

SU1161944A1 |

| Устройство для обмена информацией | 1981 |

|

SU962901A2 |

| Имитатор абонентов | 1983 |

|

SU1291987A1 |

| Устройство для отображения информации на экране телевизионного индикатора | 1986 |

|

SU1695372A1 |

| Аналого-цифровая вычислительная система и аналоговая вычислительная машина (ее варианты) | 1983 |

|

SU1259300A1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЦВМ С КАНАЛОМ СВЯЗИ | 1991 |

|

RU2011217C1 |

| Устройство для ввода информации | 1982 |

|

SU1075248A1 |

Изобретение относится к вычислительной технике и может быть использовано для контроля и диагностики функционирования ЦВМ. Цель изобретения - повышение эффективности контроля ЦВМ и увеличение быстродействия. Изобретение основано на использовании сигналов с выходов схем сравнения адреса и данных для организации считывания заранее записанных в оперативную память устройства новых значений адреса и данных и перезаписи их соответственно в регистры адреса и данных, подключенных к соответствующим схемам сравнения, к которым также подключены соответственно регистры адреса и данных, принимающие информацию из интерфейса контролируемой ЦВМ. Для этого в устройство для контроля ЦВМ, содержащее блок оперативной памяти, три коммутатора, регистр управления, пять регистров, счетчик, пять схем И, три триггера, распределитель импульсов, две схемы ИЛИ, генератор, введены коммутатор, счетчик, три схемы сравнения, пять схем ИЛИ, восемь схем И с соответствующими связями. 7 ил.

ма 28 сравнения вьщает сигнал через схему И 46 на выход 45 устройства, по которому управляющая ЦВМ по прерыванию может в регистр 12 управления записать код, при котором с его выхода вьщается сигнал, который через схемы И 47 и ИЛИ 49 поступает на вход схемы И 30 как разрешающий.

записанного в счетчик 36 из управляющей ЦВМ.

В режиме считывания информации из блока 10 оперативной памяти в регистр- 12 управления записывается код, который на выходах формирует сигналы, устанавливающие в блоке 10 оперативной памяти режим считывания, и сигнал

915

выборки соответственно, затем из управляющей ЦВМ в счетчик 36 записывается адрес ячейки, по которому с выхода блока 10 оперативной памяти через выход 38 устройства управляющая ЦВМ списывает информацию,

В режиме сравнения информации с заранее записанной в блок 10 оперативной памяти в исходном состоянии из управляющей ЦВМ в регистры 21-23 записывается информация.

В регистр 12 управления записываются код, формирующий на выходе регистра сигнал, устанавливающий блок 10 оперативной памяти в режим считывания, сигнал, разрешающий прохождение сигналов с выходов распределителя 34 через схемы И 16-18 управляющих записью информации соответственно в регистры 21-23 из блока 10 оперативной памяти. В счетчики 36 и 41 записываются исходные данные, Затем запускается процесс в проверяемой ЦВМ, запускается генератор 42 тактовых импульсов. Если произойдет совпадение кодов в регистрах 4 и 5 с кодами регистров 21 и 22. то сигнал сравнения с выходов схем 25 тл 26 сравнения через схему И 24 поступает на вход схемы ИЛИ 44, затем через схему И 50 на распределитель 34, кроме зтого, сигнал с выхода схемы И 24 переводит триггер 27 в единичное состояние.

С выходов распределителя 34 через схему ИЛИ 35 последовательность им- .пульсов образует последовательность адресов на счетчике 36, в соответствии с которыми в блоке 10 оперативной памяти из ячеек считывается ин- .формация. Кроме того, эта же последовательность импульсов организует перезапись информации из оперативной памяти в регистры 21-23. В исходном состоянии в счетчике 36 код установлен, в соответствии с этим адресом на выходе оперативной памяти находится код, который через второй ка- нальный вход коммутатора 20 передается на его выход. Первый импульс с выхода распределителя 34 через схемы И 16 и ИЛИ .13 производит запись информации с выхода коммутатора 20 в регистр 21 и задним фронтом устанавливает адрес следующей ячейки в счет чике 36. Второй импульс переписывает информацию в регистр 22, третий - изменяет только адрес, эта ячейка не

0

5

0

5

908

0

5

0

5

10

используется в данном режиме четвертый импульс переписывает информацию в регистр 23 и подготавливает счетчик 36.

Если сравнение содержимого регистров 5, 6 с содержимьм регистров 21, 22 не произойдет до момента сравнения содержимого регистра 23, где записано граничное время с содержимым счетчика 41, то сигнал с выхода схемы 28 сравнения поступит на вход схемы И 46. Цоскольку в этом случае сигнал с выхода схемы И 24 на единичньм вход триггера 27 не поступил, то он находится в исходном состоянии, в которое был установлен сигналом записи информации в регистр 23 через схему ИЛИ 51.

Таким образом, с инверсного выхода триггера 27 выдается разрешение на схему И 46, и сигнал схемы 28 сравнения проходит на выход 45 устройства и может быть использован для организации останова в проверяемой ЦВМ и подключения программ в управляющей ЦВМ для анализа неисправности. В этом режиме триггер 6 к проверяемой ЦВМ не подключается. Отсутствие сигналов на выходе триггера 6 формирует сигнал запрета на схемы И 30 и сигнал разрешения на входы схемы И 31. В регистре 12 управления устанавливается код, формирующий на выходе сигнал запрета на вход схемы И 31, , сигнал разрещения на вход схемы И 51 для организации установки триггера / 33 в исходное состояние при отсутствии сигнала сравнения с выхода схемы И 24, на выходе регистра 12 - сигнал .запрета на вход схемы И 43. Кроме то-- го, перед пуском процесса в проверяемой ЦВМ в регистре 12 управления необходимо установить код,- формирующий на выходе сигнал подключения к выходу коммутатора 20 его второго канального входа.

При переполнении счетчика 36 с его выхода через выход 55 устройства вьщается сигнал, который можно ис- по.льзовать для организации прерывания в управляющей ЦВМ или останова в проверяемой ЦВМ.

Формула изобретения

Устройство для контроля ЦВМ, содержащее блок оперативной памяти, первый, второй и третий коммутаторы,

входные регистры адреса и команд, триггер управления, регистр адреса, регистр данных, регистр времени,счетчик времени, два триггера, распределитель импульсов, пять элементов И, два элемениа ИЛИ, генератор тактовых импульсов, регистр управления, выход первого разряда которого соединен с управляющими входами первого и вто- рого коммутаторов, выход второго разряда регистра управления соединен с первым входом первого элемента ИЛИ, выход третьего разряда регистра управления соединен с первым входом первого элемента И, выход четвертого разряда регистра управления соединен с входом записи блока оперативной памяти, информационный- вход регистра управления является входом управления устройства для подключения к системной шине управляющей ЦВМ, выходы входных регистров адреса и команд соединены с первыми информационными входами соответственно первого и второго коммутаторов, первый и второй выходы распределителя импульсов соединены соответственно с первым входом второго элемента И, с первым входом третьего элемента И, первый информа- ционный вход третьего коммутатора является информационным входом устройства для подключения и системной шине управляющей ЦВМ, выход пятого разряда регистра управления соединен с управляющим входом третьего коммутатора, выход которого соединен с информационным входом регистра адреса, отличающееся тем, что, с целью повышения эффективности контро- ля и повышения быстродействия, оно содержит счетчик адреса, три схемы- сравнения, пять элементов ИЛИ, восемь элементов И, элемент задержки и четвертый коммутатор, причем выход бло- ка оперативной памяти соединен с вторым информационным входом третьего коммутатора и является информационным выходом устройства для подключения к системной шине управляющей ЦВМ, выход третьего коммутатора соединен с информационными входами регистров данных и времени, входы записи регистров адреса, данных и времени соеди- нены с выходами соответственно первого, второго и третьего элементов ИЛИ, выходы регистров адреса данных и времени соединены с первьми входами соответственно первой, второй и треть

JQ 15 20 25ЗОQ35

0

5

ей схем сравнения, вторые входы первой и второй схем сравнения соединены с выходами соответствено входного регистра адреса и входного регистра команд, информационные входы которых являются соответственно входом адреса и входом команд устройства для подключения и соответствующим выходом контролируемой ЦВМ, выходы регистров адреса и данных соединены с вторыми информационными входами соответственно первого и второго коммутаторов, выход счетчика времени соединен с вторым входом третьей схемы сравнения и с первым информационным входом четвертого коммутатора, информационный вход счетчика времени является входом начального времени устройства для подключения к системной шине управляющей ЦВМ, счетный вход счетчика времени соединен с выходом четвертого элемента И, выходы первого и второго коммутаторов соединены соответственно с вторым и третьим информационными входами четвертого коммутатора, выходы шестого и седьмого разрядов регистра управления соединены с первыми входами соответственно второго и третьего элементов ИЛИ, вторые входы первого, второго и третьего элементов РШИ соединены с выходами соответственно первого, третьего и второго элементов И, вторые входы второго и третьего элементов И соединены с выходом третьего разряда регистра управления, выход восьмого разряда регистра управления соединен с первым входом четвертого элемента И, выход,,, генератора тактовых импульсов соединен; с вторым входом четвертого элемента И ис первыми входами пятого и шестого элементов И, вход пуска генератора тактовых импульсов является входом пуска устройства для подключения к системной шине управляющей ЦВМ, выход, триггера управления соединен с четвертым информационным входом четвертого коммутатора, вторым входом пятого элемента И и первым входом седьмого элемента И, выход четвертого коммутатора соединен с информационным входом блока оперативной памяти, S-вход триггера управления является входом идентификации информации устройства для подключения к соответствующему выходу контролируемой ЦВМ, выходы с первого по четвертый распределители импульсов и выход девятого разряда регистра управления соединены с входами четвертого элемента ИЛИ, выход которого соединен с счетным входом счечика адреса и входом синхронизации блока оперативной памяти, адресньй вход которого соединен с информационный выходом счетчика адреса, информационный вход и выход переполнения которого является соответственно входом кода начального адреса устройства для подключения к системной шине управляющей ЦВМ и первым выходом останова устройства, выходы с первого по четвертый распределителя импульсов соединены с группой управляющих входов четвертого коммутатора, первый и третий выходы распределителя импульсов соединены соответственно с R-входом триггера управления и вторым входом первого элемента И, выход третьего элемента ИЛИ соединен с первым входом пятого элемента ИЛИ, второй вход которого соединен с выходом десятого разряда регистра управления, первый и второй входы восьмого элемента И соединены соответственно с выходами первой и второй схем сравнения, первый вход девятого элемента И соединен с выходом одиннадцатого разряда регистра управления, первый, второй и третий входы шестого элемента ИЛИ соединены соответственно с выходами седьмого и девятого элементов И и выходом двенадцатого разряда регистра управления, выход тринадцатого разряда которого соединен с вторым входом седьмого элемента И, выход пятого элемента ИЛИ соединен с R-входом

0

0

5

0

5

0

первого триггера, S-вход которого, первый вход седьмого элемента ИЛИ и второй вход девятого элемента И соединены с выходом восьмого элемента И, выход второго триггера соединен с первым входом десятого элемента И, второй вход которого соединен с выходом седьмого элемента ИЛИ, второй и третий входы которого соединены с выходами соответственно пятого и шестого элементов И, выход девятого элемента И соединен с входом распределителя импульсов и через элемент задержки с S-входом второго триггера, R- вход которого соединен с выходом шестого эх емента ИЛИ с первыми входами одиннадцатого и двенадцатого элементов И, выход четырнадцатого разряда регистра управления соединен с вторым входом шестого элемента И. выход пятнадцатого разряда регистра управления соединен -: с первым входом тринадцатого элемента И, второй вход которого соединен с прямым выходом первого триггера, выходы двенадцатого и тринадцатого элемента И соединены соответственно с первь1м и вторым входами восьмого элемента ИЛИ, выход которого соединен с третьим входом пятого .элемента И и является вторым вькЪдом останова устройства, выход третьей схемы сравнения соединен с вторым входом одиннадцатого элеиента И, выход которого яаляется третьим выходом останова устройства, выход шестнадцатого разряда регистра управления соединен с вторым входом двенадцатого элемента И.

Ы 55

о-ЛГбО

л

г-I

Г

j боНбг |5Г № S3 Ш 53 U. -1 i-11-11

г-I

Г

S3 Ш 53 i-11-1

Фиг.З

ФиеЛ

| Устройство для отладки программ | 1986 |

|

SU1363221A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для отладки программ | 1984 |

|

SU1166122A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1989-09-23—Публикация

1987-04-13—Подача