Изобретение относится к области вычислительной техники и может быть использовано для сопряжения специализированных ЦВМ с универсальными, серийно выпускаемыми ЭВМ.

Известно устройство для обмену информацией между электронными вычислитель- ными машинами 1, содержащее дешифратор адреса, блок обработки запросов, таймер, коммутатор запросов приема, триггер прерывания, группы элементов И выходного коммутатора информации, группу элементов И, группу элементов И-ИЛИ входного коммутатора информации, усилитель-приемник блока передающих усилителей и соответствующие связи.

Недостатком устройства являются большие временные затраты на установление связи между ЭВМ, большие аппаратные затраты, сложный алгоритм обмена.

Наиболее близким из известных к предложенному является устройство для сопряжения двух электронных вычислительных машин 2, содержащее блок канальных приемопередатчиков (первый и второй магистральные элементы), дешифратор адреса, блок дешифрации управляющих сигналов ЭВМ1 (селектор адреса), блок шифрации сигналов интерфейса ЭВМ2, регистр состояния, мультиплексор (коммутатор шины), блок контроля четности, блок прерывания, блок связи.

Недостатком устройства является большое время обмена между ЦВМ, большие затраты оборудования, сложная процедура обмена. Это связано с тем, что процедурой обмена в значительной степени занимается, кроме устройства, и одна из ЦВМ. То есть устройство перекладывает функции ввода-вывода информации из АЛУ одной из ЦВМ на эту ЦВМ, что приводит с одной стороны к потере производительности ЦВМ, с другой стороны к увеличению времени обмена, появлению дополнительных блоvj00 Јь О О

о

ков в устройстве, усложнению программирования обмена.

Целью изобретения является сокращение времени обмена информацией и сокращение аппаратных затрат устройства.

Поставленная цель достигается тем, что в устройство для обмена информацией между ЭВМ, содержащее селектор адреса, информационный вхйд которого подключен к выхЪду первого магистрального усилителя, коммутатор шины, выход которого соединен стинформационным входом второго магистрального усилителя, причем выход второго и вход первого магистральных усилителей образуют вход-выход устройства для подключения к информационному входу-выходу первой ЭВМ, группа управляющих входов и выходов ответа селектора адреса является соответственно группой входов и выходов устройства для подключе- ния к группе управляющих шин к выходу ответа первой ЭВМ, введены блок синхронизации, арифметико-логический узел, счетчик адреса, коммутатор микроопераций, коммутатор адреса, триггер формиро- вания синхросигнала, триггер ответа, триггер пуска, первый элемент И-ИЛИ-НЕ, второй элемент И-ИЛИ-НЕ, первый элемент И, первый элемент И-НЕ, второй элемент

И-НЕ, второй элемент И, третий элемент И, первый элемент ИЛИ-НЕ, второй элемент ИЛИ-НЕ, третий элемент ИЛИ-НЕ, четвертый элемент ИЛИ-НЕ, пятый элемент ИЛИ- НЕ, шестой элемент ИЛИ-НЕ. элемент ИЛИ, четвертый элемент И, пятый элемент И, при- чем первый выход выборки селектора адреса соединен с первым входом первого элемента ИЛИ-НЕ, второй вход которого соединен с первым входом второго элемента ИЛИ-НЕ, и выходом ЗАПИСЬ селектора адреса, второй выход выборки которого соединен с первым входом первого элемента И и вторым входом второго элемента ИЛИ- НЕ, выход которого соединён с первым входом элемента ИЛИ, второй вход которого соединен с первым входом третьего элемента ИЛИ-НЕ, с первым входом управления коммутатора шины и с выходом четвертого элемента ИЛИ-НЕ, первый вход которого соединен с первым входом второго элемен- та И и с третьим выходом выборки селектора адреса, выход ЧТЕНИЕ которого соединен со вторым входом четвертого элемента ИЛИ-НЕ, вход ответа селектора адреса соединен с выходом пятого элемента ИЛИ-НЕ, первый вход которого соединен с первым входом, шестого элемента ИЛИ-НЕ и прямым выходом триггера ответа, инверсный выход которого соединен со входом +1 счетчика адреса и с первым входом

первого элемента И-НЕ, второй вход которого соединен со входом сброса триггера ответа, первым входом первого элемента И-ИЛИ-НЕ, выходом элемента ИЛИ, первым входом второго элемента И-НЕ и первым входом третьего элемента И, второй вход которого соединен с синхровходом триггера ответа и инверсным выходом триггера формирования синхросигнала, синх- ровход и информационный вход которого соединены соответственно с выходом первого элемента И-НЕ и выходом третьего элемента И, прямой выход триггера формирования синхросигнала соединен с первым входом второго элемента И-ИЛИ-НЕ, второй вход которого соединен с первыми входами четвертого и пятого элементов И и выходом второго элемента И-НЕ, второй вход которого соединен с третьим входом третьего элемента И, выходом ПРИЗНАК РАБОТЫ блока синхронизации, вторыми входами первого и второго элементов И и входом управления коммутатора адресов, информационный вход которого соединен с выходом счетчика адреса, управляющий вход которого соединен со вторым входом пятого элемента ИЛИ-НЕ и выходом первого элемента ИЛИ-НЕ, информационный вход счетчика адресу соединен с выходом первого магистрального элемента и первым информационным входом коммутатора шины, второй информационный вход которого соединен с входом арифметико-логического узла, вход управления которого соединен с выходом коммутатора микроопераций, тактирующий вход арифметико-логического узла Соединен с выходом второго элемента И-ИЛИ-НЕ, выход коммутатора адресов соединен с входом адресации арифметико-логического узла, информационный вход которого соединен с выходом коммутатора шины, вход управления второго магистрального элемента соединен с выходом третьего элемента ИЛИ-НЕ, второй и третий входы управления коммутатора шины соединены соответственно с выходами четвертого и пятого элементов И, выход шестого элемента ИЛИ-НЕ соединен с синхровходом триггера пуска, вход сброса которого соединен с выходом первого элемента И-ИЛИ-НЕ, второй вход которого соединен с выходом синхросигнала блока синхронизации, выход триггера пуска соединен со входом пуска блока синхронизации, информационные входы триггера ответа, триггеров пуска и группа режимных входов селектора адреса соединены с шиной логической единицы, третий вход второго элемента И-ИЛИ-НЕ, третий вход первого элемента И-ИЛИ-НЕ, соединенный с входами сброса блока синхронизации и триггера формирования синхросигнала, второй вход шестого элемента ИЛИ-НЕ и третий вход первого элемента И-НЕ, соединенный с тактовым входом блока синхронизации, являются соответст- вующими входами устройства для подключения к выходам синхронизации, сброса, пуска и тактов второй ЭВМ, выходы первого и второго элементов И соединены с группой адресных входов коммутатора микроопера- ций, вторые входы четвертого и пятого элементов И и первый информационный вход коммутато ра микроопераций образуют группу входов устройства для подключения к группе выходов микроопераций второй ЭВМ, второй вход третьего элемента ИЛИ- НЕ и третий-пятый информационные входы коммутатора шины являются соответствующими входом и группой входов устройства для подключения к выходу управления и группе информационных выходов второй ЭВМ, выход синхросигнала блока синхронизации и вход адреса коммутатора адресов являются соответствующими выходом и входом устройства для подключения к так- товому входу и выходу заданий поля адресов второй ЭВМ, второй и третий информационные входы коммутатора микроопераций образуют группу входов устройства для подключения к группе выходов задания кодов микроопераций записи и чтения устройства.

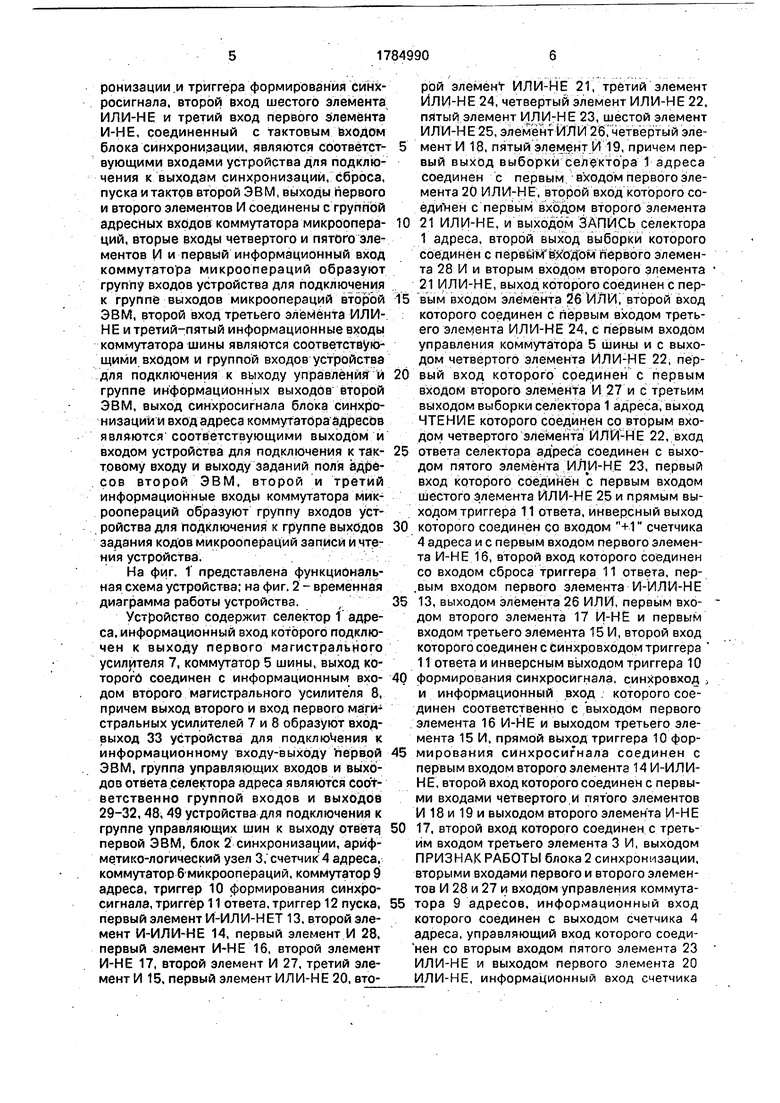

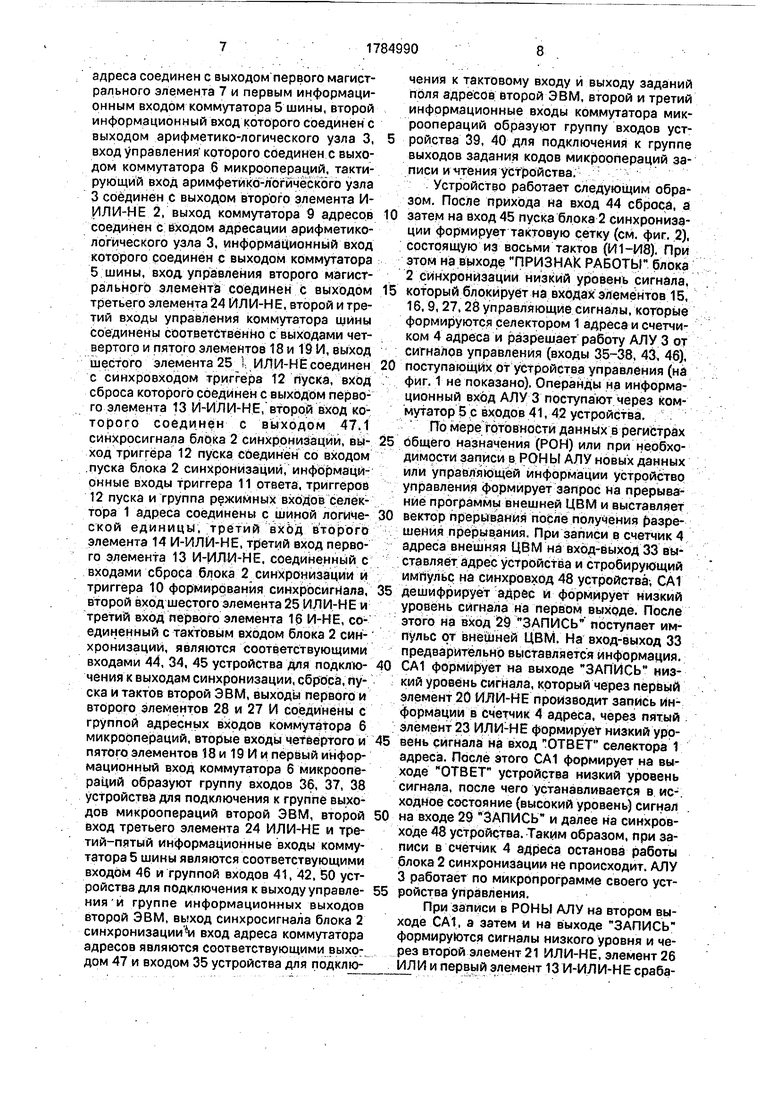

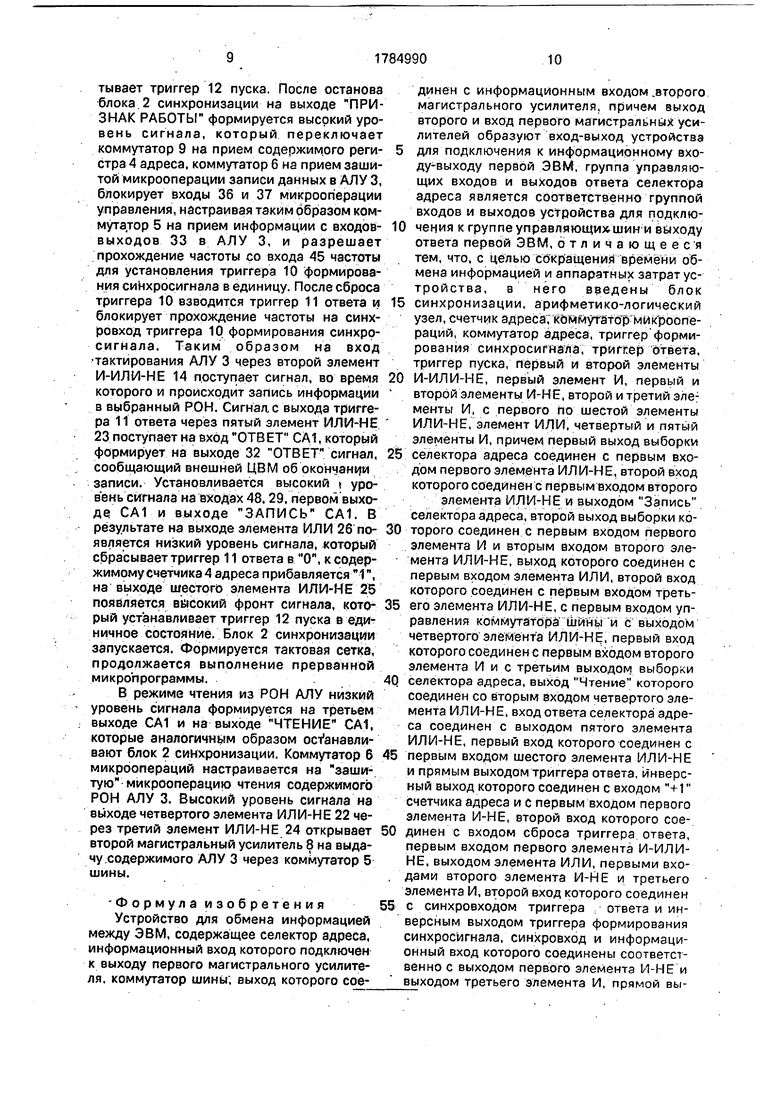

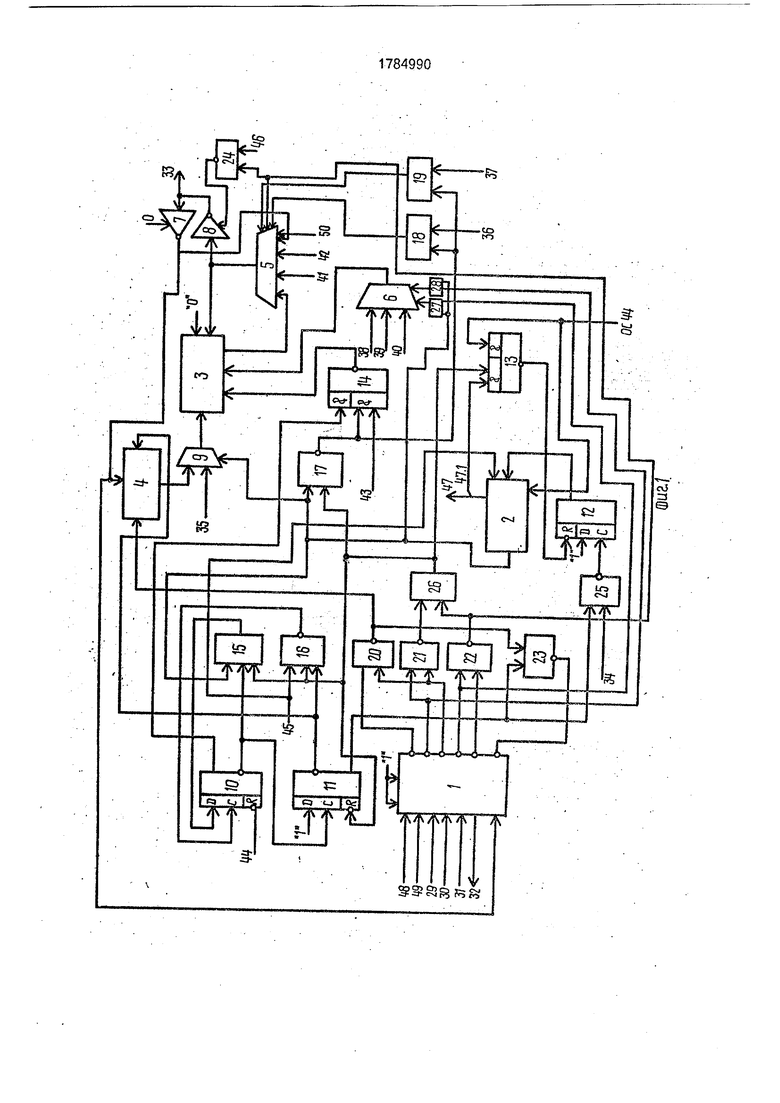

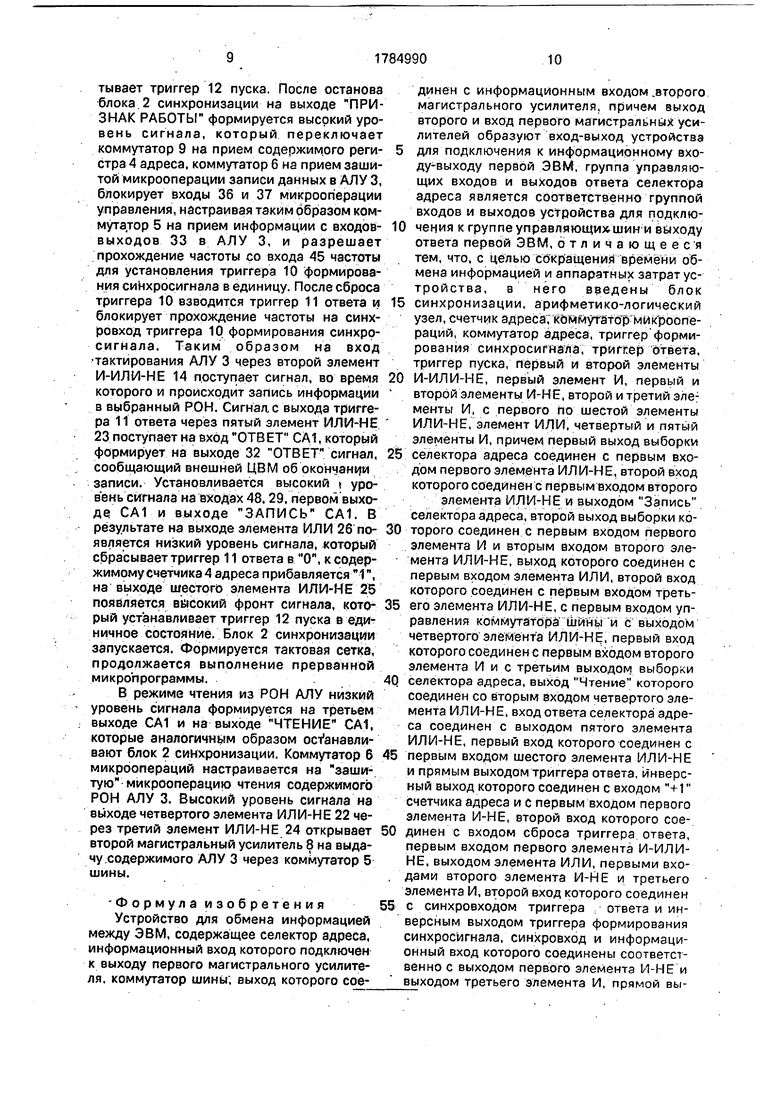

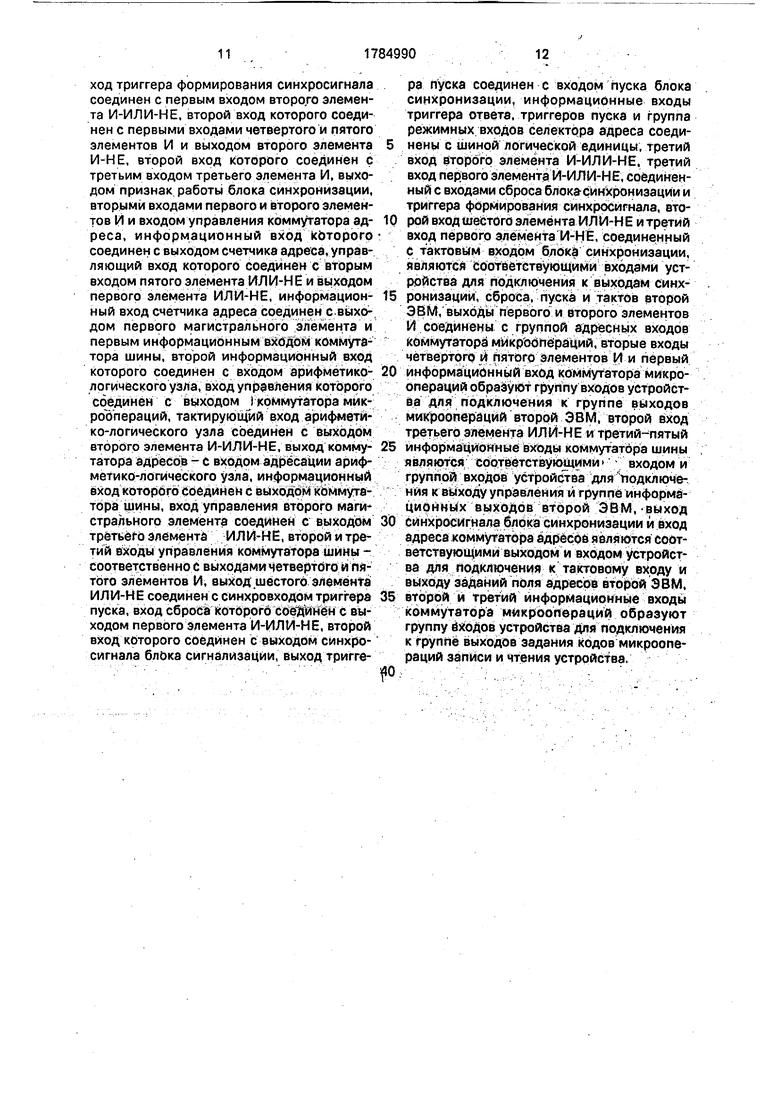

На фиг. 1 представлена функциональная схема устройства; на фиг. 2 - временная диаграмма работы устройства.,

Устройство содержит селектор 1 адреса, информационный вход которого подключен к выходу первого магистрального усилителя 7, коммутатор 5 шины% выход которого соединен с информационным вхо- дом второго магистрального усилителя 8, причем выход второго и вход первого маги-1 стральных усилителей 7 и 8 образуют вход- выход 33 устройства для подключения к информационному входу-выходу первой ЭВМ, группа управляющих входов и выходов ответа селектора адреса являются соответственно группой входов и выходов 29-32,48,49 устройства для подключения к группе управляющих шин к выходу ответа. первой ЭВМ, блок 2 синхронизации, арифметико-логический узел 3, счетчик 4 адреса, коммутатор 6 микроопера ций, коммутатор 9 адреса, триггер 10 формирования синхросигнала, триггер 11 ответа, триггер 12 пуска, первый элемент И-ИЛИ-НЕТ 13, второй элемент И-ИЛИ-НЕ 14, первый элемент И 28, первый элемент И-НЕ 16, второй элемент И-НЕ 17, второй элемент И 27, третий элемент И 15, первый элемент ИЛИ-НЕ 20, второй элемент ИЛИ-НЕ 21, третий элемент ЙЛИ-НЕ 24, четвертый элемент ИЛИ-НЕ 22, пятый элемент ИЛИ-НЕ 23, шестой элемент ИЛИ-НЕ 25, элемент ИЛИ 26, четвертый элемент И 18, пятый элемент И 19, причем первый выход выборки селектора 1 адреса соединен с первым входом первого элемента 20 ИЛИ-НЕ, второй вход которого со- еди нен с первым входом второго элемента 21 ИЛИ-НЕ, и выходом ЗАПИСЬ селектора

Iадреса, второй выход выборки которого соединен с первыМШоДом первого элемента 28 И и вторым входом второго элемента 21 ИЛИ-НЕ, выход которого соединен с первым входом элемента 26 ИЛИ, второй вход которого соединен с первым входом третьего элемента ИЛИ-НЕ 24, с первым входом управления коммутатора 5 шины и с выходом четвертого элемента ИЛИ-НЕ 22, первый вход которого соединен с первым входом второго элемента И 27 и с третьим выходом выборки селектора 1 адреса, выход ЧТЕНИЕ которого соединен со вторым входом четвертого элемента ИЛИ-НЕ 22, вход ответа селектора адреса соединен с выходом пятого элемента 23, первый вход которого соединен с первым входом шестого Элемента ЙЛИ-НЕ 25 и прямым выходом триггера 11 ответа, инверсный выход которого соединен со входом +1 счетчика 4 адреса и с первым входом первого элемента И-НЕ 16, второй вход которого соединен со входом сброса триггера 11 ответа, пер- .вым входом первого элемента И-ИЛИ-НЕ

13, выходом элемента 26 ИЛИ, первым входом второго элемента 17 И-НЕ и первым входом третьего элемента 15 И, второй вход которого соединен с синхровходом триггера

I1ответа и инверсным выходом триггера 10 формирования синхросигнала, синхровход , и информационный вход которого соединен соответственно с выходом первого элемента 16 И-НЕ и выходом третьего элемента 15 И, прямой выход триггера 10 формирования синхросигнала соединен с первым входом второго элемента 14 И-ИЛИ- НЕ, второй вход которого соединен с первыми входами четвертого и пятого элементов И 18 и 19 и выходом второго элемента И-НЕ 17, второй вход которого соединен с третьим входом третьего элемента 3 И, выходом ПРИЗНАК РАБОТЫ блока 2 синхронизации, вторыми входами первого и второго элементов И 28 и 27 и входом управления коммутатора 9 адресов, информационный вход которого соединен с выходом счетчика 4 адреса, управляющий вход которого соеди- нен со вторым входом пятого элемента 23 ИЛИ-НЕ и выходом первого элемента 20 ИЛИ-НЕ, информационный вход счетчика

адреса соединен с выходом первого магистрального элемента 7 и первым информационным входом коммутатора 5 шины, второй информационный вход которого соединен с выходом арифметико-логического узла 3, вход управления которого соединен с выходом коммутатора 6 микроопераций, тактирующий вход аримфетико-логического узла 3 соединен с выходом второго элемента И- ИЛИ-НЕ 2, выход коммутатора 9 адресов соединен с входом адресации арифметико- логического узла 3, информационный вход которого соединен с выходом коммутатора 5 шины, вход управления второго магистрального элемента соединен с выходом третьего элемента 24 ИЛИ-НЕ, второй и третий входы управления коммутатора шины соединены соответственно с выходами четвертого и пятого элементов 18 и 19 И, выход шестого элемента 25 I ИЛИ-НЕ соединен с синхровходом триггера 12 пуска, вход сброса которого соединен с выходом первого элемента 13 И-ИЛИ-НЕ, второй вход которого соединен с выходом 47.1 синхросигнала блока 2 синхронизации, вы- ход триггера 12 пуска соединен со входом пуска блока 2 синхронизации, информационные входы триггера 11 ответа, триггеров 12 пуска и группа режимных входов селектора 1 адреса соединены с шиной логиче- ской единицы, третий вход второго элемента 14 И-ИЛИ-НЕ, третий вход первого элемента 13 И-ИЛИ-НЕ. соединенный с входами сброса блока 2 синхронизации и триггера 10 формирования синхросигнала, второй вход шестого элемента 25 ИЛИ-НЕ и третий вход первого элемента 16 И-НЕ, соединенный с тактовым входом блока 2 синхронизации, являются соответствующими входами 44, 34, 45 устройства для подклю- чения к выходам синхронизации, сброса, пуска и тактов второй ЭВМ, выходы первого и второго элементов 28 и 27 И соединены с группой адресных входов коммутатора 6 микроопераций, вторые входы четвертого и пятого элементов 18 и 19 И и первый информационный вход коммутатора б микроопераций образуют группу входов 36, 37, 38 устройства для подключения к группе выходов микроопераций второй ЭВМ, второй вход третьего элемента 24 ИЛИ-НЕ и тре- тий-пятый информационные входы коммутатора 5 шины являются соответствующими входом 46 и группой входов 41, 42, 50 устройства для подключения к выходу управле- ния и группе информационных выходов второй ЭВМ, выход синхросигнала блока 2 синхронизации и вход адреса коммутатора адресов являются соответствующими выходом 47 и входом 35 устройства для подключения к тактовому входу и выходу заданий поля адресов второй ЭВМ, второй и третий информационные входы коммутатора микроопераций образуют группу входов устройства 39, 40 для подключения к группе выходов задания кодов микроопераций записи и чтения устройства.

Устройство работает следующим образом. После прихода на вход 44 сброса, а затем на вход 45 пуска блока 2 синхронизации формирует тактовую сетку (см. фиг. 2). состоящую из восьми тактов (И1-И8). При этом на выходе ПРИЗНАК РАБОТЫ блока

2синхронизации низкий уровень сигнала, который блокирует на входах элементов 15, 16,9,27,28 управляющие сигналы, которые формируются селектором 1 адреса и счетчиком 4 адреса и разрешает работу АЛУ 3 от сигналов управления (входы 35-38, 43, 46), поступающих от устройства управления (на фиг. 1 не показано). Операнды на информационный вход АЛУ 3 поступают через коммутатор 5 с входов 41, 42 устройства.

По мере готовности данных в регистрах общего назначения (РОН) или при необходимости записи в РОНЫ АЛУ новых данных или управляющей информации устройство управления формирует запрос на прерывание программы внешней ЦВМ и выставляет вектор прерывания после получения разрешения прерывания. При записи в счетчик 4 адреса внешняя ЦВМ на вход-выход 33 выставляет адрес устройства и стробирующий импульс на синхровход 48 устройства, СА1 дешифрирует адрес и формирует низкий уровень сигнала на первом выходе. После этого на вход 29 ЗАПИСЬ поступает импульс от внешней ЦВМ. На вход-выход 33 предварительно выставляется информация. СА1 формирует на выходе ЗАПИСЬ низкий уровень сигнала, который через первый элемент 20 ИЛИ-НЕ производит запись информации в счетчик 4 адреса, через пятый элемент 23 ИЛИ-НЕ формирует низкий уровень сигнала на вход ОТВЕТ селектора 1 адреса. После этого СА1 формирует на выходе ОТВЕТ устройства низкий уровень сигнала, после чего устанавливается в исходное состояние (высокий уровень) сигнал на входе 29 ЗАПИСЬ и далее на синхров- ходе 48 устройства. Таким образом, при записи в счетчик 4 адреса останова работы блока 2 синхронизации не происходит. АЛУ

3работает по микропрограмме своего устройства управления.

При записи в РОНЫ АЛУ на втором выходе СА1, а затем и на выходе ЗАПИСЬ формируются сигналы низкого уровня и через второй элемент 21 ИЛИ-НЕ, элемент 26 ИЛ И и первый элемент 13 И-ИЛИ-НЕ срабатывает триггер 12 пуска. После останова блока 2 синхронизации на выходе ПРИЗНАК РАБОТЫ формируется высокий уровень сигнала, который переключает коммутатор 9 на прием содержимого реги- стра 4 адреса, коммутатор 6 на прием зашитой микрооперации записи данных в АЛУ 3, блокирует входы 36 и 37 микрооперации управления, настраивая таким образом коммутатор 5 на прием информации с входов- выходов 33 в АЛУ 3, и разрешает прохождение частоты со входа 45 частоты для установления триггера 10 формирования синхросигнала в единицу. После сброса триггера 10 взводится триггер 11 ответа и блокирует прохождение частоты на синх- ровход триггера 10 формирования синхросигнала. Таким образом на вход тактирования АЛУ 3 через второй элемент И-ИЛИ-НЕ 14 поступает сигнал, во время которого и происходит запись информации в выбранный РОН. Сигнадс выхода триггера 11 ответа через пятый элемент ИЛИ-НЁ 23 поступает на вход ОТВЕТ СА1, который формирует на выходе 32 ОТВЕТ сигнал, сообщающий внешней ЦВМ об окончании записи. Установливается высокий t уровень сигнала на входах 48,29, первом выходе СА1 и выходе ЗАПИСЬ СА1. В результате на выходе элемента ИЛИ 26 по- является низкий уровень сигнала, который сбрасывает триггер 11 ответа в 0й, к содержимому счетчика 4 адреса прибавляется 1, на выходе шестого элемента ИЛИ-НЕ 25 появляется высокий фронт сигнала, кото- рый устанавливает триггер 12 пуска в единичное состояние. Блок 2 синхронизации запускается. Формируется тактовая сетка, продолжается выполнение прерванной микропрограммы.

В режиме чтения из РОН АЛУ низкий уровень сигнала формируется на третьем выходе СА1 и на выходе ЧТЕНИЕ СА1, которые аналогичным образом останавливают блок 2 синхронизации. Коммутатор 6 микроопераций настраивается на зашитую микрооперацию чтения содержимого РОН АЛУ 3. Высокий уровень сигнала на выходе четвертого элемента ИЛИ-НЕ 22 через третий элемент ИЛИ-НЕ 24 открывает второй магистральный усилитель 8 на выдачу содержимого АЛУ 3 через коммутатор 5 шины.

-Формулаизобретения

Устройство для обмена информацией между ЭВМ, содержащее селектор адреса, информационный вход которого подключен к выходу первого магистрального усилителя, коммутатор шины, выход которого соединен с информационным входом .второго магистрального усилителя, причем выход второго и вход первого магистральных усилителей образуют вход-выход устройства для подключения к информационному входу-выходу первой ЭВМ, группа управляющих входов и выходов ответа селектора адреса является соответственно группой входов и выходов устройства для подключения к группе управляющих- шин и выходу ответа первой ЭВМ, отличающееся тем, что, с целью сокращения времени обмена информацией и аппаратных затрат устройства, в него введены блок синхронизации, арифметико-логический узел, счетчик адреса, коммутатор микроопераций, коммутатор адреса, триггер формирования синхросигнала, триггер ответа, триггер пуска, первый и второй элементы И-ИЛИ-НЕ, первый элемент И, первый и второй элементы И-НЕ, второй и третий элементы И, с первого по шестой элементы ИЛИ-НЕ, элемент ИЛИ, четвертый и пятый элементы И, причем первый выход выборки селектора адреса соединен с первым входом первого элемента ИЛИ-НЕ, второй вход которого соединен с первым входом второго элемента ИЛИ-НЕ и выходом Запись селектора адреса, второй выход выборки которого соединен с первым входом первого элемента И и вторым входом второго элемента ИЛИ-НЕ, выход которого соединен с первым входом элемента ИЛИ, второй вход которого соединен с первым входом третьего элемента ИЛИ-НЕ, с первым входом управления коммутатора шины и с выходом четвертого элемента ИЛИ-НЕ, первый вход которого соединен с первым входом второго элемента И и с третьим выходом выбора селектора адреса, выход Чтение которого соединен со вторым входом четвертого элемента ИЛИ-НЕ, вход ответа селектора адреса соединен с выходом пятого элемента ИЛИ-НЕ, первый вход которого соединен с первым входом шестого элемента ИЛИ-НЕ и прямым выходом триггера ответа, инверсный выход которого соединен с входом +1 счетчика адреса и с первым входом первого элемента И-НЕ, второй вход которого соединен с входом сброса триггера ответа, первым входом первого элемента И-ИЛИ- НЕ, выходом элемента ИЛИ, первыми входами второго элемента И-НЕ и третьего элемента И, второй вход которого соединен с синхровходом триггера ответа и инверсным выходом триггера формирования синхросигнала, синхровход и информационный вход которого соединены соответственно с выходом первого элемента И-НЕ и выходом третьего элемента И, прямой выход триггера формирования синхросигнала соединен с первым входом второго элемента И-ИЛИ-НЕ, второй вход которого соединен с первыми входами четвертого и пятого элементов И и выходом второго элемента И-НЕ, второй вход которого соединен с третьим входом третьего элемента И, выходом признак работы блока синхронизации, вторыми входами первого и второго элементов И и входом управления коммутатора адреса, информационный вход которого соединен с выходом счетчика адреса, управляющий вход которого соединен с вторым входом пятого элемента ИЛ И-НЕ и выходом первого элемента ИЛИ-НЕ, информационный вход счетчика адреса соединен с выходом первого магистрального элемента и первым информационным входом коммутатора шины, второй информационный вход которого соединен с входом арифметико- логического узла, вход управления которого соединен с выходом I коммутатора микроопераций, тактирующий вход арифметико-логического узла соединен с выходом второго элемента И-ИЛИ-ЙЕ, выход коммутатора адресов - с входом адресации арифметико-логического узла, информационный вход которого соединен с выходом коммутатора шины, вход управления второго маги стрального элемента соединен с выходом третьего элемента ИЛИ-НЁ, второй и третий входы управления коммутатора шины - соответственно с выходами четвертого и пятого элементов И, выход шестого элемента ИЛИ-НЕ соединен с синхровходом триггера пуска, вход сброса которого соединен с выходом первого элемента И-ИЛИ-НЕ, второй вход которого соединен с выходом синхросигнала блика сигнализации, выход триггера пуска соединен с входом пуска блока синхронизации, информационные входы триггера ответа, триггеров пуска и группа режимных входов селектора адреса соединены с шиной логической единицы, третий вход второго элемента И-ИЛИ-НЕ. третий вход первого элемента И-ИЛИ-НЕ, соединенный с входами сброса блока-синхронизации и триггера формирования синхросигнала, второй вход шестого элемента ИЛ И-Н Е и третий вход первого элемента И-НЕ, соединенный С тактовым входом блока синхронизации, являются соответствующими входами устройства для подключения к выходам синхронизации, сброса, пуска и тактов второй ЭВМ, выходы первого и второго элементов И соединены с группой адресных входов коммутатора микроопераций, вторые входы четвертого и пятого элементов И и первый

информационный вход коммутатора микроопераций образуют группу входов устройства для подключения к группе выходов микроопераций второй ЭВМ, второй вход третьего элемента ИЛИ-НЕ и третий-пятый

информационные входы коммутатора шины являются соответствующими) - входом и группой входов устройства для подключения к выходу управления и группе информационных выходов второй ЭВМ,-выход

синхросигнала блока синхронизации и вход адреса коммутатора адресов являются соответствующими выходом и входом устройства для подключения к тактовому входу и выходу заданий поля адресов второй ЭВМ,

второй и третий информационные входы коммутатора микроопераций образуют группу ёходов устройства для подключения к группе выходов задания кодов микроопераций записи и чтения устройства.

SJ Sk&SrSsS1

1У If

I

45

M

I

rtii ii

1

Ј

I

| название | год | авторы | номер документа |

|---|---|---|---|

| Трехканальная мажоритарно-резервированная система | 1981 |

|

SU1104696A1 |

| Устройство для сопряжения ЭВМ с магистралью | 1988 |

|

SU1605242A1 |

| Устройство для сопряжения ЭВМ с внешними устройствами | 1987 |

|

SU1501077A1 |

| Устройство для сопряжения с микроЭВМ | 1986 |

|

SU1709322A1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЭВМ С КАНАЛОМ СВЯЗИ | 1992 |

|

RU2043652C1 |

| Устройство для имитации неисправностей | 1987 |

|

SU1444775A1 |

| Микропрограммируемый векторный процессор | 1987 |

|

SU1594557A1 |

| Устройство для сопряжения периферийного устройства с ЭВМ | 1988 |

|

SU1596339A1 |

| Устройство для сопряжения ЭВМ с общей магистралью | 1987 |

|

SU1456963A1 |

| Микропрограммное устройство для управления и обмена данными | 1983 |

|

SU1129601A1 |

Изобретение относится к вычислительной технике и может быть использовано для сопряжения специализированных ЭВМ с универсальными ЭВМ. Цель изобретения - сокращение времени обмена информацией и сокращение аппаратных затрат устройства. Цель достигается тем, что в устройство, содержащее селектор адреса, коммутатор шины и два магистральных усилителя, введены триггер пуска, два элемента И-ИЛИ- НЕ, шесть элементов ИЛИ-НЕ, пять элементов И, блок синхронизации, арифметико-логическое устройство, счетчик адреса, коммутатор микроопераций, коммутатор адреса, триггер формирования синхросигнала, триггер ответа, два элемента И-НЕ и элемент ИЛИ. 2 ил.

| Устройство для обмена информацией между электронными вычислительными машинами | 1985 |

|

SU1262513A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для сопряжения двух электронных вычислительных машин | 1984 |

|

SU1251093A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1992-12-30—Публикация

1990-02-26—Подача