Изобретение относится к области цифровой вычислительной техники, может, быть использовано для отработки и определения эффективности программно-аппаратных средств контроля и обеспечения надежности ЭВМ, а также для определения устойчивости к сбоям ЭВМ с.мажорированием и является усовершенствованием устройства по авт. св. № 1107126.

Целью изобретения является расширение функциональных возможностей за счет обеспечения раздельного поразря ного динамического моделирования переходных процессов при сбоях.

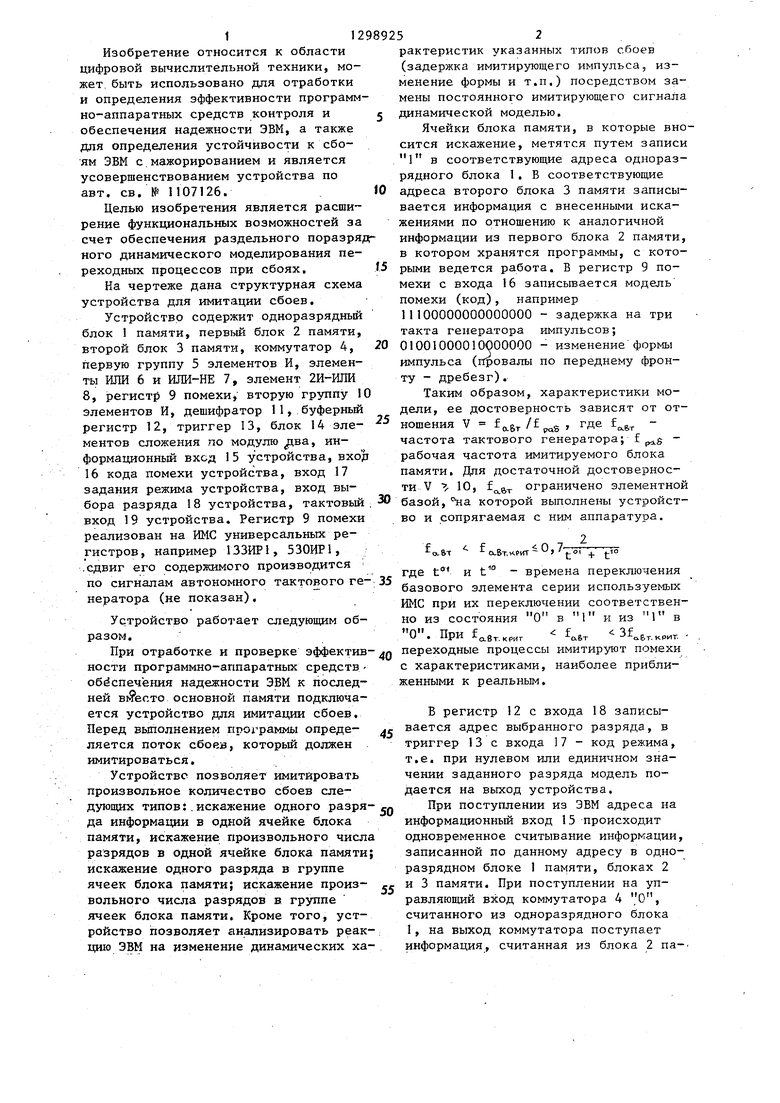

На чертеже дана структурная схема устройства для имитации сбоев.

Устройство содержит одноразрядньш блок 1 памяти, первый блок 2 памяти второй блок 3 памяти, коммутатор 4, первую группу 5 элементов И, элементы ИЛИ 6 и ИЛИ-НЕ 7, элемент 2И-ИЛИ 8, регистр 9 помехиj вторую группу элементов И, дешифратор 11, буферный регистр 12, триггер 13, блок 14 эле- ментов сложения по модулю два, информационный вход 15 устройства, вхо 16 кода помехи устройства, вход 17 задания режима устройства, вход выбора разряда 18 устройства, тактовый вход 19 устройства. Регистр 9 помехи реализован на ИМС универсальных регистров, например 133ИР1, 530ИР1, .сдвиг его содержимого производится по сигналам автономного тактового ге нератора (не показан).

Устройство работает следующим образом.

При отработке и проверке эффектив- лп переходные процессы имитируют помехи

45

40

ности программно-аппаратных средств обеспечения надежности ЭВМ к последней основной памяти подключается устройство для имитации сбоев. Перед вьшолнением программы определяется поток сбоев, который должен имитироваться.

Устройстве позволяет имитировать произвольное количество сбоев следующих типов.искажение одного разря- сп да информации в одной ячейке блока памяти, искажение произвольного числа разрядов в одной ячейке блока памяти; искажение одного ргшряда в группе

с характеристиками, женными к реальным.

наиболее приблиВ регистр 12 с входа 18 записывается адрес выбранного разряда, в триггер 13 с входа 17 - код режима, т.е. при нулевом или единичном значении заданного разряда модель подается на выход устройства.

При поступлении из ЭВМ адреса на информационный вход 15 происходит одновременное считывание информации, записанной по данному адресу в одноразрядном блоке 1 памяти, блоках 2

ячеек блока памяти; искажение произ- ее памяти. При поступлении на уп . U / 11 Т1

ВОЛЬНОГО числа разрядов в. группе ячеек блока памяти. Кроме того, устройство позволяет анализировать реак- цию ЭВМ на изменение динамических харавляющий вход коммутатора 4 , 0 считанного из одноразрядного блока 1, на выход коммутатора поступает информация, считанная из блока 2 п

0

Г5

ношения V 35

рактеристик указанных типов сбоев (задержка имитирующего импульса, изменение формы и т.п.) посредством замены постоянного имитирующего сигнала динамической моделью.

Ячейки блока памяти, в которые вносится искажение, метятся путем записи 1 в соответствующие адреса одноразрядного блока 1. В соответствующие адреса второго блока 3 памяти записывается информация с внесенными искажениями по отношению к аналогичной информации из первого блока 2 памяти, в котором хранятся программы, с которыми ведется работа. В регистр 9 помехи с входа 16 записьгоается модель помехи (код), например 11100000000000000 - задержка на три такта генератора импульсов; 01001000010000000 - изменение формы импульса (провалы по переднему фронту - дребезг).

Таким образом, характеристики модели, ее достоверность зависят от /f pcxS Я с.6т частота тактового генератора; f р. - рабочая частота имитируемого блока памяти. Для достаточной достоверности V 10, ограничено элементной 30 базой,°на которой выполнены устройство и сопрягаемая с ним аппаратура.

0

ношения V

,7

О-бТ Сх.Вт.РИТ f-OI ц. 4-1

где f и f - времена переключения базового элемента серии используемых ИМС при их переключении соответственИА „ 1 1 „ „„ л 1 I

в

При f

авт. Крит

f.

абт

3f.

чВт. критс характеристиками, женными к реальным.

наиболее прибли

В регистр 12 с входа 18 записывается адрес выбранного разряда, в триггер 13 с входа 17 - код режима, т.е. при нулевом или единичном значении заданного разряда модель подается на выход устройства.

При поступлении из ЭВМ адреса на информационный вход 15 происходит одновременное считывание информации, записанной по данному адресу в одноразрядном блоке 1 памяти, блоках 2

U / 11 Т1

равляющий вход коммутатора 4 , 0 считанного из одноразрядного блока 1, на выход коммутатора поступает информация, считанная из блока 2 памяти. Если на управляющий вход коммутатора 4 с выхода блока 1 поступает 1, то на выход коммутатора поступает информация из второго блока 3 памяти, в которую перед выпол- нением программы внесены искажения. Дешифратор 11 согласно кода регистра 12 открывает элемент И соответствующего разряда групп 5 и 10, при этом выделенный разряд устанавлива- ется в соответствии с содержимым блока 3 памяти, выходы остальных разрядов групп 5 и 10 установлены в состояние о. Если вьщеленный разряд содержит 1, сработает элемент ИЛИ 6, если О - сработает элеме 1т ИЛИ-НЕ 7. В соответствии с режимом, установленным на триггере 13, возбужден один из управляющих входов элемента 2И-ИЛИ. В .том случае, если на выходе коммутатора 4 формируется неискаженная информация, соответственно О - на управляющем входе коммутатора, этот О блокирует выходной сигнал элемента 8 и неискажен ная информация поступает на выход устройства (на выходе группы 10 код 000..0).

Если искажение информации опре- деленного слова предусмотрено и в соответствующий разряд блока 1 записана 1, то она поступает на входы элемента 2H-IinH 8, сигнал разрешения регистра 9 на выходе элемента 8 сформируется в том случае, если содержимое выбранного разряда и режим контроля совпадают. По сигналу запуска автономный тактовый генератор последовательно сдвигает содер- жимое регистра 9 помехи, которое за время опроса имитируемого блока памяти последовательно поступает на . входд 1 элементов И группы 10 и одновременно перезаписывается. Дешифра- тор 11 разрешает прохождение моделирующей импульсной последовательност в выбранном разряде, после чего она накладывается (только в случае совпадения значения выбранного разряда и режима) на искаженную информацию, мо делируя переходные процессы, помехи и т.п. В случае, если выбранный разряд равен нулю, характеристика имитируемого сбоя в точности СООТВетСТ-

вует коду регистра. 9. Если выбранный разряд равен 1, то характеристика сбоя инверсна. Эта особенность устройства позволяет анализировать анал

5

Q е п е

5

гичные процессы при различных значениях выбранного разряда без перезаписи содержимого регистра 9.

Искажения, введенные устройством имитации, должны быть обнаружены программно-аппаратурными средствами контроля ЭВМ. При имитации сбоев устройством определяются допустимые искажения сигналов в цепях передачи и обработки данных ЭВМ, во время выполнения программы отрабатывается реакция программно-аппаратных средств контроля и обеспечения надежности ЭВМ. При отработке мажорированных ЭВМ к каждому каналу резерва ЭВМ подключается свое устройство имитации сбоев и для каждого канала задается свой поток сбоев, их характедистики, которые должны имитироваться при выполнении программ, при этом устройства работают аналогично отработке программно-аппаратных средств контроля ЭВМ.

Таким образом обеспечивается возможность раздельного поразрядного моделирования переходных процессов при функционировании ЭВМ в реальном масштабе времени в соответствии с заданным типом сбоев,

Формула изобретения

Устройство для имитации сбоев по авт. св. № 1107126, отличающееся тем, что, с целью расширения функциональных возможностей за счет обеспечения раздельного поразрядного динамического моделирования переходных процессов при сбоях, устройство содержит регистр помехи, буферный регистр, триггер, дешифратор, блок элементов сложения по модулю два, первую и вторую группы элементов И, элементы ИЛИ, ИШ1-НЕ и 2И-ИЛИ, причем, выход второго блока памяти по- рязрядно соединен с первыми входами элементов И первой группы, выходы элементов И первой группы соединены с входами элементов ИЛИ и ИЛИ-НЕ, выход элемента Ш1И соединен с первым входом первой группы входом элемента 2И-Ш1И, выход элемента ИЛИ-НЕ соединен с первым входом второй группы входов элемента 2И-ИЛИ, выход одноразрядного блока памяти соединен с вторыми входами первой и второй групп входов элемента 2И-ИЛИ, третьи входы первой и второй групп входов которого соединены соответственно с прямым

и инверсным выходами триггера, инфор- .мационный вход которого является входом задания режима устройства, выход элемента 2И-ИЛИ сое;ц1нен с разрешающим входом регистра помех, первый информационный вход к оторого является входом кода помехи устройства, выход регистра помех соединен с вторым информационным входом регистра помех и с первыми входами элементов И второй группы, вторые входы элементов И первой и второй групп соединены с выхоРедактор Л.Гратилло

Составитель Д.Ванюхин

Техред М.Ходанич Корректор с.Черни

Заказ 899/60

Тираж 902Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д, 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

дами дешифратора, вход которого соединен с выходом буферного регистра, информационный вход которого является входом выбора разряда устройства, группа выходов коммутатора и выходы элементов И второй группы соединены соответственно с первой и второй группами информационных входов блока элемент Ов сложения по модулю два, выход которого является выходом устройства, вход сдвига регистра помех является тактовым входом устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для имитации неисправностей | 1987 |

|

SU1444775A1 |

| Имитатор абонентов | 1986 |

|

SU1325490A2 |

| УСТРОЙСТВО ДЛЯ ОТСЧЕТА ВРЕМЕНИ | 1990 |

|

RU2079165C1 |

| Устройство для сопряжения ЭВМ с каналами связи | 1985 |

|

SU1288706A1 |

| Устройство для имитации сбоев | 1983 |

|

SU1107126A1 |

| Способ многодорожечной цифровой магнитной записи и устройство для его осуществления | 1990 |

|

SU1732380A1 |

| Устройство для имитации сбоев | 1985 |

|

SU1297058A1 |

| Устройство для имитации отказов и сбоев ЭВМ | 1987 |

|

SU1564628A1 |

| Устройство для имитации сбоев | 1985 |

|

SU1267421A1 |

| Устройство для контроля управляющей ЭВМ | 1988 |

|

SU1522216A1 |

Изобретение относится к цифровой вычислительной технике и может быть использовано для отработки и определения эффективности программноаппаратных средств контроля и обеспечения надежности работы ЭВМ. Цель изобретения расширение функциональных возможностей за счет обеспечения поразрядного динамического моделирования переходных процессов при сбоях. Устройство содержит одноразрядный блок 1 памяти, первый 2 и второй 3 блоки памяти, коммутатор 4 первую группу 5 элементов И, элементы ИЛИ 6, ИЛИ-НЕ 7 и 2И-ИЛИ 8, регистр помехи 9, вторую группу 10 элементов И, дешифратор 11, буферный регистр 12, триггер 13 и блок 14 элементов сложения по модулю два. 1 ил. с S (Л 1чЭ со 00 со ю ел М

| Устройство для имитации сбоев | 1983 |

|

SU1107126A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-03-23—Публикация

1985-10-04—Подача