Изобретение относится к области вычислительной техники и предназначено для имитации неисправностей в высоконадежных управляющих вычислительных системах (УВС) при экспериментальном исследовании их надежноо- сти.

Целью изобретения является расширение области применения устройства

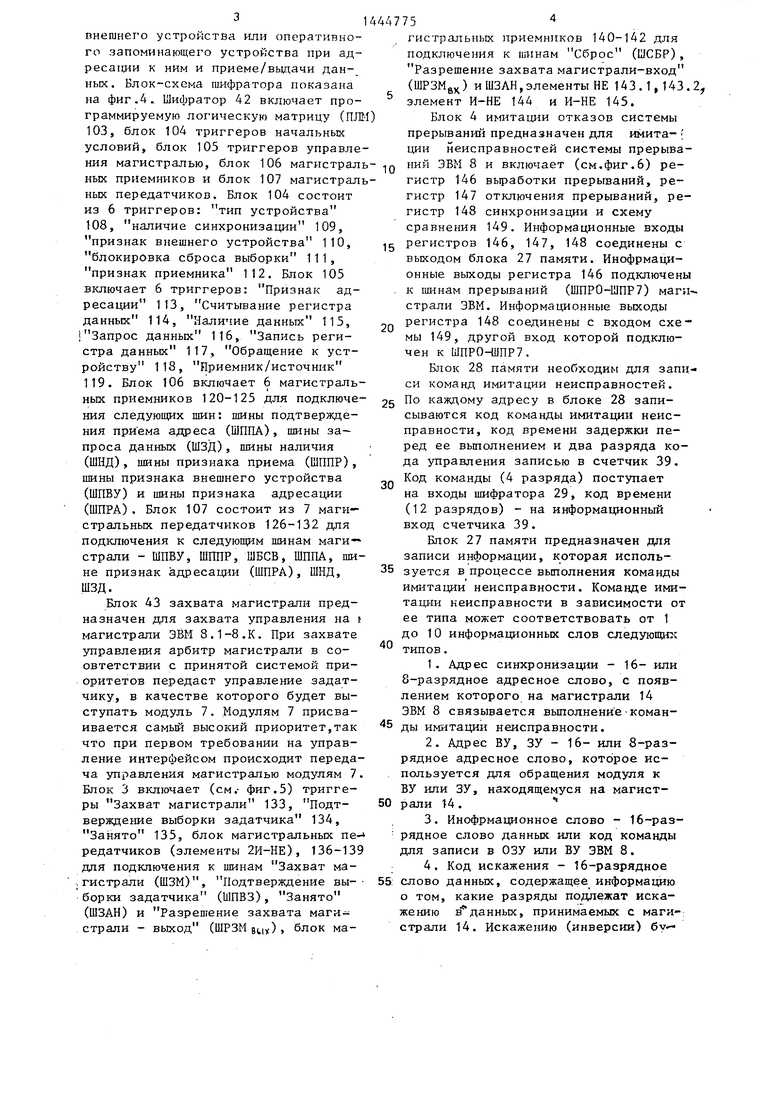

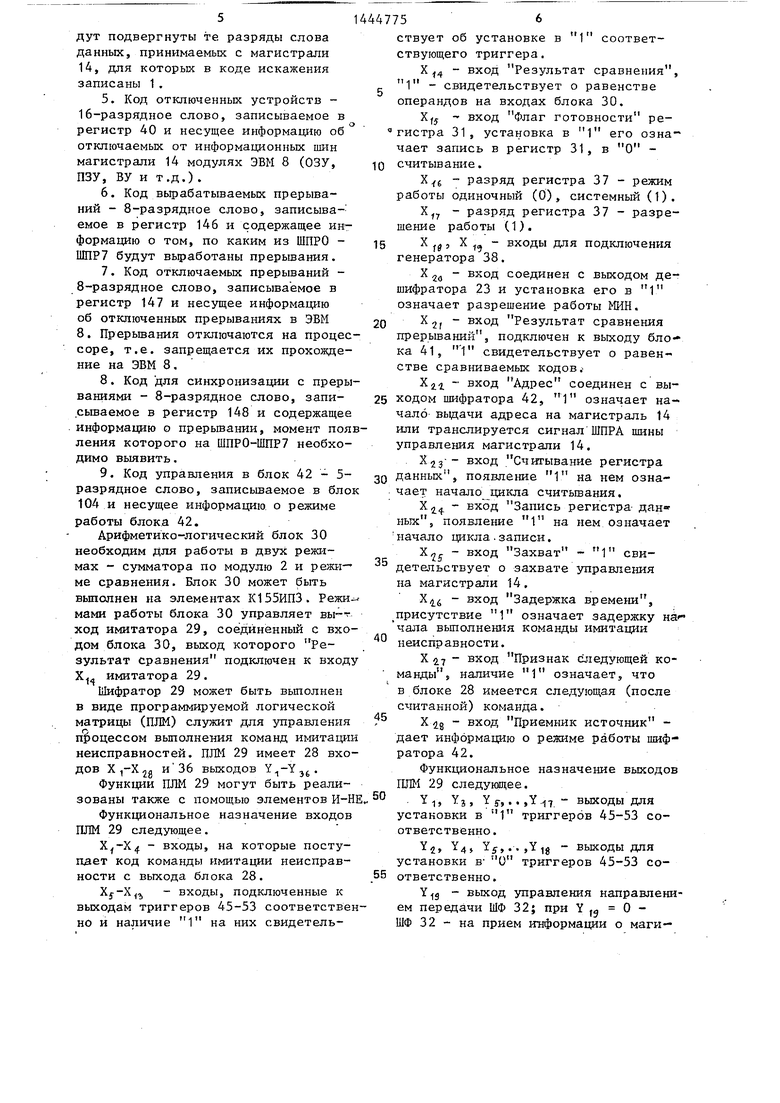

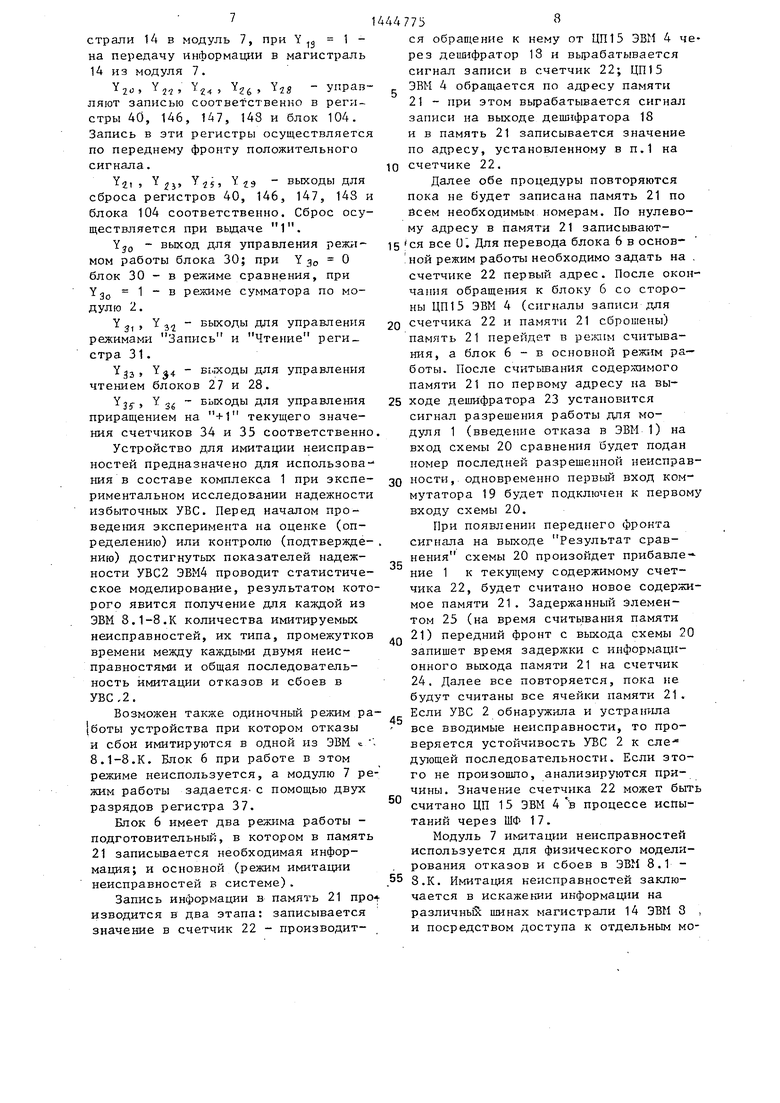

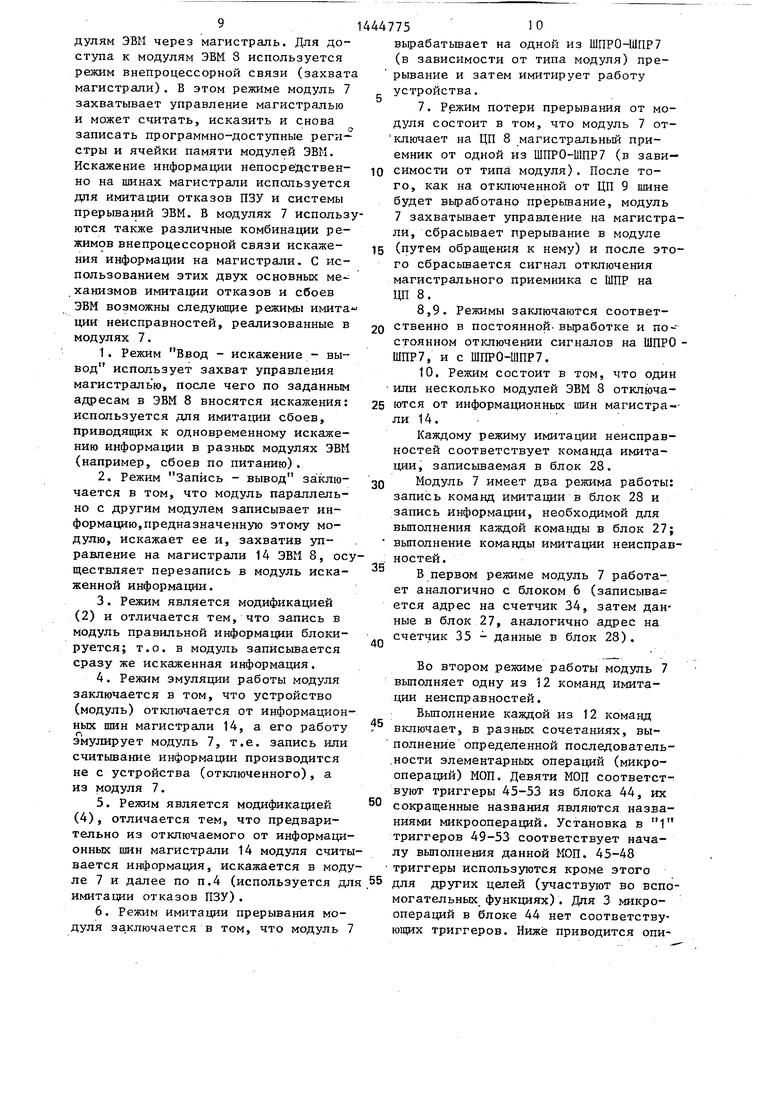

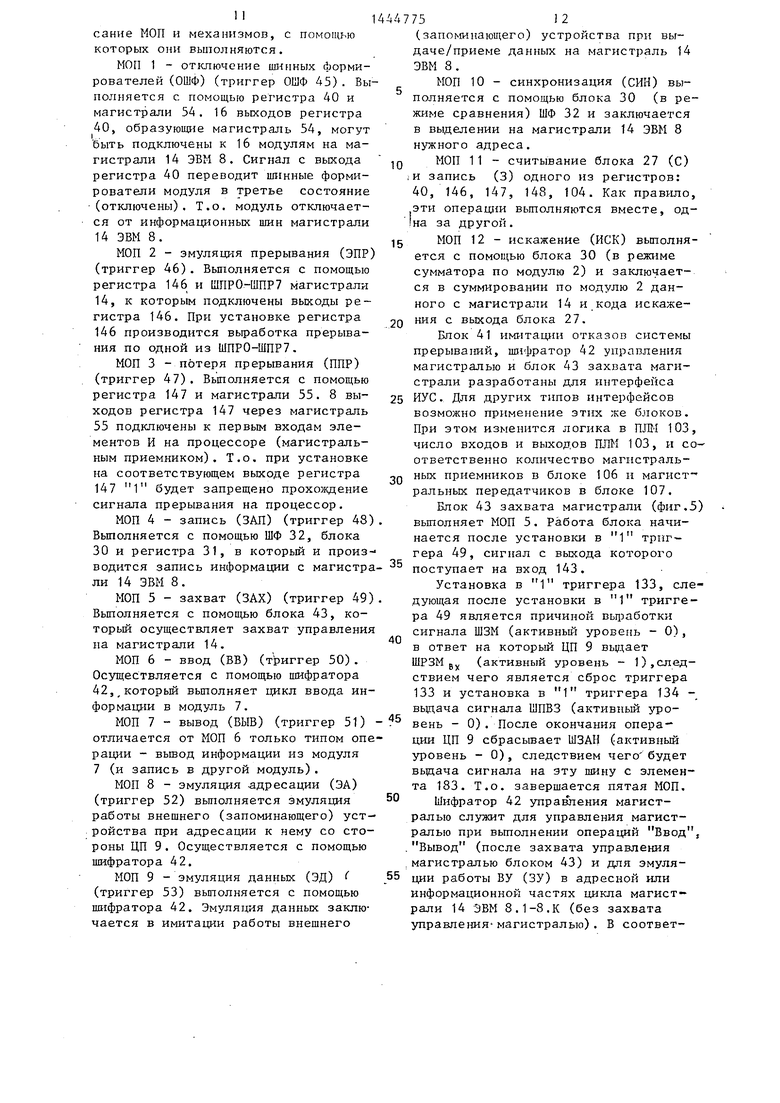

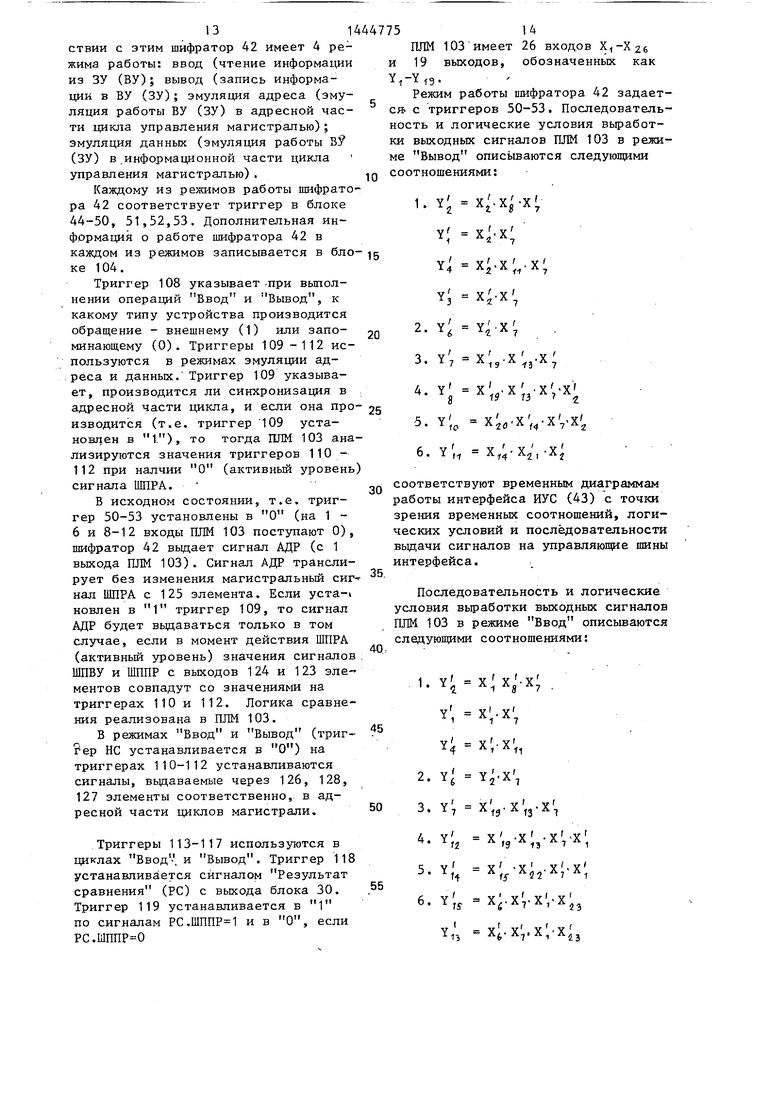

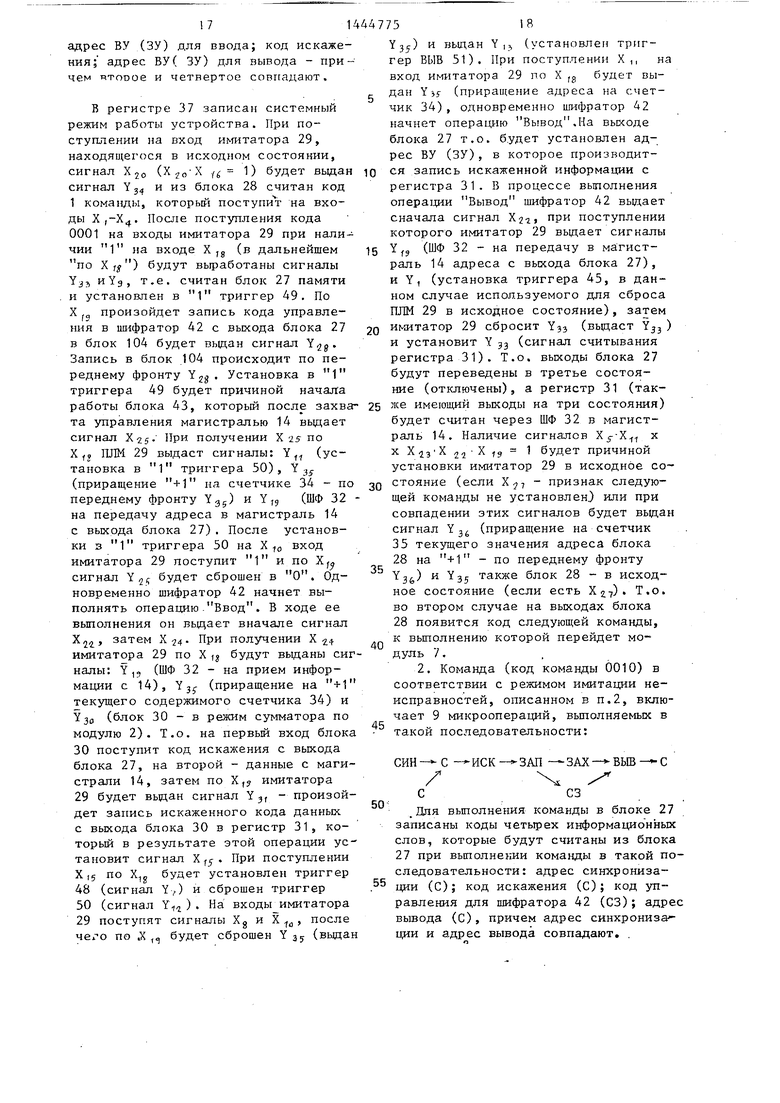

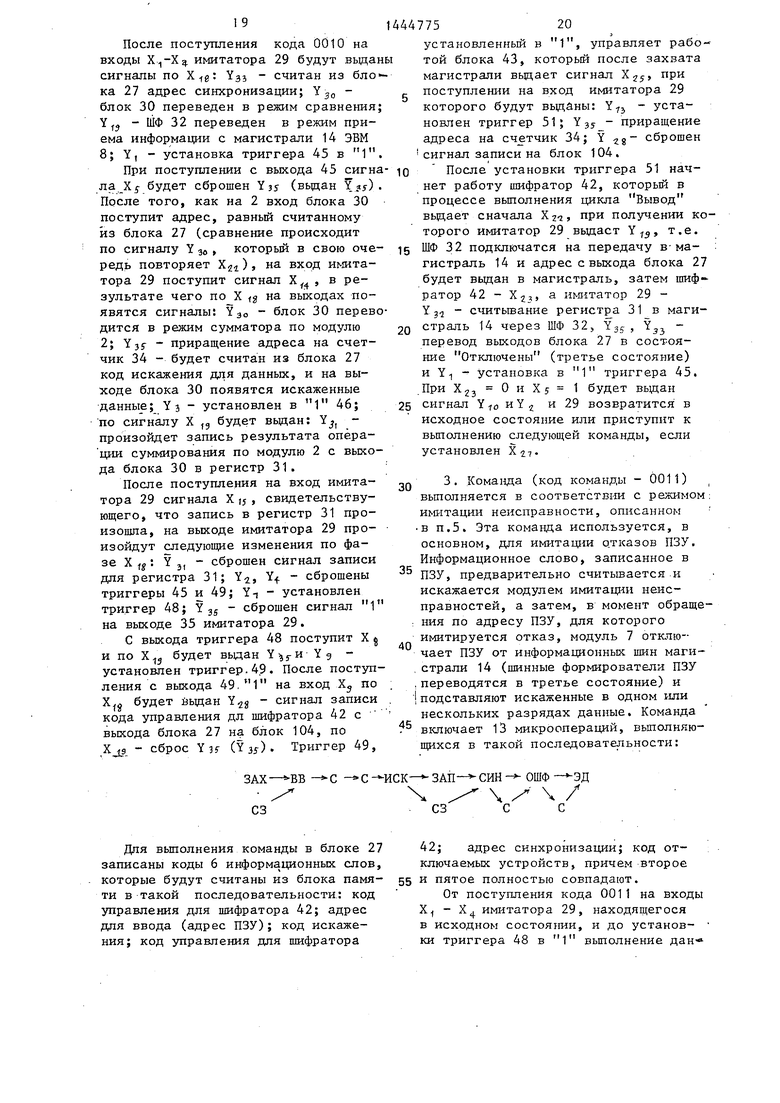

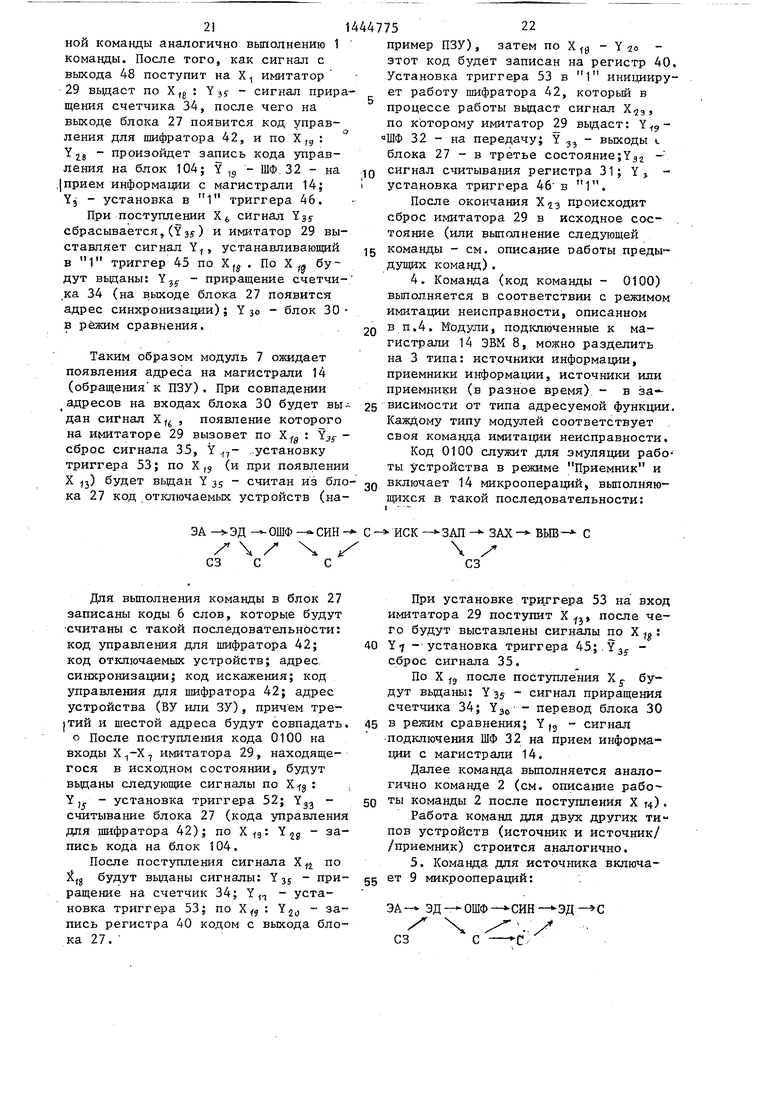

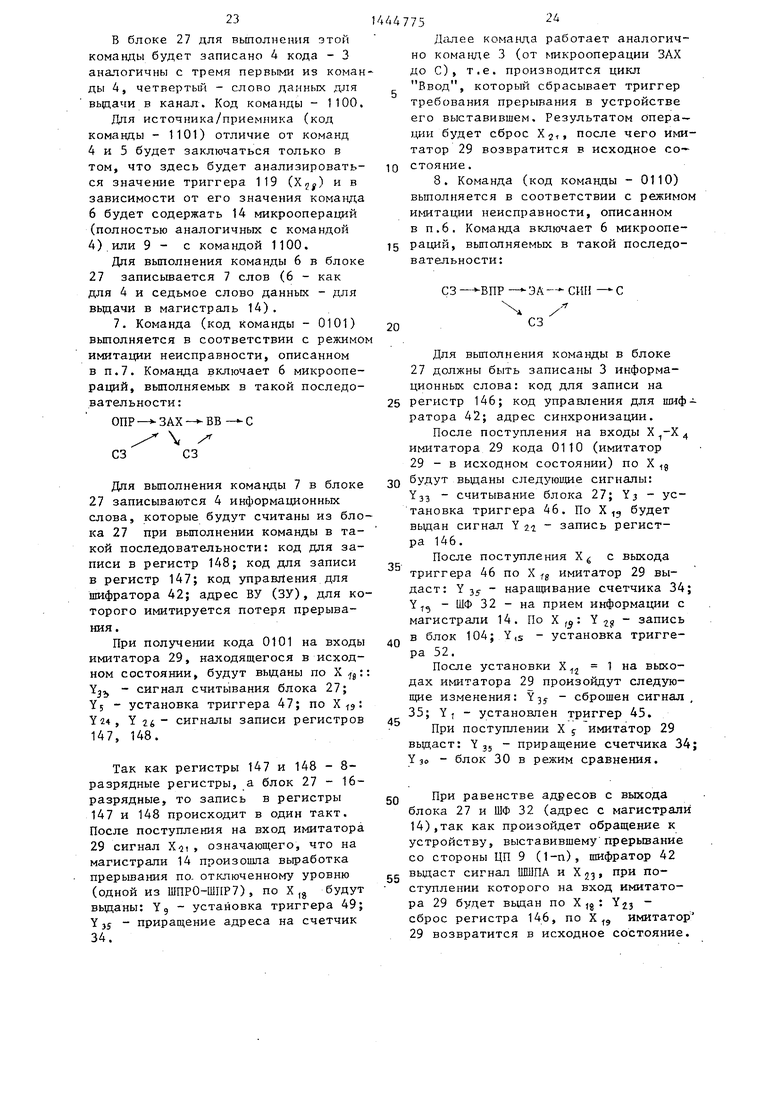

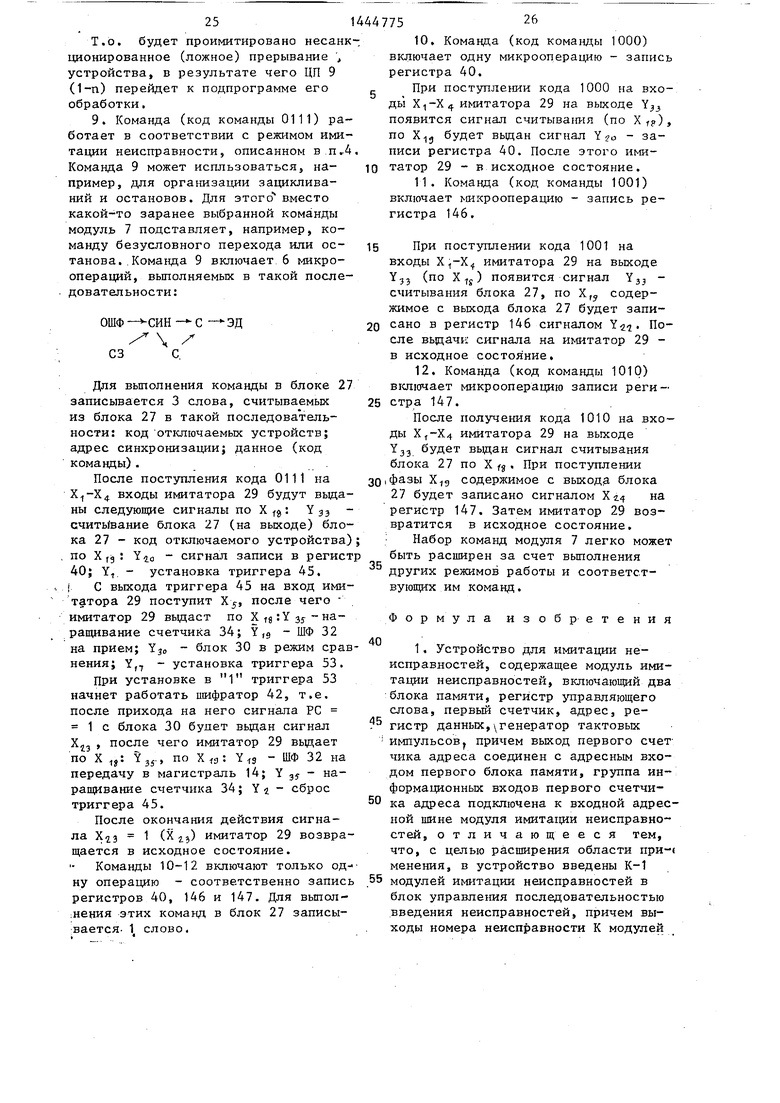

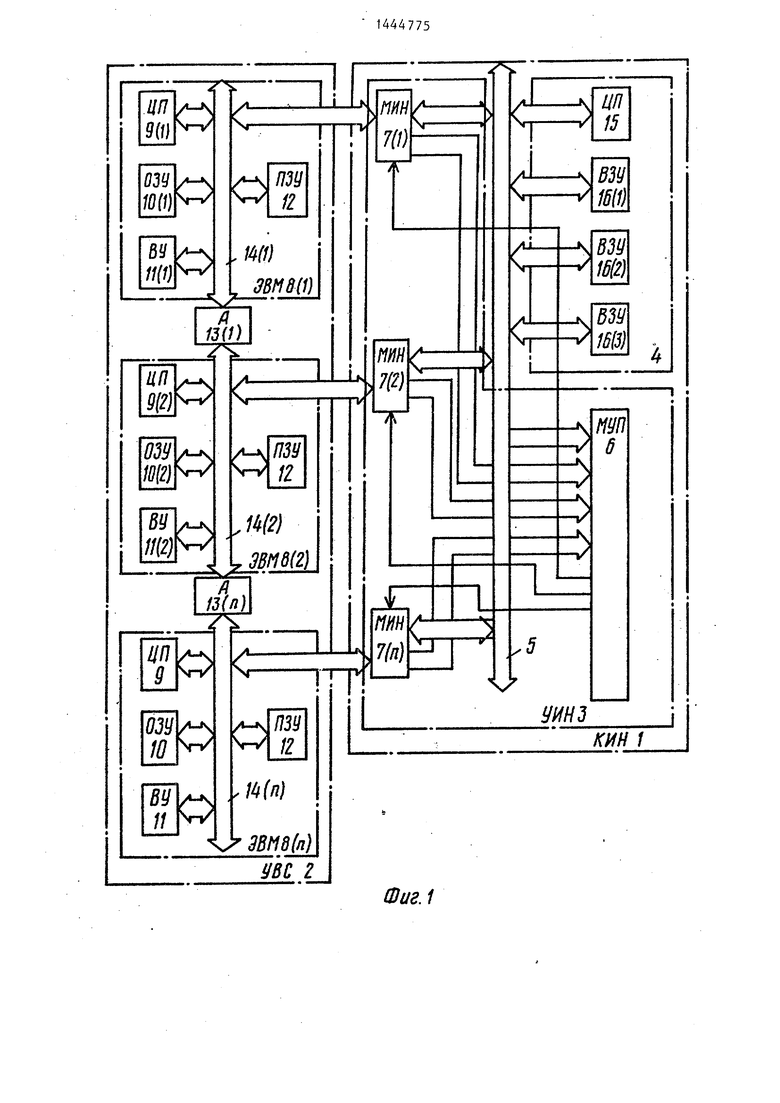

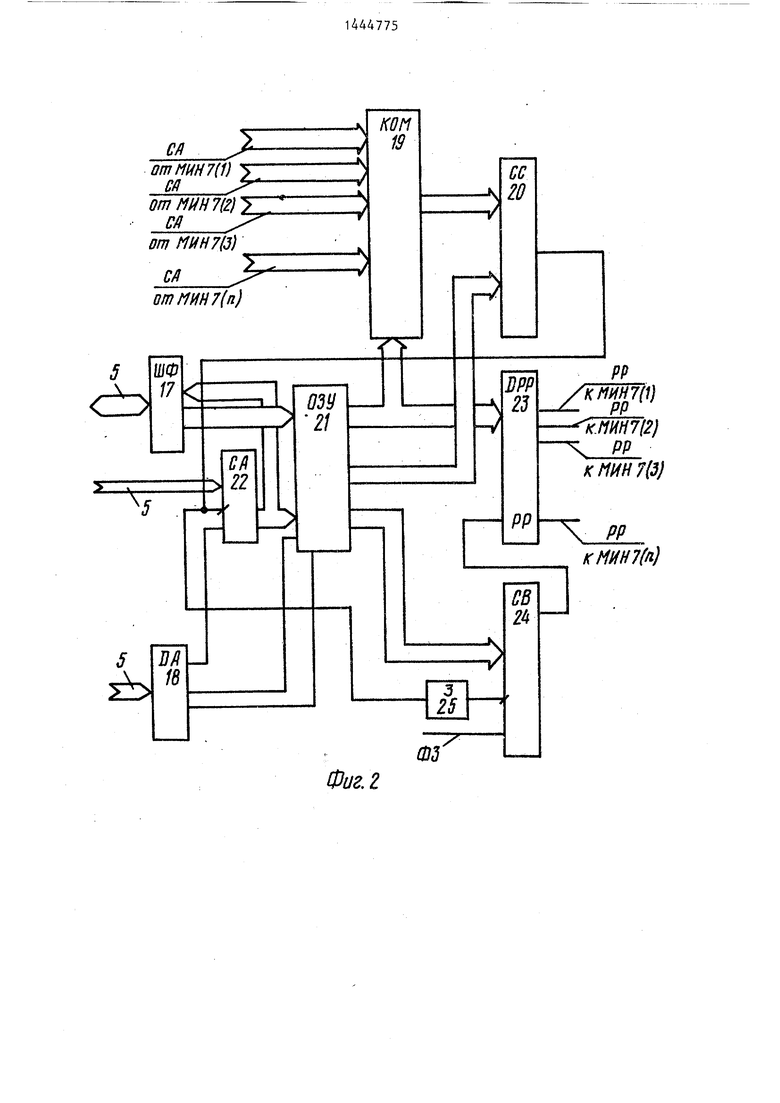

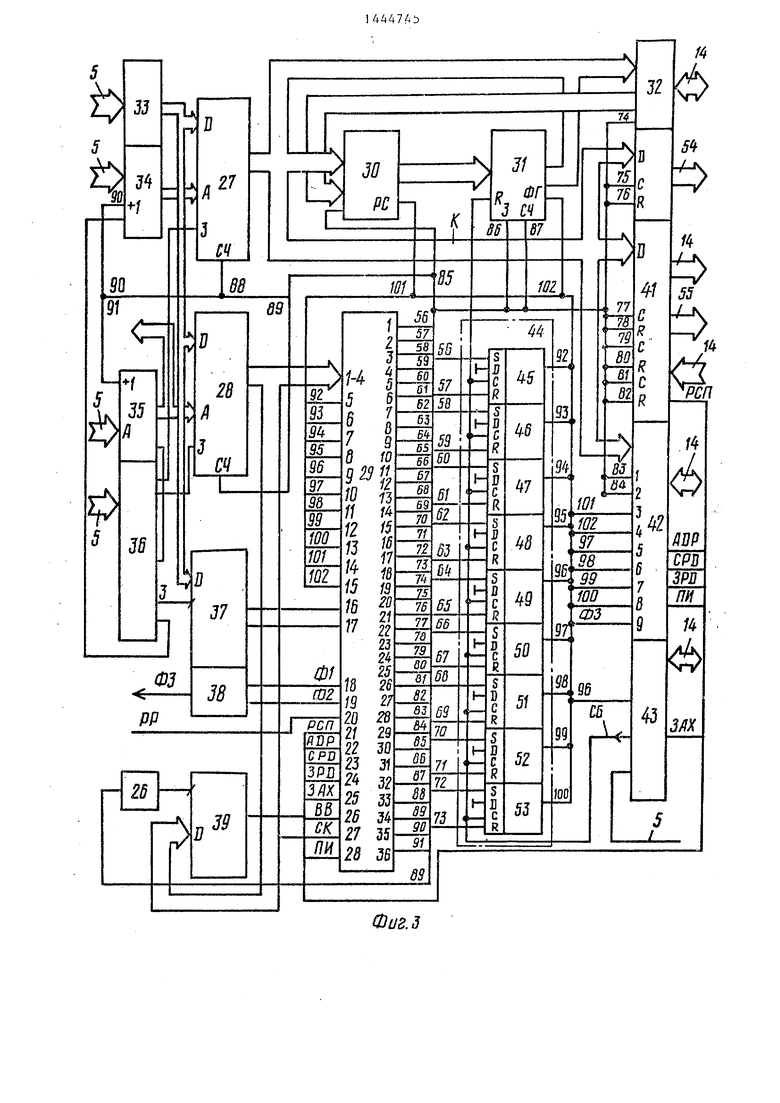

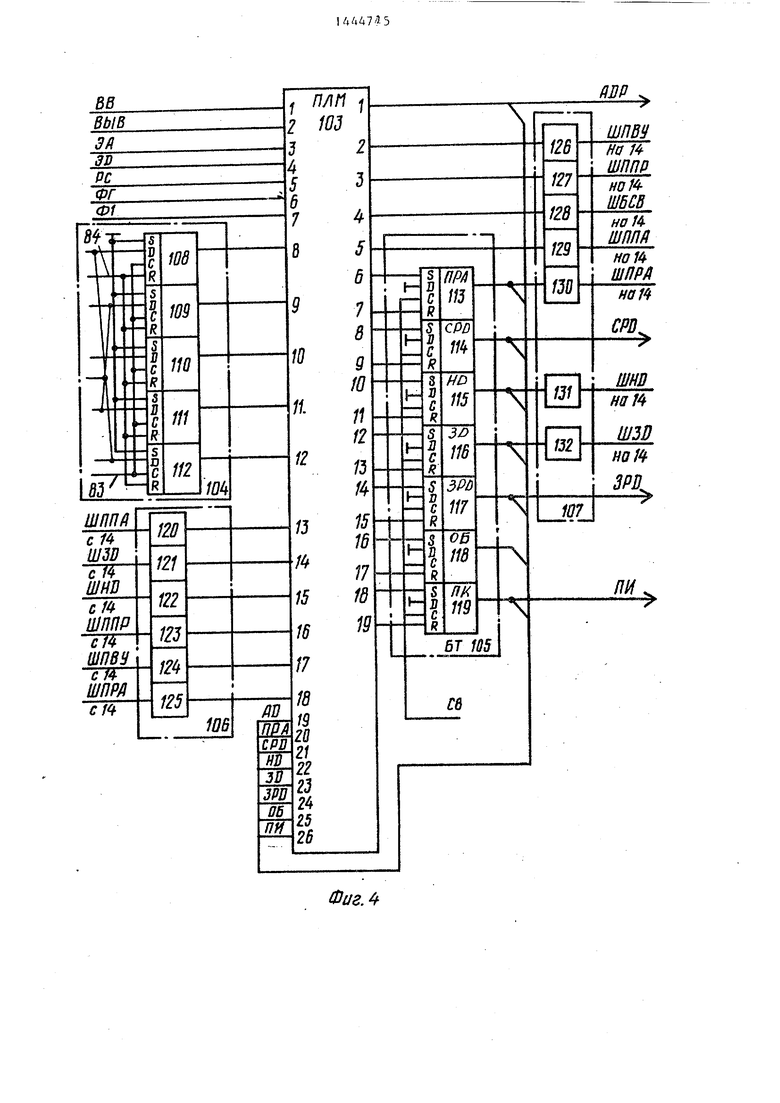

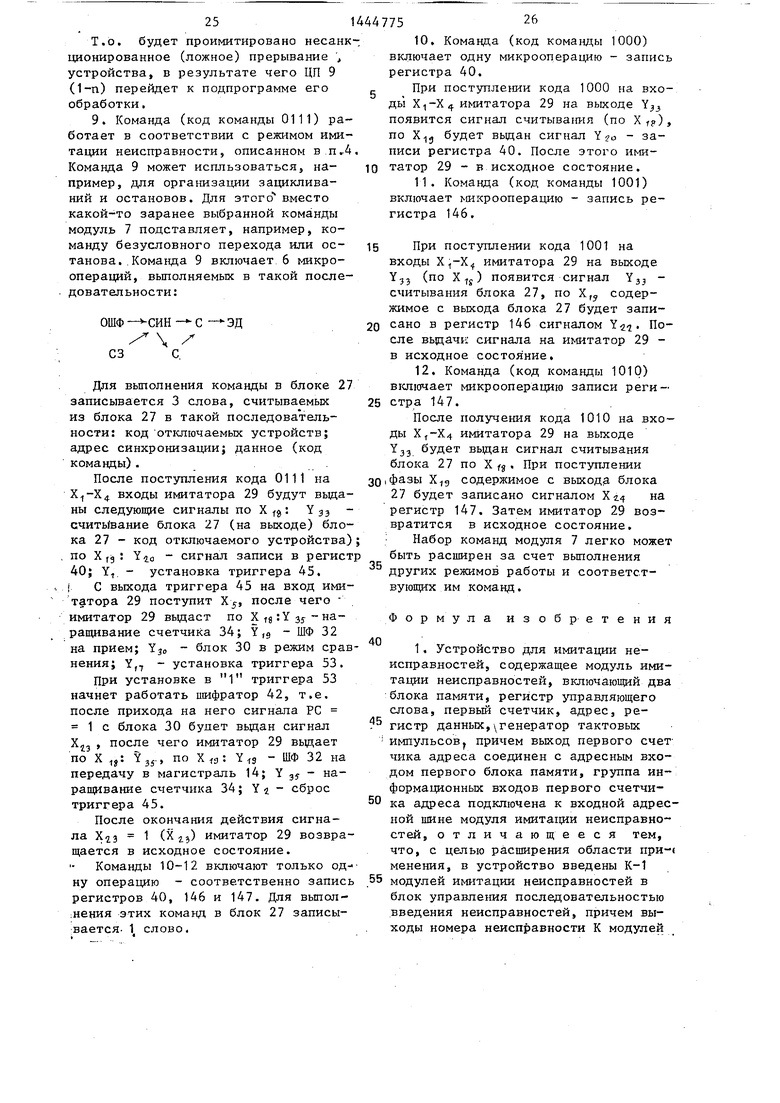

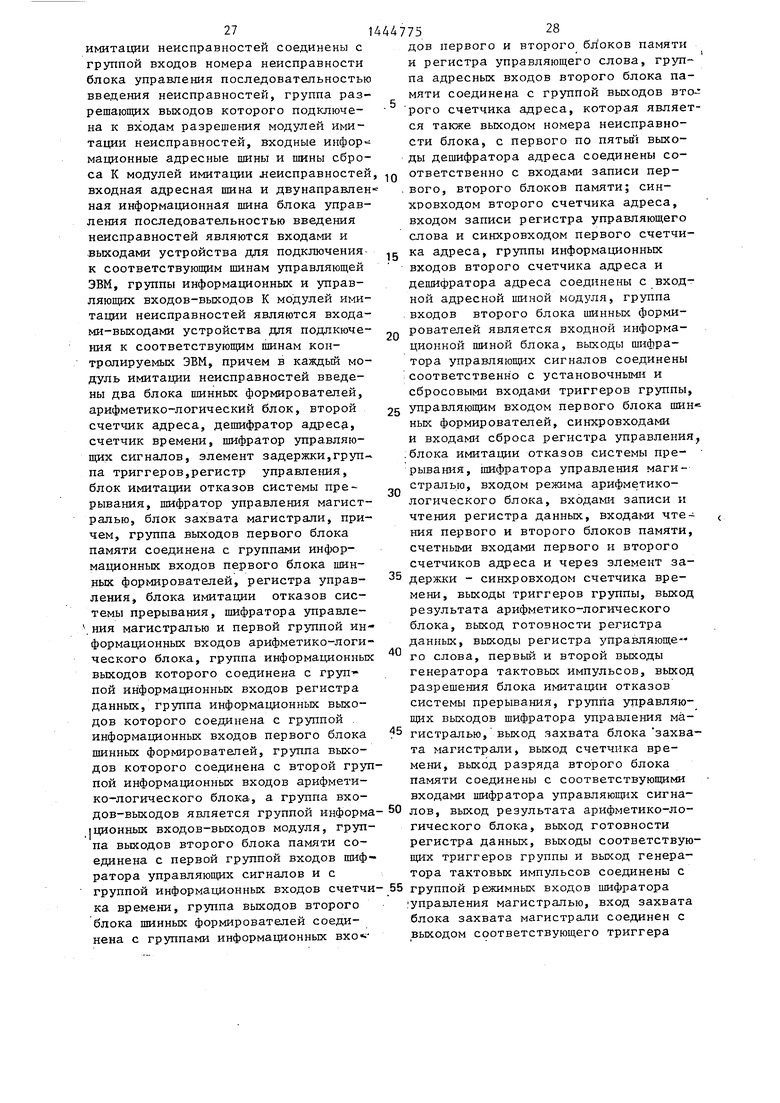

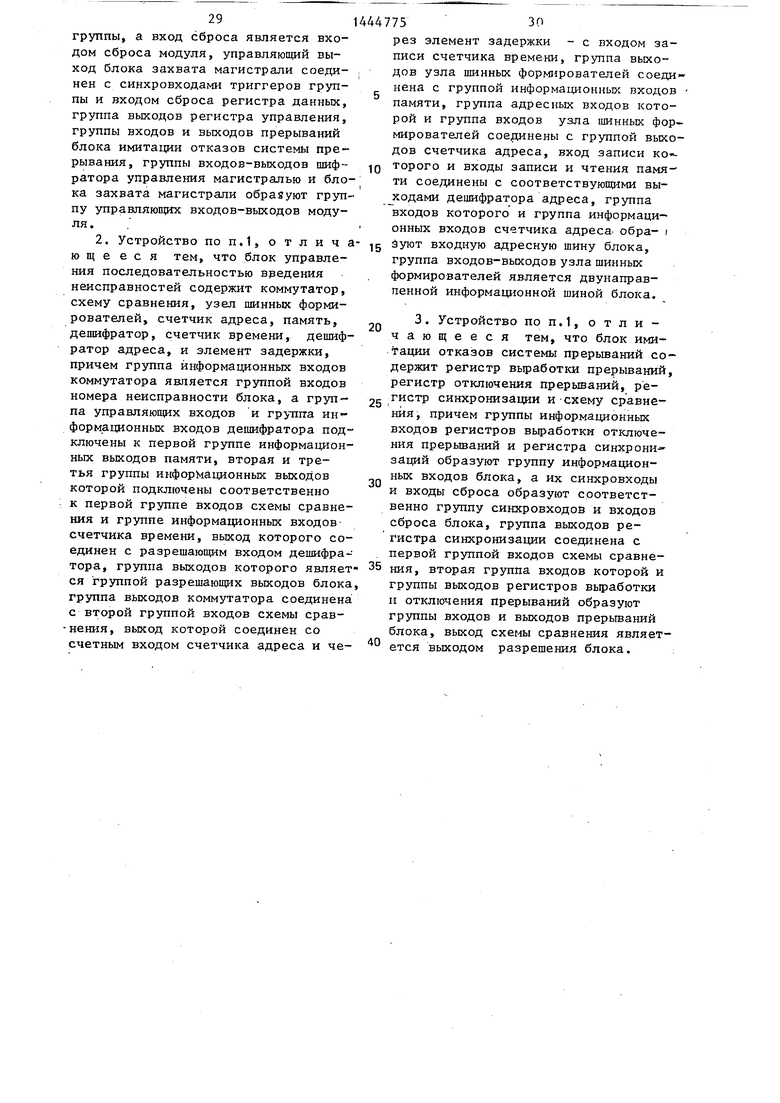

На фиг.1 показана блок-схема системы, в которой применяется устройство; на фиг.2 - схема блока управления последовательностью введения неисправностей; на фиг.З - схема модуля имитации неисправностей; на фиг.4 - схема шифратора управления магистралью; на фиг.З - схема блока захвата магистрали; на фиг.6 - схема блока имитации отказов системы прерьшаний.

На фиг.1 подазана блок-схема комплекса 1 для исследования надежности избыточной управляющей вычислительной системы (УВС) 2, в состав которого входят устройство для имитации неисправностей 3 и управляюща микроэвм 4, объединенные общей магистралью 5. Устройство для имитации неисправностей включает в себя блок 6 управления последовательностью введения неисправностей и модули 7.1-7.К имитации неисправностей, количество которых в общем слчае равно количеству ЭВМ в исследуемой системе. Показанная на фиг.1 исследуемая система состоит из ми- кроЭВМ 8,1-8.К, калщая из которых включает в себя центральный процессор (ЦП) 9, оперативное запоминающее устройство 10, внешнее устройство 11, постоянное запоминающее устройство 12j и адаптеров межмаиин- ной связи 13. ЭВМ 8 могут также в:слючать любые другие устройства напримера устройства связи с объектом, Щ1фроаналоговые и аналого-цифровые преобразователи)5 которые будут, подключены к магистрали 14.1 14.К. Управляющая ЭВМ 4 включает центральный процессор (ЦП) 15 и . внешние и запоминающие устройства 16. Модули подключены к магистрали .5 ЭВМ 4 на правах внешних устройств а также как и блок 6. Выходы моду лей (1-п) соединены с входами блока и необходимы для передачи номера имитируемой в настоящее время неисправности. Каждой ЭВМ 8 в исследуемой системе соответствует свой модуль, который соединен с ней дву- . направленной магистралью.

МУП 6 предназначен для управления

с последовательностью введения неисправностей в систему из нескольких ЭВМ 8.1-8.К, образующих высоконадежный управляющий вычислительный комплекс. Блок 6 СОСТОИТ (см. фиг.2) из

0 узла шинных формирователей (ШФ) 17, дешифратора 18 адреса, коммутатора 19, схемы 20 сравнения, памяти 21, счетчика 22, дешифратора (разрешения работы модулей имитации неисп5 |равностей) 23, счетчика 24 времени . и элемента 25 задержки.

Модуль имитации неисправностей служит для проведения физического моН делирования неисправностей, которые

0 могут появляться в процессе эксплуатации ЭВМ. Показанный на фиг.З модуль 7 включает элемент 26 задержки, два блока 27 и 28 памяти, имитатор 29 управляюш11Х сигналов, ариф25 метико-логический блок 30, регистр 31 данных, блоки 32 и 33 шинных формирователей (1ЯФ), счетчики 34 и 35 адреса, дешифратор 36 адреса, регистр 37 управляющего слова, генера-

30 тор 38 тактовых импульсов, счетчик 39 времени, регистр 40 управления (отключением шинных формирователей), блок 41 имитации отказов системы прерываний, шифратор 42 управления магистралью-, блок 43 захвата магистра ли и группу 44 триггеров.

Группа триггеров состоит из 9 триггеров: отключение шинных формирователей 45, эмуляция прерьгоания - 46, потеря прерывания 47, запись.. в регистр данных 48, захват магистрали 49, Ввод 50, Вывод 51, эмуляция адреса 52 и эмуляция дай- ных 53. Для расширения функциональ- ньк возможностей модулей 7 к шинам

имеющимся в магистрали 14, добавлены две группы шин: 54 - шины управления отключением шинньк формирователей в модулях ЭВМ 8.1-8.К (ЦП, ОЗУ, ПЗУ, ВУ) и 55 - шины управления от0 ключением прерьшаний (соединены с входами ЦП в ЭВМ 8.1-8.К. Шифратор 29 имеет выходы 56-91 и входы 92-102.

Шифратор 42 управления магистра- 5 необходим для осуществления опе рации Ввод и Вывод после захва-; та управления магистралью в соответствии с логикой работы интерфейса ИУС, а также для эмуляции работы

3

внешнего устройства или оперативного запоминающего устройства при ад- pecaioiH к ним и приеме/выдачи данных. Блок-схема шифратора показана на фиг.4. Шифратор 42 включает программируемую логическую матрицу СПШ) 103, блок 104 триггеров начальных условий, блок 105 триггеров управления магистралью, блок 106 магистральных приемников и блок 107 магистральных передатчиков. Блок 104 состоит

триггеров: II,

тип устройства

из 6

108, наличие синхронизации 109, признак внешнего устройства 110, блокировка сброса выборки 111, признак приемника 112. Блок 105 включает 6 триггеров: Признак адресации 113, Считывание регистра данных 114, Наличие данных 115,

I Запрос данных 116, Запись регистра данных 117, Обращение к устройству 118, Приемник/источник 119. Блок 106 включает 6 магистральных приемников 120-125 для подключения следующих пин: шины подтверждения приема адреса (ШППА), шины за- проса данных (ШЗД), шины наличия (ШНД), шины признака приема (ШППР), шины признака внешнего устройства (ШПВУ) и шины признака адресации (ШПРА). Блок 107 состоит из 7 магистральных передатчиков 126-132 для подключения к следующим шинам магистрали - ШПВУ, ШППР, ШБСВ, ШППА, шине признак адресации (ШПРА), ШНД, ШЗД.

Блок 43 захвата магистрали предназначен для захвата управления на магистрали ЭВМ 8.1-8.К. При захвате управлеьшя арбитр магистрали в со- овтетствии с принятой системой приоритетов передаст управление задат- чику, в качестве которого будет выступать модуль 7. Модулям 7 присваивается самьй высокий приоритет,так что при первом требовании на управление интерфейсом происходит передача управления магистралью модулям 7 Блок 3 включает (см.- фиг.5) триггеры Захват магистрали 133, Подтверждение выборки задатчика 134, Занято 135, блок магистральных пе редатчиков (элементы 2И-НЕ), 136-13 для подключения к шинам Захват ма.гистрали (ШЗМ), Подтверждение выборки задатчика (ШПВЗ), Занято (ШЗАН) и Разрешение захвата магистрали - выход (ШРЗМ ) , блок ма10

15

20

25

44775

гистральных приемников 140-142 для подключения к шинам Сброс (ШСБР), Разрешение захвата магистрали-вход (ШРЗМвх) иШЗАН,элементы НЕ 143.1,143.2, элемент И-НЕ 144 и И-НЕ 145.

Блок 4 имитации отказов системы прерываний предназначен для кмита- ции неисправностей системы прерываний ЭВМ 8 и включает (см.фиг.6) регистр 146 выработки прерываний, регистр 147 отключения прерываний, регистр 148 синхронизации и схему сравнения 149. Информационные входы регистров 146, 147, 148 соединены с выходом блока 27 памяти. Инофрмаци- онные выходы регистра 146 подключены к шинам прерываний (ШПРО-ШПР7) маги, страли ЭВМ. Информационные вькоды регистра 148 соединены с входом схемы 149, другой вход которой подключен к ИПРО-ШПР7.

Блок 28 памяти необходим для записи команд имитации неисправностей. По каждому адресу в блоке 28 записываются код команды имитации неисправности, код времени задержки перед ее вьтолнением и два разряда кода управления записью в счетчик 39. Код команды (4 разряда) поступает на входы шифратора 29, код времени (12 разрядов) - на информационный вход счетчика 39.

Блок 27 памяти предназначен для записи информации, которая используется в процессе вьтолнения команды имитации неисправности. Команде имитации неисправности в зависимости от ее типа может соответствовать от 1 до 10 информационных слов следующие: типов.

1.Адрес синхронизации - 16- или 8-разрядное адресное слово, с появлением которого на магистрали 14 ЭВМ 8 связывается выполнени е команды имитации неисправности.

2.Адрес ВУ, ЗУ - 16- или 8-разрядное адресное слово, которое используется для обращения модуля к ВУ или ЗУ, находящемуся на магист50 рали 14.

3.Инофрмационное слово - 16-разрядное слово данных или код команды для записи в ОЗУ или ВУ ЭВМ 8.

4.Код искажения - 16-разрядное 55 слово данных, содержащее информацию

о том, какие разряды подлежат искажению выданных, принимаемых с маги-; страли 14. Искажению (инверсии) бу 30

35

40

45

дут подвергнуты те разряды слова данных, принимаемых с магистрали 14, для которых в коде искажения записаны 1.

5.Код отключенных устройств - 16-разрядное слово, записываемое в регистр 40 и несущее информащш об отключаемых от информационных шин магистрали 14 модулях ЭВМ 8 (ОЗУ, ПЗУ, ВУ и т.д.).

6.Код вырабатываемых прерываний - 8-разрядное слово, записыва- емое в регистр 146 и содержащее информацию о том, по каким из ШПРО -

ШПР будут выработаны прерывания.

7.Код отключаемых прерываний - 8-разрядное слово, записываемое в

регистр 147 и несущее информацию об отключенных прерываниях в ЭВМ 8. Прерьтания отключаются на процессоре, т.е. запрещается их прохождение на ЭВМ 8,

8.Код для синхронизации с прерываниями - 8-разрядное слово, запи- сьшаемое в регистр 148 и содержащее информацию о прерьшании, момент пояления которого на Ш11РО-ШПР7 необходимо выявить.

9.Код управления в блок 42 - 5- разрядное слово, записьшаемое в бло 104 и несущее информацию о режиме

работы блока 42.

Арифметико-логический блок 30 необходим Для работы в двух режио

мах - сумматора по модулю / и режиме сравнения. Блок 30 может быть вьшолнен на элементах К155ИПЗ. Режи мами работы блока 30 управляет вы--- ход имитатора 29, соединенный с входом блока 30, выход которого Результат сравнения подключен к вход Х имитатора 29.

Шифратор 29 может быть вьпюлнен в виде программируемой логической матрицы (ПЛМ) служит для управления п оцессом выполнения команд и итaци неисправностей. ПЛМ 29 имеет 28 входов и 36 выходов .

Функции ПШ 29 могут быть реализованы также с помощью элементов ИФункциональное назначение входо ПЛМ 29 следующее.

- входы, на которые посту- пдет код команды имитации неисправности с выхода блока 28.

Xj-X,, - входы, подключенные к выходам триггеров 45-53 соответствно и наличие 1 на них свидетель

ю

14447756

ствует об установке в 1 соответствующего триггера.

X - вход Результат сравнения, 1 - свидетельствует о равенстве операндов на входах блока 30,

X|j - вход Флаг готовности регистра 31, установка в 1 его озна чает запись в регистр 31, в О - считывание.

XYS разряд регистра 37 - режим работы одиночный (0), системный (1).

Х, - разряд регистра 37 - разрешение работы (1).

X

ГЙ

X

генератора

X

9

- ВХОДЫ для подключения 38.

2д - ВХОД соединен с выходом дешифратора 23 и установка его в 1 означает разрешение работы МИН.

Хз, вход Результат сравнения прерываний, подключен к выходу бло- ка 41, 1 свидетельствует о равенстве сравниваемых кодов.Х - вход Адрес соединен с вы- ходом шифратора 42, 1 означает начало выдачи адреса на магистраль 14 или транслируется сигнал ШПРА шины управления магистрали 14,

вход Считывание регистра данных, появле ше 1 на нем означает начало цикла считьюания.

Х, - вход Запись регистра данных, появление 1 на нем означает начало цикла.записи.

25

- вход Захват - 1

5

0

5

0

детельствует о захвате управления на магистрали 14.

Х - вход Задержка времени,

присутствие 1 означает задержку на чала вьшолненик команды имитации неисправности.

X 7 вход Признак следующей кома нды, наличие 1 означает, что в блоке 28 имеется следующая (после считанной) команда.

X jg - вход Приемник источник - дает информацию о режиме работы ншф- ратора 42.

Функциональное назначение выходов ПШ 29 следующее.

YI, YJ, YS-, .. ,Y.7. выходы для установки в 1 триггеров 45-53 соответственно.

Yi, Y4, Y установки в ответственно.

- выход управления ем передачи ШФ 32; при Y ,д ШФ 32 - на прием информации о

5

.. О

,Y g выходы для триггеров 45-53 сонаправлени- О - маги-

страпи 14 в модуль 7, при 13 1 на передачу информации в магистраль 14 из модуля 7.

20, Yj.;, Y , Y , - управ- ляют записью cooTBefственно в регистры 40, 146, 147, 148 и блок 104. Запись в эти регистры осуществляется по переднему фронту положительного сигнала.

YJ, , , , - выходы для сброса регистров 40, 146, 147, 148 и блока 104 соответственно. Сброс осуществляется при вьщаче 1.

YJO - выход для управления режи- мом работы блока 30; при Y О блок 30 - в режиме сравнения, при

Зо

1 - В режиме сумматора по модулю 2.

Y J, , Y 3 - выходы для управления режимами Запись и Чтение регистра 31.

В1и;ходы для управления чтением блоков 27 и 28.

YJJ-, Y 3 - выходы для управления приращением на +1 текущего значения счетчиков 34 и 35 соответственно

Устройство для имитации неисправностей предназначено для использования в составе комплекса 1 при экспе- риментальном исследовании надежности избыточных УВС. Перед началом проведения эксперимента на оценке (определению) или контролю (подтвержде- нию) достигнутых показателей надежности УВС2 ЭВМ4 проводит статистическое моделирование, результатом которого явится получение для каждой из ЭВМ 8.1-8.К количества имитируемых неисправностей, их типа, промежутков времени между каждыми двумя неисправностями и общая последовательность имитации отказов и сбоев в УБС,2,

Возможен также одиночный режим ра (боты устройства при котором отказы и сбои имитируются в одной из ЭВМ ч 8.1-8.К. Блок 6 при работе в этом режиме неиспользуется, а модулю 7 режим работы задается- с помощью двух разрядов регистра 37.

Блок 6 имеет два режима работы - подготовительный, в котором в память 21 записывается необходимая информация; и основной (режим имитации неисправностей в системе).

Запись информации в память 21 npo изводится в два этапа: записывается значение в счетчик 22 - производит

Q

5

0

5

о

0

5

7738

ся обращение к нему от ЦП 15 ЭВМ 4 через дешифратор 18 и вырабатывается сигнал записи в счетчик 22; ЦП 15 ЭВМ 4 обращается по адресу памяти 21 - при этом вырабатывается сигнал записи на выходе дешифратора 18 и в память 21 записывается значение по адресу, установленному в п.1 на счетчике 22.

Далее обе процедуры повторяются пока не будет записана память 21 по всем необходимым номерам. По нулевому адресу в памяти 21 записывают- ся все о; Для перевода блока 6 в основ- ной режим работы необходимо задать на . счетчике 22 первый адрес. После окончания обращения к блоку б со стороны ЦП15 ЭВМ 4 (сигналы записи для счетчика 22 и памяти 21 сброшены) память 21 перейдет в ре;к11м считывания, а блок 6 - в основной режим работы. После считьшания содержимого памяти 21 по первому адресу на выходе дешифратора 23 установится сигнал разрешения работы для модуля 1 (введение отказа в ЭВМ 1) на вход схемы 20 сравнения будет подан номер последней разрешенной неисправности, одновременно первЕ 1Й вход коммутатора 19 будет подключен к первому входу схемы 20.

При появлении переднего фронта сигнала на выходе Результат сравнения схемы 20 произойдет прибавле- ние 1 к текущему содержимому счетчика 22, будет считано новое содержимое памяти 21. Задержанный элементом 25 (на время считывания памяти 21) передний фронт с выхода схемы 20 запишет время задержки с информационного выхода памяти 21 на счетчик 24. Далее все повторяется, пока не будут считаны все ячейки памяти 21. Если УВС 2 обнаружила и устранила все вводимые неисправности, то проверяется устойчивость УВС 2 к еле дующей последовательности. Если этого не произовшо, анализируются причины. Значение счетчика 22 может быть считано ЦП 15 ЭВМ 4 в процессе испытаний через ШФ 17.

Модуль 7 имитации неисправностей используется для физического моделирования отказов и сбоев в ЭВМ 8.1 - 8.К. Имитация неисправностей заключается в искажении иь-формации на различнь15с шинах магистрали 14 ЭВМ 8 , и посредством доступа к отдельным модулям ЭВМ через магистраль. Для доступа к модулям ЭВМ 8 используется режим внепроцессорной связи (захвата магистрали). В этом режиме модуль 7 захватывает управление магистралью и может считать, исказить и снова записать программно-доступные регистры и ячейки памяти модулей ЭВМ. Искажение информации непосрействен- но на шинах магистрали используется для имитации отказов ПЗУ и системы прерываний ЭВМ. В модулях 7 используются также различные комбинации режимов внепроцессорной связи искажения информации на магистрали. С использованием этих двзос основных ме-: ханизмов имитадаи отказов и сбоев ЭВМ возможны следующие режимы имита ции неисправностей, реализованные в модулях 7.

1.Режим Ввод - искажение - вывод использует захват управления магистраль ю, после чего по заданным адресам в ЭВМ 8 вносятся искажения: используется для имитагщи сбоев, приводящих к одновременному искажению информации в разных модулях ЭВМ (например, сбоев по питанию).

2.Режим Запись - вывод заключается в том, что модуль параллельно с другим модулем записывает информацию,предназначенную этому модулю, искажает ее и, захватив управление на магистрали 14 ЭВМ 8, осуществляет перезапись в модуль искаженной информации.

3.Режим является модификацией (2) и отличается тем, что запись в модуль правильной информации блокируется; т.о. в модуль записывается сразу же искаженная информация.

4.Режим эмуляции работы модуля заключается в том, что устройство (модуль) отключается от информацион14, а его работу т.е. запись или считывание информации производится не с устройства (отключенного), а из модуля 7.

5.Режим является модификацией (4), отличается тем, что предварительно из отключаемого от информационных шин магистрали 14 модуля считывается информация, искажается в моду10

ных шин магистрали эмулирует модуль 7,

15

20

25

30

35

40

45

50

вырабатьшает на одной из ШПРО-ШПР7 (в зависимости от типа модуля) прерывание и затем имитирует работу устройства.

7. Режим потери прерывания от модуля состоит в том, что модуль 7 отключает на ЦП 8 магистральный приемник от одной из ШПРО-ШПР7 (в зависимости от типа модуля). После того, как на отключенной от ЦП 9 шине будет вьфаботано прерьшание, модуль 7 захватывает управление на магистрали, сбрасывает прерывание в модуле (путем обращения к нему) и после этого сбрасьшается сигнал отключения магистрального приемника с ШПР на ЦП 8.

8,9. Режимы заключаются соответственно в постоянной, выработке и по- стоянном отключении сигналов на ШПРО - ШПР7, и с ШПРО-ШПР7.

10. Режим состоит в том, что один или несколько модулей ЭВМ 8 отключаются от информационных шин магистра-- ли 14.

Каждому режиму имитации неисправностей соответствует команда имитации, записьшаемая в блок 28.

Модуль 7 имеет два режима работы: запись команд имитации в блок 28 и запись информации, необходимой для выполнения каждой комавды в блок 27; выполнение команды имитации неисправностей.

В первом режиме модуль 7 работает аналогично с блоком 6 (записыва ется адрес на счетчик 34, затем данные в блок 27, аналогично адрес на счетчик 35 - данные в блок 28).

Во втором режиме работы модуль 7 вьтолняет одну из 12 команд имитации неисправностей.

Вьшолнение каждой из 12 команд включает, в разных сочетаниях, вы- полнение определенной последователь- .ности элементарных операций (микроопераций) МОП. Девяти МОП соответствуют триггеры 45-53 из блока 44, их сокращенные названия являются названиями микроопераций. Установка в 1 триггеров 49-53 соответствует началу выполнения данной МОП. 45-48 триггеры используются кроме этого

ле 7 и далее по п.4 (используется для ,55 для других целей (участвуют во вспо- имитации отказов ПЗУ).могательных функциях). Рдя 3 микро6. Режим имитации прерывания модуля за.ключается в том, что модуль 7

операций в блоке 44 нет соответствующих триггеров. Ниже приводится опи

5

0

5

0

5

0

5

0

вырабатьшает на одной из ШПРО-ШПР7 (в зависимости от типа модуля) прерывание и затем имитирует работу устройства.

7. Режим потери прерывания от модуля состоит в том, что модуль 7 отключает на ЦП 8 магистральный приемник от одной из ШПРО-ШПР7 (в зависимости от типа модуля). После того, как на отключенной от ЦП 9 шине будет вьфаботано прерьшание, модуль 7 захватывает управление на магистрали, сбрасывает прерывание в модуле (путем обращения к нему) и после этого сбрасьшается сигнал отключения магистрального приемника с ШПР на ЦП 8.

8,9. Режимы заключаются соответственно в постоянной, выработке и по- стоянном отключении сигналов на ШПРО - ШПР7, и с ШПРО-ШПР7.

10. Режим состоит в том, что один или несколько модулей ЭВМ 8 отключаются от информационных шин магистра-- ли 14.

Каждому режиму имитации неисправностей соответствует команда имитации, записьшаемая в блок 28.

Модуль 7 имеет два режима работы: запись команд имитации в блок 28 и запись информации, необходимой для выполнения каждой комавды в блок 27; выполнение команды имитации неисправностей.

В первом режиме модуль 7 работает аналогично с блоком 6 (записыва ется адрес на счетчик 34, затем данные в блок 27, аналогично адрес на счетчик 35 - данные в блок 28).

Во втором режиме работы модуль 7 вьтолняет одну из 12 команд имитации неисправностей.

Вьшолнение каждой из 12 команд включает, в разных сочетаниях, вы- полнение определенной последователь- .ности элементарных операций (микроопераций) МОП. Девяти МОП соответствуют триггеры 45-53 из блока 44, их сокращенные названия являются названиями микроопераций. Установка в 1 триггеров 49-53 соответствует началу выполнения данной МОП. 45-48 триггеры используются кроме этого

операций в блоке 44 нет соответствующих триггеров. Ниже приводится опи

11

санне МОП и механизмов, с помощью которых они вьшолняются.

МОП 1 - опшючсние шнпнък формирователей (ОШФ) (триггер ОШФ 45). Выполняется с помощью регистра 40 и магистрали 54. 16 выходов регистра 40, образующие магистраль 54, могут быть подключены к 16 модулям на магистрали 14 ЭВМ 8. Сигнал с вькода регистра 40 переводит шинные формирователи модуля в третье состояние (отключены). Т.о. модуль отключается от информационных шин магистрали 14 ЭВМ 8.

МОП 2 - эмуляция прерывания (ЭПР (триггер 46). Вьпюлняется с помощью регистра 146 и ШПРО-ШПР7 магистрали 14, к которым подключены выходы регистра 146. При установке регистра

146производится выработка прерывания по одной из ШПРО-ШПР7.

МОП 3 - потеря прерывания (ППР) (триггер 47). Выполняется с помощью регистра 147 и магистрали 55. 8 вы- ходов регистра 147 через магистраль 55 подключены к первым входам элементов И на процессоре (магистральным приемником). Т.о. при установке на соответствующем выходе регистра

будет запрещено прохождение сигнала прерывания на процессор.

МОП 4 - запись (ЗАП) (триггер 48) Вьшолняется с помощью ШФ 32, блока 30 и регистра 31, в которьш и производится запись информации с магистра ли 14 ЭВМ 8.

МОП 5 - захват (ЗАХ) (триггер 49) Выполняется с помощью блока 43, ко- торьй осуществляет захват управления на магистрали 14.

МОП 6 - ввод (ВВ) (т риггер 50) . Осуществляется с помощью шифратора 42,которьш выполняет цикл ввода информации в модуль 7.

МОП 7 - вывод (ВЫВ) (триггер 51) отличается от МОП 6 только типом операции - вывод информации из модуля 7 (и запись в другой модуль).

МОП 8 - эмуляция -адресации (ЭА) (триггер 52) вьшолняется эмуляция работы внешнего (запоминающего) устройства при адресации к нему со стороны ЦП 9. Осуществляется с помощью шифратора 42.

МОП 9 - эмуляция данных (ЭД) (триггер 53) выполняется с помощью шифратора 42. Эмуляция данных заключается в имитации работы внешнего

5

47

д

5

5

0

5

7512

(запоминающего) устройства при выдаче/приеме данных на магистраль 14 ЭВМ 8.

МОП 10 - синхронизация (СИН) выполняется с помощью блока 30 (в режиме сравнения) ШФ 32 и заключается в выделении на магистрали 14 ЭВМ 8 нужного адреса.

МОП 11 - считывание блока 27 (С) и запись (3) одного из регистров: 40, 146, 147, 148, 104. Как правило, эти операции выполняются вместе, од- на за другой.

МОП 12 - искажение (ИСК) выполняется с помощью блока 30 (в режиме сумматора по модулю 2) и заключается в суммировании по модулю 2 данного с магистрали 14 и кода искажения с вькода блока 27.

Блок 41 имитац1П1 отказов системы прерываний, шифратор 42 управления магистралью и блок 43 захвата магистрали разработаны для интерфейса ИУС. Для других типов интерфейсов возмолсно применение этих ;ке блоков. При этом изменится логика в ПЛ1-1 103, число входов и выходов ШТМ 103, и соответственно количество магистральных приемников в блоке 106 и магистральных передатчиков в блоке 107.

Блок 43 захвата магистрали (фиг.5) выполняет МОП 5. Работа блока начинается после установки в 1 триггера 49, сигнал с выхода которого поступает на вход 143.

Установка в 1 триггера 133, следующая после установки в 1 триггера 49 является причиной вьфаботки сигнала ШЗМ (активный уровень - 0), в ответ на который ЦП 9 вьщает ШРЗМ gj (активный уровень - 1),следствием чего является сброс триггера 133 и установка в 1 триггера 134 - вьщача сигнала ШПВЗ (активный уровень - 0). После окончания операции ЦП 9 сбрасывает ЫЗАН (активный уровень - 0), следствием чего будет вьдача сигнала на эту шину с элемента 183. Т.о. завершается пятая МОП.

Шифратор 42 управления магистралью служит для управления магистралью при выполнении операций Ввод, Вывод (после захвата управления магистралью блоком 43) и для эмуляции работы ВУ (ЗУ) в адресной или информационной частях цикла магистрали 14 ЭВМ 8.1-8.К (без захвата управления магистралью). В соответ13

1 ре

ствии с этим шифратор 42 имеет 4 жима работы: ввод (чтение информации из ЗУ (ВУ); вывод (запись информации в ВУ (ЗУ); эмуляция адреса (эмуляция работы ВУ (ЗУ) в адресной части цию1а управления магистралью); эмуляция данных (эмуляция работы В (ЗУ) в.информационной части цикла управления магистралью),

Каждому из режимов работы шифратора 42 соответствует триггер в блоке 44-50, 51,52,53. Дополнительная информация о работе шифратора 42 в каждом из режимов записывается в бло ке 104.

Триггер 108 указывает-при выполнении операций Ввод и Вывод, к какому типу устройства производится обращение - внешнему (1) или запо- минающему (0). Триггеры 109-112 используются в режимах эмуляции адреса и данных. Триггер 109 указывает, производится ли синхронизация в адресной части цикла, и если она про изводится (т.е. триггер 109 установлен в 1.), то тогда ПЛМ 103 анализируются значения триггеров 110 - 112 при налчии О (активный уровень сигнала ШПРА.

В исходном состоянии, т.е. триггер 50-53 установлены в О (на 1 - 6 и 8-12 входы ПЛМ 103 поступают 0), шифратор 42 вьщает сигнал АДР (с 1 выхода ПЛМ 103). Сигнал АДР транслирует без изменения магистральный сиг нал ШПРА с 125 элемента. Если уста-i новлен в 1 триггер 109, то сигнал АДР будет вьщаваться только в том случае, если в момент действия ШПРА (активный уровень) значения сигналов ШПВУ и ШППР с выходов 124 и 123 элементов совпадут со значениями на триггерах 110 и 112. Логика сравнения реализована в ПЛМ 103.

В режимах Ввод и Вывод (триг- ер НС устанавливается в О) на триггерах 110-112 устанавливаются сигналы, вьщаваемые через 126, 128, 127 элементы соответственно, в адресной части циклов магистрали.

и

0

14

26 входов

обозначенных как

ПЛМ 103 имеет

19 вькодов, Y,-Y,9.

Резким работы пшфратора 42 задает- ся- с триггеров 50-53. Последовательность и логические условия выработки выходных сигналов ПЛМ 103 в режиме Вывод описываются следующими соотношениями:

соответствуют временным диаграммам работы интерфейса ИУС (43) с точки зрения временных соотношений, логических условий и последовательности выдачи сигналов на управляющие шины интерфейса.

Последовательность и логические условия вьфаботки выходных сигналов ПЛИ 103 в режиме Ввод описьшаются следуюш ми соотношениями:

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для имитации отказов и сбоев ЭВМ | 1987 |

|

SU1564628A1 |

| Устройство для имитации неисправностей | 1988 |

|

SU1661766A1 |

| Устройство для контроля и перезапуска ЭВМ | 1987 |

|

SU1464162A1 |

| МОДЕЛИРУЮЩИЙ КОАП | 2013 |

|

RU2516703C1 |

| Имитатор абонентов | 1986 |

|

SU1325490A2 |

| Устройство для контроля неисправностей | 1991 |

|

SU1798787A1 |

| Устройство для контроля неисправностей | 1987 |

|

SU1564626A1 |

| Устройство для сопряжения электронно-вычислительной машины с группой внешних устройств | 1989 |

|

SU1734098A1 |

| Имитатор абонентов | 1983 |

|

SU1291987A1 |

| Устройство для сопряжения двух магистралей | 1989 |

|

SU1725223A1 |

Изобретение относится к области вычислительной техники и предназначено для имитации неисправностей в структурно-избыточных управляющих ВЫ числительных системах (УВС) при эк- спериментальном исследовании их надежности. Целью изобретения являет- .ся расширение области применения. Устройство для имитации неисправно- ; стей включает блок управления последовательностью введения неисправностей, содержащий узлы шинных формирователей и дешифратор адреса, коммутатор, схему сравнения, память, счетчик адреса, дешифратор, счетчик времени и модули имитации неисправностей, состоящие из блоков шинных формирователей, блоков памяти, счетчиков адреса, арифметико-логического блока, регистра данных,.дешифратора адреса, регистра управления и состояния, генератора тактовых импульсов, счетчика времени, шифратора управляющих сигналов, регистра управления, блока имитации отказов системы прерываний, блока управления магистрали. Модуль имитаи-ии неисправностей проводит имитацию отказов и сбоев различных компонентов ЭВМ, составлякищх ЗПВС. Устройство вьшолняет 12 различных команд имитации неисправностей.При этом иШти- руются физические неисправности модулей ЭВМ (ОЗУ, ПЗУ, УЗО) с исполь- , зова.нием режима прямого доступа к памяти - искажением состояния эле- , ментов модулей и информации в них, или же непосредственным воздействием на информащюнные и управляющие шины магистрали .ЭВМ. 2 э.п. ф-лы, 6 ил. i СЛ 1 4 4;: N1 сд

Триггеры 113-117 используются в циклах Ввод, и Вывод. Триггер 118 устанавливается сигналом Результат сравнения (PC) с выхода блока 30. Триггер 119 устанавливается в 1 по сигналам РС. и в О, если РС.

15

В режиме эмуляции данных nocxie- повательность выработки сигналов, будет следующей:

1 Yg Х4 X , -Х

Y ю

Y I

11

- Y -Y . Y - Л Л , Aj

.x,- x

В режиме эмуляции адреса будут вьщаваться следующие сигналы:

5 х.х;.х,-(х,, ®

Ф ).(Х,2 ® и

to ® ФХ,) (Х, ©Х,)

Н ® Ф Х) -( ©Xf)

Если бьши установлены два триггера 52 и 53 (режимы ЭА и ЭД), то после режима ЭА, т.е. установки триггера 118 в 1 следует режим ЭД, причем если триггер 119 уста новлен в 1, то режим ЭД не отличется от описанного вьппе, если 119 В О, то последовательность сигналов будет следующей:

Y 11

Y:

Y

lf

П

v v Y Y

- X -A j-Aj-A -A., X -Xj-X -X X -X /j-Xj. X Xg X Хз Х

Y

V

Логика функционирования шифратора 42 и блока 43 описаны для интерфейса ИУС, однако возможно изменени логики функционирования данных блоков для других интерфейсов.

Перед началом работы модуля 7 (после включения питания в ЭВМ 4) производится сброс устройства в исходное состояние. Сигнал Сброс производит запись нулей в триггеры 45-53 из блока 44, в 108-112 из блока 104, в 113 - 119 из блока 105, 133 - 135 из блока 43 и осуществляет сброс регистров 31, 37 и счетчика 39,

44477516

В исходном состоянии (перед началом выполнения команды имитации неисправностей) на входы ГШМ 29 Х - г будут поступать следующие сигналы (в дальнейшем приняты обозначения X г 1, , 0);

X , - Х4 выходы блока 28 в состоянии Отключено, команды с та- j 10 ким кодом нет;

Х5 - X j - триггеры 45-43 сброшены;

X , - операнды на входах блока 30 не равны;

X fJ- - регистр 31 сброшен; , Xt7 регистр 37 сброшен;

X fg, X f5 тактовые частоты.

X -г, - X i« - установлены в О после сигнала Сброс.

На входы X и- X . поступают 2 тактовые частоты.

После того, как произведена запись блоков 27 и 28, на счетчики 34 и 35 записывается первьш адрес (Адрес 1) и в регистр 37 записьша- ется режим работы модуля 7.

Началом выполнения первой коман5

0

ды служит появление сигналов X

Г6

X X 0 (режим работы - систем- 0 ный) или X 7 Xf4 X2(, 1 (режим работы одиночный)

После выполнения первой команды в ПЛМ 29 анализируется значение Х27« Если установлен признак следующей команды (Xj)- то производится наращивание значения счетчика 35 на +1.

Каждая из 12 описьшаемых ниже команд имитации включает выполнегше в определенной последовательности ,нескольких МОП. Набор команд имитации при необходимости может быть легко расширен. Для этого потребуется изменить только логику функционирования ПЛМ 29.

5

50 ЗАХ-Hi-BB-H-C -С - ЙСК- -ЗАП-ВЬШСЗ

Для выполнения команды 1 в блок .55 27 записаны 4 информационных слова, которые последовательно будут считаны из блока 27 при выполнении команды: код управления шифратора 42;

адрес ВУ (ЗУ) для ввода; код искажения; адрес ВУ( ЗУ) для вывода причем RTODoe и четвертое совпадают.

В регистре 37 записан системный режим работы устройства. При поступлении на вход имитатора 29, находящегося в исходном состоянии,

сигнал X

20

(X

20

X

I&

1) будет выда

сигнал Y и из блока 28 считан код 1 команды, который поступив на входы Х,-Х. После поступления кода 0001 на входы имитатора 29 при наличии 1 на входе X ,g (в дальнейшем по Xf) будут выработаны сигналы иУэ, т.е. считан блок 27 памяти и установлен в 1 триггер 49. По X fg произойдет запись кода управления в ш1фратор 42 с выхода блока 27 в блок 104 будет вьщан сигнал . Запись в блок 104 происходит по пе

реднему фронту Y

г«

Установка в 1

триггера 49 будет причиной начала

работы блока 43, который после захва- 25 ® имеющий выходы на три состояния)

та управления магистралью 14 выдает сигнал Х25- При получении X 25 по X |, ПЛМ 29 выдаст сигналы: Y (установка в 1 триггера 50), Y , (приращение +1 на счетчике 34 - п переднему фронту Ygg) и Y,5 (ШФ 32 на передачу адреса в магистраль 14 с выхода блока 27). После установки 3 1 триггера 50 на X ,(, вход имитатора 29 поступит 1 и по Х сигнал будет сброшен в О. Одновременно шифратор 42 начнет выполнять операцию- Ввод. В ходе ее выполнения он вьщает вначале сигнал Xj, затем Х24- При получении X t имитатора 29 по X будут выданы синалы: Y,5 (ШФ 32 - на прием информации с 14), Yjj- (приращение на +1 текущего содержимого счетчика 34) и УЗО (блок 30 - в режим сумматора по модулю 2). Т.о. на первьй вход блок 30 поступит код искажения с выхода блока 27, на второй - данные с маги страли 14, затем по Х, имитатора

29 будет выдан сигнал Yj, - произой

дет запись искаженного кода данных

с выхода блока 30 в регистр 31, который в результате этой операции установит сигнал Х|5 При поступлении Х,5 по X,g будет установлен триггер 48 (сигнал Y,) и сброшен триггер 50 (сигнал YI ) . На входы имитатора 29 поступят сигналы Xg и X , после чего по ,Х ,, будет сброшен Y э (выда

УЗ) и выдан YIJ (установлен триггер ВЫВ 51). При поступлении X,, на вход имитатора 29 по X ,д будет выдан Y35 (приращение адреса на счетчик 34), одновременно шифратор 42 начнет операцию Вывод.На выходе блока 27 т.о. будет установлен адрес ВУ (ЗУ), в которое производится запись искаженной информации с регистра 31. В процессе выполнения опера1дии Вывод шифратор 42 выдает сначала сигнал Хг-г при поступлении которого имитатор 29 выдает сигналы

5 Y ,3 (ШФ 32 - на передачу в магистраль 14 адреса с выхода блока 27), и Y, (установка триггера 45, в данном случае используемого для сброса ПЛМ 29 в исходное состояние), затем

0 и итaтop 29 сбросит УЭЭ (вьдаст УЗЗ ) и установит Y 33 (сигнал считывания регистра 31). Т.о. выходы блока 27 будут переведены в третье состояние (отключены), а регистр 31 (так0

о /

5

будет считан через ШФ 32 в магистраль 14. Паличие сигналов х X 21 Т9 будет причиной установки имитатор 29 в исходное состояние (если Xj7 признак следующей команды не установлен) или при совпадении этих сигналов будет вьщан сигнал Yj (приращение на счетчик 35 текущего значения адреса блока 28 на +1 - по переднему фронту Yj) и Y35 также блок 28 - в исходное состояние (если есть Х27)« Т.о. во втором случае на выходах блока 28 появится код следующей команды, к вьшолнению которой перейдет модуль 7.

вьт

-иск- ЗАЛ --ЗАХСИН- С/

С

СЗ

Для вьшолнения команды в блоке 27 записаны коды четырех информационных слов, которые будут считаны из блока 27 при выполнении команды в такой последовательности: адрес синхронизации (С); код искажения (С); код управления для шифратора 42 (СЗ); адрес вывода (С), причем адрес синхрониза дни и адрес вывода совпадают.

СЗ

Для вьшолнения команды в блоке 27 записаны коды 6 информационных слов, которые будут считаны из блока памяти в такой последовательности: код управления для шифратора 42; адрес для ввода (адрес ПЗУ); код искажения; код управления для шифратора

СИН ОШФ

X / С С

42; адрес синхронизации; код отключаемых устройств, причем второе 55 и пятое полностью совпадают.

От поступления кода 0011 на входы Х 4 имитатора 29, находящегося в исходном состоянии, и до установки триггера 48 в 1 выполнение дан-

,10

ной команды аналогично выполнению 1 команды. После того, как сигнал с выхода 48 поступит на Х имитатор

29 выдаст по : 35- сигнал приращения счетчика 34, после чего на выходе блока 27 появится код управления для шифратора 42, и по X ,д : Y - произойдет запись кода управления на блок 104; Y - ШФ. 32 - на

прием информации с магистрали 14; Yj - установка в 1 триггера 46,

При поступлении Х сигнал Y35- сбрасывается,(Y35) и имитатор 29 выставляет сигнал Y, устанавливающий g в 1 триггер 45 по Х, . По X , будут вьщаны; . - приращение счетчи- ка 34 (на выходе блока 27 появится адрес синхронизации); Yзо - блок 30- в режим сравнения.

2Q 25

Таким образом модуль 7 ожидает появления адреса на магистрали 14 (обращения к ПЗУ). При совпадении адресов на входах блока 30 будет выдан сигнал Х| , появление которого на имитаторе 29 вызовет по Х : - сброс сигнала 35, Y ,,7- .установку триггера 53; по X ,9 (и при появлении

Код 0100 служит для эмуляции работы устройства в режиме Приемник и

X 1з) будет вьщан Y 35 считан из бло- Q включает 14 микроопераций, вьшолняю- ка 27 код отключаемых устройств (на- в такой последовательности:

ЭА-УЭД СX X Ч сз с с

Для выполнения команды в блок 27 записаны коды 6 слов, которые будут считаны с такой последовательности: код з равления для шифратора 42; код отключаемых устройств; адрес, синхронизации; код искажения; код управления для шифратора 42; адрес устройства (ВУ или ЗУ), причем тре- тий и шестой адреса будут совпадать, о После поступления кода 0100 на входы имитатора 29, находящегося в исходном состоянии, будут вьщаны следующие сигналы по : Y ,,. - установка триггера 52; Y

)5

33

считывание блока 27 (кода управления для шифратора 42); по Х.: - запись кода на блок 104,

После поступления сигнала Х., по Xjg будут выданы сигналы: Y зу - приращение на счетчик 34; Y, - установка триггера 53; по Х : Yj - запись регистра 40 кодом с выхода блока 27.

0

g

пример ПЗУ), затем по X g - Y о - этот код будет записан на регистр 40. Установка триггера 53 в 1 инициирует работу шифратора 42, который в процессе работы вьвдаст сигнал по которому имитатор 29 выдаст: Y «ШФ 32 - на передачу; Y д, - выходы L блока 27 - в третье состояние;Y32 сигнал считывания регистра 31; Y, установка триггера 46 в 1.

После окончания происходит сброс имитатора 29 в исходное тояние (или выполнение следующей команды - см. описание работы предыдущих команд).

Код 0100 служит для эмуляции работы устройства в режиме Приемник и

ЗАП- ЗАХ X

СЗ

выв

При установке триггера 53 на вход имитатора 29 поступит X у,, после чего будут выставлены сигналы по X : - установка триггера 45;. Yj - сброс сигнала 35,

По X 13 после поступления X j. будут вьщаны: Y 35 - сигнал приращения счетчика 34; Yao перевод блока 30 в режим сравнения; Y (j сигнал подключения ШФ 32 на прием информации с магистрали 14,

Далее команда выполняется аналогично команде 2 (см. описание работы команды 2 после поступления X Т4)

Работа команд для двух других ти пов устройств (источник и источник/ /приемник) строится аналогично.

5, Команда для источгшка включает 9 микроопераций:

-син

l;./

23

В блоке 27 для выполнения этой команды будет записано 4 кода - 3 аналогичны с тремя первыми из команды 4, четвертый - слово данных для вьдачи в канал. Код команды - 1100.

Для источника/приемника (код команды - 1101) отличие от команд 4 и 5 будет заключаться только в том, что здесь будет анализировать- ся значение триггера 119 (Х) и в зависимости от его значения команда 6 будет содержать 14 микроопераций (полностью аналогичных с командой 4) или 9 - с командой 1100.

Для выполнения команды 6 в блоке 27 записьшается 7 слов (6 - как для 4 и седьмое слово данных - для вьщачи в магистраль 14),

ОПР -V ЗАХ С

сз сз

Для вьшолнения команды 7 в блоке 27 записываются 4 информационных слова, которые будут считаны из блока 27 при выполнении команды в такой последовательности: код для записи в регистр 148; код для записи в регистр 147; код управления для шифратора 42; адрес ВУ (ЗУ), для которого имитируется потеря прерывания .

При получении кода 0101 на входы имитатора 29, находящегося в исходном состоянии, будут выданы по X j: Yj,j - сигнал считывания блока 27; YS - установка триггера 47; по Y24, Y 26 сигналы записи регистров 147, 148.

Так как регистры 147 и 148 - 8- разрядные регистры, а блок 27 - 16- разрядные, то запись в регистры 147 и 148 происходит в один такт. После поступления на вход имитатора 29 сигнал , означающего, что на магистрали 14 произошла выработка прерывания по. отключенному уровню (одной из ШПРО-ШГ1Р7), по X ,g будут выданы: Yg - установка триггера 49; YJ5 приращение адреса на счетчик 34.

7524

Дгглее команда работает аналогично команде 3 (от микрооперации ЗАХ до С), т.е. производится цикл Ввод, который сбрасывает триггер требования прерывания в устройстве его выставившем. Результатом опера- Щ1И будет сброс Xjt. после чего имитатор 29 возвратится в исходное со- стояние.

СЗ - Э А - СМ - С

/г

/

сз

Для вьшолнения команды в блоке 27 должны быть записаны 3 информационных слова: код для записи на регистр 146; код управления для шифратора 42; адрес синхронизации.

После поступления на входы X -Х 4 имитатора 29 кода 0110 (имитатор 29 - в исходном состоянии) по X ,g будут вьщаны следз юище сигналы: Y33 - считывание блока 27; Yj - установка триггера 46. По X будет вьщан сигнал Y г - запись регистра 146.

После поступления Х с выхода триггера 46 по X g имитатор 29 выдаст: Y 35- наращивание счетчика 34; Y, - ШФ 32 - на прием информации с магистрали 14. По X ,: Y jij запись в блок 104; Y ,5 - установка триггера 52.

После установки Х выходах имитатора 29 произойдут следующие изменения: Y35 - сброшен сигнал 35; YJ - установлен триггер 45,

При поступлении X имитатор 29 вьщаст: Y35 приращение счетчика 34 Y 30 - блок 30 в режим сравнения.

При равенстве адресов с выхода блока 27 и ШФ 32 (адрес с магистрали 14),так как произойдет обращение к устройству, выставившему прерывание со стороны ЦП 9 (1-п), шифратор 42 выдаст сигнал ШШПА и X j., при поступлении которого на вход имитатора 29 будет вьщан по X ,g : сброс регистра 146, по X,, имитатор 29 возвратится в исходное состояние.

Т.о. будет проимитировано несанкционированное (ложное) прерывание , устройства, в результате чего ЦП 9 (1-п) перейдет к подпрограмме его обработки.

ОШФ С

сз с

-эд

Для выполнения команды в блоке 27 записывается 3 слова, считываемых из блока 27 в такой последовательности: код от1шючаемых устройств; адрес синхронизации; данное (код команды)..

После поступления кода 0111 на входы имитатора 29 будут вьща- ны следующие сигналы по X g : Y 33 - считывание блока 27 (на выходе) блока 27 - код отключаемого устройства); по X (д : YJO - сигнал записи в регистр 40; Y, - установка триггера 45. С выхода триггера 45 на вход имитатора 29 поступит Х5 после чего имитатор 29 вьщаст по ращивание счетчика 34; Y ,9 - ШФ 32 на прием; Yjo блок 30 в режим сравнения; Y,7 - установка триггера 53.

При установке в 1 триггера 53 начнет работать шифратор 42, т.е. после прихода на него сигнала PC 1 с блока 30 будет вьщан сигнал Х,з , после чего имитатор 29 выдает

После получения кода 1010 на вх ды Xf-X4 имитатора 29 на выходе 33. будет вьщан сигнал считывания блока 27 по X /j. При поступлении фазы Х,д содержимое с выхода блока 27 будет записано сигналом Хг н регистр 147. Затем имитатор 29 воз вратится в исходное состояние.

Набор комавд модуля 7 легко мож быть расширен за счет вьшолнения других режимов работы и соответствующих им команд.

30

35

40

45

по X

1Г

3s-

по Х«: Yi5 - ШФ 32 на передачу в магистраль 14; Y зу - наращивание счетчика 34; Yj - сброс триггера 45.

После окончания действия сигнала 1 (Х.,) имитатор 29 возвращается в исходное состояние.

Команды 10-12 включают только од-50

Формула изобретени

ну операцию - соответственно запись .55 модулей имитации неисправностей в

регистров 40, 146 и 147. Для вьшол- ;нения этих команд в блок 27 записывается- 1 слово.

5

При поступлении кода 1000 на входы ,. имитатора 29 на выходе Y появится сигнал считыватш (по Х,), по будет выдан сигнал Yго - записи регистра 40. После этого имитатор 29 - в исходное состояние.

При поступлении кода 1001 на входы имитатора 29 на выходе

ээ

(по X j) появится сигнал Y

33

0

считывания блока 27, по Х,у содержимое с выхода блока 27 будет записано в регистр 146 сигналом Y. После вьдачи сигнала на имитатор 29 - в исходное состояние,

После получения кода 1010 на входы Xf-X4 имитатора 29 на выходе 33. будет вьщан сигнал считывания блока 27 по X /j. При поступлении фазы Х,д содержимое с выхода блока 27 будет записано сигналом Хг на регистр 147. Затем имитатор 29 возвратится в исходное состояние.

Набор комавд модуля 7 легко может быть расширен за счет вьшолнения других режимов работы и соответствующих им команд.

0

5

40

45

50

Формула изобретения

блок управления последовательностью введения неисправностей, причем выходы номера неисправности К модулей

имитации неисправностей соединены с группой входов номера неисправности блока управления последовательностью введения неисправностей, группа разрешающих выходов которого подключена к входам разреше шя модулей имитации неисправностей, входные инфор ; мационные адресные пины и шины сброca К модулей имитации неисправностей, Q ответственно с входами записи первходная адресная шина и двунаправлен- ная информационная шина блока управления последовательностью введения неисправностей являются входами и выходами устройства для подключения к соответствующим шинам управляющей ЭВМ, группы информационных и управляющих входов-выходов к модулей имитации неисправностей являются входами-выходами устройства для подлкюче- ния к соответствующим шинам контролируемых ЭВМ, причем в каждый модуль имитации неисправностей введены два блока шинных формирователей, арифметико-логический блок, второй счетчик адреса, дешифратор адресэ5 счетчик времени, шифратор зшравляю- шзих сигналов, элемент задержки,груп- па триггеров,регистр управлеьшя, блок имитации отказов системы прерывания, шифратор управления магистралью, блок захвата магистрали, причем, группа выходов первого блока памяти соединена с группами информационных входов первого блока щин- ных формирователей, регистра управления, блока имитации отказов системы прерывания, шифратора управле- .ния магистралью и первой группой информационных входов арифметико-логического блока, группа информационных выходов которого соединена с группой информационных входов регистра данных, грзшпа информационных выходов которого соединена с группой . информационных входов первого блока шинных формирователей, группа выходов которого соединена с второй группой информационных входов арифметико-логического блока, а группа вхо20

.вого, второго блоков памяти; син- хровходом второго счетчика адреса, входом записи регистра управляющего слова и синхровходом первого счетчи- g ка адреса, группы информационных входов второго счетчика адреса и дешифратора адреса соединены с входной адресной шиной модуля, группа входов второго блока шинных формирователей является входной информационной шиной блока, выходы шифратора управляющих сигналов соединены

соответственно с установочными и сбросовыми входами триггеров группы, 25 управляющим входом первого блока ных формирователей, синхровходами и входами сброса регистра управления

.блока имитации отказов системы прерывания, шифратора управления магистралью, входом режима арифметико- логического блока, входами записи и чтения регистра данных, входами чтения первого и второго блоков памяти, счетными входами первого и второго счетчиков адреса и через элемент задержки - синхровходом счетчика времени, выходы триггеров группы, вькод результата арифметико-логического блока, выход готовности регистра данных, выходы регистра управляюще30

35

40

45

го слова, первый и второй выходы генератора тактовых импульсов, выход разрешения блока имитации отказов системы прерывания, группа управляющих выходов шифратора управления магистралью, выход захвата блока захвата магистрали, выход счетчика времени, выход разряда второго блока памяти соединены с соответствующими

входами шифратора управляю1цих сигна- дов-выходов является группой информа- 50 лов, выход результата арифметико-ло- ционных входов-выходов модуля, груп-гического блока, выход готовности

па выходов второго блока памяти со-регистра данных, выходы соответствуюединена с первой группой входов шиф- щих триггеров группы и выход генера- ратора управляюштнх сигналов и стора тактовых импульсов соединены с

группой информационных входов счетчи- 55 группой режимных входов шифратора ка времени, группа выходов второго. управления магистралью, вход захвата

блока шинных формирователей соеди-блока захвата магистрали соединен с

нена с группами информационных вхо«.-выходом соответствующего триггера

дов первого и второго бл оков памяти и регистра управляющего слова, группа адресных входов второго блока памяти соединена с группой выходов вто-- рого счетчика адреса, которая является также выходом номера неисправности блока, с первого по пятьп выходы дешифратора адреса соединены co0

.вого, второго блоков памяти; син- хровходом второго счетчика адреса, входом записи регистра управляющего слова и синхровходом первого счетчи- g ка адреса, группы информационных входов второго счетчика адреса и дешифратора адреса соединены с входной адресной шиной модуля, группа входов второго блока шинных формирователей является входной информационной шиной блока, выходы шифратора управляющих сигналов соединены

соответственно с установочными и сбросовыми входами триггеров группы, 5 управляющим входом первого блока ных формирователей, синхровходами и входами сброса регистра управления

.блока имитации отказов системы прерывания, шифратора управления магистралью, входом режима арифметико- логического блока, входами записи и чтения регистра данных, входами чтения первого и второго блоков памяти, счетными входами первого и второго счетчиков адреса и через элемент задержки - синхровходом счетчика времени, выходы триггеров группы, вькод результата арифметико-логического блока, выход готовности регистра данных, выходы регистра управляюще0

5

0

5

го слова, первый и второй выходы генератора тактовых импульсов, выход разрешения блока имитации отказов системы прерывания, группа управляющих выходов шифратора управления магистралью, выход захвата блока захвата магистрали, выход счетчика времени, выход разряда второго блока памяти соединены с соответствующими

группы, а вход сброса является входом сброса модуля, управляющий выход блока захвата магистрали соеди- нен с синхровходами триггеров группы и входом сброса регистра данных, группа выходов регистра управления, группы входов и выходов прерываний блока имитации отказов системы прерывания, группы входов-выходов шифратора управления магистралью и блока захвата магистрали образуют группу управляюпчих входов-выходов модуля. .

йуют входную адресную шину блока, группа входов-выходов узла шинных формирователей является двунаправленной информационной шиной блока.

I

тз

f(HH /

Фае.1

Си

Jот мин 7(1) Y Си

от nil Н 7(2} Т СД

от f1HH7(3)

СД omf1HH7(n)

ШФ 17

ОЗУ 21

Cfl 12

V

D/I 16

Фиг. 2

коп

19

Л

V

ее 20

-V

)

т

23

рр

рр

уЧ(7Ш7(1)

UZ. рр

(2)

рр

к мин 7(31

РР кМИН7{п)

СВ 2

:

Ф5

/

Фиг.з

вв

ФигЛ

w

шар

C5

т

нШРЗН

W

м

Фаг.5

Т

шзп

mt

Г

шпвз

на 14

ъ

ШЗ/lff

т на 14

ШРЗПбы

HoW

т с

к

ее

а

| Устройство для имитации сбоев и неисправностей цифровой вычислительной машины | 1985 |

|

SU1265779A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для имитации сбоев | 1985 |

|

SU1264185A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1988-12-15—Публикация

1987-03-10—Подача