1C

а

Изобретение относится к автоматике и вычислительной технике и может быть использовано для обработки и определения эффективности программно-аппаратных средств контроля и обеспечения надежности ЦВМ и устойчивых к сбоям ЦВМ с мажоритированием

Целью изобретения является расширение функциональных возможностей устройства за счёт увеличения количества различных вариантов искажений вносимых в считываемую программу.

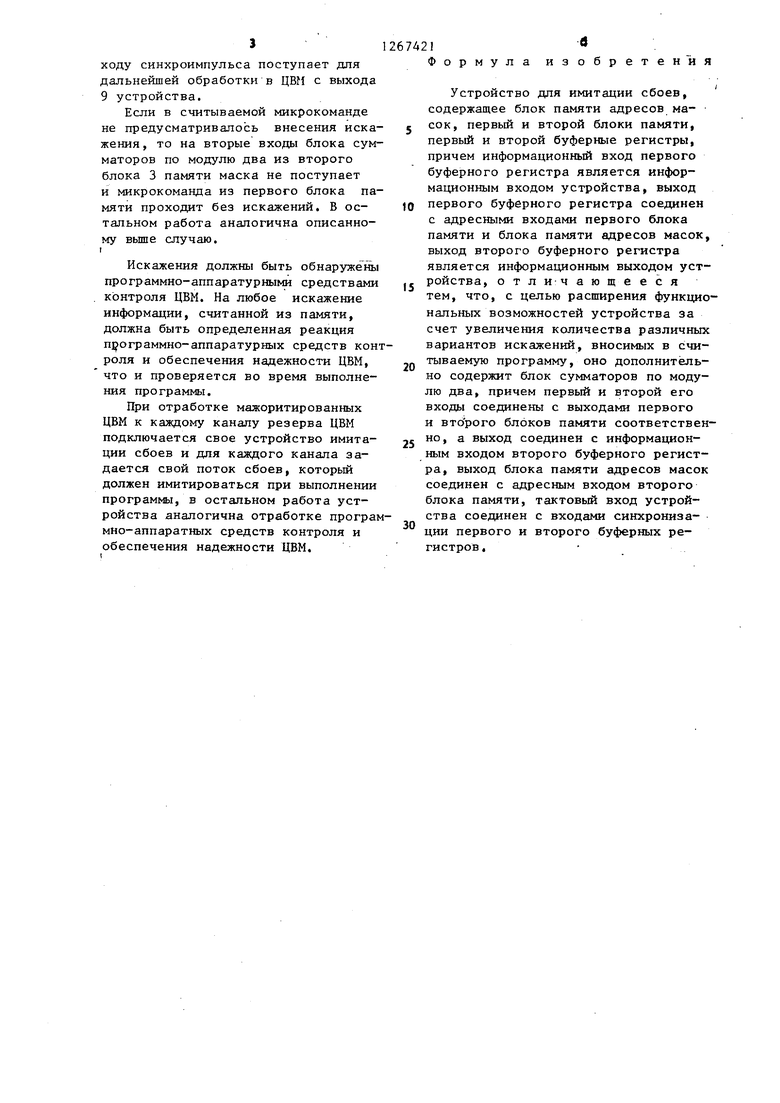

На чертеже показана функцийнальная схема устройства.

Устройство содержит блок 1 памяти адресов масок, первый 2 и второй 3 блоки памяти, блок 4 сумматоров по модулю два, первый.5 и второй 6 буфер1Ш1е регистры, информационный 7 и тактовый 8 входы устройства, выход . 9 устройства.

Блок 1 памяти адресов масок предназначен для записи и хранения адресов масок с целью выбора соответствующей маски, накладываемой на считываемую микрокоманду.

Первый блок 2 памяти предназначен для .записи и хранения неискаженных микрокоманд.

Второй блок 3 памяти предназначен для записи и хранения набора масок, определяющих вид искажений в считываемых микрокомандах.

Блок 4 сумматоров по модулю два предназначен для наложения на считыБаемую из первого блока 2 памяти микрокоманду кода маски, поступившей из второго блока 3 , или выдачи неискаженной микрокоманда из первого блока 2 памяти,

Первый регистр 5 предназначен для приема из ЦВМ, хранения и выдачи ,первьй блок 2 памяти и блок 1 памяти адресов масок адреса считываемой микрокоманды ,

Второй регистр 6 предназначен для приема из блока 4 сумматоров по модулю два искаженной или неискаженной микрокоманды, хранения ее и выдачи для дальнейшей обработки в ЦВМ,

Устройство для имитации сбоев работает следующим образом.

При отработке и проверке эф эективности аппаратно-программных средств обеспечения надежности ЦВМ к ней вместо основной памяти подключается устройство для имитации сбоев.

Устройство позволяет имитировать произвольное количество сбоев следующих типов; искажение одного раз- . ряда информации в одной ячейке блока памяти, искажение произвольного числа разрядов в одной ячейке блока памяти; искажение одного разряда в группе ячеек блока памяти; искажение произвольного числа разрядов в группе ячеек блока памяти.

Перед выполнением программы определяется поток сбоев, который должен имитироваться, В одноразрядный блок 1 памяти по адресам ячеек первого 2 блока памяти, в которых необходимо исказить микрокоманды, записываются адреса масок, обеспечивающих внесение выбранного вида искажения,

В первом блока 2 памяти хранятся программы, с которыми ведется работа, Б исходном состоянии все элементы памяти устройства находятся в нулевом состоянии за исключением блока памяти адреса масок, в котором записаны по адресам микрокоманды первого блока 2 памяти адреса масок, определяющих вид вносимого искажения, первого блока 2 памяти, в котором хранятся программы, с которыми ведется работа, и второго блока 3 памяти, в котором записаны маски, определяющие вид искажения, Цепи установки в исходное состояние на черте-, же условно не показаны,

Работа устройства начинается после поступления на вход 7 устройства адреса считываемой микрокоманды,

По синхроимпульсу, поступающему на тактовьй 8 вход устройства, информация записывается в первый регистр 5, а по, следующему - из первого регистра 5 поступает на адресные входы первого блока 2 памяти и блока 1 памяти адресов масок. Происходит считывание информации, записанной по этому адресу в первом блоке 2 памяти, далее она поступает на первые информационные входы блока 4 сумматоров по модулю два. Одновременно по этому же адресу из блока I памяти адресов масок считывается адрес маски и поступает во второй блок 3 памяти, откуда по этому адресу считывается маска, которая в блоке накладаваеися на микрокоманду, поступившую из первого блока 2 памяти, С выхода блока сумматоров по модулю Два микрокоманда поступает на второй регистр 6, откуда по

ходу синхроимпульса поступает дпя дальнейшей обработки в ЦВМ с выхода 9 устройства.

Если в считываемой микрокоманде не предусматривалось внесения искажения, то на вторые входы блока сумматоров по модулю два из второго блока 3 памяти маска не поступает и микрокоманда из первого блока памяти проходит без искажений. В остальном работа аналогична описанному вьше случаю. I

Искажения должны быть обнаружё нъ nporpaMMHo-annapaTypHbiNoi средствами контроля ЦВМ. На любое искажение информации, считанной из памяти, должна быть определенная реакция программно-аппаратурных средств конроля и обеспечения надежности ЦВМ, что и проверяется во время выполнения программы.

При отработке мажоритированных ЦВМ к каждому каналу резерва ЦВМ подключается свое устройство имитации сбоев и для каждого канала задается свой поток сбоев, который должен имитироваться при выполнении программы, в остальном работа устройства аналогична отработке программно-аппаратных средств контроля и обеспечения надежности ЦВМ.

7421

Формула изобретен и Я

Устройство дпя имитации сбоев, содержащее блок памяти адресов ма- сок, первый и второй блоки памяти, первый и второй буферные регистры, причем информационный вход первого буферного регистра является информационным входом устройства, выход

JO первого буферного регистра соединен с адресными входами первого блока памяти и блока памяти адресов масок, выход второго буферного регистра является информационным выходом устройства, отл и-чающееся

15 тем, что, с целью расширения функциональных возможностей устройства за счет увеличения количества различных вариантов искажений, вносимых в счи„ тываемую программу, оно дополнительно содержит блок сумматоров по модулю два, причем первый и второй его входы соединены с выходами первого и второго блоков памяти соответствен-

-, но, а выход соединен с информационным входом второго буферного регистра, выход блока памяти адресов масок соединен с адресным входом второго блока памяти, тактовый вход устройства соединен с входами синхрониза30ции первого и второго буферных регистров.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для имитации сбоев | 1985 |

|

SU1264185A1 |

| Устройство для имитации сбоев | 1983 |

|

SU1107126A1 |

| Устройство для имитации сбоев | 1985 |

|

SU1298925A2 |

| Устройство для управления восстановлением микропрограмм при сбоях | 1982 |

|

SU1056193A1 |

| Микропрограммное устройство управления | 1981 |

|

SU1016782A1 |

| Устройство для имитации сбоев | 1985 |

|

SU1297056A1 |

| Микропрограммное устройство управления с контролем и восстановлением | 1984 |

|

SU1242947A1 |

| Микропрограммное устройство управления с контролем и восстановлением | 1983 |

|

SU1120337A1 |

| Генератор тестовых воздействий | 1987 |

|

SU1439564A1 |

| Микропрограммный процессор с самоконтролем | 1980 |

|

SU1007109A1 |

Изобретение.относится к области автоматики и вычисли тельной техники и может быть использовано для обработки и определения эффективности программно-аппаратных средств контроля и обеспечения надежности ЦВМ и устойчивых к сбоям ЦВМ с мажоритированием. Целью изобретения является расширение функциональных возможностей устройства за счет увеличения количества различных вариантов искажений, вносимых в считываемую программу. Устройство содержит блок памяти адресов масок, перв1ж и .второй блоки памяти, блок сумматоров по модулю два, первый и второй буферные регистры. 1 ил. С .S, (Л с:

| Устройство для имитации сбоев цифровых вычислительных машин | 1980 |

|

SU879592A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Устройство для имитации сбоев | 1983 |

|

SU1107126A1 |

| Приспособление для получения кинематографических стерео снимков | 1919 |

|

SU67A1 |

Авторы

Даты

1986-10-30—Публикация

1985-04-11—Подача