Изобретение относится к цифровой вычислительной технике и может быть использовано для отработки и опреде- ления эффективности программно-аппаратных средств контроля и обеспечения надежности ЦВМ, устойчивых к сбоям.

Целью изобретения является сокращение аппаратурных затрат.

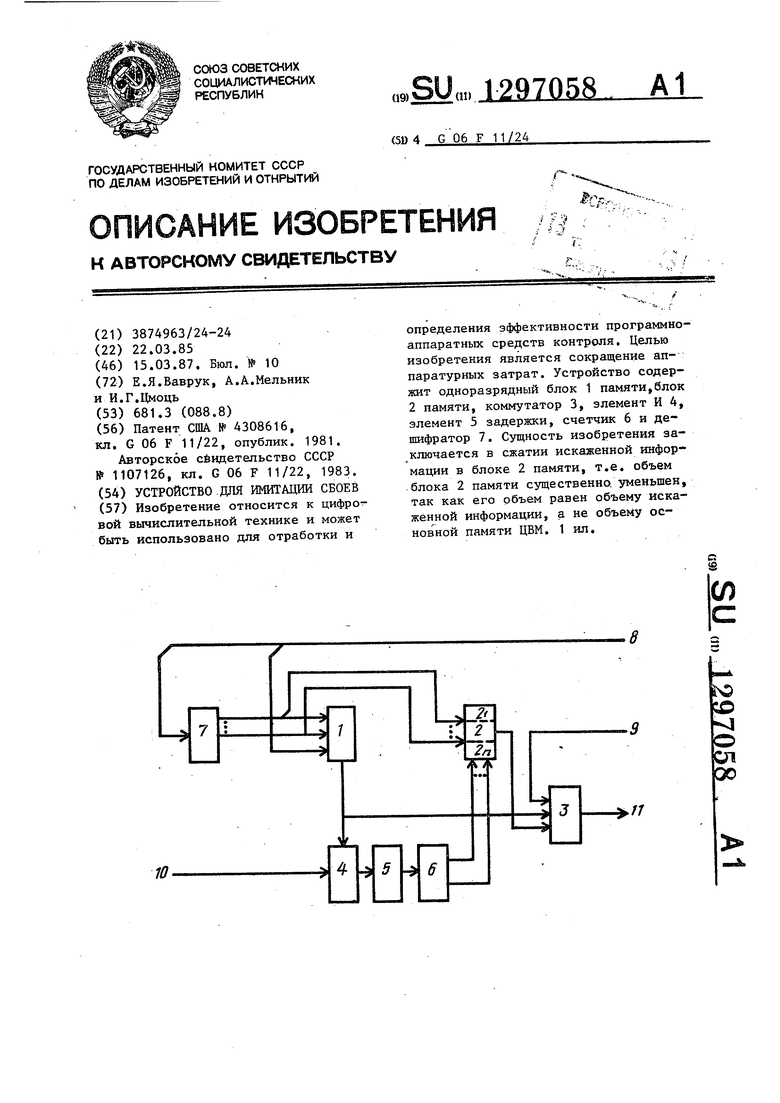

На чертеже приведена функциональная схема устройства для имитации сбоев.

На чертеже приняты следующие обозначения: одноразрядный блок 1 памяти, блок 2 памяти, коммутатор 3, элемент

20

25

30

И 4, элемент 5 задержки, счетчик Ь дешифратор 7, старшие разряды группы адресных входов 8 устройства,информационный вход 9 устройства,вход 10 задания режима имитации сбоя,информационный выход 11 устройства.

Устройство работает следующим образом.

По сигналу начальной установки (на чертеже не показан) счетчик 6 устанавливается в нулевое состояние. При поступлении на вход 8 устройства адреса происходит считывание информации из одноразрядного блока 1, Старшие разряды адреса, продешифрирован- ные дешифратором 7, служат сигналом выборки соответствунхцей микросхемы блоков памяти 1 и 2, а младшие разряды адресного входа устройства служат адресом считывания микросхемы блока 1 памяти. По тому же адресу считывается информация с основной памяти ЦВМ, поступающая на вход 9 устройства. Если на выходе одноразрядного блока 1 памяти единица, то коммутатор 3 коммутирует на выход 11 сигнал с выхода блока 2 памяти, если на выходе блока 1 памяти О, то на ыход коммутатора 3 поступает сигнал с входа 9 устройства. При наличии единицы на входе Ш устройства и единицы на вькоде блока 1 единичный сигнал появляется на выходе элемента И 4, задерживается на элементе заержки 5 и увеличивает значение счет- ика 6 на -i-l. Следующая искаженная нформация считывается не с нулевого дреса (начальное состояние счетчи О

40

45

35

ВНИИПИ Заказ 782/5 Тираж 673 Подписное Произв.-полигр. пр-тие, г. Ужгород, ул. Проектная, 4

ка 6), ас единичного. Время задержки элемента 5 задержки должно быть больше времени реакции программно- аппаратных средств контроля ЦВМ. Информация с выхода 11 устройства поступает в ЦВМ, при этом в одном случае (единичное значение соответствующей ячейки блока 1 памяти) в ЦВМ поступает искаженная информация, а

в другом (нулевое значение соответствующей ячейки блока 1 памяти) искажение должно быть обнаружено программно-аппаратными средствами контроля ЦВМ и последние должны соответствующим образом на них прореагировать. Адресная часть блока 1 памяти равна адресности основного блока памяти ЦВМ.

20

Формула изобретения

5

0

О

0

5

Устройство для имитации сбоев, содержащее одноразрядный блок памяти, блок памяти и коммутатор, причем информационный вход устройства соединен с первьм информационным входом коммутатора, выход которого является информационным выходом устройства, выход одноразрядного блока памяти соединен с управляющим входом коммутатора, выход блока памяти соединен с вторым информационным входом коммута- . тора, младшие разряды группы адресных входов устройства соединены с первой группой адресных входов одноразряд- 5 кого блока памяти, отличающееся тем, что, с целью сокращения аппаратурных затрат,- в устройство введены элемент И, элемент за- , держки, дешифратор и счетчик, причем вход задания режима имитации сбоя устройства соединен с первым входом элемента И, выход одноразрядного блока памяти соединен с вторым входом элемента И, выход которого через элемент задержки соединен с счетным входом счетчшса, выход которого соединен с первой группой адресных входов блока памяти, старшие разряды группы адресных входов устройства соединены с входами дешифратора, вы-, ходы которого соединены с вторыми группами адресных входов одноразрядного блока памяти и блока памяти.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для имитации сбоев | 1985 |

|

SU1297056A1 |

| Устройство для имитации сбоев | 1983 |

|

SU1107126A1 |

| Устройство для имитации сбоев | 1985 |

|

SU1298925A2 |

| Устройство для имитации сбоев | 1985 |

|

SU1267421A1 |

| Устройство для отладки программ | 1986 |

|

SU1327112A1 |

| Устройство для имитации сбоев | 1985 |

|

SU1264185A1 |

| Устройство для контроля оперативных запоминающих блоков | 1980 |

|

SU890442A1 |

| Устройство для имитации сбоев цифровых вычислительных машин | 1985 |

|

SU1300648A2 |

| Микропрограммное устройство управления | 1983 |

|

SU1100624A1 |

| Имитатор канала | 1987 |

|

SU1425675A2 |

Изобретение относится к цифровой вычислительной технике и может быть использовано для отработки и определения эффективности программно- аппаратных средств контроля. Целью изобретения является сокращение аппаратурных затрат. Устройство содержит одноразрядный блок 1 памяти,блок 2 памяти, коммутатор 3, элемент И 4, элемент 5 задержки, счетчик 6 и дешифратор 7. Сущность изобретения заключается в сжатии искаженной информации в блоке 2 памяти, т.е. объем .блока 2 памяти существенно, уменьшен, так как его объем равен объему искаженной информации, а не объему основной памяти ЦВМ. 1 ил. ю X) о сд эо

| Патент США № 4308616, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Приспособление для изготовления в грунте бетонных свай с употреблением обсадных труб | 1915 |

|

SU1981A1 |

| Устройство для имитации сбоев | 1983 |

|

SU1107126A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-03-15—Публикация

1985-03-22—Подача