Изобретение относится к вычислительной технике и может быть использовано в системах автоматического управления на базе ЭВМ для контроля выполнения программ на ЭВМ и восстановления вычислительного процесса при сбоях о

Цель изобретения - повышение достоверности контроля.

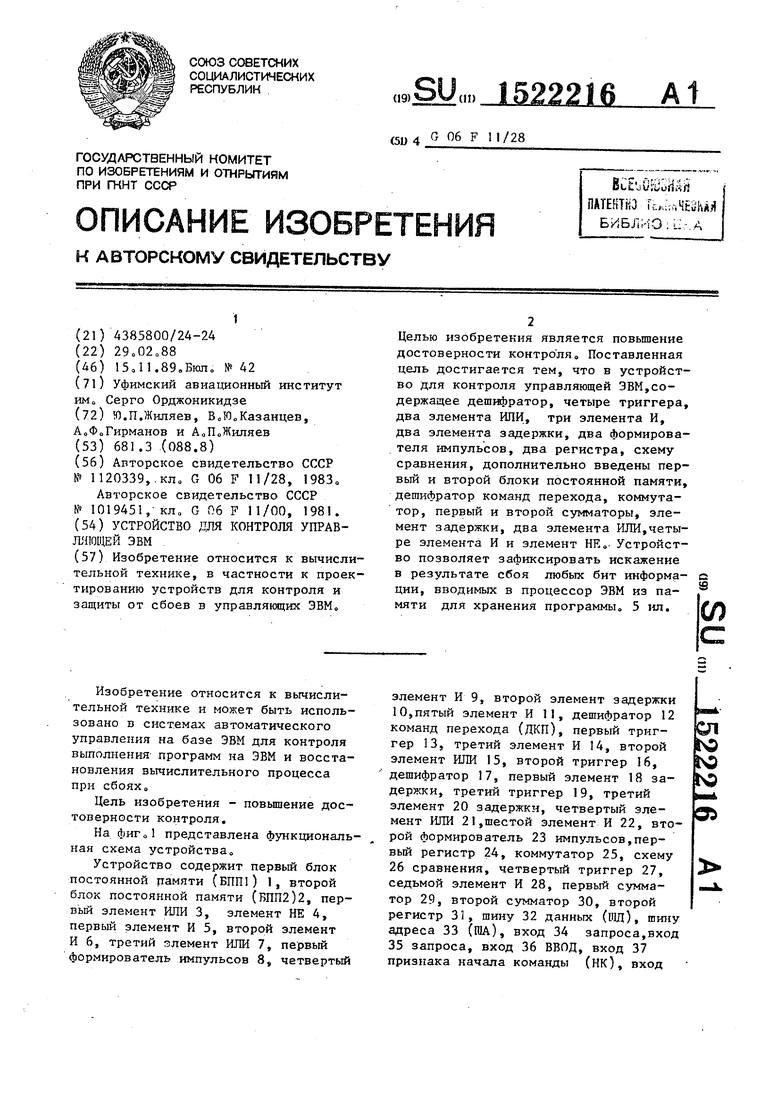

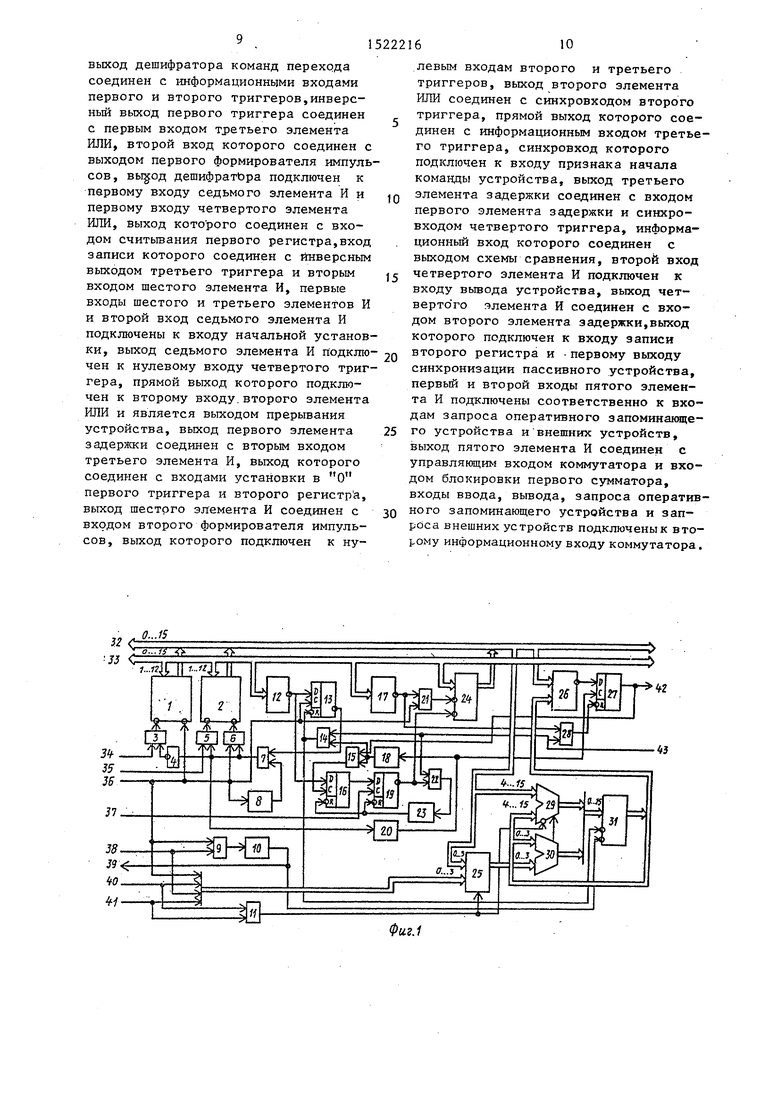

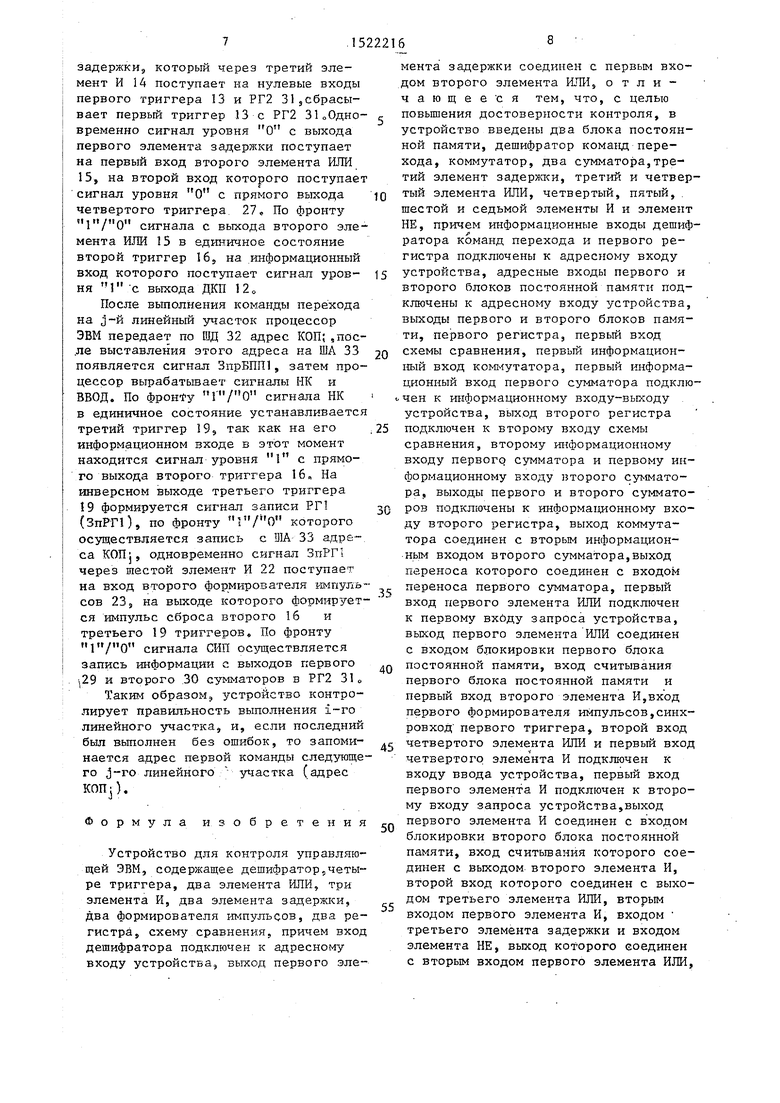

На фиг о 1 представлена функциональная схема устройства.

Устройство содержит первый блок постоянной памяти (БПШ ) 1, второй блок постоянной памяти (БПП2)2, первый элемент ИЛИ 3, элемент НЕ 4, первьй элемент И 5, второй элемент И 6, третий элемент ИЛИ 7, первый формирователь импульсов 8, четвертый

элемент И 9, второй элемент задержки 10,пятый элемент И 11, дешифратор 12 команд перехода (ДКП), первый триггер I3, третий элемент И 14, второй элемент ИЛИ 15, второй триггер 16, дешифратор 17, первый элемент 18 задержки, третий триггер 19, третий элемент 20 задержки, четвертый элемент ИЛИ 21,шестой элемент И 22, второй формирователь 23 импульсов,первый регистр 24, коммутатор 25, схему 26 сравнения, четвертый триггер 27, седьмой элемент И 28, первый сумматор 29, второй сумматор 30, второй регистр 31, шину 32 данных (ИЩ), шину адреса 33 (ША), вход 34 запроса,вход 35 запроса, вход 36 ВВОД, вход 37 признака начала команды (НК), вход

:л

ю э o

38 сигнала ВЫВОД, вход 39 синхронизации пассивного устройства (СИП), вход АО запроса оперативного запоминающего устройства (ЗпрОЗУ), вход 41 запроса внешних устройств (ЗпрВУ), вход 42 сигнала прерьгоания (ПРЕР), вход 43 сигнала начальной установки (НУ)е

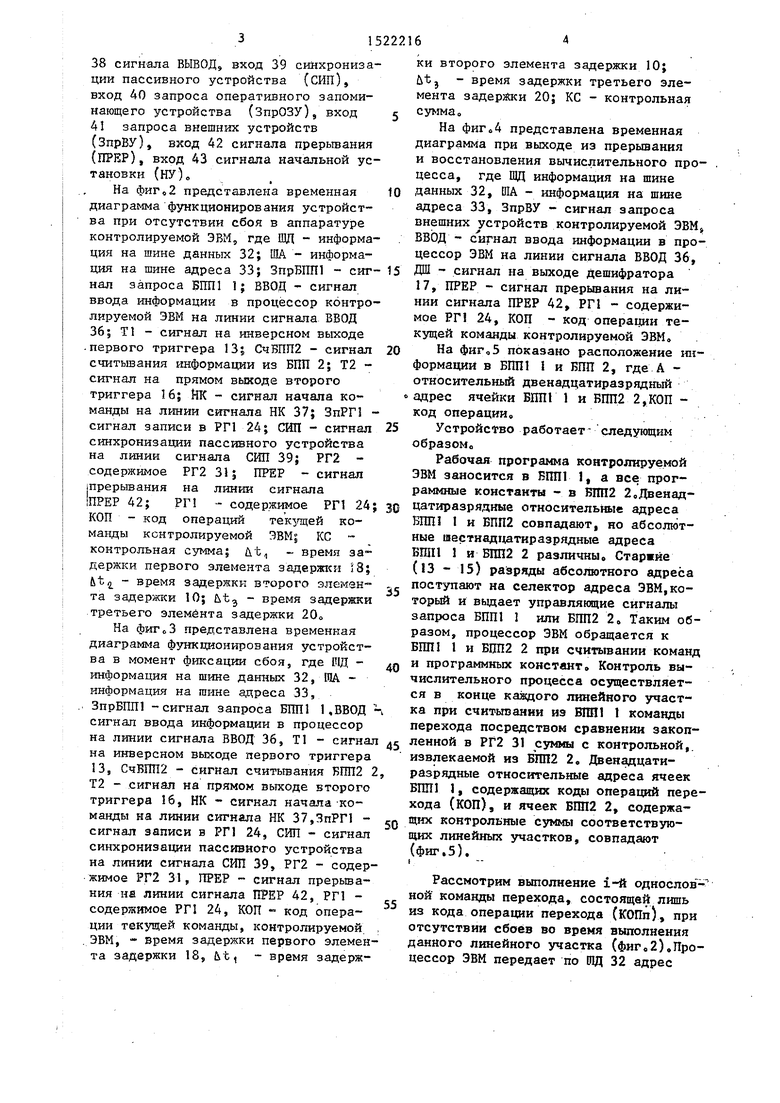

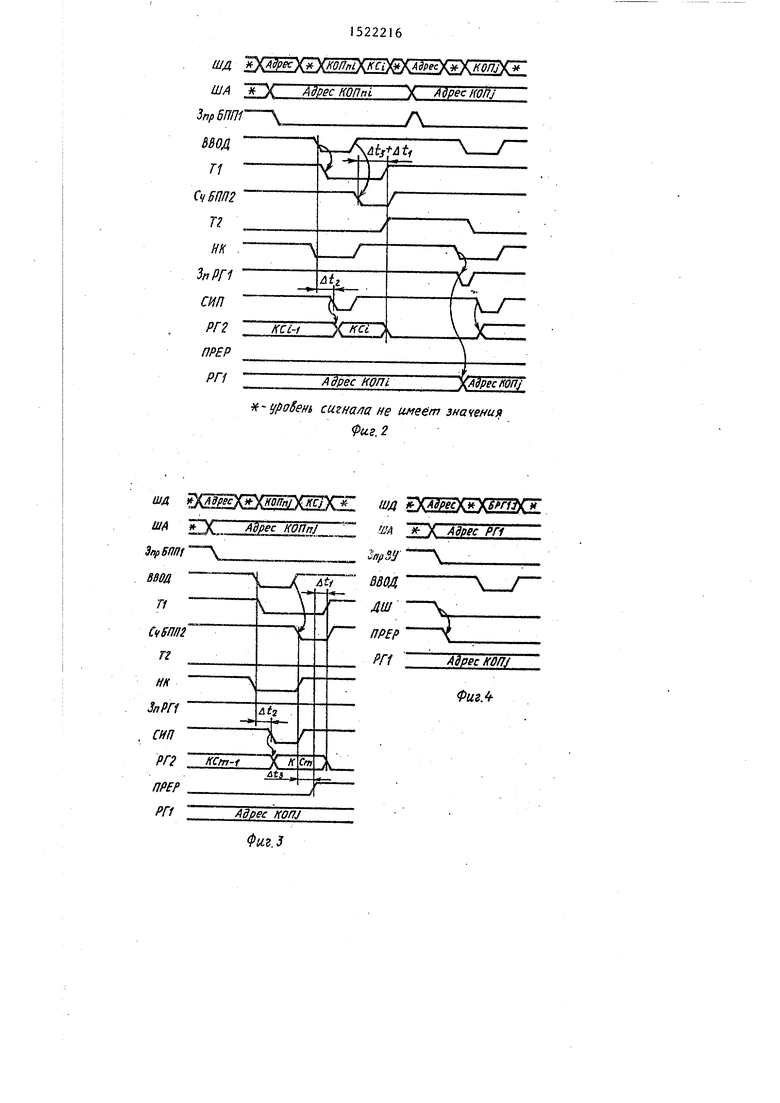

На фиго 2 представлена временная диаграмма функционирования устройства при отсутствии сбоя в аппаратуре контролируемой ЭВМ, где ЩД - информация на шине данных 32; ША - информация на шине адреса 33; ЗпрБПП - сиг- нал запроса Б1Ш1 1; ВВОД - сигнал ввода информации в процессор контролируемой ЭВМ на линии сигнала ВВОД 36; Т1 - сигнал на инверсном выходе первого триггера 13; СчБПП2 - сигнал считьшания информации из БПП 2; Т2 - сигнал на прямом выходе второго триггера 16; ЙК - сигнал начала ко- манды на линии сш нала НК 37; ЗпРП - сигнал записи в РГ1 24; СИП - сигнал синхронизации пассивного устройства на линии сигнала СИП 39; РГ2 содержимое РГ2 31; ПРЕР - сигнал прерьюания на линии сигнала ПРЕР 42; РГ1 содержююе РГ1 24 КОП - код операций команды контролируемой ЭВМ| КС контрольная сзгмма; ut, - время задержки первого элемента задершси 18; &t,j, - время задержки второго элемен- та задержки 10; bt - время задержки третьего элемента задержки 20о

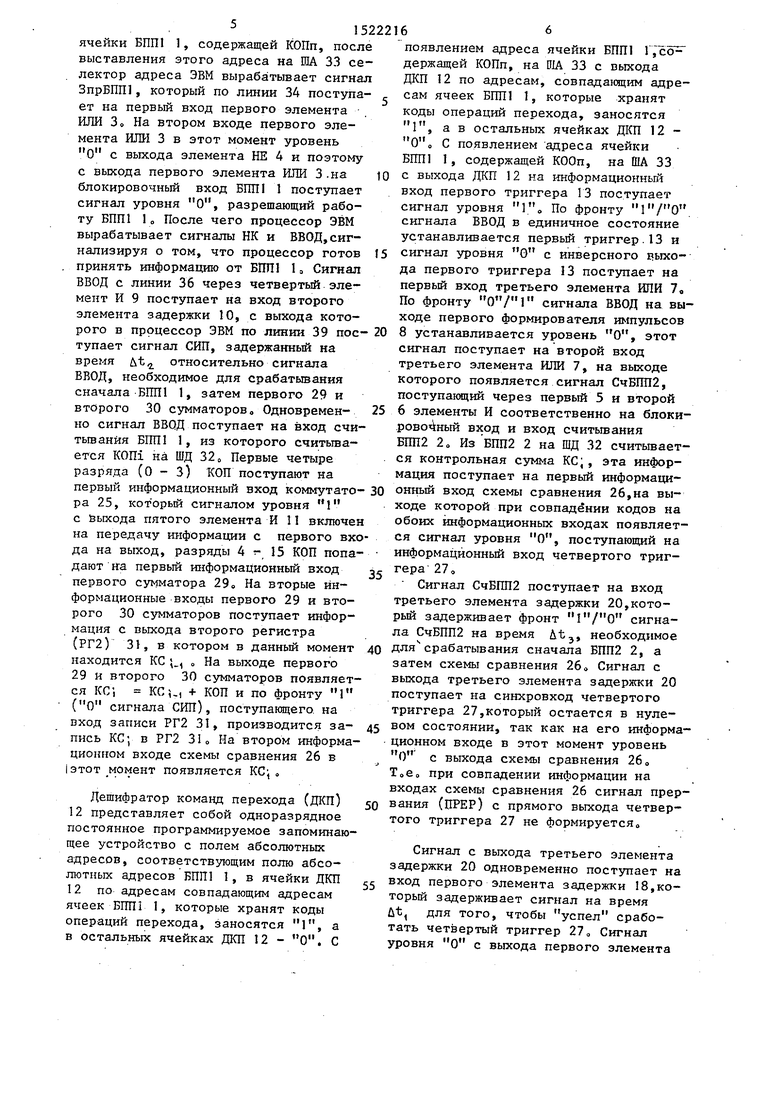

На фиГ(,3 представлена временная диаграмма функционирования устройства в момент фиксации сбоя, где ШД - информация на шине данных 32, IBA - информация на гаине адреса 33, ЗпрБПП -сигнал запроса БШ11 1,ВВОД сигнал ввода информации в процессор на линии сигнала ВВОД 36, TI - сигна на инверсном выходе первого триггера 13, СчБШ12 - сигнал считьтания НПП2 Т2 - сигнал на прямом выходе второго триггера 16, НК - сигнал начала команды на линии сигнала НК 37,ЗпРП - сигнал записи в РГ1 24, СИП - сигнал синхронизации пассивного устройства на линии сигнала СИП 39, РГ2 - содержимое РГ2 31, ПРЕР - сигнал прерьта- ния на линии сигнала ПРЕР 42, РГ1 - содержимое РГ1 24, КОП код операции текущей команды, контролируемой ЭВМ, время задержки первого элемента задержки 18, bt, - время задерж

,

д 0

5

ки второго элемента задержки 10; utj - время задержки третьего элемента задерзйси 20; КС - контрольная сумма,

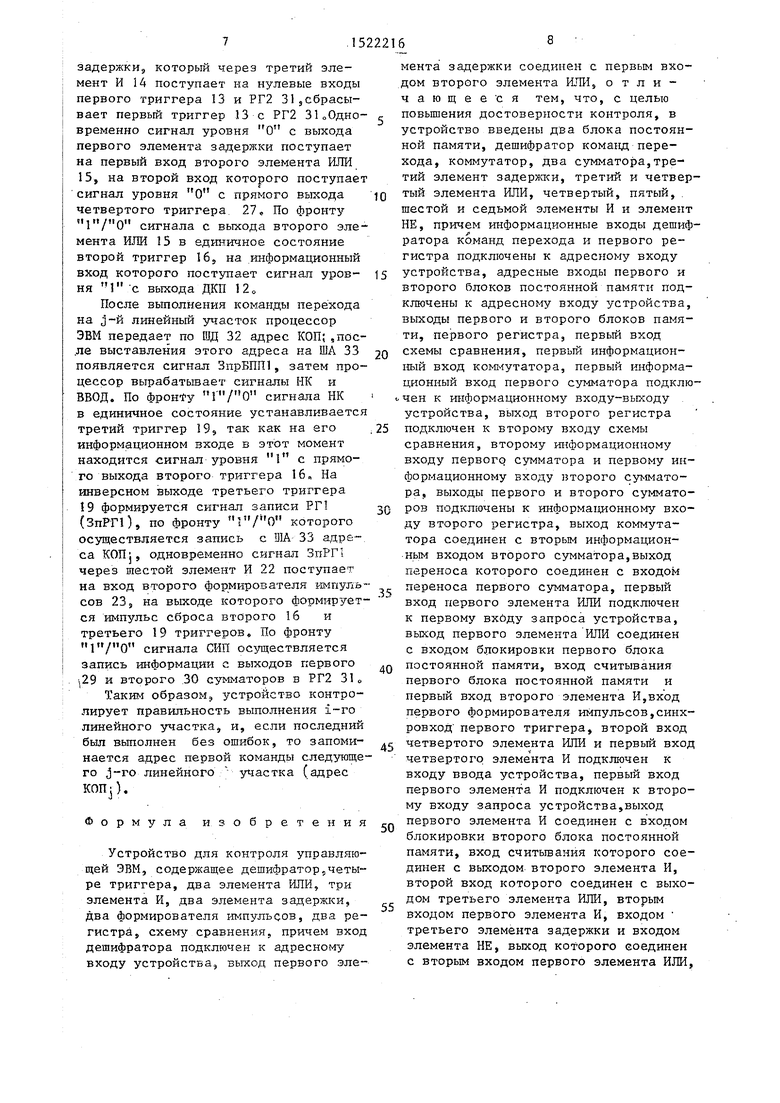

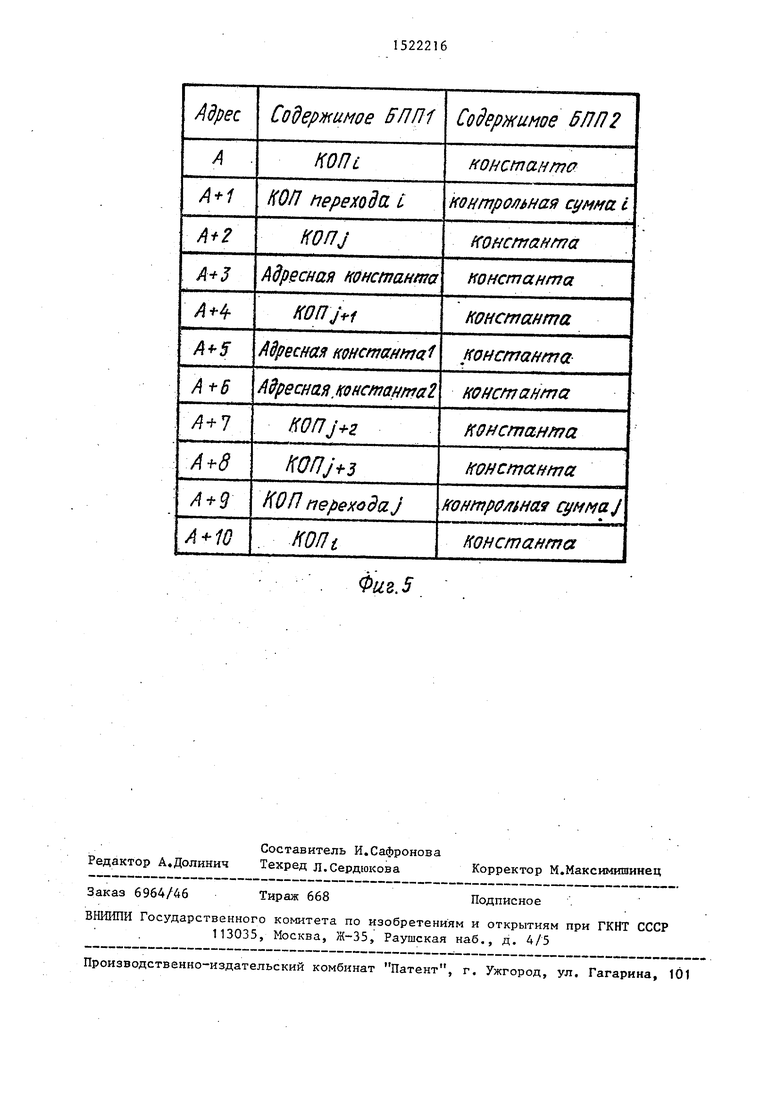

На фиг о4 представлена временная диаграмма при выходе из прерывания и восстановления вычислительного процесса, где ЩД информация на шине данных 32, ИА - информация на шине адреса 33, ЗпрВУ - сигнал запроса внешних устройств контролируемой ЭВМ ВВОД - с игнал ввода информации в процессор ЭВМ на линии сигнала ВВОД 36, ДШ - сигнал на выходе дешифратора 17, ПРЕР - сигнал прерывания на линии сигнала ПРЕР 42, РГ1 - содержимое РГ1 24, КОП - код операции текущей команды контролируемой ЭВМ

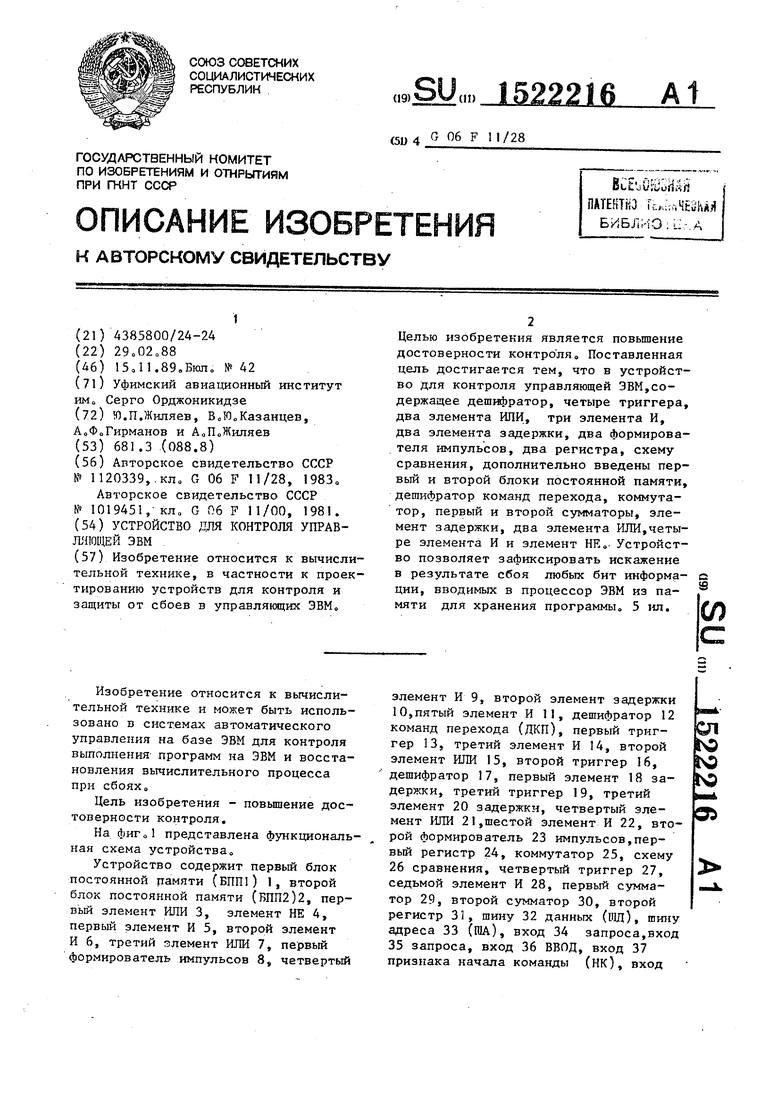

На фиг,5 показано расположение информации в БШ11 1 и БПП 2, где А - относительный двенадцатиразрядный адрес ячейки БШ 1 и БШ12 2,КОП - код операции.

Устройство работает- следующим образомо

Рабочая программа контролируемой ЭВМ заносится в БПП1 1, а все программные констакты - в Шт2 2,Двенадцатиразрядные относительные адреса ВШИ I и БПП2 совпадают, но абсолк т- ные шестиададтиразрядные адреса БЩП 1 и Б1Ш2 2 различны. Старшие (13 - 15) разряды абсолютного адреса поступают на селектор адреса ЭВМ,ко- торьй и вьздает управляющие сигналы запроса БПП1 1 или БШТ2 2. Таким образом, процессор ЭВМ обращается к БПП 1 и БЩ12 2 при считывании команд и программных констант. Контроль вычислительного процесса осзгществляет- ся в конце каждого линейного участка при считывании из ВПП1 I команды перехода посредством сравнении закоп- ленной в РГ2 3 суымы с контрольной,, извлекаемой нз БПП2 2, Двенадцатиразрядные относительные адреса ячеек БШ11 1, содержащих коды операций перехода (коп), и ячеек БШ12 2, содержащих контрольные суммы соответствующих линейных участков, совпадают

(фиг,5),

I

Рассмотрим выполнение i-й однослов - ной команды перехода, состоящей лишь из кода операции перехода (КОПп), при отсутствии сбоев во время выполнения данного линейного участгаса (фиг«2),Процессор ЭВМ передает по ИД 32 адрес

515

ячейки БПП1 1, содержащей КОПп, после выставления этого адреса на ША 33 селектор адреса ЭВМ вырабатывает сигнал ЗпрБПШ, который по линии 34 поступа- ет на первый вход первого элемента ИЛИ Зо На втором входе первого элемента ИЛИ 3 в этот момент уровень О с выхода элемента НЕ 4 и поэтому с выхода первого элемента ИЛИ З.на блокировочный вход Б1Ш1 1 поступает сигнал уровня О, разрешающий работу БПП 1 о После чего процессор ЭВМ вырабатывает сигналы НК и ВВОД,сигнализируя о том, что процессор готов принять информацию от БПЛ1 1 Сигнал ВВОД с линии 36 через четвертый элемент И 9 поступает на вход второго элемента задержки 10, с выхода которого в процессор ЭВМ по линии 39 пос- тупает сигнал СИП, задержанный на время ut, относительно сигнала ВВОД, необходимое для срабатывания сначала БПП1 1, затем первого 29 и второго 30 сумматоров Одновремен- но сигнал ВВОД поступает на вход счи- тьгоанйя БШ11 1, из которого считывается KOni на ШД 32 о Первые четыре разряда (о - З) КОП поступают на первый информационный вход коммутато- ра 25, кот орый сигналом уровня 1 с выхода пятого элемента И II включен на передачу информации с первого входа на выход, разряды 4 15 КОП попа- дают иа первый информационный вход первого сумматора 29 На вторые информационные входы первого 29 и второго 30 сумматоров поступает информация с выхода второго регистра (РГ2) 31, в котором в данный момент находится КС , На выходе первого 29 и второго 30 сумматоров появляется КС , КСи, + КОП и по фронту 1 (О сигнала сип), поступающего, на вход записи РГ2 31, производится за- пись КС; в РГ2 31 , На втором информационном входе схемы сравнения 26 в I этот момент появляется КС

Дешифратор команд перехода (ДКП) 12 представляет собой одноразрядное постоянное программируемое запоминающее устройство с полем абсолютных адресов, соответствующим полю абсолютных адресов БПП1 1, в ячейки ДКП 12 по адресам совпадающим адресам ячеек БПП1 1, которые хранят коды операций перехода, заносятся 1, а в остальных ячейках ДКП 12 - О. С

66

появлением адреса ячейки БПП1 держащей КОПп, на Г1А 33 с выхода ДКП 12 по адресам, совпадакщим адресам ячеек БШТ1 1, которые хранят коды операций перехода, заносятся 1, а в остальных ячейках ДКП 12 - С появлением адреса ячейки БШ11 1, содержащей КООп, на ША 33 с выхода ДКП 12 на информационньй вход первого триггера 13 поступает сигнал уровня По фронту . сигнала ВВОД в единичное состояние устанавливается первый триггер.13 и сигнал уровня О с инверсного рыхо- да первого триггера 13 поступает на первьй вход третьего элемента ИПИ 7, По фронту сигнала ВВОД на выходе первого формирователя импульсов 8 устанавливается уровень О, этот сигнал поступает на второй вход третьего элемента ИЛИ 7, на выходе которого появляется сигнал СчБШ12, поступакяций через первый 5 и второй 6 элементы И соответственно на блоки- вход и вход считьшания БШ12 2 о Из БПП2 2 на ШД 32 считывается контрольная сумма КС;, эта информация поступает на первый информационный вход схемы сравнения 26,на выходе которой при совпадении кодов на обоих информационных входах появляется сигнал уровня О, поступающий на информационный вход четвертого триггера 27 о

Сигнал СчБПП2 поступает на вход третьего элемента задержки 20,который задерживает фронт сигнала СчБПП2 на время At, необходимое для срабатывания сначала БПП2 2, а затем схемы сравнения 26 Сигнал с выхода третьего элемента задержки 20 поступает на синхровход четвертого триггера 27,который остается в нулевом состоянии, так как на его информационном входе в этот момент уровень О с вьпсода схемы сравнения 26 при совпадении информации на входах схемы сравнения 26 сигнал прер- вания (ПРЕР) с прямого выхода четвертого триггера 27 не формируется

Сигнал с выхода третьего элемента задержки 20 одновременно поступает на вход первого элемента задержки 18,который задерживает сигнал на время ut, для того, чтобы успел сработать четвертый триггер 27„ Сигнал уровня О с выхода первого элемента

задержки, который через третий элемент И 14 поступает на нулевые входы первого триггера 13 и РГ2 31jC6pacH- вает первый триггер 13 с РГ2 ЗКОдно- временно сигнал уровня О с выхода первого элемента задержки поступает на первый вход второго элемента ИЛИ 15, на второй вход которого поступает сигнал уровня О с прямого выхода четвертого триггера 27, По фронту сигнала с выхода второго элемента ИЛИ 15 в единичное состояние второй триггер 16, на информационный вход которого поступает сигнал уровня 1 с выхода ДКП 12о

После вьшолнения команды перехода на й линейный з асток процессор ЭВМ передает по ШД 32 адрес КОП;,после выставления этого адреса на ША 33 появляется сигнал ЗпрВПИ, затем процессор вырабатывает сигналы НК и ВВОД. По фронту сигнала НК в единичное состояние устанавливается третий триггер 19, так как на его информационном входе в этот момент находится сигнал уровня 1 с прямого выхода второго триггера 16 На инверсном выходе третьего триггера 19 формируется сигнал записи РГ (ЗпРП), по фронту которого осуществляется запись с ША 33 адре-. са КОП;, одновременно сигнал ЗпРП через шестой элемент И 22 поступает на вход второго формирователя импуль- сов 23,, на выходе которого формируется импульс сброса второго 16 и третьего 19 триггеров. По фронту i| YiiQ4 сигнала СИП осуществляется запись информации с выходов первого и второго .30 сумматоров в РГ2 31 Таким образом, устройство контролирует правильность выполнения i-ro линейного участка, и, если последний был выполнен без ошибок, то запоминается адрес первой команды следующего j-ro линейного участка (адрес

копр.

Формула изобретения

Устройство для контроля управляющей ЭВМ, содержащее дешифратор,четыре триггера, два элемента ИЛИ, три элемента И, два элемента задержки, два формирователя импульсов, два регистра, схему сравнения, причем вход дешифратора подключен к адресному входу устройства, выход первого эле

мента задержки соединен с первым вхо- .дом второго элемента ИЛИ, отличающееся тем, что, с целью повышения достоверности контроля, в устройство введены два блока постоянной памяти, дешифратор комагщ перехода, коммутатор, два сумматора,третий элемент задершси, третий и четвер- Q тый элемента ИЛИ, четвертый, пятый, . шестой и седьмой элементы И и элемент НЕ, причем информационные входы дешифратора команд перехода и первого регистра подключены к адресному входу 5 устройства, адресные входы первого и второго блоков постоянной памяти подключены к адресному входу устройства, выходы первого и второго блоков памяти, первого регистра, первый вход 0 схемы сравнения, первый информационный вход ком1 утатора, первый информационный вход первого сумматора подклю- «. чен к информационному входу-выходу .

устройства, выход второго регистра 5 подключен к второму входу схемы

сравнения, второму информационному входу первого сумматора и первому информационному входу второго сумматора, выходы первого и второго суммато- 30 ров подключены к информатщонному входу второго регистра, выход коммутатора соединен с вторым информацион- нь1м входом второго сумматор а, выход переноса которого соединен с входом , переноса первого сумматора, первый вход первого элемента ИЛИ подключен к первому вхйду запроса устройства, выход первого элемента ИЛИ соединен с входом блокировки первого блока 4Q постоянной памяти, вход считывания первого блока постоянной памяти и первьш вход второго элемента И,вход первого формирователя иМпульсов,синх- ровход первого триггера, второй вход д5 четвертого элемента ИЛИ и первый вход четвертого элемента И подключен к входу ввода устройства, первый вход первого элемента И подключен к второму входу запроса устройства,выход первого элемента И соединен с входом блокировки второго блока постоянной памяти, вход считьгоания которого соединен с выходом второго элемента И, второй вход которого соединен с выходом третьего элемента ИЛИ, вторым входом первого элемента И, входом третьего элемента задержки и входом элемента НЕ, выход которого соединен с вторым входом первого элемента ИЛИ,

50

55

выход дешифратора команд перехода соединен с информационными входами первого и второго триггеров,инверс- ньш выход первого триггера соединен с первым входом третьего элемента ИЛИ, второй вход которого соединен с выходом первого формирователя импульсов, дешифратЬра подключен к первому входу седьмого элемента И и первому входу четвертого элемента ИЛИ, выход которого соединен с входом считьшания первого регистра,вход записи которого соединен с инверсным выходом третьего триггера и вторым входом шестого элемента И, первые входы шестого и третьего элементов И и второй вход седьмого элемента И подключены к входу начальной установки, выход седьмого элемента И подкшо- чен к нулевому входу четвертого триггера, прямой выход которого подключен к второму входу.второго элемента ИЛИ и является выходом прерывания устройства, выход первого элемента задеряжи соединен с вторым входом третьего элемента И, выход которого соединен с входами установки в О первого триггера и второго регистр а, выход шестого элемента И соединен с входом второго формирователя импульсов, выход которого подключен к ну0

5

Q 5 О

левым входам второго и третьего триггеров, выход второго элемента ИЛИ соединен с синхровходом второго триггера, прямой выход которого соединен с информационным входом третьего триггера, синхровход которого подключен к входу признака начала команды устройства, выход третьего элемента задержки соединен с входом первого элемента задержки и синхровходом четвертого триггера, информационный вход которого соединен с выходом схемы сравнения, второй вход четвертого элемента И подключен к входу вывода устройства, выход чет- верто го элемента И соединен с входом второго элемента задержки,выход которого подключен к входу записи второго регистра и - первому выходу синхронизации пассивного устройства, первый и второй входы пятого элемента И подключены соответственно к входам запроса оперативного запоминающего устройства и внешних устройств, выход пятого элемента И соединен с управляющим входом коммутатора и входом блокировки первого сумматора, входы ввода, вывода, запроса оперативного запоминающего устройства и запроса внешних устройств подключены к второму информационному входу коммутатора.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля управляющей ЭВМ | 1988 |

|

SU1619280A1 |

| Устройство для сопряжения процессора с памятью | 1987 |

|

SU1439605A1 |

| Устройство для контроля выполнения программ на эвм | 1986 |

|

SU1383371A1 |

| Микропрограммный процессор | 1987 |

|

SU1517034A1 |

| Устройство для формирования адресов процессора усеченного быстрого преобразования Фурье | 1984 |

|

SU1278883A1 |

| Устройство для сопряжения внешних устройств с электронной вычислительной машиной | 1983 |

|

SU1100615A1 |

| Микропрограммный процессор | 1984 |

|

SU1211746A1 |

| Устройство для сопряжения ведущей и N ведомых цифровых вычислительных машин | 1988 |

|

SU1531104A1 |

| Устройство для сопряжения вычислительной машины с линиями связи | 1985 |

|

SU1262512A1 |

| Устройство для сопряжения ЭВМ с внешними устройствами | 1987 |

|

SU1501077A1 |

Изобретение относится к вычислительной технике, в частности к проектированию устройств для контроля и защиты от сбоев в управляющих ЭВМ. ЦЕЛЬЮ ИЗОБРЕТЕНИЯ ЯВЛЯЕТСЯ ПОВЫШЕНИЕ ДОСТОВЕРНОСТИ КОНТРОЛЯ. ПОСТАВЛЕННАЯ ЦЕЛЬ ДОСТИГАЕТСЯ ТЕМ, ЧТО В УСТРОЙСТВО ДЛЯ КОНТРОЛЯ УПРАВЛЯЮЩЕЙ ЭВМ, СОДЕРЖАЩЕЕ ДЕШИФРАТОР, ЧЕТЫРЕ ТРИГГЕРА, ДВА ЭЛЕМЕНТА ИЛИ, ТРИ ЭЛЕМЕНТА И, ДВА ЭЛЕМЕНТА ЗАДЕРЖКИ, ДВА ФОРМИРОВАТЕЛЯ ИМПУЛЬСОВ, ДВА РЕГИСТРА, СХЕМУ СРАВНЕНИЯ, ДОПОЛНИТЕЛЬНО ВВЕДЕНЫ ПЕРВЫЙ И ВТОРОЙ БЛОКИ ПОСТОЯННОЙ ПАМЯТИ, ДЕШИФРАТОР КОМАНД ПЕРЕХОДА, КОММУТАТОР, ПЕРВЫЙ И ВТОРОЙ СУММАТОРЫ, ЭЛЕМЕНТ ЗАДЕРЖКИ, ДВА ЭЛЕМЕНТА ИЛИ, ЧЕТЫРЕ ЭЛЕМЕНТА И И ЭЛЕМЕНТ НЕ. УСТРОЙСТВО ПОЗВОЛЯЕТ ЗАФИКСИРОВАТЬ ИСКАЖЕНИЕ В РЕЗУЛЬТАТЕ СБОЯ ЛЮБЫХ БИТ ИНФОРМАЦИИ, ВВОДИМЫХ В ПРОЦЕССОР ЭВМ ИЗ ПАМЯТИ ДЛЯ ХРАНЕНИЯ ПРОГРАММЫ. 5 ИЛ.

(7.../5

Фиг.1

РП

Адрес кот

-{/ро5ень сUZна/га не имебт значения Фиг. 2

X Адрес копп ЗпрБПЛ( Л

A3pecKonj

Адрес KOnj

Составитель И.Сафронова Редактор А.Долинич Техред л.Сердюкова

Заказ 6964/46

Тираж 668

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР 113035, Москва, Ж-35, Раушская наб,, д. 4/5

.5

Корректор М.Максимишинец

Подписное

| Устройство для контроля времени выполнения программ | 1983 |

|

SU1120339A2 |

Авторы

Даты

1989-11-15—Публикация

1988-02-29—Подача