11298930

Изобретение относится к электросвязи и может быть использовано в аппаратуре контроля дискретных каналов или каналов передачи данных.

Цель изобретения - повышение точности контроля.

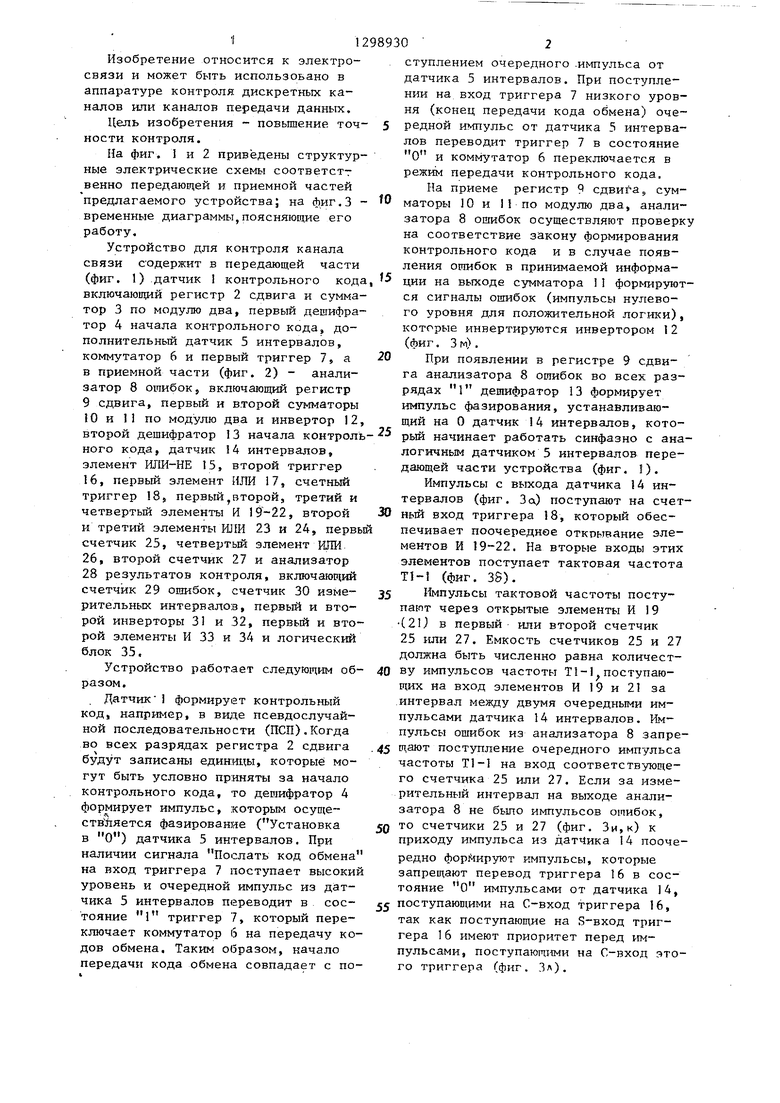

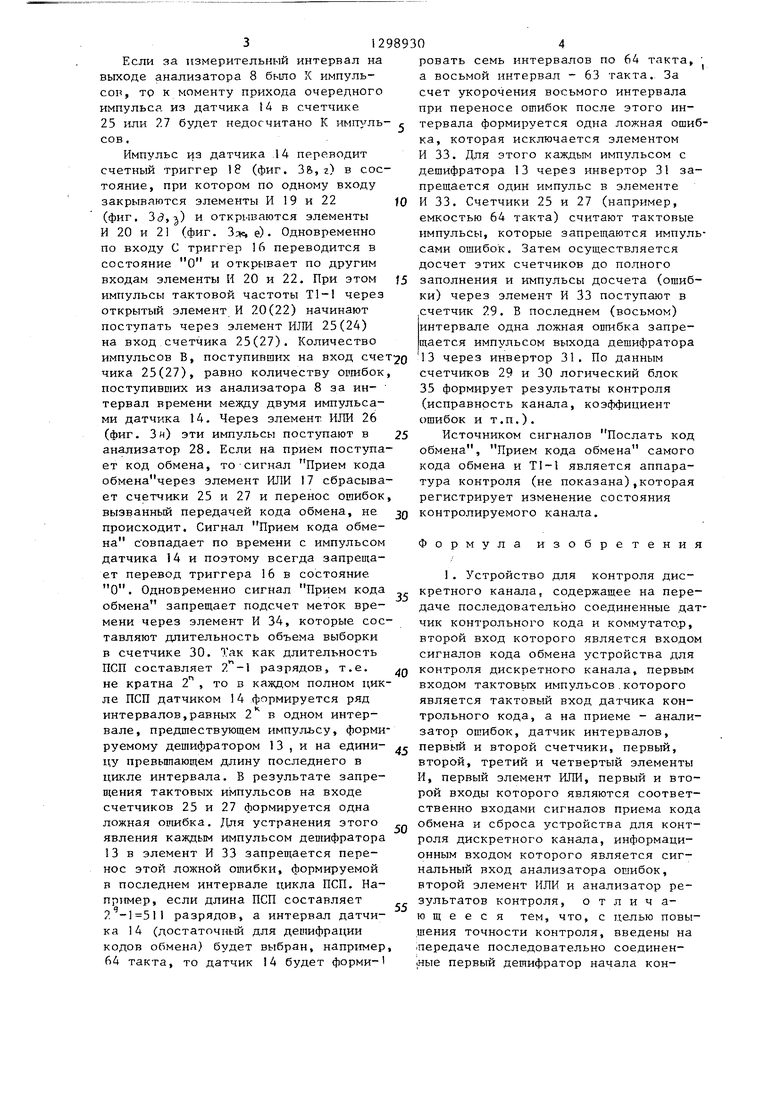

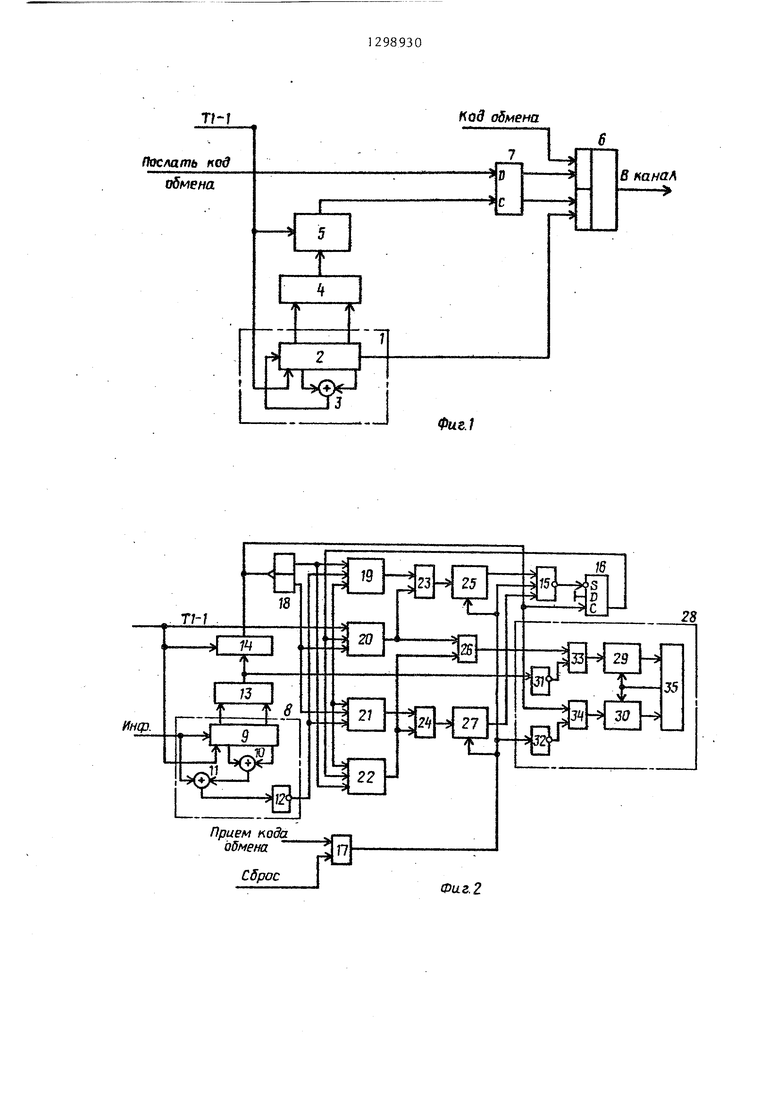

На фиг. 1 и 2 приведены структурные электрические схемы соответстт венно передающей и приемной частей предлагаемого устройства; на фиг.З временные диаграммы,поясняющие его работу.

Устройство для контроля канала связи содержит в передающей части

- 10

ступлением очередного .импульса от датчика 5 интервалов. При поступлении на вход триггера 7 низкого уровня (конец передачи кода обмена) очередной импульс от датчика 5 интервалов переводит триггер 7 в состояние О и коммутатор 6 переключается в режим передачи контрольного кода.

На приеме регистр 9 сдвига., сумматоры 0 и I} по модулю два, анализатора 8 опшбок осуществляют проверку на соответствие закону формирования контрольного кода и в случае появления ощибок в принимаемой информа(фиг. 1) датчик 1 контрольного кода, ции на выходе сумматора 15 формируют- включающий регистр 2 сдвига и сумма- ся сигналы ошибок (импульсы нулево- тор 3 по модулю два, первьгй дешифра- го уровня для положительной логики), тор 4 начала контрольного кода, дополнительный датчик 5 интервалов,

которые инвертируются инвертором I2 (фиг. 3м).

коммутатор 6 и первый триггер 7, а в приемной части (фиг. 2) - анализатор 8 ошибок, включающий регистр

9сдвига, первый и второй сумматоры

10и 11 по модулю два и инвертор 12,

20 При появлении в регистре 9 сдвига анализатора 8 ошибок во всех разрядах I дешифратор 13 формирует импульс фазирования, устанавливающий на О датчик 14 интервалов, котовторой дешифратор 13 начала контроль- рый начинает работать синфазно с ана- ного кода, датчик 14 интервалов, элемент ИЛИ-НЕ 15, второй триггер 16, первый элемент ИЛИ 17, счетньШ триггер 18, первый,второй, третий и четвертый элементы И 19-22, второй и третий элементы ИЛИ 23 и 24, первьй счетчик 25, четвертый элемент ИЛИ 26, второй счетчик 27 и анализатор 28 результатов контроля, включаюп1ий счетчик 29 ошибок, счетчик 30 измерительных интервалов, первый и второй инверторы 31 и 32, первый и второй элементы И 33 и 34 и логический блок 35.

логичным датчиком 5 интервалов передающей части устройства (фиг. I).

Импульсы с выхода датчика 14 интервалов (фиг. За) поступают на счет- Л) ньй вход триггера 18, который обеспечивает поочередное открывание элементов И 19-22. На вторые входы этих элементов поступает тактовая частота Т1-} (фиг. 3S).

{Тмпульсы тактовой частоты поступают через открытые элементы И 19 (2U в первый или второй счетчик 25 или 27. Емкость счетчиков 25 и 27 должна быть численно равна количест35

Устройство работает следующим об- 40 ву импульсов частоты Т1-1 поступаюразом.

Датчик 1 формирует контрольный код, например, в виде псевдослучайной последовательности (ПСИ).Когда во всех разрядах регистра 2 сдвига будут записаны единицы, которые могут быть условно приняты за начало контрольного кода, то дешифратор 4 формирует импульс, которым осуще- ств ляется фазирование (Установка в О) датчика 5 интервалов. При наличии сигнала Послать код обмена на вход триггера 7 поступает высокий уровень и очередной импульс из датчика 5 интервалов переводит в состояние 1 триггер 7, который переключает коммутатор 6 на передачу кодов обмена. Таким образом, начало передачи кода обмена совпадает с по10

ступлением очередного .импульса от датчика 5 интервалов. При поступлении на вход триггера 7 низкого уровня (конец передачи кода обмена) очередной импульс от датчика 5 интервалов переводит триггер 7 в состояние О и коммутатор 6 переключается в режим передачи контрольного кода.

На приеме регистр 9 сдвига., сумматоры 0 и I} по модулю два, анализатора 8 опшбок осуществляют проверку на соответствие закону формирования контрольного кода и в случае появления ощибок в принимаемой информа, ции на выходе сумматора 15 формируют- ся сигналы ошибок (импульсы нулево- го уровня для положительной логики),

ции на выходе сумматора 15 формируют- ся сигналы ошибок (импульсы нулево- го уровня для положительной логики),

которые инвертируются инвертором I2 (фиг. 3м).

При появлении в регистре 9 сдвига анализатора 8 ошибок во всех разрядах I дешифратор 13 формирует импульс фазирования, устанавливающий на О датчик 14 интервалов, который начинает работать синфазно с ана-

рый начинает работать синфазно с ана-

логичным датчиком 5 интервалов передающей части устройства (фиг. I).

Импульсы с выхода датчика 14 интервалов (фиг. За) поступают на счет- ньй вход триггера 18, который обеспечивает поочередное открывание элементов И 19-22. На вторые входы этих элементов поступает тактовая частота Т1-} (фиг. 3S).

{Тмпульсы тактовой частоты поступают через открытые элементы И 19 (2U в первый или второй счетчик 25 или 27. Емкость счетчиков 25 и 27 должна быть численно равна количест

щих на вход элементов И 19 и 21 за интервал между двумя очередными импульсами датчика 14 интервалов. Импульсы ощибок из анализатора 8 запре- .45 щают поступление очередного импульса частоты Т1-1 на вход соответств; гюще- го счетчика 25 или 27. Если за измерительный интервал на выходе анализатора 8 не было импульсов ошибок,

50 то счетчики 25 и 27 (фиг. Зи,к) к

приходу импульса из датчика I4 поочередно формируют импульсы, которые запрещают перевод триггера 16 в состояние О импульсами от датчика 14,

jj поступающими на С-вход триггера 16, так как поступающие на S-вход триггера 16 имеют приоритет перед импульсами, поступающими на С-вход этого триггера (фиг. 3л).

Если за измерительный интервал на выходе анализатора 8 бьшо К импульсов, то к моменту прихода очередного импульса из датчика 14 в счетчике 25 или 27 будет недосчитано К имщшь- сов.

Импульс из датчика 14 переводит счетный триггер 18 (фиг. 36,г) в состояние, при котором по одному входу закрываются элементы И 19 и 22 (фиг, 3(,j) и открываются элементы И 20 и 21 (фиг. Зяс, е). Одновременно по входу С триггер 16 переводится в состояние О и открывает по другим входам элементы И 20 и 22. При этом импульсы тактовой частоты Т1-1 через открытый элемент И 20(22) начинают поступать через элемент ИЛИ 25(24) на вход счетчика 25(27). Количество импульсов В, поступивших на вход сче чика 25(27), равно количеству ошибок поступивших из анализатора 8 за интервал времени между двумя импульсами датчика 14. Через элемент ИЛИ 26 (фиг. 3н) эти импульсы поступают в анализатор 28. Если на прием поступает код обмена, то-сигнал Прием кода обмена через элемент ИЛИ 17 сбрасывает счетчики 25 и 27 и перенос ошибок вызванный передачей кода обмена, не происходит. Сигнал Прием кода обмена с овпадает по времени с импульсом датчика 14 и поэтому всегда запрещает перевод триггера 16 в состояние О. Одновременно сигнал Прием кода обмена запрещает подсчет меток времени через элемент И 34, которые составляют длительность объема выборки в счетчике 30. Так как длительность ПСИ составляет .- разрядов, т.е. не кратна 2, то в каждом полном цикле ПСИ датчиком 14 формируется ряд интервалов,равных 2 в одном интервале, предшествующем импульсу, формируемому дешифратором 13 , и на едини- цу превышающем длину последнего в цикле интервала. В результате запрещения тактовых импульсов на входе счетчиков 25 и 27 формируется одна ложная оишбка. Для устранения этого явления каждым импульсом дешифратора 13 в элемент И 33 запрещается перенос этой ложной ошибки, формируемой в последнем интервале цикла ПСП. Например, если длина ПСП составляет разрядов, а интервал датчика 14 (достаточньш для дешифрации кодов обмена) будет выбран, например 64 такта, то датчик 14 будет форми-1

O 5 о 5 0 «

5

0

ровать семь интервалов по 64 такта, а восьмой интервал - 63 такта.. За счет укорочения восьмого интервала при переносе ошибок после этого интервала формируется одна ложная ошибка, которая исключается элементом И 33. Для этого каждым импульсом с дешифратора 13 через инвертор 31 запрещается один импульс в элементе И 33. Счетчики 25 и 27 (например, емкостью 64 такта) считают тактовые импульсы, которые запрещаются импульсами ошибок. Затем осуществляется досчет этих счетчиков до полного заполнения и импульсы досчета (ошибки) через элемент И 33 поступают в счетчик 29. В последнем (восьмом) интервале одна ложная опгибка запрещается импульсом выхода дешифратора 13 через инвертор 31. По данным счетчиков 29 и 30 логический блок 35 формирует результаты контроля (исправность канала, коэффициент ошибок и т.п.).

Источником сигналов Послать код обмена, Прием кода обмена самого кода обмена и Т1-1 является аппаратура контроля (не показана),которая регистрирует изменение состояния контролируемого канала.

Формула изобретения

1. Устройство для контроля дискретного канала, содержащее на передаче последовательно соединенные датчик контрольного кода и коммутато.р, второй вход которого является входом сигналов кода обмена устройства для контроля дискретного канала, первым входом тактовьгх импульсов .которого является тактовый вход датчика контрольного кода, а на приеме - анализатор ошибок, датчик интервалов, первый и второй счетчики, первый, второй, третий и четвертый элементы И, первый элемент ИЛИ, первый и второй входы которого являются соответственно входами сигналов приема кода обмена и сброса устройства для контроля дискретного канала, информационным входом которого является сигнальный вход анализатора ошибок, второй элемент ИЛИ и анализатор результатов контроля, отличающееся тем, что, с целью повышения точности контроля, введены на .передаче последовательно соединен- «ые первый дешифратор начала контрольного кода, дополнительный датчик интервалов и первый триггер, а. на приеме - второй дешифратор начала контрольного кода, счетный триггер, третий и четвертый элементы ИЛИ, элемент ИЛИ-НЕ и второй триггер, при этом на передаче выходы разрядов и тактовый вход датчика контрольного кода соединены соответст- венно с входами первого дешифратора начала контрольного кода и с тактовым входом дополнительного датчика интервалов, а первый и второй выходы первого триггера, второй вход которого является входом сигнала о по- сыпке кода обмена, подключены соответственно к третьему и четвертому входам коммутатора, а на приеме - выходы разрядов анализатора ошибок подключены к входам второго дешиф- ратора начала контрольного кода, выход которого подключен к первому входу анализатора результатов контроля и к управляющему входу датчика интервалов, выход которого под- ключен к входу счетного триггера, к С-входу второго триггера и к второму входу анализатора результатов контроля, первый выход счетного триггера через последовательно соединен- ныв первый элемент И, второй элемент ИЛИ, первый счетчик и элемент ЙДИ-НЕ подключен к З-входу второго триггера, D-ВХОД которого подключен к общей стине, второй выход счетного триг гера через второй элемент И подключен к второму входу второго элемета , ИЛИ и к первому входу четвертого элемента ИЛИ, выход которого подключен к третьему входу анализатора результатов контроля, второй выход счетного триггера через последователно соединенные третий элемент И,

третий элемент.ИЛИ и второй счетчик подключен к второму входу элемента ;ИЛИ-НЕ, первый выход счетного триггера через четвертый элемент И подключен к вторым входам третьего и чевертого элементов ИЛИ, выход анализатора опшбок подключен к вторым входам первого и третьего элементов И, выход второго триггера подключен к вторым входам второго и четвертого элементов И, третьи входы которых соединены с третьими входами первого и третьего элементов И, с тактовым входом анализатора ошибок и с тактовым входом датчика интервалов, являющимся вторым тактовым входом устройства для контроля дискретного канала, а выход первого элемента ИЛИ подключен к третьему входу элемента ИЛИ-НЕ, к четвертому входу анализатора результатов контроля и к входам сброса первого и второго счетчиков, 2. Устройство по п. 1, отличающееся тем, что анализатор результатов контроля содержит последовательно соединенные первый инвертор, первый элемент И, счетчик ошибо и логический блок и последовательно соединенные второй инвертор, второй элемент И и счетчик измерительных, интервалов, при этом выход счетчика измерительных интервалов подключен к второму входу логического блока, выход которого подключен к входам установки счетчика ошибок и счетчика измерительных интервалов, а первьм, вторым, третьим и четвертым входами анализатора результатов контроля являются соответственно вход первого инвертора, второй вход второго элемента И, второй вход перво- го элемента И и вход второго инвертора.

Tf-l

Код

В канал

Н -« -| Г

CJ ю QO v

ад

Составитель В.Слепаков Редактор Л.Гратилло Техред М.Ходанич

Заказ 900/60 Тираж 639Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

с

«

С)

о

Ч 5Г

- з:

Корректор М.Самборская

| название | год | авторы | номер документа |

|---|---|---|---|

| Система передачи и приема цифровой информации | 1988 |

|

SU1559361A1 |

| УСТРОЙСТВО ДЛЯ АВТОМАТИЧЕСКОГО ИЗМЕРЕНИЯ ХАРАКТЕРИСТИК ДИСКРЕТНОГО КАНАЛА СВЯЗИ | 1995 |

|

RU2138910C1 |

| Система передачи и приема цифровой информации | 1986 |

|

SU1392583A1 |

| Устройство для контроля резервированного генератора | 1980 |

|

SU907887A1 |

| Устройство для обмена информацией | 1982 |

|

SU1131035A1 |

| Устройство сопряжения с магистралью последовательного интерфейса | 1983 |

|

SU1275417A1 |

| Устройство для контроля блоков постоянной памяти | 1983 |

|

SU1125657A1 |

| Устройство для диспетчерской дуплексной связи | 1985 |

|

SU1293853A1 |

| Устройство для телеконтроля | 1990 |

|

SU1732366A1 |

| Устройство для обучения радиотелеграфистов | 1985 |

|

SU1264366A1 |

Авторы

Даты

1987-03-23—Публикация

1984-11-20—Подача