ИСКЛЮЧАЮЩЕЕ ШТИ, второй вход которог подключен к первому выходу сдвигового регистра и к второму входу кодирующего блока, третий вход которого соединен с вторым входом элемента 2И-ИЛИ-НЕ и с тринадцатым выходом блока управления, четьфнадцатый выход которого соединен с управляющим входом буферного регистра, выходы которого подключены к пятым входам сдвигового регистра, шестой вход которого соединен с первым дополнительным выходом дешифратора, второй дополнительный выход которого соединен с третьим входом блока исправления ошибок, четвертый, пятый и шестой входы которого подключены соответственно к второму, третьему и четвертому выходам анализатора, пятый выход которого соединен с первым входом элемента ИЛИ, второй вход которого подключен к первому выходу блока исправления ошибок, второй выход которого соединен с первым входом элемента И, выход которого подключен к седьмому дополнительному входу блока управления, третий вьгход которого соединен с четвертым входом кодирующего блока, выход которого соединен с третьим входом элемента 2И-ИЛИНЕ, четвертый; вход которого подклю.чен к второму выходу сдвигового регистра, третьи выходы, которого соединены с вторыми входами коммутатора, выход блока сравнения соединен с седьмым входом блока исправления ошибок, третий и четвертьш выходы которого соединены соответственно с пятым и шестым входами декодирующего блока, третий допол- « нительный выход дешифратора подключен к дополнительному входу анализатора, выход элемента ИСКЛЮЧАЮЩЕЕ ИЖ подключен к второму входу элемента И вьгход элемента ИЛИ соединен с третьим входом блока управления коммутатором тактовый выход которого является синхронизирующим выходом устройства для обмена информацией, синхронизирующим вхгдом которого является синхронизирующий вход блока управления, шестой дополнительный вход которого является управляющим входом устройства для обмена информацией, контрольным выходом которого является пятый выход блока исправления оши- . бок, информационными входами устройства для обмена информацией являются информационные входы преобразователя кода и буферного регистра, информационные выходы которых являются информационными выходами устройства для обмена информацией, входом начальной установки которого является восьмой дополнительньй вхо блока Управления.

2. Устройство по п. 1, отличающееся тем, что кодирующи блок содержит одиннадцать триггеров пять элементов ИСКЛЮЧАЮЩЕЕ ИЛИ и элемент И, вьгход i; которого соедине с первым входом первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, с первым входом второго элемента ИСКЛЮЧАЩЕЕ ИЛИ, с первым входом .третьего-элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, с первым входом четвертого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ и с первым входом первого триггера, вьгход которого соединен с вторым входом первого элемента ИСКЛЮЧАКШЩЕ РШИ, вьгход которого соединен с первым входом второго триггеру, выход которого соединен с .первым входом третьего триггера, выход которого соединен с первым входом четвертого триггера, выход которого подключенк второму входу второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, выход которого соединен с первым входом пятого триггера, выход которого соединен с первым входом шестого триггера, выход которого соединен с первым входом седьмого триггера, вьгход которого подключен к второму входу третьего элемента ИСКЛЮЧАЮЩЕЕ .ИЛИ, выход которого-соединен с первым входом восьмого триггера, выход которого подключен к второму входу четвертого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, выход которого соединен с первым входом девятого триггера, выход которого соединен с первым входом десятого триггера, выход которого соединен с первым входом одиннадцатого триггера. Выход которого подключен к первому входу пятого элемента ИСКЛЮЧАМЦЕЕ ИЛИ, выход которого соединен с первым входом элемента И, второй вхрд которого является третьим входом кодирующего блока, щричем вторые и третьи входы первого, второготретьего, четвертого, пятого, шестого, седьмого, восьмого, девятого, десятого и одиннадцатого триггеров (Соответственно объединены и явля.ются соответственно первым и- четвертым входами кодирующего блока.

вторым входом которого является второй вход пятого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, первьшвход которого является выходом кодирующего блока.

3. Устройство по п. 1, отличающееся тем, что декодирующий блок содержит одиннадцать триггеров, три элемента ИСКЛЮЧАЮЩЕЕ ИЛИ и три элемента И, причем выход первого элемента И соединен с первым входом первого элемента ИСКЛЮЧ1УОЩЕЕ ИЛИ и с первым входом второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ выход которого соединен с первым входом первого триггера, единичный выход которого соединен с первым входом второго триггера, единичный выход которого соединен с первым входом третьего триггера,единичный выход которого соединен с первым входом четвертого триггера,единичный выход которого соединен с первым входом пятого триггера, единичный выход которого ;соединен с первым входом шестого триггера, единичный выход.которого соединен с первым входом седьмого т триггера, единичный выход которого соединен с вторым входом второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, выход второго элемента И соединен с первым входом третьего -элемента ИСКЛЮЧАЮЩЕЕ ИЛИ и с первым входом восьмого триггера, единичный выход которого подключен к второму входу третьего элемента ИСКЛЮЧАКЩЕЕ ИЛИ, выход которого соединен с первым входом девятого триггера, единичный выход которого соединен с первым входом десятого триггера, единичный выход которого подключен к первому входу одиннадцатого триггера, единичный выход которого соединен с первым входом третьего элемента И и с вторым входом первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, выход которого подключе к первому входу второго элемента И, второй вход которого является пятым входом декодирующего блока, первым и третьим входами которого являются соответственно первьй и второй входы первого элемента И, шестым входом декодирующего блока является второй вход третьего элемента И, выход которого является дополнительным выходом декодирующего блока, основными выходами которого являются инверсные выходы первого, вторго, третьего, четвертого, пятого,

1

естого, седьмого, восьмого, девятого, десятого и одиннадцатого триггеров, вторые и третьи входы которых соответственно объединены являются оовтветствённо вторым и етвертым входами декодирующего блоа.

4 о Устройство по п. 1, отличающееся тем, что анализатор содержит шесть элементов И, элемент ШШ-НЕ и элемент НЕ, выхоД которого соединен с первым входом элемента ИЛИ-НЕ, второй вход которого соединен с первым входом первого элемента И и с выходом второго элемента И, первый вход которого соединен с вькодом третьего элемента И, первый входкоторого подключен к выходу четвертого элемента И, выход пятого элемента И соединен с вторым входом второго Элемента И, выход шестого элемента И подключен к второму входу третьего элемента И, вход элемента НЕ соединен с вторым входом первого элемента И и является дополнительным входом анализатора, основными входами которого являются входы четвертого, пятого и шестого элементов И, первым выходом анализатора является выход элемента НЕ, выход шестого элемента И является вторым выходом анализатора, третьим, четвертым и пятым выходами которого являются соответственно выход пятого элемента И, выход третьего элемента И и выход первого элемента И,

5. Устройство по п. 1, отличающееся тем, что блок исправления ошибок содержит три триггера, два элемента И, два элемента И-НЕ, элемент ИЛИ-НЕ и элемент НЕ, выход которого соединен с первым входом первого элемента И, второй вход которого подключен к первому входу первого триггера и к первому входу второго элемента И, второй вход которого соединен с первым входом второго триггера, с входом э элемента НЕ и с первым входом третье го триггера, выход которого подключен к первому входу первого элемента И-НЕ, второй вход которого подключен к вьЬсоду второго триггера, второй вход которого соединен с вторым входом первого триггера, выход второго элемента И-НЕ подключен к первому входу элемента ИЛИ-НЕ, выход

которого подключен к второму входу третьего триггера, выход которого является четвертым выходом блока исправления ошибок., первым, вторым и третьим выходами которого являются соответственно выход второго элемента И, выход первого триггера и выход первого элемента И, второй вхо элемента ИЛИ-НЕ является первым входом блока исправления ошибок, вторым и третьим входами которого являются соответственно второй и первый входы первого триггера, первый вход второго триггера является четвертым входом блока исправления ошибок, пя,тым, шестым и седьмым входами коiToporo являются соответственно первый вход второго элемента И-НЕ, третий вход элемента ИЛИ-НЕ и второй вход второго элемента И-НЕ, причем выход первого элемента И-НЕ является пятым выходом блока исправления ошибок.

6. Устройство по п. .1, отличающееся тем, что блок сравнения содержит четыре элемента . ИСКЛЮЧАЮЩЕЕ ИЛИ, элемент ШШ-НЕ, элемент И, первый вход которого подключен К выходу элемента ИЛИ-НЕ, первый, второй, третий и четвертый входы которого соединены с выходами соответственно первого, второго третьего и четвертого элементов ИСКЛЮЧАЩЕЕ ИЛИ, входы которых являются основными входами блока сравнения, дополнительным входом которог

11

является второй вход элемента И, выход которого является выходом блока сравнения.

7. Устройство по п. 1, отличающее ся тем, что блок управления коммутатором содержит счетчик, дешифратор, триггер, три элемента И, два элемента ИЛИ и элемент НЕ, вход которого подключен к первому входу первого элемента И и к первому входу второго элемента И выход которого соединен с первым входом триггера, второй вход которого соединен с выходом первого элемента ИЛИ,первый вход которого подключен к первому выходу дешифратора, вторые выходы которого соединены с входами второго элемента ИЛИ, выход которого подключен к второму входу первого элемента И, выход элемента НЕ соединен с первым входом третьего элемента И, второй вход которого подключен к выходу триггера выход третьего элемента И соединен с входом счетчика, выходы которого подключены к входам дешифратора, вторые выходы которого являются управляющими выходами блока управления коммутатором, тактовым выходом которого является выход первого элемента И, вход элемента-НЕ, второй вход первого элемента ИЛИ и второй вход второго элемента И являются соответственно первым, вторым и третьим входами блока управления коммутатором.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для коррекции ошибок в блоках памяти | 1985 |

|

SU1257708A1 |

| СПОСОБ И ДЕКОДИРУЮЩЕЕ УСТРОЙСТВО ИСПРАВЛЕНИЯ ДВУХ ОШИБОК В ПРИНИМАЕМОМ КОДЕ | 2006 |

|

RU2336559C2 |

| Декодирующее устройство | 1989 |

|

SU1644223A1 |

| Устройство декодирования произведений кодов Рида-Соломона | 2017 |

|

RU2677372C1 |

| УСТРОЙСТВО ДЕКОДИРОВАНИЯ КОДОВ РИДА-СОЛОМОНА | 2010 |

|

RU2441318C1 |

| Декодирующее устройство линейного циклического кода | 1990 |

|

SU1718386A1 |

| Устройство для декодирования с исправлением ошибок | 1986 |

|

SU1411981A1 |

| Устройство для исправления ошибок | 1984 |

|

SU1216832A1 |

| Устройство для обнаружения ошибок в блоках памяти | 1985 |

|

SU1249593A1 |

| Устройство для вычитания | 1987 |

|

SU1418703A1 |

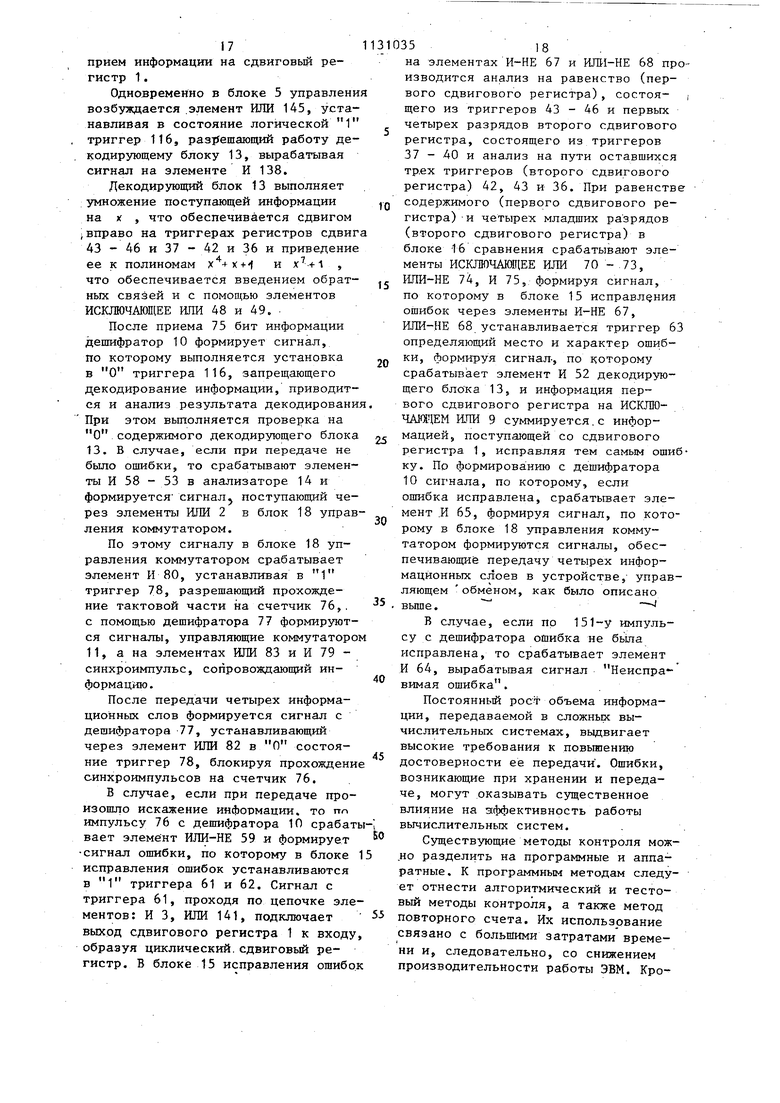

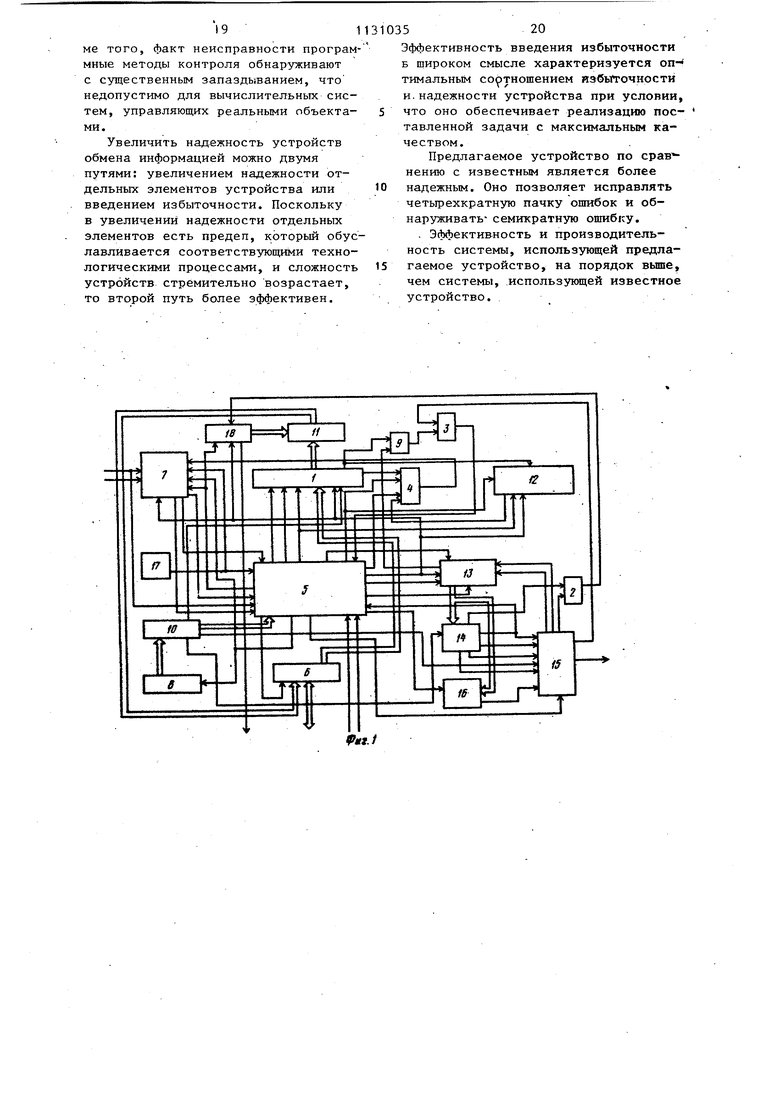

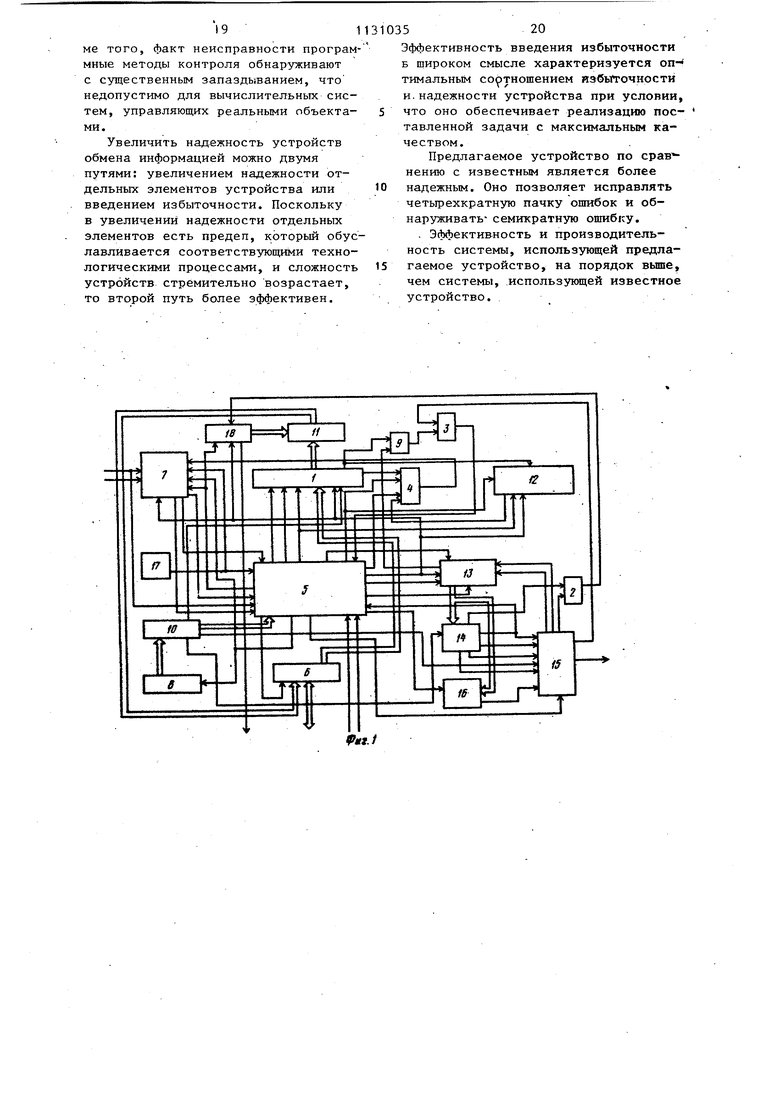

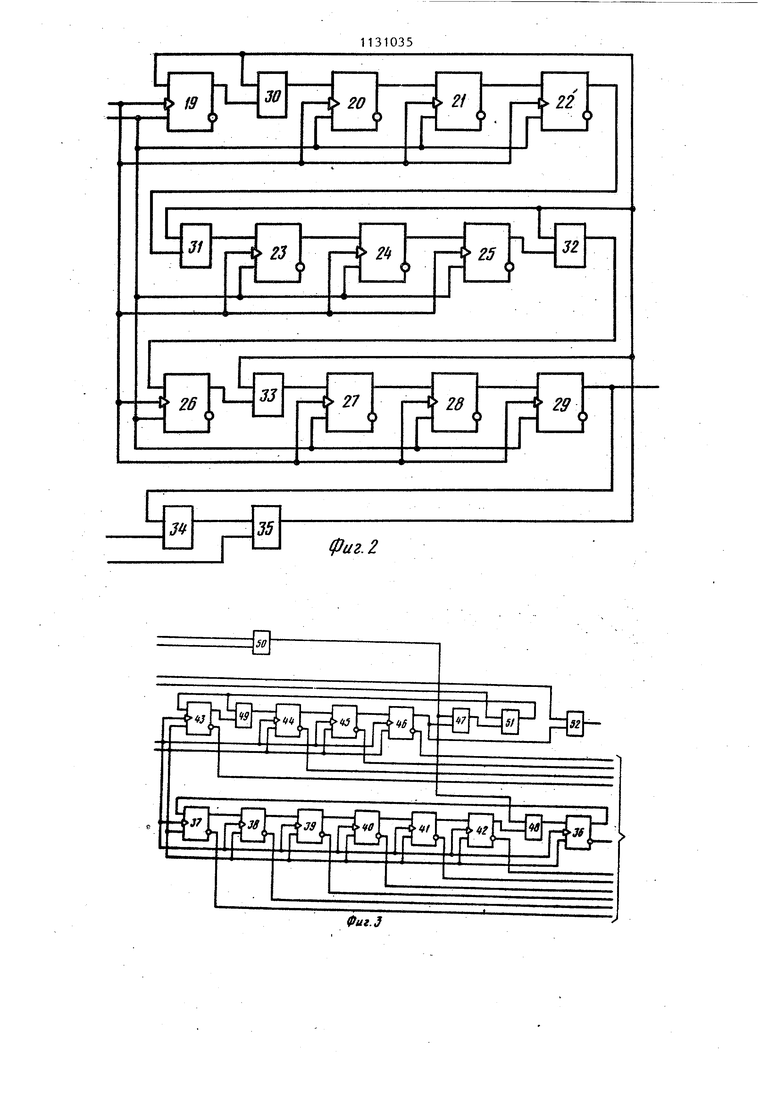

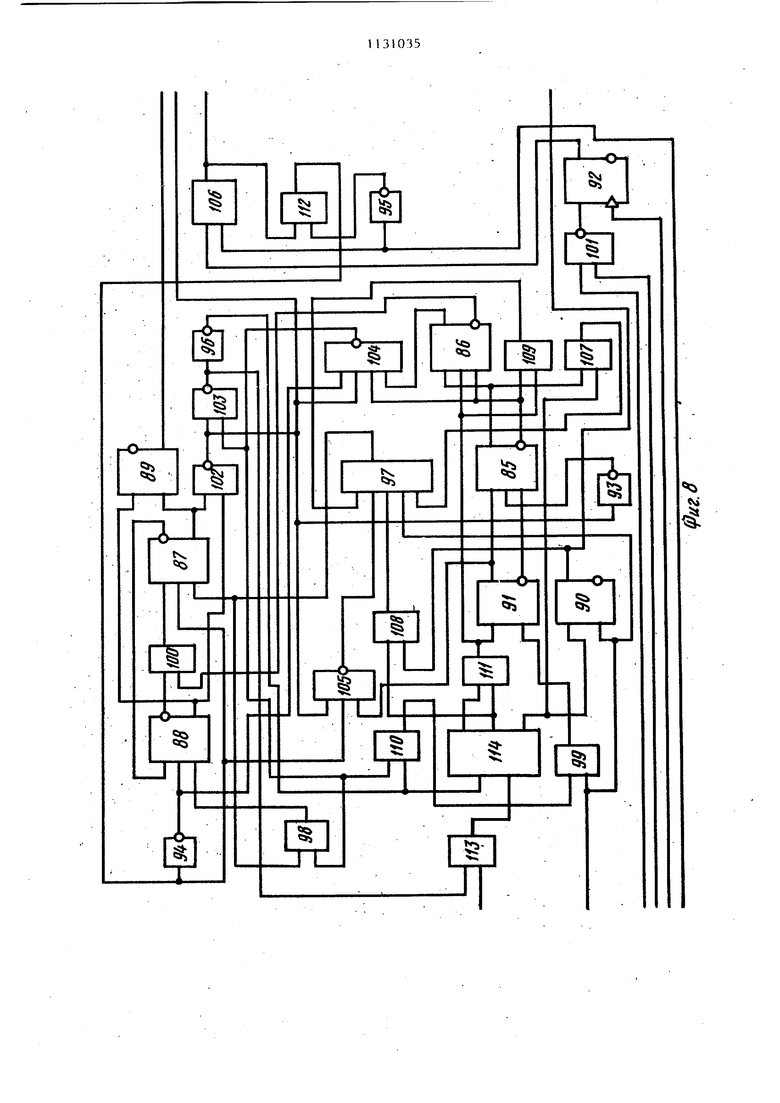

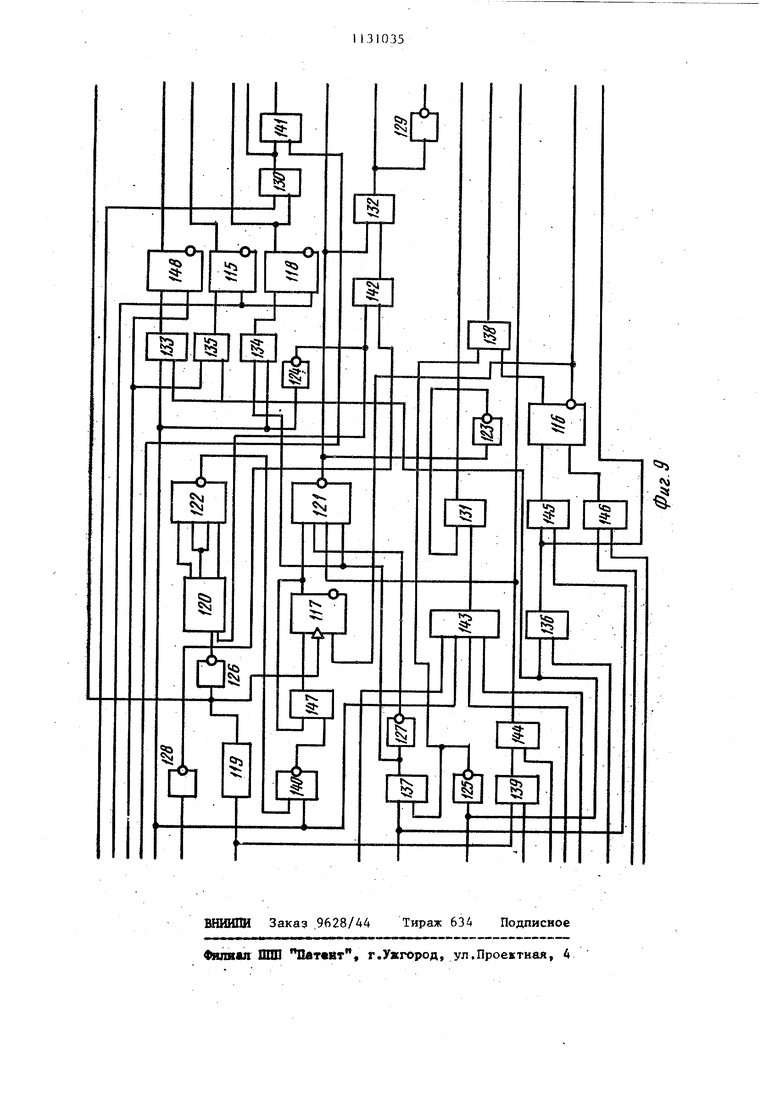

1. УСТРОЙСТВО ДЛЯ ОБМЕНА ИНФОРМАЦИЕЙ, содержащее счетчик, выходы которого соединены с входами дешифратора, основные выходы которого подключены к соответствующим входам блока управления, первый, второй и третий выходы которого соединены соответственно с первым, вторым и третьим входами сдвигового регистра, преобразователь кода, кодирующий блок, декодирующий блок, блок управления коммутатором, управляющие выходы которого подключены к первым входам коммутатора, выходы которого соединены с первыми входами буферного регистра, отличающеес я тем, что, с целью повышения достоверности за счет исправления групповой ошибки, в него введены элемент И, элемент 2И-ИЛИ-НЕ, элемент ИСКЛЮЧАЩЕЕ ИЛИ, элемент ИЛИ., блок сравнения, блок исправления ошибок, анализатор и генератор, выход которого соединен с первым входом преобразователя кодаи с первым дополнительньм входом блока управления, четвертый выход которого подключен к первому входу декодирз тощего блока, основные выходы соединены с основными входами анализатора и с основными входами блoJca сравнения, дополнительный вход которого соединен с пятым выходом блока управления, шестой выход ко-торого подключен к первому входу блока исправления ошибок, второй вход которого соединен с первым выходом анализатора и с вторым дополнительным входом блока управления, седьмой выход которого соединен с входом счетчика и с вторым входом преобразователя кода, первый, второй и третий выходы которого подключены.со(Л oTiBeTCTBeHHo к третьему, четвертому и пятому дополнительным входам блока управления, шестой дополнительный вход которого соединен с третьим входом преобразователя кода,-четвертый вход которого соединен с пер|вым входом блока управления коммусо татором и с восьмым выходом блока управления, девятый выход которого подключен к второму входу декодируюоо ел щего блока, к первому входу кодирующего блока, к четвертому входу сдвигового регистра, к второму входу блока управления - коммутатором и к пятому входу преобразователя кода, шестой вход которого соединен с выходом элемента 2И-ИЛИ-НЕ, первый вход которого Соединен с десятым выходом блока управления, одиннадцать и. двенадцатьгй выходы которого подключены соответственно к третьему и четвертому входам декодирующего блока, : дополнительный выход которого соединен с первым входом элемента

Изобретение относится к технике связи и может быть использовано в вычислительных системах для передачи информации по каналам связи.

Изве1 тно устройство для передачи и приема данных, содержащее передающий сдвиговый регистр, соединенный группой входов с регистром переда чи данных, входы которого соединены с информйционным буферным регистром, вторая группа выходов которого соединена с управляющим регистром, выход которого соединен с блоком управления передачей, блок выборки.

первый выход которого соединен с блоком управления передачей, .регистр состояния, ВХОД7ВЫХОД которого соединен с блоком прерьгоания, регистр приема данньк, группа входов которого соединена с приемным сдвиговым регистром, первый вход которого соединен с входом устройства, с блоком синхронизации и с входом блока контроля по четности, выход которого соединен с блоком управления приемом, блок управления приемом, вход которого соединен с управляющим регистром, тактовый генератор, соединенный с блоком синхронизации l. Недостатком этого устройства является значительное число связей с объектом, что приводит к увеличению габаритов и снижению надежности устройства. Наиболее близким техническим решением к изобретению является уст ройство для обмена информацией, сод жащее счетчик, выходы которого соед нены с входами дешифратора, основны выходы которого подключены к соответствующим входам блока управления первый, второй и третий выходы которого соединены соответственно с первым, вторым и третьим входами сдвигового регистра, преобразовател кода, кодирунлций блок, декодирующий блок, блок управления коммутатором, управляющие выходы которого подключены к первым входам коммутатора, в ходы которого .соединены с первыми входами буферного регистра 23, Однако известное устройство обладает недостаточной достоверностью Цель изобретения - повьшение дос товерности за счет исправления груп повой ошибки. . . Для этого в устройство для обмена информацией, содержащее счетчик, выходы которого соединены с входами дешифратора, основные выходы которого подключены к соответствующим входам блока управления, первый, второй и третий выходы которого соединены соответственно с первым, вторым и третьим входами сдвигового регистра, преобразователь кода, кодирующий блок, декодирующий блок, блок управления коммутатором, управляющие выходы которого подключены к первым входам коммутатора, выходы которого соединены с первыми входами буферного регистра, введены элемент И, элемент 2И-ИЛИ-НЕ,. элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, элемент ИЛИ, блок сравнения, блок исправления ошибок, анализатор и генератор, выход которого соединен с первым входом преобразователя кода и с пер Ьым дополнительным входом блока управления, четвертый выход которого подключен к первому входу декодирующего блока, основные вьпсоды которого соединены с основными входами анализатора и с основными входами блока сравнения, дополнительный вход которого соединен с пятым выхо дом блока управления, шестой выход которого подключен к первому входу блока исправления ошибок, второй вход которого соединен с первым выходом анализатора и. с вторым дополнительньм входом блока управления, седьмой выход которого соединен С входом счетчика и с вторым входом преобразователя кода, первый, второй и третий выходы которого подключены соответственно к третьему, четвертому и пятому дополнительным входам блока управления, шестой до-полнительный вход которого соединен с третьим входом преобразователя кода четвертый вход которого соединен с первым входом блока управления коммутатором и с восьмым выходом блока управления, девятый выход которого подключен к второму входу декодирующего блока, к первому входу кодирующего блока, к четвертому входу сдвигового регистра, к второму входу блока управления коммутатором и к пятому входу преобразователя кода,, шестой вход которого соединен с выходом элемента 2И-ШШ-НЕ, первый вход которого соединен с десятым выходом блока управления, одиннадцатый и двенадцатый выходы которого подключены соответственно к третьему и четвертому входам декодирующего блока, дополнительный выход которого соединен с первым входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, второй вход которого подключен к первому выходу сдвигового регистра и к второму входу кодирующего блока, третий вход которого соединен с вторым входом элемента 2И-ИЛИ-НЕ и с тринадцатым выходом блока управления, четырнадцатый выход которого соединен с управляющим входом буферного регистра, выходы которого подключены к пятым входам сдвигового регистра, тестой вход которого соединен с первым дополнительным выходом дешифратора, второй дополнительный выход которого соединен с третьим входом блока исправления ошибок, четвертый, пятый и шестой входы которого подключены соответственно к второму, третьему и четвертому выходам анализатора, пятый выход которого соединен с первым входом элемента ИЛИ, второй вход которого подключен к первому iвыходу блока исправления ошибок, второй выход которого соединен с первым входом элемента И, выход которого подключен к седьмому дополнительному входу блока управления, третий выход которого соединен с четвертым входо кодирующего блока, вьЬсод которого соединен с третьим входом элемента 2И-ИЛИ-ПЕ, четвертый вход которого подключен к второму выходу сдвигового регистра, третьи выходы которого соединены с вторыми входами коммутатора, выход блока сравнения соединен с седьмым входом блока исправления ошибок, третий и четвертый выходы которого соединены соответственно с пятым и шестым входами декодирующего блока, третий дополнительный выход дешифратора подключен к дополнительному вход анализатора, выход элемента ИСКЛЮЧА ЩЕЕ ИЛИ подключен к второму входу элемента И, выход элемента ИЛИ соединен с третьим входом блокауправления коммутатором, тактовый выход которого является синхронизирующим выходом устройства для обмена информацией, синхронизирующим входо - которого является синхронизирующий вход блока управления, шестой дополнительный вход.которого является управляющим входом устройства для обмена информацией, контрольным выходом которого является пятьй выход блока исправления ошибок, инфор мационными входами устройства для обмена информацией являются информационные входы преобразователя кода и буферного регистра, информационные вькоды которых являются информационными выходами устройства для обмена информацией, входом начальной установки которого является восьмой дополнительный вход блока управления. ПРИ этом кодирующий блок содержит одиннадцать триггеров, пять элементов ИСКЛЮЧАЮЩЕЕ ШШ и элемент выход которого соединен с первым входом первого элемента ИСКЛЮЧАЮЩЕЕ ШШ, с первым входом второго. элемента ИСКЛЮЧАЮЩЕЕ ИЖ, с первым входом третьего элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, с первым входом четвертого :элемента ИСКЛЮЧАМЦЕЕ ИЛИ и с первым входом первого триггера, выход которого соединен с вторым входом первого элемента ИСКЛЮЧАНЩЕЁ ШШ, выход которого соединен с первым входом второго тригг ера, выход которого соединен с первым входом третьего агриггера, выход которого соединен с первым четвертого триггера, выход которого подключен к второму входу второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, выход которого соединен с первым входом пятого тригге- ра, выход которого соединен с первым входом шестого триггера, выход iKOToporo соединен с первым входом седьмого триггера, выход которого подключен к второму входу третьего элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, выход которого соединен с первым входом восьмого триггера, выход которого подключен к второму входу четвертого элемента ИСКЛЮЧАКШЩЕ ИЛИ, выход которого соединен с первым входом девятого триггера, выход которого соединен с первым входом десятого триггера, выход .которого соединен с первьм входом одиннадцатого триггера, выход которого подключен к первому входу пятого элемента ИСКЛОЧАЮЩЕЕ ИЛИ, выход которого соединен с первым входом элемента И, второй вход которого является третьим входом кодирующего блока, причем вторые и третьи входы первого, второго, третьего, четвертого, пятого, шестого, седьмого, восьмого девятого, десятого и одиннадцатого триггеров соответственно объединены и являются соответственно первым и четвертым входами кодирующего блока, вторым входом которого является второй вход пятого элемента ИСКЛЮЧАЩЕЕ ИЛИ, первый вход которого является выходом кодирующего блока. При этом декодирующий блок содержит 9Диннадцать триггеров, три элемента ИСКЛЮЧАЮ1ЧЕЕ ИЛИ,и три элемента И, причем выход jiepfeoro элемента И соединен с первым входом первого э лемента ИСКЛЮЧАКШЩЕ Ш1И и с первым входом второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, выход которого соединен с первым входом первого триггера, единичньй вьпсод которого соединен с первым входом второго триггера, единичный выход которого соединен с первым входом третьего триггера, единичный выход которого соединен с первым входом четвертого триг.гера, единичный выход которого соединен с первым входом пятого триггера, единичный выход которого Соединен с первым входом шестого триггера, единичный выход которого соединен с первым входом седьмого триггера, единичный выход которого соединен с втррым входом второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, выход второго элемента И соединен с первым входом третьего элемента ИСКЛЮЧАЮЩЕЕ ИЛИ и с первым входом восьмого триггера, единичный выход которого подключен к второму входу третьего элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, выход которого,соединен с первым входомдевятого триггера, единичный выход которого соединен с первьм взсодом десятого триггера, единичный выход которого подключен к первому одиннадцатого триггера, единичньй выход которого соединен с первьм входом третьего элемента И и с вторым входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, выход которого подключен к первому входу вт рого элемента И, второй вход которо является пятым входом декодирующего блока, первым и третьим входами которого являются соответственно первый и второй входы первого элемента И, шестым входом декодирующего блок является второй вход третьего элеме та И, выход которого является допол нительным выходом декодирз зщего блока, основными выходами которого являются инверсные выходы первого, второго, третьего, четвертого, пятого, шестого, седьмого, восьмого, девятого, десятого и одиннадцатого триггеров, вторые и третьи входы ко торых соответственно объединены и являются соответственно вторым и четвертым входами декодирующего бло ка. При этом анализатор содержит шесть элементов И, элемент ИЛИ-НЕ и элемент НЕ, выход которого соединен с первым входом элемента ИЛИ-НЕ второй вход которого соединен с первым входом первого элемента И и с выходом второго элемента И, первый вход которого соединен с выходом третьего элемента И, первый вход которого подключен к выходу четвертого элемента И, выход пятого элемента И соединен со вторым входо второго элемента И, выход шестого элемента И подключен к второму входу третьего элемента И, вход эле мента НЕ соединен с вторым входом первого элемента И и является дополнительным входом анализатора, основными входами которого являются входы четвертого, пятого и шестого элементов И, первым выходом анализатора является выход элемента НЕ, выход шестого элемента И является вторым выходом анализатора, третьим четвертым и пятым выходами которого являются соответственно выход пятого элемента И, выход третьего элемента И и выход первого элемента И. При этом блок исправления ошибок содержит три триггера, два элемента И два элемента И-НЕ, элемент ИЛИ-НЕ и элемент НЕ, выход которого соединен с первым входом первого элемента И, второй вход которого подключен к первому входу первого триггера и к первому, входу второго элемента И второй вход которого соединен с первым входом второго триггера, с входом элемента НЕ и с первым входом третьего триггера, выход которого подключен к первому входу первого элемента И-НЕ, второй вход которого подключен к выходу второго триггера, второй вход которого соединен с вторым входом первого триггера, выход второго элемента И-НЕ подключен к первому входу элемента ИЯИ-НЕ, . выход которого подключен к второму входу третьего триггера, выход которого является четвертым выходом блока исправления ошибок, первым, вторым и третьим выходами которого являются соответственно выход второго элемента И, выход первого триггера и выход -первого элемента И, второй вход элемента ИПИ-НЕ является первым входом блока исправления, ошибок, вторым и третьим входами которого являются соответственно второй и первый входы первого триггера, первый вход второго триггера явтяется четвертьм входом блока исправления ошибок, пятым, шестым и седьмым входами которого ябляются соответственно первый вход второго элемента И-НЕ, третий вход элемента ИЛИ-НЕ и второй вход второго элемента И-НЕ, причем выход первого элемента И-НЕ является пятым выходом йлока исправления ошибок. При этом блок сравнения содержит четьфе элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, элемент ИЛИ-НЕ, элемент И, первый вход которого подключен к выходу элемента ИЛИ-НЕ, первый, второй, третий и четвертый входы которого с пдинены с выходами соответственно первого, второго, третьего и четвертого элементов ЙСКЖ1ЧАЮЩЕЕ ИЛИ,входы которых являются основными входами блока сравнения, дополнительным входом которого является второй .9 вход элемента И, выход которого является выходом блока сравнения. При этом блок управления коммутатором содержит счетчик, дешифрато триггер, три элемента И, два элемен та ИЛИ и элемент НЕ, вход которого подключен к первому входу первого элемента Инк первому входу второго элемента И, выход которого соеди нен с первым входом триггера, второй вход которого соединен с выходом первого элемента ИЛИ, первый вх которого подключен к первому выходу дешифратора, вторые выходы которого соединены с входами второго эл мента ИЖ, выход которого подключен к второму входу первого элемента И, выход элемента НЕ соединен с первым входом третьего элемента И, второй вход которого под1ключен к вы ходу триггера, выход третьего элемента И соединен с входом счетчика, выходы которого подключены к входам - дешифратора, вторые выходы которого являются управляющими выходами блок управления коммутатором, тактовым выходом которого является выход первого элемента И, вход элемента Н второй вход первого элемента PfflH и Второй вход второго элемента И являются соответственно первым, вто рым и третьим входами блока управления коммутатором. На фиг. 1 изображена структурная электрическая схема устройстваj на фиг. 2 - структурная электрическая схема кодирующего блока,.на . фиг. 3 - структурная электрическая схема декодирующего блокаj на фиг.4 , структурная электрическая схема анализатораi на фиг, 5 -. структурна электрическая схема блока исправ/ления ошибок на фиг. 6 - структурная электрическая схема блока сравнения-, на фиг, 7 - структурная электрическая схема блока управления коммутатором; на фиг, 8 - струк турная электрическая схема преобразователя кода на фиг, 9 - структур ная электрическая схема блока управ |Ления, , Устройство для обмена информации содержит сдвиговый регистр 1, элемент ИЛИ 2, элемент И 3, элемент 2И-ИЛИ-НЕ 4, блок 5 управления. буферньй регистр 6, преобразователь 7 кода, счетчик 8, ИСКЛЮЧАЮЩЕЕ ИЛИ дешифратор 1@, коммутатор 11, коди,рующий блок 12, декодирующий блок 1 5 анализатор 14, блок 15 исправления ошибок, блок 16 сравнения, генератор 17, блок 18 управления коммутатором. Кодирующий блок содержит первый, второй, третий, четвертый пятый, шестой, седьмой, восьмой, девятый, десятьй и одиннадцатый триггеры 19 29, первый, второй, третий, четвертый и пятый элементы ИСКЛЮЧАЮЩЕЕ ИЛИ 30-34 и элемент И 35. / Декодирующий блок содержит первый, второй, третий, четвертый, пятый, шестой, седьмой, восьмой, девятый, десятый и одиннадцатый триггеры 36 - 46, первый, второй и третий элементы ИСКЛЮЧАЮЩЕЕ ИЛИ 47 - 49, первый, второй и третий элементы И 50 - 52. Анализатор содержит первый, второй, третий, четвертый, пятьш и шестой элементы И 53 - 58. элемент ИЛИ-НЕ 59, элемент НЕ 60. БЛОК исправления ошибок содержит первый, второй и третий триггеры 61 - 63, первый и второй элементы И 64 и 65, первый и второй элементы И-НЕ 66 и 67, элемент ИЛИ-НЕ 68, элемент НЕ-69. Блок сравнения содержит первьш, второй, третий и четвертьш элементы ИСКЛЮЧАЮЩЕЕ ИЛИ 70-73, элемент ИЛИ-НЕ 74, элемент И 75. Блок управления коммутатором содержит счетчик 76, дешифратор 77, триггер 78, первый, второй и третий элементы И 79, 80 и 81, первый и второй элементы ИЛИ 82 и 83, элемент НЕ 84. Преобразователь кода содержит первый, второй, третий, четвертый, пятый, шестой, седьмой и восьмой триггеры 85 - 92, первый, второй, третий, четвертый элементы НЕ 93 - 96, первый, второй, третий и четвертый элементы ИЛИ 97 - 100, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 101, первый второй, третий и четвертьй элементы ИЛИ-НЕ 102 - 105, переключающий элемент 106, первый, второй, третий, четвертый, пятый, шестой и седьмой элементы И 107 - 113, счетчик 114. Блок управлен дя содержит первый второй, третий и четвертый триггеры 115 - 118, первый и второй счетчики 119 и 120, первый и второй элементы 2И-ИЛИ-НЁ 121 и 122, первый, второй, третий, четвертьй, пятьй, шестой,и седьмой элементы НЕ .123 129, первьй, второй третий, четвертый, пятый, шестой, седьмой, восьмой, девятый, десятьш элементы И 13 139, элемент И-НЕ 140, первый, второй, третий, четвертый, пятый и шестой элементы ИЛИ 141 - 146, элемент ИСКЛЮЧАЩЕЕ ИЛИ 147, пятый триггер 148. Устройство работает следующим образом. Помехоустойчивое кодирование сос тоит в наложении на передаваемое сообщение некоторых дополнительных условий за счет введения- избыточной информации. На приемной стороне осуществляется проверка этих условий. Если ошибок не бьто, то все условия выполняются и принятая информаДия считается достаточной. Есл возникли не слишком большие (4 бита информации) искажения, то некоторые из условий не выполняются. Сост невыполненных условий определяет наличие и местоположение ошибок в кодовой комбинации. Предложим, что передавался кодовый вектор {f tx.i и появилась пачка ошибок ). Тогда на выходе получен вектор .f(xHiВ (3 . На основ полученного вектора можно производить проверку на четность, деля многочлен f(x)-х- В (у) на многочлен |(х) , порождающий код, и сохраняя остаток, которьй должен быть равен О, если на выходе получен кодовый вектор, и не равен О при возникновении ошибок. В последнем случае остаток содержит информацию об ошиб ках. Поскольку f (X )1 - кодовый-вектор, то многочлен (хУ делится на ( и, следовательно, .остаток равен остатку от деле;ния многочлена (x)J н (U). Пусть x-B(x) «j(xl5(x) р(х) , где степень многочлена R(x) меньше /п-К, степени «(х). Задача исправления ошибок состоит в том, чтобы ., зная результат проверочных в гчислеНИИ R{K| , найти многочлен х В(х) т.е. точно определить расположение ошибок. Процесс исправления ошибок сво- ,дится к следующему: умножить. RX.X) на X и привести полученный многочлен по модулю (.)() т.е. разделить многочлен X и рассмотреть остаток; проверить, будет ли полученный многочлен исправимой комбинацией ошибок. Если будет, то перейти к 1 5 третьему шагу. Если не будет, то повторять первый и второй шаги до тех пор, пока это условие не будет удовлетворено, или до тех пор, пока первьм и второй шаги не будут повторены h раз;. i если после Л шагов остаток окажется исправимой комбинацией ошибок, то образующий вектор смежного класса равен ., (i)5 так, что, если при передаче появилась исправимая .комбинация ошибок, она будет исправлена после того, как из полученного на выходе вектора будет вычтен вектор R (.xjTj если получаюпщеся остатки не совпадают ни с одной из исправимых комбинаций ошибок, то это значит, что обнаружена неисправимая комбинация ошибок. Обоснование этого процесса проводится следующим образом. Предположим, что появилась некоторая комбинация ошибок/ Е).Йусть R(xl - результат проверочных вычислений, т.е. .( (2(х)( х) ..Далее, пусть остаток полученный после умножения f(xl на х и деления произв.едения «(.х равен R(xl . Тогда XVR(x) 5(i(l5(x),(x| х e((xl (х| 5{x|-i-()c)5.,(x) откуда следует, что вектор хE(x)-((x) принадлежит коду и что оба вектора (,x)J и ( должны входить в один и тот же смежньй класс. Если вектор ) определяет комбинацию ошибок, которая может быть обнаружена, но не исправлена, то никакая другая комбинация й,(к) принадлежащая тому же самому смежному классу, также не может быть исправлена. В этом случае в качестве остатка на втором шаге не может появиться исправимая комбинация ошибок. Предположим теперь, 4Toj;E(x)j .Я В (х) - исправимая комбинация ошибок, и пусть U n-j , тогда x((x) х 8(х|- х(х) S(xfi -()BCxl- x,5(x)S{xH 8(х) и так как многочлен делится Hd {х) 1, а степень многочлена В(х.) меньше, уем n-k - степень (х) то в(х) должен быть остатком от деления многочлена xRlxi на («) Таким образом, после n-j шагов в качестве остатка появится исправимая комбинация ошибок, именно В/(х) ,. Предположим - что {({)х В (x)J где B{xV неисправимая комбинация ошибок и дотуустим, что после умно13жения на х возникает исправийая комбинация ошибок . Тогда векторы -f ( х| (х)}оба принадлежат одному и тому же смежному кла су, и так как оба задают исправимые комбинации ошибок, то они дол ны совпадать. Если следовать описан ному процессу исправления ошибок, то нужно взять в качестве комбинации ошибок вектор R(x) и считать, что эта комбинация расположен в полученном после передачи векторе, начиная с (,р-i J- -и компонент Таким образом, вектор ошибок равен у-и(хП ,(xlj (X) (х)Ь-Сх.: (х) В(х) , что дает исход ньй результат. Процесс исправления ошибок сводится к трем этапам: кодирования информации, декодирова:ние информации и исправление ошибок. Предположим, передается вектор f(x)5 . Процедура кодирования заключается в умножении кодового вектора на X и-приведении его к полно му ( xV х ч-X 1) , В результате чего получается остаток R(x) который передается следом за кодовы вектором. Если при передаче появилась пачка ошибок (х1 , тогда передава мый вектор равен (х} к-) B(x)J . Декодирование вьтолняется путем умножения кодового вектора на х и приведении его к полиному (x-t-.х + + 4-х - x+i), который удобно представить в виде р(х|()(И) ,( +1)( x+где р(,х) неприводимьй многочлен сте пени m , в нашем сшучае равньй ,( t) , порядок корней которого равен . ,е ( 15), причем р(х| и (+1) выбираются таким образом, . чтобы Р не делилось на С, т,е. .17 не делится на 7. Длина кода ft равна наименьшему общему кратному чисел 2 и С потому что именно в этом случае многочлен дёлит ся на (х) . Число проверочных символов равно Cf m , а число информационных символов k f -c--iVT 105-11 94. Можно получить код меньшей длины с тем же самым числом проверочньЬс символов, если просто заменить некоторые информационные символы нулями и не учитьшать ихв передаваемом и получаемом векторах. 514 Используя эти коды, можно испра-. вить любую одиночную пачку ошибок, длина которой равна 4 символам или меньше. Проверочные вычисления состоят .,в делении многочлена (х) + х в{х) отдельно на р(х) и Ha{v +-1, Для кодового вектора оба остатка будут равны нулю, а если они не равны нулю, то в них содержится информация об ошибке. Поскольку ( х) кодовый вектор и, следовательно, делится и на р(х) и на X +1 , остатки от деления будут совпадать с остатками от деления многочлена (х) соответственно на р(х) и на X М. ) P(x)5(x)+R.,(x) (xlc()S(x)R2(xl. где степень многочлена |7(у) меньше m - степени многочлена р(х) , а степень многочлена (i} меньше с, Исправление ошибок выполняется следующим образом. умножить: на х и привести результат по модулю р(х) , т,е. разделить его на р{х) и взять остаток. Умножить на X и привести результат по модулю многочлена у сравнить полученные многочлены. Если они совпадают и их степени меньше пятой, то перейти к третьему шагу. Если это не так, то повторить перЙый и второй шаги до тех пор, пока ти шаги не будут повторены rt раз, если полученные многочлены на каком либо шаге окажутся равными многочленами степени меньше пяти, то оба они равны 6(xi и первый шаг повторяется(п-j раз. Таким образом, комбинация ошибок 6(х) и / |-{ - место, с которого она начинается, найде- на и опгибки иожно исправить, вычитая вектор Г х 8(х) из полученного вектора;. если ни в одном случае полученные многочлены не будут равными мно.гочленами, степень которых меньше пяти, то это значит, обнаружена неисправимая ошибка. Вычисление проверочных символов можно производить, используя два регистра (один для .р(х) , а второй для (. +1) изменяя их таким образом, чтобы в них производилось автоматическое умножение входа на о 151 В 3TH7V устройствах сдвиг с нулевым входом эквивалентен умножению на и приведению результата по модулю соответственно.р( XI или х 1 Перед началом работы из ЭВМ или из какого-либо устройства, управляющего обменом, поступает сигнал Начальная установка в блок 5 управления, по которому через элемент ИЛИ 146 устанавливается триггер 116, формирующий сигнал, по которому устанавливается в 0 сдви говый регистр 1 и триггера ,87 и 88, находящиеся в преобразователе 7 кода, находящийся в блоке 18 управления коммутатором триггер 78, триг гера 1.9,/ 27, 28, 29, 20, 21, 22, 23 24, 25 и 26, находящиеся в кодирующем блоке 12, и триггера 43, 44, 45 46, 37, .38, 39, 40, 41, 42 и 36, на ходящиеся в декодирующем блоке 13, приводя устройство в исходное состо ние.. В режиме работы Передача на третий вход преобразователя 7 кода передается из ЭВМ (не показан) сигнал, разрешающий прием информации. При передаче из устройства, управля щего обменом, синхроимпульса, сопро .вождающего информацию, срабатывают .элементы И 136 и ИЛИ 145, устанав)ливая триггер 116 в единичное состо ние, и информация записывается в буферньй регистр 6, Триггер 116 устанавливаясь в 1, снимает блокировку с триггера 117, формирую щего тактовую частоту 1 МГц, поступающую через элемент 2И-ИЛИ-НЕ 121 на счетчик 8. По первому импульсу с дешифратора ID на элементах: счет чик 120, 2И-ИЛИ-НЕ 122, И-НЕ 140, ИСКЛЮЧАЩЕЕ ИЛИ 147, триггер 117 формируется последовательность импульсов , период первого из которых равен .ЗТ (где Т 0,5 икс), а перио всех последующих импульсов равен 2Т. Эта последовательность импульсо в преобразователе 7 кода формирует на элементах ИСКШЧАИЯЦЕЕ ИЛИ 101, триггере 92 фазоманипулированный код - сначала синхроимпульса, а затем информации. Одновременно первый импульс с дещифратора 10 возбзпкдает алемент И 133 и устанавливает триггер 148 в 1, формируя сигнал, разрешающий кодирование информации. .Кодирующий блок 12 выполняет умножение поступакмцей информации на Х% что обеспечивается сдвигом вправо 5 на триггерах 27, 28, 29, 19, 20-26 и приведение ее к полиному (+x+x -f что обеспечивается введением обратной связи с помощью элементов ИСКПЮЧАЮП1ЕЕ ИЛИ 30-33. После кодирования 16 бит информации с дешифратора 10 формируется сигнал, по которому срабатьшают в блоке 5 управления элементы ИЛИ 143, И 131, формирующие сигнал занесения информации с буферного регистра 6 на регистр 1 сдвига, причем устройство, управляющее обменом, к этому времени должно записать на буферный регистр 6 следующее информационное : слово. Кодирование следуилцих трех слов выполняется аналогично. Зане- сение информации с буферного регистра 6 на регистр 1 сдвига выполняется по сигналам с дешифратора 10. После передачи 64 битов информа- ции по сигналу устанавливается в О триггер 148, запрещая кодирование информации, и через элемент И 135 устанавливается в 1 триггер 115 формируя сигнал, по которому информация с кодирующего блока 12 через элемент 2 И-ИЛИ-НЕ 4 поступит в преобразователь 7 кода. После передачи одиннадцати контрольных бит информации по 76-тактовому импульсу (или по седьмому разряду группы входов) с дешифратора 10 устанавливается в О триггер 115, запрещая прохозкдение контрольной информации с кодирующего блока 12, и триггер 116, устанавливая в исходное состояние устройство. В режиме работы Прием иа третий вход преобразователя 7 кода передается из ЭВМ сигнал уровнем логического , разрешающий прием информации ; и передачу информации в устройство, управляю цее обменом. В преобразователе 7 кода выполняется преобразование фазомаиип лированного кода на триггерах 87 - 89 и элементах ИЛИ 100 и ИПИ-НЕ 102 и 103 и НЕ 96 и вьщеление синхроимпульса на элементах, счетчик 114, триггера 85, 86, 90 и 91, И 107, 109 и 111 и ИЛИ 99. По вьщелен1во синхроимпульса, определяющему начало поступающей информации в преоё1()азователе 7. кода формируется сигнал, по которому в блоке 5 управления срабатывает элемент И 137, разрешающий формирование на элементе 2И-ИЛИ-НЕ 121 тактовой частоты, обеспечивающей 17 прием информации на сдвиговый регистр 1. Одновременно в блоке 5 управлени возбуждается .элемент ИЛИ 145, устанавливая в состояние логической 1 триггер 116, раз11ешак1щий работу декодирующему блоку 13, вырабатывая сигнал на элементе И 138. Декодирующий блок 13 выполняет умножение поступающей информации на X , что обеспечивается сдвигом jвправо на триггерах регистров сдвиг 43 - 46 и 37 - 42 и 36 и приведение ее к полиномам x +x+f и х + 1 , что обеспечивается введением обратных связей и с помощью элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 48 и 49. После приема 75 бит информации дешифратор 10 формирует сигнал, по которому выполняется установка в О триггера 116, запрещающего декодирование информации, приводится и анализ результата декодировани При этом вьшолняется проверка на О содержимого декодирующего блока 13, В случае, если при передаче не было ошибки, то срабатывают элемен ты И 58 - 53 в анализаторе 14 и формируется сигналJ поступающий через элементы ИЛИ 2 в блок 18 управ ления коммутатором. По этому сигналу в блоке 18 управления коммутатором срабатывает элемент И 80, устанавливая в 1 триггер 78, разрешающий прохождение тактовой части на счетчик 76,. с помощью дешифратора 77 формируются сигналы, управляющие коммутаторо 11, а на элементах ИЛИ 83 и И 79 синхроимпульс, сопровождаюпщй информацию. После передачи четырех информационных слов формируется сигнал с дешифратора 77, устанавливающий через элемент ИЛИ 82 в О состояние триггер 78, блокируя прохождени синхроимпульсов на счетчик 76. В случае, если при передаче произошло искажение информации, то пп импульсу 76 с дешифратора 10 срабат вает элемент ИЯИ-НЕ 59 и формирует сигнал ошибки, по которому в блоке исправления ошибок устанавливаются в 1 триггера 61 и 62. Сигнал с триггера 61, проходя по цепочке эле ментов: ИЗ, ИЛИ 141, подключает выход сдвигового регистра 1 к входу образуя циклический, сдвиговьй регистр. В блоке 15 исправления ошибо 3518 . на элементах И-НЕ 67 и ИШ1-НЕ 68 производится анализ на равенство (первого сдвигового регистра) , состоя- , щего из триггеров 43 - 46 и первых четырех разрядов второго сдвигового регистра, состоящего из триггеров 37 - ДО и анализ на пути оставшихся трех триггеров (второго сдвигового регистра) 42, 43 и 36. При равенстве содержимого (первого сдвигового регистра) -и четырех младших разрядов (второго сдвигового регистра) в блоке 16 сравнения срабатывают элементы ИСКЛЮЧАЮЩЕЕ ИЛИ 70-73, ИЛИ-НЕ 74, И 75,.формируя сигнал, по которому в блоке 15 исправления ошибок через элементы И-НЕ 67, ИЛИ-НЕ 68 устанавливается триггер 63 определяющий место и характер ошибки, формируя сигнал-, по которому срабатывает элемент И 52 декодирующего блока 13, и информация первого сдвигового регистра на ИСКЛЮЧАКХЦЕМ ИЛИ 9 суммируется. с информацией, поступающей со сдвигового регистра 1, исправляя тем самым ошибку. По формирова нию с дешифратора 10 сигнала, по которому, если ошибка исправлена, срабатьшает элемент .И 65, формируя сигнал, по которому в блоке 18 управления коммутатором формируются сигналы, обеспечивающие передачу четырех информационных слоев в устройстве, управляющем обменом, как было описано вьшзе. В случае, если по 151-у импульсу с дешифратора ошибка не бьша исправлена, то срабатывает элемент И 64, вырабатьгоая сигнал Неисправимая ошибка. Постоянный рост объема информации, передаваемой в сложньк вычислительных системах, выдвигает высокие требования к повьшению достоверности ее передачи. Ошибки, возникающие при хранении и передаче, могут оказывать существенное влияние на эффективность работы вычислительных систем. Существующие методы контроля мож.но разделить на программные и аппаратные. К программным методам следует отнести алгоритмический и тестовый методы контроля, а также метод повторного счета. Их использование связано с большими затратами времени и, следовательно, со снижением производительности работы ЭВМ. Кро191

ме того, факт неисправности программные методы контроля обнаруживают с существенным запаздыванием, что недопустимо для вычислительных систем, управляющих реальными объектами.

Увеличить надежность устройств обмена информацией можно двумя путями: увеличением надежности отдельных элементов устройства или введением избыточности. Поскольку в увеличении надежности отдельных элементов есть предел, который обуславливается соответствующими технологическими процессами, и сложность устройств стремительно возрастает, то второй путь более эффективен.

3103520

Эффективность введения избыточности Б широком смысле характеризуется оптимальным соотношением яэбьгточности и.надежности устройства при условии, 5 что оно обеспечивает реализацию пос тавленной задачи с максимальным качеством.

Предлагаемое устройство по срав нению с известным является более 10 надежным. Оно позволяет исправлять четырехкратную пачку ошибок и обнаруживать- семикратную ошибку.

. Эффективность и производительность системы, использующей предла15 гаемое устройство, на порядок выше, чем системы, использующей известное устройство.

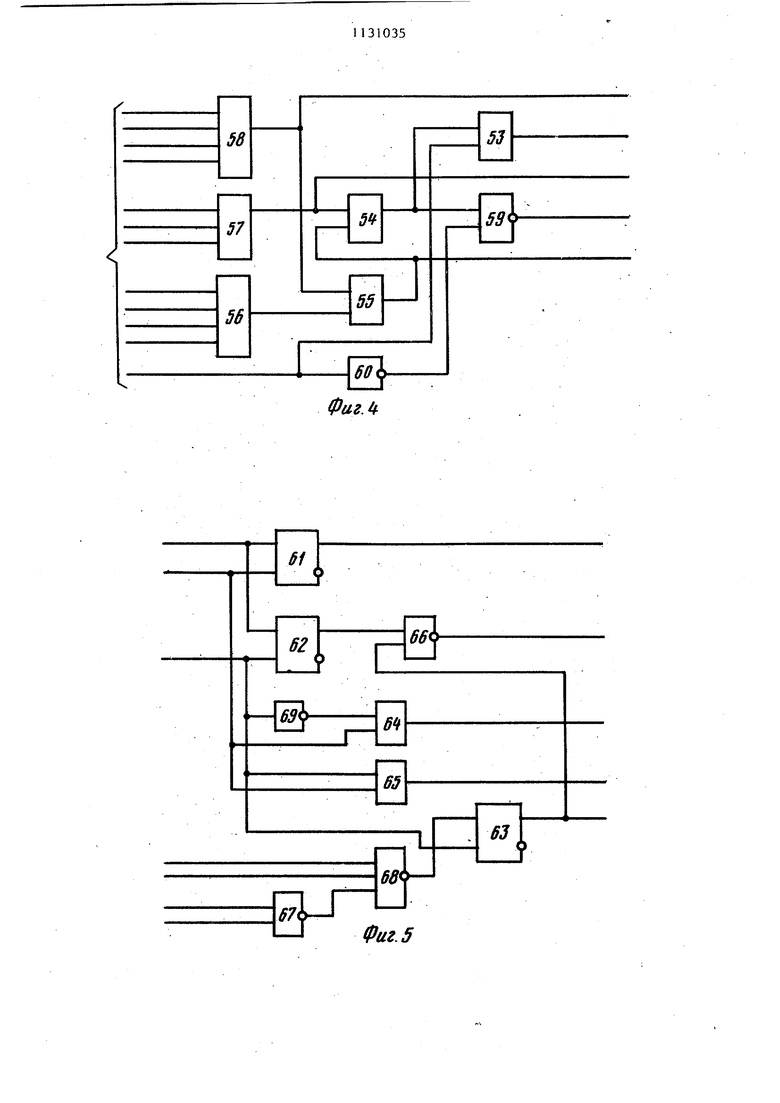

58

53

57

ФигЛ

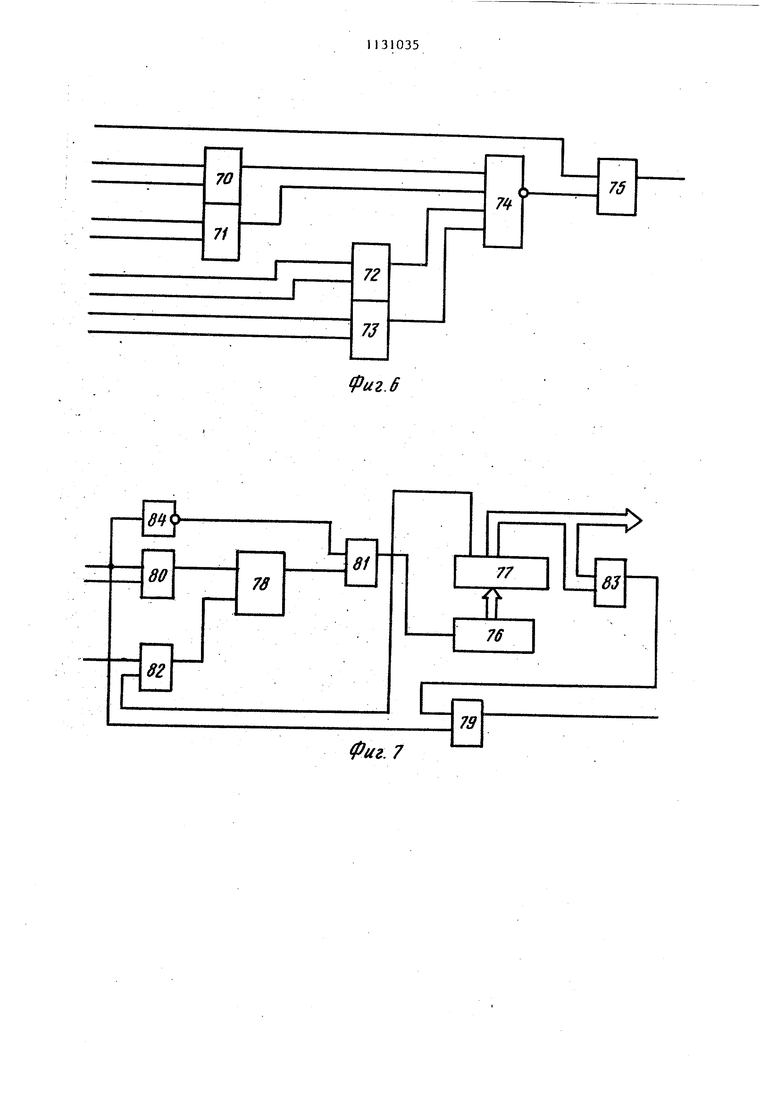

62

Щ66

Фиг, 5

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| ПРИСПОСОБЛЕНИЕ ДЛЯ РАЗРЕЗАНИЯ ТАБАЧНЫХ СКРУТКОВ | 1926 |

|

SU6800A1 |

| DATA BOOK, DATA, Inc | |||

| Cordura, Сотр | |||

| Orange, N.J.Izt | |||

| Edition, 1976, p | |||

| Способ получения кодеина | 1922 |

|

SU178A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Авторское свидетельство СССР по заявке № 3388934/18-09, кл | |||

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1984-12-23—Публикация

1982-12-16—Подача