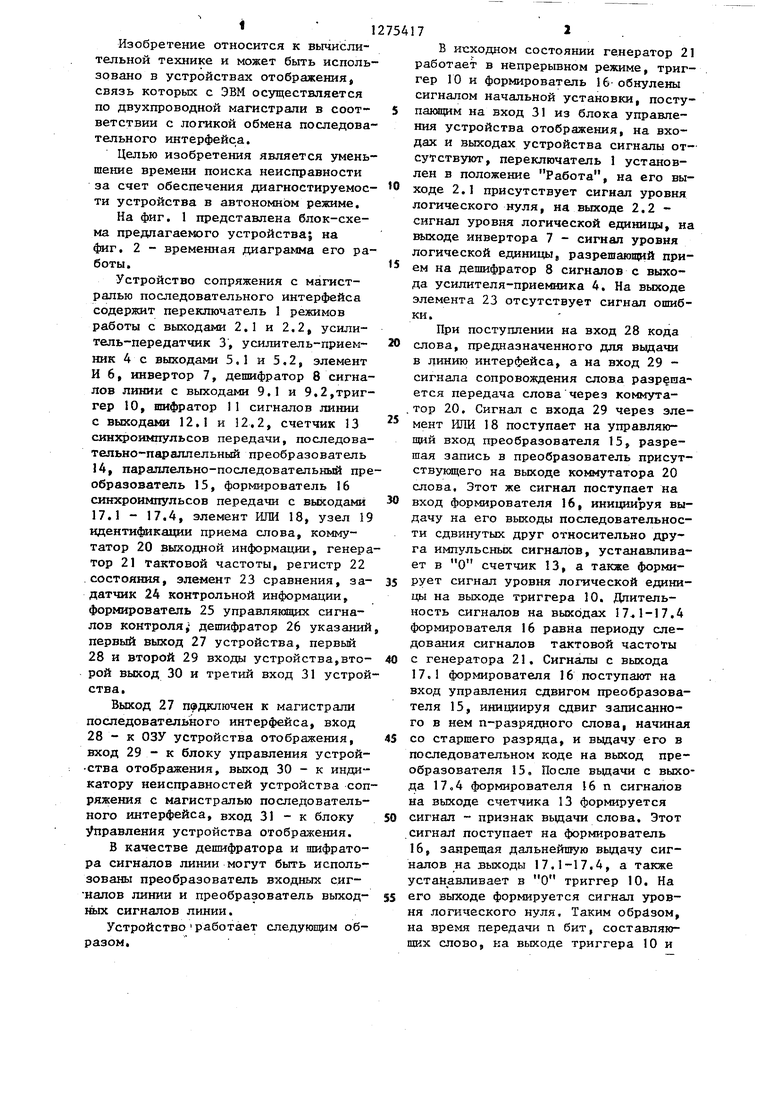

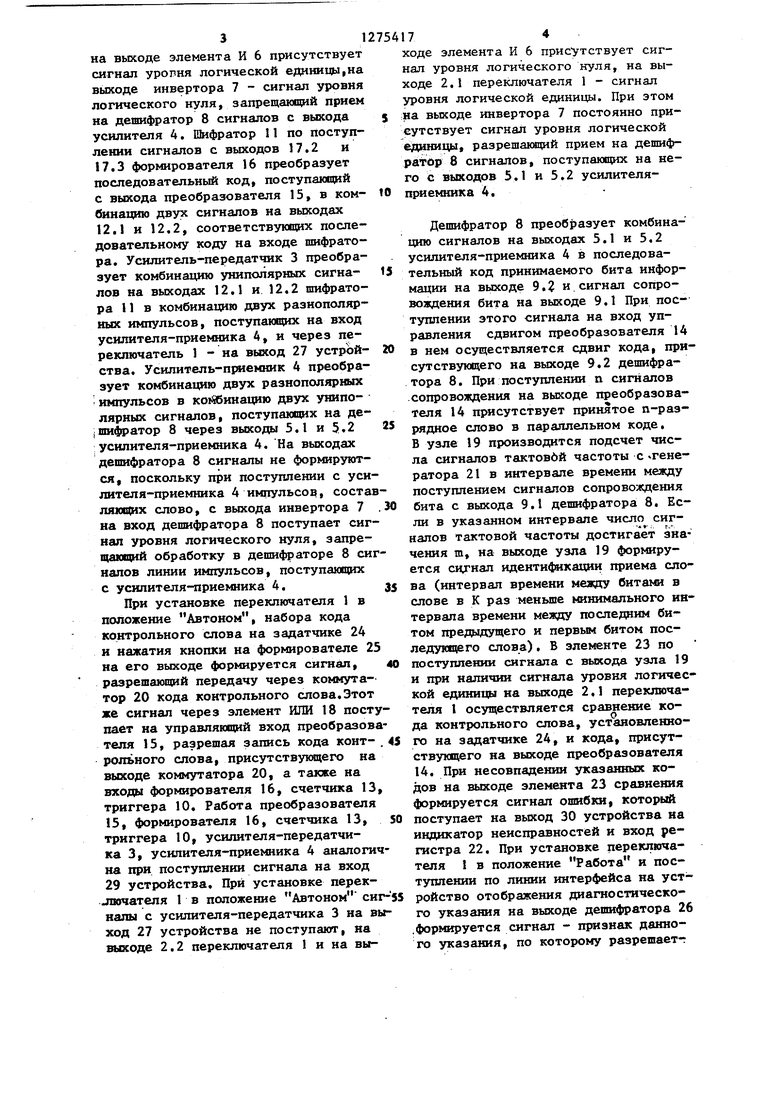

1 Изобретение относится к вычислительной технике и может быть использовано в устройствах отображения, связь которых с ЭВМ осуществляется по двухпроводной магистрали в соответствии с логикой обмена последовательного интерфейса. Целью изобретения является уменьшение времени поиска неисправности за счет обеспечения диагностируемоети устройства в автономном режиме. На фиг. 1 представлена блок-схема предлагаемого устройства; на фиг. 2 - временная диаграмма его работы. Устройство сопряжения с магистралью последовательного интерфейса содержит переключатель 1 режимов работы с выходами 2.1 и 2.2, усилитель-передатчик 3, усилитель-приемник 4 с выходами 5.1 и 5.2, элемент И 6, инвертор 7, дешифратор 8 сигналов линии с выходами 9.1 и 9.2,триггер 10, шифратор 11 сигналов линии с выходами 12.1 и 12.2, счетчик 13 синхроимпульсов передачи, последовательно-параллельный преобразователь 14, параллельно-последовательный пре образователь 15, формирователь 16 синхроимпульсов передачи с выходами 17.1 - 17.4, элемент ИЛИ 18, узел 19 идентификации приема слова, коммутатор 20 выходной информации, генера тор 21 тактовой частоты, регистр 22 .состояния, элемент 23 сравнения, задатчик 24 контрольной информации, формирователь 25 управляющих сигналов контроля,- дешифратор 26 указаний первый выход 27 устройства, первый 28 и второй 29 входы устройства,второй выход 30 и третий вход 31 устрой ства. Выход 27 пФдключен к магистрали последовательного интерфейса, вход 28 - к ОЗУ устройства отображения, вход 29 - к блоку управления устройства отображения, выход 30 - к индикатору неисправностей устройства соп ряжения с магистралью последовательного интерфейса, вход 31 - к блоку Управления устройства отображения. В качестве депшфратора и шифратора сигналов линии могут быть использованы преобразователь входных сигналов линии и преобразователь выходных сигналов линии. Устройствоработает следующим образом. 7 В исходном состоянии генератор 21 работает в непрерывном режиме, триггер ГО и формирователь 16- обнулены сигналом начальной установки, поступакщим на вход 31 из блока управления устройства отображения, на входах и выходах устройства сигналы отсутствуют, переключатель 1 установлен в положение Работа, на его выходе 2.1 присутствует сигнал уровня логического нуля, на выходе 2.2 сигнал уровня логической единицы, на выходе инвертора 7 - сигнал уровня логической единицы, разрешающий прием на дешифратор 8 сигналов с выхода усилителя-приеьшика 4. На выходе элемента 23 отсутствует сигнал ошибки. При поступлении на вход 28 кода слова, предназначенного для вьвдачи в линию интерфейса, а на вход 29 сигнала сопровождения слова разрушается передача слова через коммутатор 20. Сигнал с входа 29 через элемент ИЛИ 18 поступает на управляющий вход преобразователя 15, разрешая запись в преобразователь присутствующего на выходе коммутатора 20 слова. Этот же сигнал поступает на вход формирователя 16, инициируя выдачу на его выходы последовательности сдвинутых друг относительно друга импульсных сигналов, устанавливает в О счетчик 13, а также формирует сигнал уровня логической единицы на выходе триггера 10. Длительность сигналов на выходах 17-. 1-1 7.4 формирователя 16 равна периоду следования сигналов тактовой частоты с генератора 21. Сигналы с выхода 17.1 формирователя 16 поступают на вход управления сдвигом преобразователя 15, инициируя сдвиг записанного в нем п-разрядного слова, начиная со старшего разряда, и вьщачу его в последовательном коде на выход преобразователя 15. После вьщачи с выхода 17 о 4 формирователя 16 п сигналов на выходе счетчика 13 формируется сигнал - признак вьщачи слова. Этот сигнал поступает на формирователь 16, запрещая дальнейшую выдачу сигналов на выходы 17.1-17.4, а также устанавливает в О триггер 10. На его выходе формируется сигнал уровня логического нуля. Таким обрйзом, на время передачи п бит, составляюших слово, ка выходе триггера 10 и

на выходе элемента И 6 присутствует снгнал уровня логической едннии9 1|На выходе инвертора 7 - сигнал уровня логического нуля, запрещающий прием на дешифратор 8 сигналов с выхода усилителя 4. Шифратор 11 по поступлении сигналов с выходов 17.2 и 17.3 формирователя 16 преобразует последовательный код, поступагаций с выхода преобразователя 15, в комбинацию двух сигналов на выходах 12.1 и 12.2, соответствующих последовательному коду на входе шифратора. Усилитель-передатчик 3 преобразует комбинацию униполярных сигналов на выходах 12.1 и 12.2 шифратора I 1 в комбинацию двух разнополярных импульсов, поступающих на вход усилителя-приемника 4 и через переключатель 1 - на выход 27 устройства. Усилитель-пцжемник 4 преобразует комбинацию двух разнополярных импульсов в комбинацию двух униполярных сигналов, поступающих на де{шифратор 8 через выходы 5.1 и 5.2 усилителя-приемника 4. На выходах дешифратора 8 сигналы не формируются, поскольку при поступлении с усилителя-приемника 4 импульсоэ, составляюо их слово, с выхода инвертора 7 на вход дешифратора 8 поступает сигнал уровня логического нуля, запрещающий обработку в дешифраторе 8 сигналов линии импульсов, поступающих с усилителя-приемника 4.

При установке переключателя 1 в положение Автоном, набора кода контрольного слова на задатчике 24 и нажатия кнопки на формирователе 25 на его выходе формируется сигнал, разрешающий передачу через коммутатор 20 кода контрольного слова.Этот же сигнал через элемент ШШ 18 поступает на управляющий вход преобразователя 15, разрешая запись кода контрольного слова, присутствукяцего на выходе коммутатора 20, а также на входы формирователя 16, счетчика 13, триггера 10. Работа преобразователя 15, формирователя 16, счетчика 13, триггера 10, усилителя-передатчика 3, усилителя-приемника 4 аналогична при поступлении сигнала на вход 29 устройства. При установке переключателя 1 в положение Автоном сиг налы с усилителя-передатчика 3 на выход 27 устройства не поступают, на выходе 2.2 переключателя 1 и на выходе элемента И 6 присутствует сигнал уровня логического куля, на выходе 2.1 переключателя 1 - сигнал уровня логической единицы. При этом на выходе инвертора 7 постоянно присутствует сигнал уровня логической единицы, разрешакжщй прием на дешифратйр 8 сигналов, поступающих на него с выходов 5.1 и 5.2 усилителяприемника 4.

Дешифратор 8 преобразует комбинацию сигналов на выходах 5.1 и 5.2 усилителя-приемника 4 в последовательный код принимаемого бита информации на выходе 9. и сигнал сопровождения бита на выходе 9.1 При поступлении этого сигнала на вход управления сдвигом преобразователя 14 в нем осуществляется сдвиг кода, присутствующего на выходе 9.2 дешифратора 8. При поступлении п сигналов сопровождения на выходе преобразоваteля 14 присутствует принятое п-разрядное слово в параллельном коде. В узле 19 производится подсчет числа сигналов тактовбй частоты с «генератора 21 в интервале времени между поступлением сигналов сопровождения бита с выхода 9.1 дешифратора 8. Если в указанном интервале число сигналов тактовой частоты достигает значения т, на выходе узла 19 формируется снгнал идентификации приема слова (интервал времени между битами в слове в К раз меньше минимального интервала времени между последним битом предыдущего и первым битом последующего слова). В элементе 23 по поступлении сигнала с выхода узла 19 и при наличии сигнала уровня логической единицы на выходе 2.1 переключателя 1 осуществляется сравнение кода контрольного слова, установленного на задатчике 24, и кода, присутствухщего на выходе преобразователя 14. При несовпадении указанных кодов на выходе элемента 23 сравнения формируется сигнал ошибки, который поступает на выход 30 устройства на индикатор неисправностей и вход регистра 22. При установке переключателя 1 в положение Работа и поступлении по линии интерфейса на устройство отображения диагностического указания на выходе дешифратора 26 .формируется сигнал - признак данного указания, по которому разрешает-:

ся передача на выход коммутатора содержимого регистра 22,

Формула изобретения

Устройство сопряжения с магистралью последовательногЙ интерфейса, содержащее генератор тактовой частоты, последовательно соединенные усилитель-приемник, дешифратор сигналов линии, узел идентификации приема слова, дешифратор указаний, элемент ИЛИ, счетчик синхроимпульсов передачи, формирователь синхроимпульсов передачи, параллельно-последовательный преобразователь, шифратор сигналов линии и усилитель-передатчик, выход которого подключен к входу усилителя-приемника, а также последовательно соединенные регистр состояния и коммутатор выходной информации, первый управляющий вход которого подключен к выходу дешифратора указаний, второй информащонный вход - к первому входу устройства, а информационный выход - к информационному входу параллельнопоследовательного преобразователя, второй управляющий вход которого подключен к выходу элемента ЕПИ,связанного также с вторым входом формирователя синхроимпульсов передачи, второй и третий выходы которого соединены с соответствующими входами шифратора сигналов линии, выход гёнератора тактовой частоты связан с третьим входом формирователя синхроимпульсов передачи и с вторым входом узла идентификации приема слова, второй вход устройства подключен к вторым входам коммутатора выходной информации и элемента ИЛИ, а третий еход устройства - к входу начальной установки формирователя синхроимпульсов передачи, отличающееic я тем, что, с целью уменьшения времени поиска неисправности за счет обеспечения диагностируемо.сти устройства в автономном режиме, в него вве-; дены последовательно-параллельный преобразователь, переключатель режимов работы, задатчик контрольной информации, формирователь управляняцих сигналов контроля, элемент сравнения, триггер, элемент И и инвертор, причем первый и второй выходы дешифратора сигналов линии подключены соответственно к первому и второму входам последовательно-параллельного преобразователя, выход которого соеданен с информационным входом дешифратора указаний и с первым информационным входом элемента сравнения первый и второй управляющие входы которого подключены соответственно к выходу узла идентификации приема слова и к первому выходу переключателя режимов работы, а выход - к входу регистра состо5шия и к второму клходу устройства, выход задатчика контрольной .информации связан с третьим информационным входом коммутатора выходной информации и с вторым информационным входом элемента сравнения, выход формирователя управягацих сигналов контроля подключен к третьему управляющему входу коммутатора входной информации и к третьему входу элемента ИЛИ, соединенного своим ВЫХОДСИ4 с единичным входом триггера, нулевой вход которого подсоединен к выходу счетчика синхроимпульсов передачи, вход начальной установки - к третьему входу устройства, а единичный выход - к первому входу элемента И, второй вход которого связан с вторым выходом переключателя работы, а выход через HHBepTojp - с управляющим входом дешифратора сигналов линни, первый вход переключателя режимов работы является первым выходом устройства, подключенным к магистрали интерфейса, а второй вход переключателя реимов работы соединен с выходом усиителя-передатчика.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения ЭВМ с абонентом по последовательному каналу связи | 1987 |

|

SU1442997A1 |

| КОНТРОЛЛЕР | 1991 |

|

RU2012043C1 |

| Устройство для формирования тестовой последовательности | 1984 |

|

SU1218389A1 |

| Многоканальное устройство для регистрации информации | 1984 |

|

SU1236452A1 |

| СИСТЕМА ПЕРЕДАЧИ ИНФОРМАЦИИ | 1991 |

|

RU2043659C1 |

| Устройство для сопряжения электронных вычислительных машин | 1984 |

|

SU1257653A2 |

| Устройство автоматизированной подготовки программ для станков с ЧПУ | 1986 |

|

SU1354160A1 |

| Многоканальная система для контроля и диагностики цифровых блоков | 1984 |

|

SU1269137A1 |

| Устройство для ввода информации | 1985 |

|

SU1312557A1 |

| Устройство для сопряжения ЭВМ с абонентом | 1986 |

|

SU1334154A1 |

Изобретение относится к области вычислительной техники и может быть использовано для подключения к ЭВМ внешних устройств в соответст- ВИИ с логикой обмена последовательного интерфейса. Цель изобретения уменьшение времени поиска неисправности за счет обеспечения диагностируемости устройства в автономном режиме. Устройство сопряжения с магистралью последовательного интерфейса содержит генератор тактовой частоты, усилитель-приемник, дешифратор сигналов линии, узел идентификации приема слова, дешифратор указаний, элемент ИЛИ, счетчик синхроимпульсов передачи, формирователь синхроимпульсов передачи, паравшельно-последовательный преобразователь, шифратор сигналов линии, регистр состояния и коммутатор выходной инi формации. Для обеспечения диагности(Л руемости в него введены последовательно-параллельный преобразователь, переключатель режимов работы, задатчик контрольной информации, формирователь управлякхцих сигналов контроля, элемент сравнения, триггер, го элемент И и инвертор. 2 ил. 8 СД 4

Авторы

Даты

1986-12-07—Публикация

1983-08-26—Подача