Изобретение относится к аналоговой технике и может быть использовано в системах автоматического управления, например в высокоточных следящих электроприводах.

Целью изобретения является повышение точности и упрощение устройства.

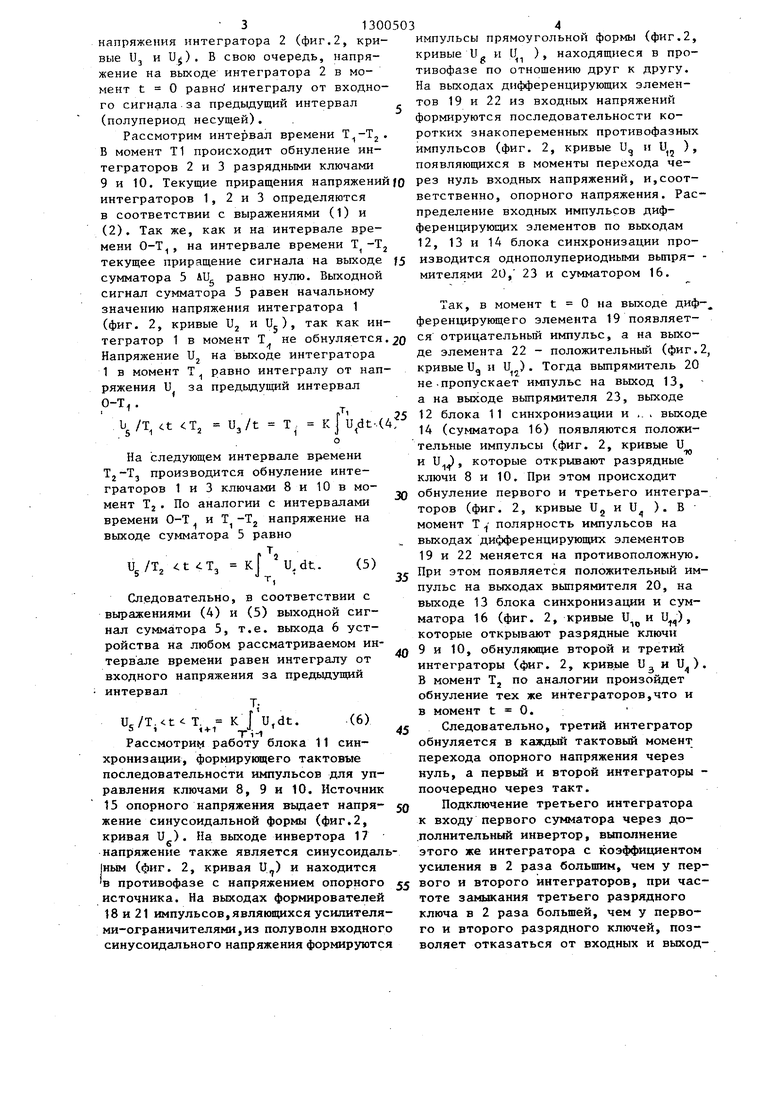

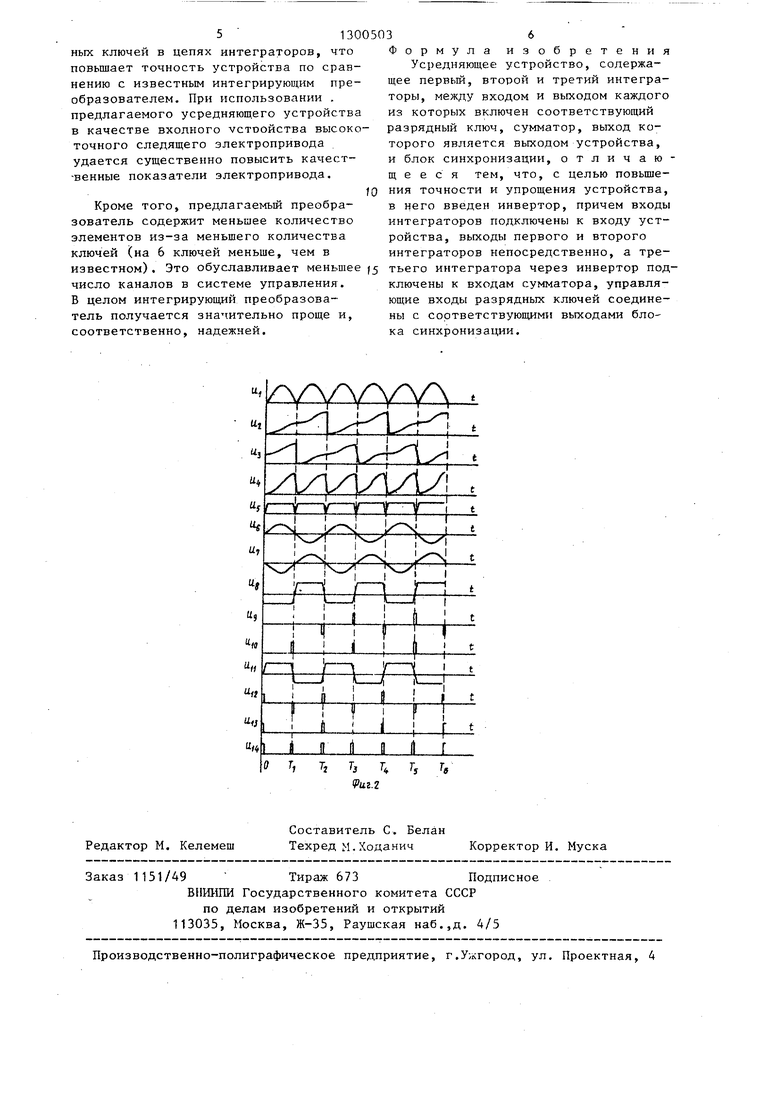

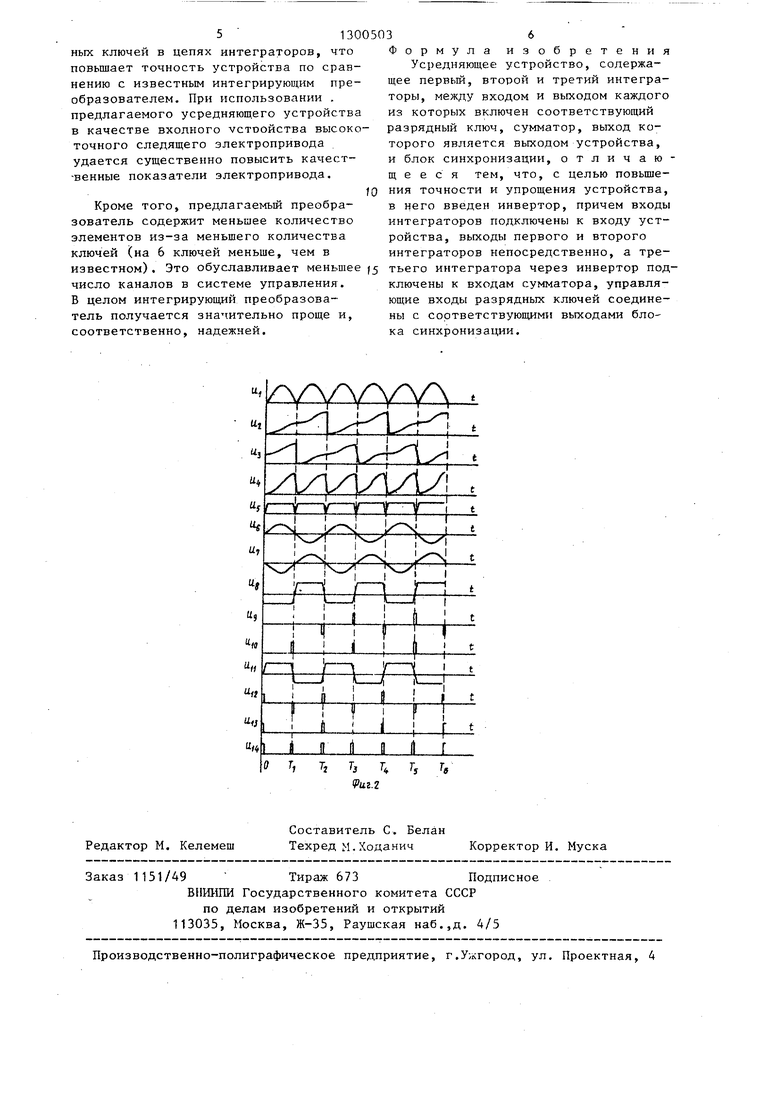

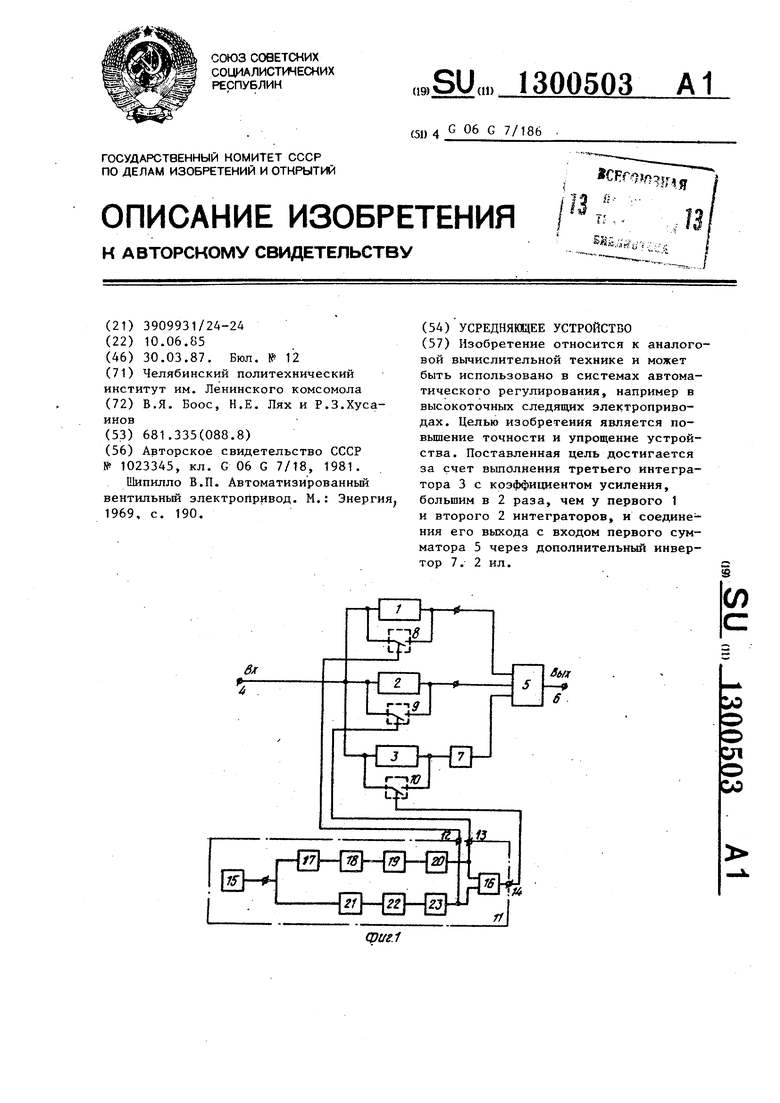

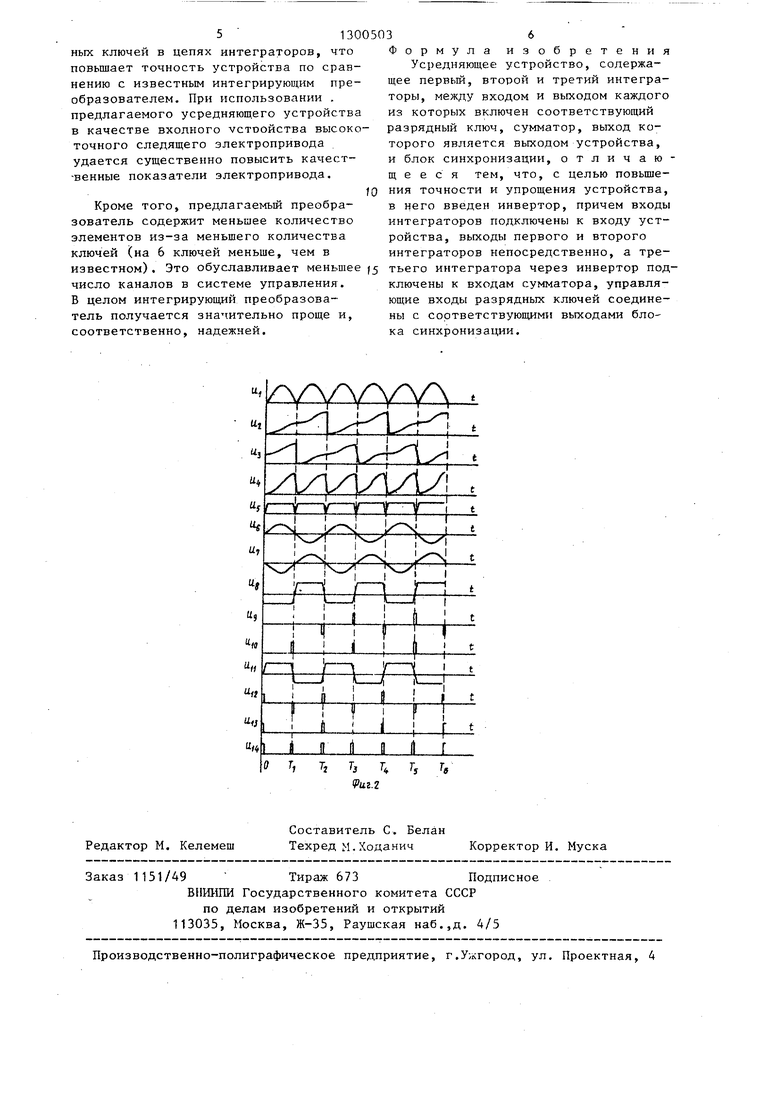

На фиг. 1 приведена схема предложенного устройства; на фиг. 2 - диа- граммы, поясняющие его работу.

Усредняющее устройство (фиг. 1) содержит первьш 1, второй 2, третий 3 интеграторы, входы которых соединены с входом 4 устройства, сумматор 5, первый и.второй входы которого соединены с выходами первого и второго интеграторов 1 и 2, а выход является выходом 6 устройства, инвертор

7,вход которого соединен с выходом интегратора 3, а выход - с третьим входом сумматора 5, разрядные ключи

8,9 и 10, включенные между входами и выходами интеграторов 1, 2 и 3 соответственно, блок 11 синхрониза- ции, вьгходы 12-14 которого соединены

с управляющими входами ключей 8, 9 и 10 соответственно. Блок 11 синхронизации содержит источник 15 опорного напряжения, частота которого син- хронизована с частотой входного сигнала, сумматор 16, выход которого является выходом 14, цепь блока синхронизации из последовательно соединенньк второго инвертора 17, вход ко- 35 гратора 3 взят в 2 раза большим коэ- торого соединен с выходом источника фициентов усиления интеграторов 1 и 15 опорного напряжения, формирователя 2, Напряжение Ug на выходе сумматора 18 импульсов, дифференцирующего эле- 5 (фиг. 2, кривая U) равно мента 19, однополупериодного выпрямителя 20, выход которого соединен с 0 одним из входов, сумматора 16 и вых.ои.. и

+ з - и, ,

(3)

дом 13 блока синхронизации, цепь из последовательно соединенных формирователя 21 импульсов, вход которого

соединен с выходом источника 15 опор- 45 ния 4.U g на выходе сумматора 5 в со- ного напряжения, дифференцирующего ответствии с выражениями (1), (2) и элемента 22, однополупериодного вып- (3) равно нулю. Следовательно, на ин- рямителя 23, соединенного с другим тервале времени 0-Т напряжение на входом сумматора 16 и выходом 12 бло- выходе сумматора 5, т.е. на выходе ка синхронизации.50 Устройства 6, не изменяется и определяется начальными значениями напряНа фиг. 1 показаны диаграммы на- жений интеграторов 1, 2 и 3. Началь- пряжёния в разных точках устройства ные значения напряжений выходов инте- согласно г. 1: U, на входе 4 уст- граторов 1,3 в момент t О равны ну- ройства; Uj , Uj , U. - на выходах инте-55 лю, так как разрядные ключи 8 и 10 в граторов t, 2 и 3 соответственно; U,- этот момент обнуляют выходы указанных на выходе сумматора 5; U, - на вьссоде интеграторов. Следовательно, выходной источника 15 опорного напряжения; сигнал сумма1 ора 5 на интервале вреи,, - на выходе инвертора 17; Uj - на

выходе формирователя 18 импульсов; Ug - на выходе дифференцирующего элемента 19; и - на выходе од- | нополупериодного выпрямителя 20; и, - на выходе Формирователя 21 импульсов; U, - на выходе дифференцирующего элемента 22; U - на выходе однополупе)иодного выпрямителя 23; и - на выходе 14 сумматора 16.

Работу устройства рассмотрим на примере, когда на вход 4 устройства подается сигнал (фиг. 2, кривая Ц ), представляющий демодулированное напряжение с выхода системы переменного тока с амплитудной модуляцией. Вначале рассмотрим участок времени 0-Т полупериода несущей. Текущее приращение выходных; напряжений интеграторов 1 и 2 HUj ,j (фиг. 2, кривые U и Uj) для произвольного момента времени t равно

ли

2,3

,dt, (1)

где К - коэффициент усиления интеграторов 1 и 2. Текущее приращение выходного напряжения интегратора 3 (фиг. 2, кривая и ) определяется выражением

и, dt, (2)

гч аи .2к

так как коэффициент усиления интеа 3 взят в 2 раза большим коэ тов усиления интеграторов 1 и ряжение Ug на выходе сумматор . 2, кривая U) равно

и.. и

+ з - и, ,

(3)

так как напряжение интегратора 3 подается на вход сумматора 5 через инвертор 7. Тогда приращение напряжемени 0-Т равен начальному значению

напряжения интегратора 2 (фиг.2, кривые Uj и Uj). В свою очередь, напряжение на выходе интегратора 2 в момент t О равно интегралу от входного сигнала за предыдущий интервал (полупериод несущей).

Рассмотрим интервал времени . В момент Т1 происходит обнуление интеграторов 2 и 3 разрядными ключами

9 и 10. Текущие приращения напряжений/о нуль входных напряжений, и,соот- интеграторов 1, 2 и 3 определяются ветственно, опорного напряжения. Рас- в соответствии с выражениями (1) и пределение входных импульсов диф- (2). Так же, как и на интервале вре- ференцируюдих элементов по выходам мени 0-Т,, на интервале времени 12, 13 и 14 блока синхронизации производится однополупериодными выпря- - мителями 20, 23 и сумматором 16.

J5

текущее приращение сигнала на выходе сумматора 5 AU равно нулю. Выходной сигнал сумматора 5 равен начальному значению напряжения интегратора 1 (фиг. 2, кривые Uj и Uj), так как интегратор 1 в момент Т не обнуляется. 20 отрицательный импульс, а на выхо- Напряжение U на выходе интегратора де элемента 22 - положительный (фиг.2,

кривые Ug и и ). Тогда вьтрямитель 20 не-пропускает импульс на выход 13,

Так, в момент t О на выходе диф- ференцирующего элемента 19 появляет1 в момент Т

на выходе интегратора равно интегралу от напНа следующем интервале вр1емени

Tj-Tj производится обнуление интеграторов 1 и 3 ключами 8 и 10 в момент Tj. По аналогии с интервалами времени 0-Т . и Т -Т напряжение на выходе сумматора 5 равно

Т.

t iT

.-I.

U,dt.

(5)

ряжения и за предыдущий интервал

0-Т..а на выходе вьтрямителя 23, выходе

. 25 12 блока 11 синхронизации и .. . выходе Ug/T t Tj - Uj/t - Т. - Kj U dt-44, (сумматора 16) появляются положительные импульсы (фиг. 2, кривые U и , которые открьшают разрядные ключи 8 и 10. При этом происходит

30 обнуление первого и третьего интеграторов (фиг. 2, кривые и2 и и ). В момент Т Y полярность импульсов на

, выходах дифференцирующих элементов 19 и 22 меняется на противоположную.

,г При этом появляется положительный импульс на выходах выпрямителя 20, на выходе 13 блока синхронизации и сумматора 16 (фиг. 2, кривые V к U), которые открывают разрядные ключи

40 9 и 10, обнуляющие второй и третий интеграторы (фиг. 2, кривые U и U). В момент Tj по аналогии произойдет обнуление тех же интеграторов,что и в момент t 0.

45 Следовательно, третий интегратор обнуляется в каждый тактовый момент перехода опорного напряжения через нуль, а первый и второй интеграторы - поочередно через такт.

50 Подключение третьего интегратора к входу первого сумматора через до- .полнительный инвертор, выполнение этого же интегратора с коэффициентом усиления в 2 раза болыиим, чем у перСледовательно, в соответствии с выражениями (4) и (5) выходной сигнал сумматора 5, т.е. выхода 6 устройства на любом рассматриваемом интервале времени равен интегралу от входного напряжения за предьщущий интервал

Us/T. к I U,dt. .(6)

т

Paccмoтpи работу блока 11 синхронизации, формирукяцего тактовые последовательности импульсов для управления ключами 8, 9 и 10. Источник 15 опорного напряжения выдает напряжение синусоидальной формы (фиг.2, кривая и). На выходе инвертора 17

S

напряжение также является синусоидаль- ным (фиг. 2, кривая Ц) и находится в противофазе с напряжением опорного 55вого и второго интеграторов, при час- источника. На выходах формирователейтоте замыкания третьего разрядного 18 и 21 импульсов,являющихся усилителя-ключа в 2 раза большей, чем у перво- ми-ограничителями,из полуволн входногого и второго разрядного ключей, поз- синусоидального напряжения формируютсяволяет отказаться от входных и выход503

импульсы прямоугольной формы (фиг.2, кривые и,, и и, ), находящиеся в проо 11

тивофазе по отношению друг к другу. На выходах дифференцирующих элементов 19 и 22 из входных напряжений формируются последовательности коротких знакопеременных противофазных импульсов (фиг. 2, кривые 1) и U ), появляющихся в моменты перехода че-

/о

J5

20

отрицательный импульс, а на выхо- де элемента 22 - положительный (фиг.2,

Так, в момент t О на выходе диф- ференцирующего элемента 19 появляет(5)

ных ключей в цепях интеграторов, что повьшает точность устройства по сравнению с известным интегрирующим преобразователем. При использовании . предлагаемого усредняюшего устройства в качестве входного устройства высокоточного следящего электропривода удается существенно повысить качест- -венные показатели электропривода.

Кроме того, предлагаемый преобразователь содержит меньшее количество элементов из-за меньшего количества ключей (на 6 ключей меньше, чем в известном). Это обуславливает меньшее число каналов в системе управления. В целом интeгpиpyюш й преобразователь получается значительно проще и, соответственно, надежней.

h/ww

Формула изобретения

Усредняющее устройство, содержащее первый, второй и третий интеграторы, между входом и выходом каждого из которых включен соответствующий разрядный ключ, сумматор, выход которого является выходом устройства, и блок синхронизации, отличающееся тем, что, с целью повышения точности и упрощения устройства, в него введен инвертор, причем входы интеграторов подключены к входу устройства, выходы первого и второго интеграторов непосредственно, а третьего интегратора через инвертор подключены к входам сумматора, управляющие входы разрядных ключей соединены с соответствующими выходами блока синхронизации.

lii

X1

i,

.

7

4t

Ц,

«

« /

о г,

г 3 Ч Is If Риг.2

Редактор М. Келемещ

Составитель С. Белан Техред м.Ходанич

Заказ 1151/49 Тираж 673Подписное

ВПИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб.,д. 4/5

Производственно-полиграфическое предприятие, г.Ужгород, ул. Проектная, 4

Корректор И. Муска

| название | год | авторы | номер документа |

|---|---|---|---|

| Мультиплицированная измерительная система | 1978 |

|

SU972654A1 |

| Генератор напряжения ступенчатой формы | 1983 |

|

SU1113814A2 |

| Способ измерения рассогласования между углами поворота,один из которых задан кодом | 1985 |

|

SU1285595A1 |

| Устройство для некогерентного приема сигналов с относительной фазовой манипуляцией | 1985 |

|

SU1396291A1 |

| Способ измерения среднего значения напряжения произвольной формы и устройство для его осуществления | 1983 |

|

SU1150561A1 |

| Устройство для измерения коэффициента нелинейности пилообразного напряжения | 1981 |

|

SU978077A1 |

| Преобразователь угла поворота вала в код | 1989 |

|

SU1633492A1 |

| Устройство для моделирования импульсного частотно-фазового дискриминатора | 1986 |

|

SU1354218A1 |

| Измеритель сдвига фаз | 1985 |

|

SU1298684A2 |

| Измеритель коэффициента нелинейности пилообразного напряжения | 1980 |

|

SU894607A1 |

Изобретение относится к аналоговой вычислительной технике и может быть использовано в системах автоматического регулирования, например в высокоточных следящих электроприводах. Целью изобретения является повышение точности и упрощение устройства. Поставленная цель достигается за счет вьшОлнения третьего интегратора 3 с коэффициентом усиления, большим в 2 раза, чем у первого 1 и второго 2 интеграторов, и соединения его выхода с входом первого сумматора 5 через дополнительньлй инвертор 7. 2 ил. i сл :л: о о :л и

| Усредняющее устройство | 1981 |

|

SU1023345A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Шипилло В.П | |||

| Автоматизированньш вентильный электропривод | |||

| М.: Энергия, 1969, с | |||

| Ускоритель для воздушных тормозов при экстренном торможении | 1921 |

|

SU190A1 |

| Лг | |||

Авторы

Даты

1987-03-30—Публикация

1985-06-10—Подача