(541 МУЛЬТИПЛИЦИРОВАННАЯ ИЗМЕРИТЕЛЬНАЯ СИСТЕМА

| название | год | авторы | номер документа |

|---|---|---|---|

| Аналого-цифровой преобразователь | 1984 |

|

SU1368990A1 |

| Адаптивный аналого-цифровой преобразователь | 1984 |

|

SU1226666A1 |

| Электромагнитный расходомер | 1986 |

|

SU1509600A1 |

| Преобразователь сигнала тензомоста в интервал времени | 1987 |

|

SU1580260A1 |

| Электромагнитный расходомер | 1987 |

|

SU1578481A1 |

| Аналого-цифровой преобразователь интегральных характеристик напряжений | 1988 |

|

SU1615888A1 |

| Функциональное интегрирующее устройство | 1977 |

|

SU732903A1 |

| Устройство управления | 1984 |

|

SU1229721A1 |

| Функциональный аналого-цифровой преобразователь | 1986 |

|

SU1310855A1 |

| Формирователь сигналов с заданным законом изменения фазы | 1986 |

|

SU1385239A1 |

Изобретение относится к измерительной технике и может быть использовано для одновременного преобразования в код непрерывных сигналов,поступающих от совокупности датчиков.

Известна мультиплицированная измерительная система, содержащая в каждом канале компаратор, интегратор, сумматор, ключ регистр, блок управления каналом, выход которого через цифроаналоговый преобразователь соединен с входом сумматора и ключом, а вход - с выходом генератора импульсов 11

Недостатком устройства является низкое быстродействие.

Известна мультиплицированная измерительная система, содержащая компараторы, выходы которых через блок управления соединены со счетчиком, выходы которого через цифроаналоговый преобразователь соединены с входами компараторов 2j.

Недостатком устройства является низкое быстродействие.

Целью изобретения является повышение быстродействия.

Указанная цель достигается тем, что в мультиплицированную измерительную систему, содержащую дифроаналоговый преобразователь и п каналов преобразования, каждый из которых выпол-, нен на компараторе, первый вход котог рого. соединен с соответствующей входной шиной, введены инвертор, элемент ИЛИ, допЪлнительный компаратор, дополнительный интегратор, дополнительный регистр сдвига, генератор монотонно

.Q изменяющегося напряжения, а в каждый канал введены триггер, интегратор, переключатель, регистр сдвига, при этом выход генератора монотонно изменяющегося напряжения соединен с входом инвертора, первым входом до15полнительного интегратора и первыми входами переключателей, вторые входы которых соединены с выходом инвертора, причем первые входы ин::еграторов соединены с первым входом генератора

20 монотонно изменяющегося напряжения, вторым входом дополнительного интегратора и R-ВХОДОМ дополнительного регистра сдвига, С-вход которого соединен с выходом элемента ИЛИ и

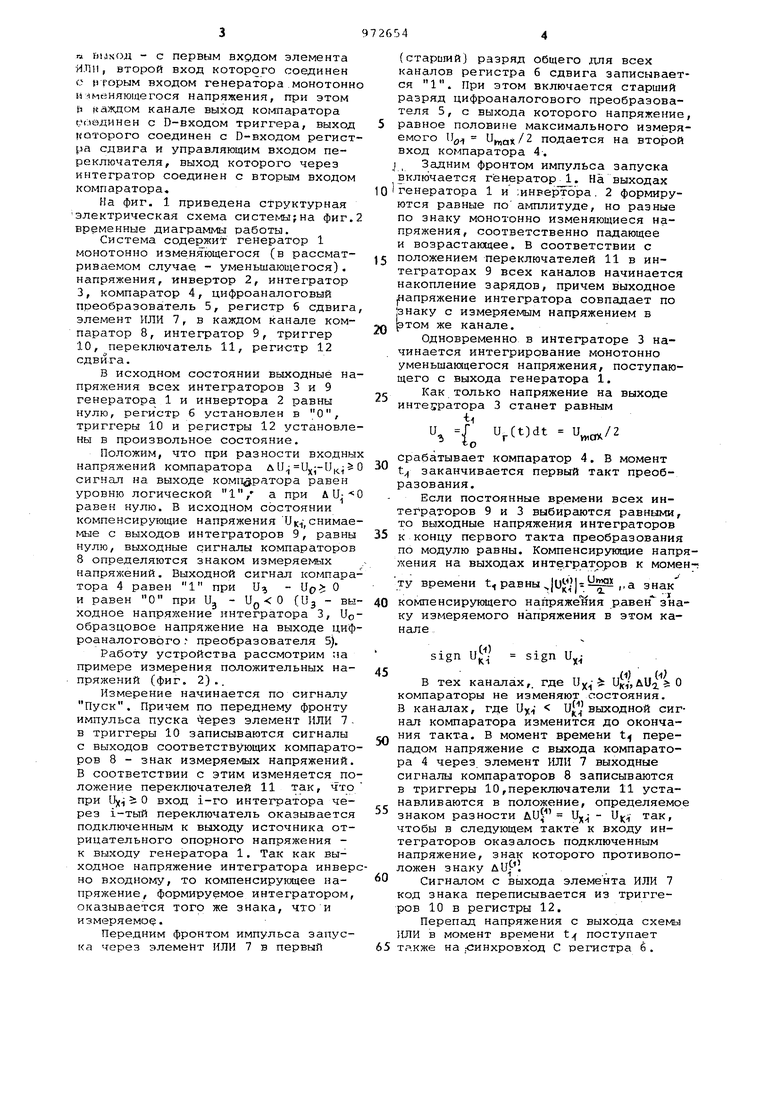

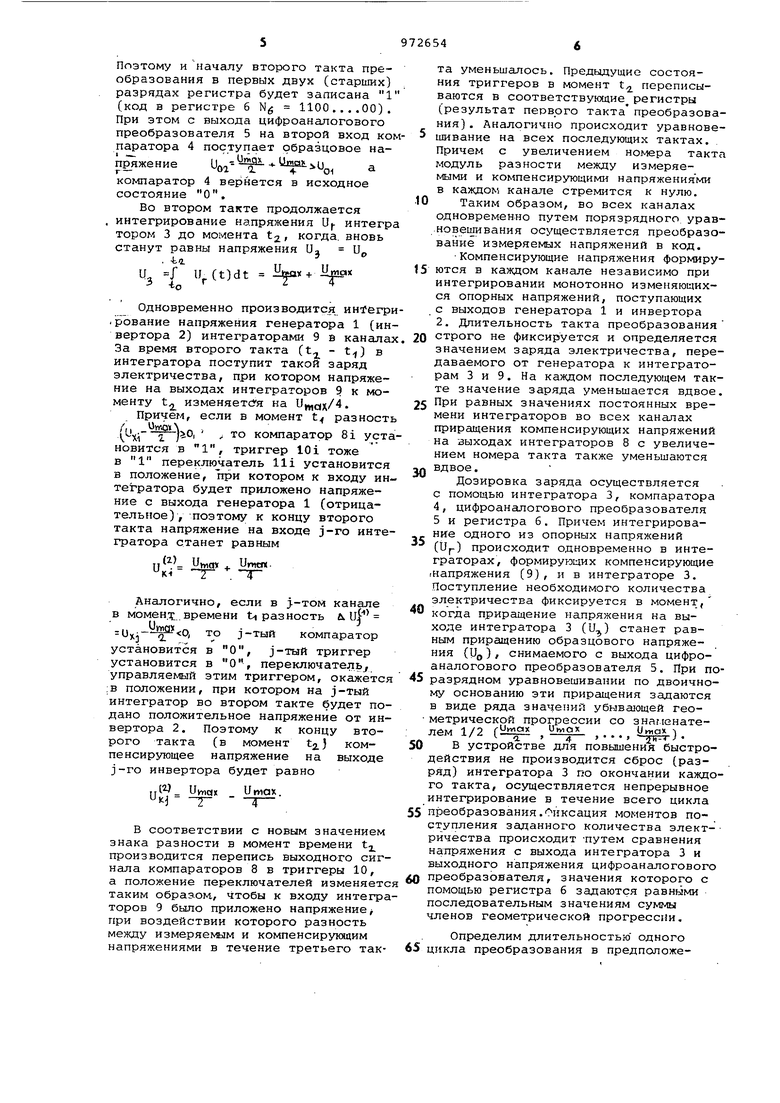

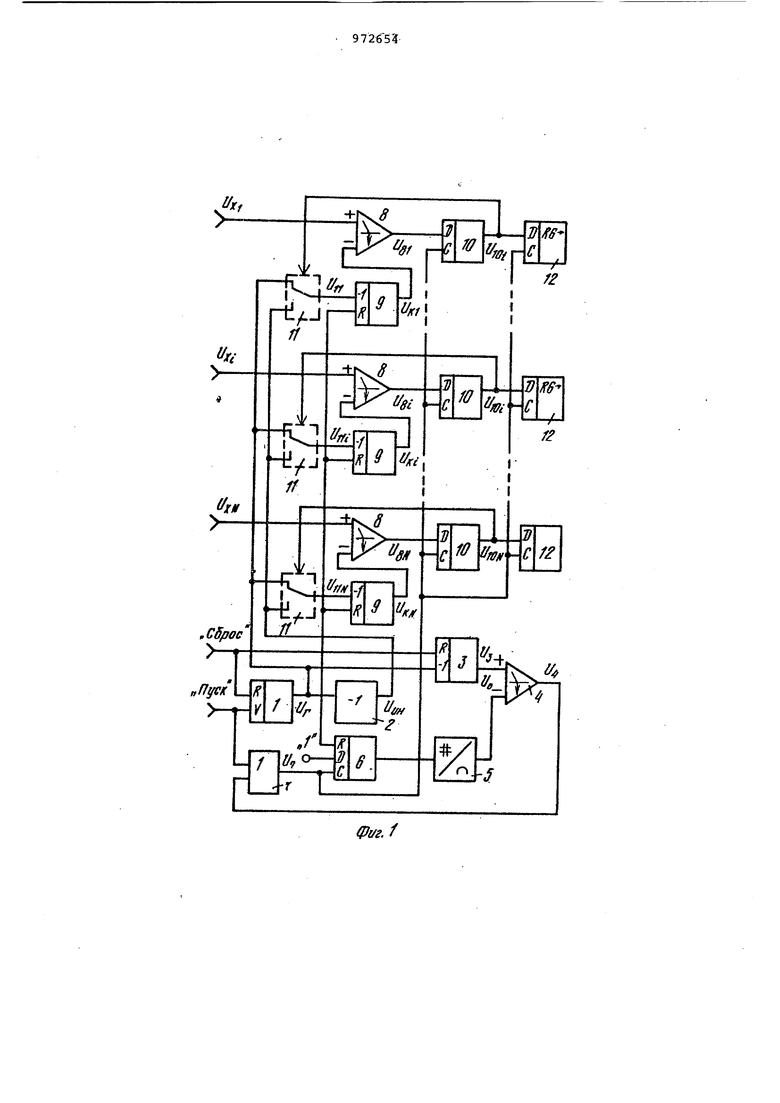

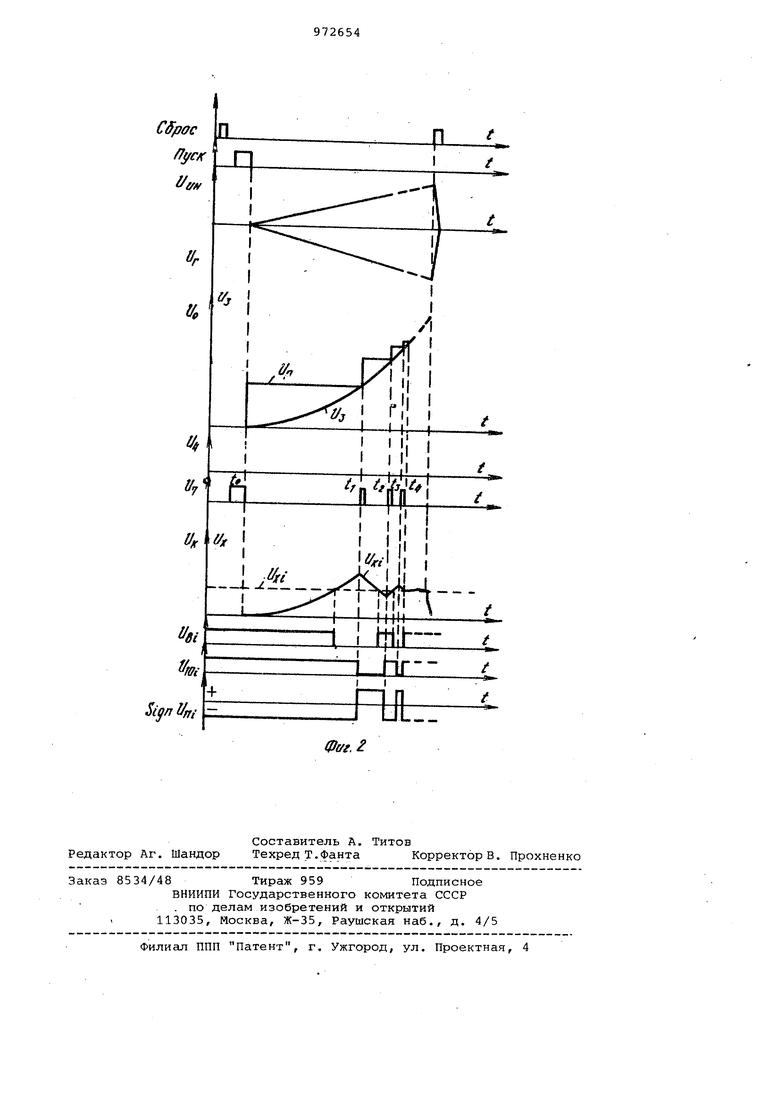

25 с-входами триггеров и регистров сдвига, а выход через цифро-аналоговый преобразователь соединен с первым входом дополнительного компаратора, второй вход которого соединен с выходом дополнительного иг1тегратора, п. hijsoji - с первым вхрдом элемента Я.ПИ, второй вход которого соединен с tiторым входом генератора монотонно н иенягощегося напряжения, при этом {5 каждом канале выход компаратора 1:(:1вдинен с D-входом триггера, выход которого соединен с D-входом регистра сдвига и управляющим входом переключателя, выход которого через интегратор соединен с вторым входом компаратора. На фиг. 1 приведена структурная электрическая схема системы;на фиг. временные диаграммы работы. Система содержит генератор 1 монотонно изменя ющегося (в рассматриваемом случае - уменьшающегося). напряжения, инвертор 2, интегратор 3, компаратор 4, цифроаналоговый преобразователь 5, регистр 6 сдвига элемент ИЛИ 7, в каждом канале компаратор 8, интегратор 9, триггер 10, переключатель 11, регистр 12 сдвига. В исходном состоянии выходные на пряжения всех интеграторов 3 и 9 генератора 1 и инвертора 2 равны нулю, регистр б установлен в О, триггеры 10 и регистры 12 установле ны в произвольное состояние. Положим, что при разности входны напряжений компаратора д IJ сигнал на выходе компаратора равен уровню логической 1, а при AU равен нулю. В исходном состоянии компенсирующие напряжения И снимае мые с выходов интеграторов 9, равны нулю, выходные сигналы компараторов 8 определяются знаком измеряемых напряжений. Выходной сигнал компара тора 4 равен 1 при - Up О и равен О при Ug - U О (Uj - вы ходное напряжение интегратора 3, Uo образцовое напряжение на выходе циф роаналогового . преобразователя 5). Работу устройства рассмотрим tia примере измерения положительных напряжений (фиг. 2).. Измерение начинается по сигналу Пуск. Причем по переднему фронту импульса пуска ерез элемент ИЛИ 7 в триггеры 10 записываются сигналы с выходов соответствующих компарато ров 8 - знак измеряемых напряжений. В соответствии с этим изменяется по ложение переключателей 11 так, что при Uyi i О вход i-ro интегратора через i-тый переключатель оказывается подключенным к выходу источника отрицательного опорного напряжения к выходу генератора 1. Так как выходное напряжение интегратора инвер но входного, то компенсирукяцее напряжение, формируемое интегратором, оказывается того же знака, что и измеряемо. Передним фронтом импульса запуска через элемент ИЛИ 7 в первый (старишй) разряд общего для всех каналов регистра б сдвига записывается 1. При этом включается старший разряд дифроаналогового преобразователя 5, с выхода которого напряжение, равное половине максимального измеряемого П подается на второй вход компаратора 4-. , Задним фронтом импульса запуска включается генератор 1. На выходах генератора 1 и ;инвертЬра. 2 формируются равные по амплитуде, но разные по знаку монотонно изменяющиеся напряжения, соответственно падающее и возрастающее. В соответствии с положением переключателей 11 в интеграторах 9 всех каналов начинается накопление зарядов, причем выходное |Напряжение интегратора совпадает по знаку с измеряемым напряжением в ртом же канапе. Одновременно в интеграторе 3 начинается интегрирование монотонно уменьшакяцегося напряжения, поступающего с выхода генератора 1. Как только напряжение на выходе интез;ратора 3 станет равным и { )dt срабатывает компаратор 4. В момент t заканчивается первый такт преобразования. Если постоянные времени всех интеграторов 9 и 3 выбираются равными, то выходные напряжения интеграторов к концу первого такта преобразования по модулю равны. Компенсирующие напряжения на выходах инте.гратрров к моменту времени Ц равны , ,,а знак компенсирунядего напряжения равен знаку измеряемого напряжения в этом канале . sign sign тех каналах,, где Uxi ,uU-2.0 компараторы не изменяют состояния. В каналах, где ,выходной сигнал компаратора изменится до окончания такта. В момент времени t перепадом напряжение с выхода компаратора 4 через элемент ИЛИ 7 выходные сигналы компараторов 8 записываются в триггеры 10,переключатели 11 устанавливаются в положение, определяемое знаком разности - U, так, чтобы в следующем такте к входу интеграторов оказалось подключенным напряжение, знак которого противоположен знаку ли|. Сигналом с выхода элемента ИЛИ 7 код знака переписывается из триггеров 10 в регистры 12. Перепад напряжения с выхода схемы ИЛИ в момент времени t поступает также на ;инхровход С регистра 6 . Поэтому и началу второго такта преобразования в первых двух (старших) разрядах регистра будет записана 1 (код в регистре б Ng 1100....00). При этом с выхода цифроаналогового преобразователя 5 на второй вход ко паратора 4 поступает образцовое напряжение Uoi b ajLiUo а компаратор 4 вернется в исходное состояние О, Во втором такте продолжается интегрирование напряжения Uf интегр тором 3 до момента t,, когда, вновь станут равны напряжения Uj Up ии. ilteax + iiwa и. / Ur(t)dt 1 4 Одновременно производится /рование напряжения генератора 1 (ин вертора 2) интеграторами 9 в канала За время второго такта (t - t) в интегратора поступит такой заряд электричества, при котором напряжение на выходах интеграторов 9 к моменту . изменяетсУя на . Причем, если в момент t разност )0| то компаратор 81 уст новится в 1, триггер 101 тоже в 1 переключатель 111 установится в положение, при котором к входу ин тегратора будет приложено напряжение с выхода генератора 1 (отрицательное) , поэтому к концу второго такта напряжение на входе j-ro инте гратора станет равным uf/ fe . -« Аналогично, если в -том канале в момент времени tn разность и. ul ,,, то j-тый компаратор О, j-тый триггер установится в установится в О, переключатель управляеглый этим триггером, окажетс :в положении, при котором на j-тый интегратор во втором такте будет по дано положительное напряжение от ин вертора 2. Поэтому к концу второго такта (в момент tj.) компенсирующее напряжение на выходе j-ro инвертора будет равно тт Uvnax Urnax. UKJ - -- В соответствии с новым значением знака разности в момент времени t, производится перепись выходного сиг нала компараторов 8 в триггеры 10, а положение переключателей изменяет таким образом., чтобы к входу интегр торов 9 было приложено напряжениеj при воздействии которого разность между измеряег лм и компенсирующим напряжениями в течение третьего так та уменьшалось. Предыдущие состояния триггеров в момент . переписываются в соответствующие регистры (результат первого такта преобразования). Аналогично происходит уравновешивание на всех последующих тактах. Причем с увеличением номера такта модуль разности между измеряемыми и компенсирующими напряжениями в каждом канале стремится к нулю. Таким образом, во всех каналах одновременно путем порязрядного уравновешивания осуществляется преобразование измеряемых напряжений в код. Компенсирующие напряжения формируются в каждом канале независимо при интегрировании монотонно изменяющихся опорных напряжений, поступающих с выходов генератора 1 и инвертора 2. Длительность такта преобразования строго не фиксируется и определяется значением заряда электричества, передаваемого от генератора к интеграторам 3 и 9. На каждом последующем такте значение заряда уменьшается вдвое. При равных значениях постоянных времени интеграторов во всех каналах приращения компенсирующих напряжений на выходах интеграторов 8 с увеличением номера такта также уменьшаются вдвое. Дозировка заряда осуществляется с помощью интегратора 3, компаратора 4, цифроаналогового преобразователя 5 и регистра 6. Причем интегрирование одного из опорных напряжений (Uj-) происходит одновременно в интеграторах, формиру эщих компенсирующие гнапряжения (9), и в интеграторе 3. Поступление необходимого количества электричества фиксируется в момент, когда приращение напряжения на выходе интегратора 3 (U.) станет равным приращению образцового напряжения (Up), снимаемого с выхода цифроаналогового преобразователя 5. При поразрядном уравновешивании по двоичному основанию эти приращения задаются в виде ряда значений убыва ощей геометрической прогрессии со знаменателем 1/2 (iiJ2 , Л , . .., ii). В устройстве для повьшения быстродействия не производится сброс (разряд) интегратора 3 по окончании каждого такта, осуществляется непрерывное интегрирование в течение всего цикла преобразования. икcaция моментов поступления заданного количества электричества происходит -путем сравнения напряжения с выхода интегратора 3 и выходного напряжения цифроаналогового преобразователя, значения которого с помощью регистра б задаются равными последовательным значениям суммы членов геометрической прогрессии. Определим длительностью одного цикла преобразования в предположеНИИ, что 11 - const. Причем значен .з опорного напряжения таково что длительность первого такта в пре лагаемой системе равна длительности первого такта t в обычном аналогоцифровом преобразователе (АЦП) пораз рядного уравновешивания. (Заметим, что длительности всех тактов уравновешивания в АЦП, как правило, равны t, а общее Jpeмя преобразования в АЦП Тдцр mt , где m - число разрядов) .. Длительность первого такта в пред лагаемом устройстве равна времени t за которое выходное напряжение какого-либо интегратора изменится на U ox/2: -vv-i -jVat-Upt,. Из этого равенства находим требуемое значение U Длительность второго .такта . в предлагаемом устройстве равна вре мени, за которое выходное напряжение интеграторов изменится на Umox г ,, If Uvwax tii. -т- J и u. L - 7:- 4-t-, 7 Откуда t Очевидно, что длительность 1-тог такта t/g) а общее преобразования предлагаемой системы +t,n,,+... Если опорные напряжения сделать монотонно изменяющимися, а не постоянными , то быстродействие предлаг емого преобразователя более увеличи ся. В сравнении с мультиплицированно системой развертывающего уравновеши вания длительнос±ь одного цикла изм рения в предлагаемой системе в К Р 2t/)/2, tppas меньше.Обычно поэтому выигрыш в быстродействии по лучается весьма значительным Формула изобретения Мультиплицированная измерительная система, содержащая цифроаналоговый преобразователь, п каналов преобразования, канодый из которых выполнен на компараторе, первый вход которого соединен с соответствующей входной шиной, отличающаяся тем, что, с целью повышения быстродейстВИЯ, в нее введены инвертор, элемент ИЛИ, дополнительный компаратор, дополнительный интегратор, дополнительный регистр, генератор монотонно изменяющегося напряжения, в каждый канал преобразования введены триггер, интегратор, переключатель, регистр сдвига, при этом выход генератора монотонно изменяющегося напряжения соединен с входом инвертора, первым входом дополнительного интегратора и первыми входами переключателей, вторые входы которых соединены с выходом инвертора, причем первые входы интеграторов соединены с первым входом генератора монотонно изменяющегося напряжения, вторым входом дополнительного интегратора и R-входом дополнительного регистра сдвига, С-вход которого соединен с выходом элемента ИЛИ и С-входами триггеров и регистров сдвига, а выход через цифроаналоговый преобразователь соединен с первым входом дополнительного компаратора, второй вход которого соединен с выходом дополнительного интегратора, а выход - с первым входом элемента ИЛИ, второй вход которого соединен с вторым входом генератора монотонно изменяющегося н: пряжения-, при этом в каждом, канале выход компаратора соединен с D-входом триггера, выход которого соединен с D-входом регистра сдвига и управляющим входом пепеключателя, выход которого через интегратор соединен с вторым входом компаратора. Источники информации, принятые во внимание при экспертизе 1.Смолов В.Б. Полупроводниковые кодирующие и декодирующие преобразователи. Л., Энергия, 1967, с. 137, 138. 2,Цапенко М.П. Измерительные информационные системы. М,, Энергия, 1974, с. 163 (прототип).

ф1/г. f

Авторы

Даты

1982-11-07—Публикация

1978-11-02—Подача