1

Изобретение относится к автоматике и вычислительной технике и может быть использовано в системах обработки цифровой информации,

Цель изобретения - расширение функциональных возможностей путем обеспечения подсчета числа единиц входного кода по модулю k, где k - заданный вес п-разрядного входного кода.

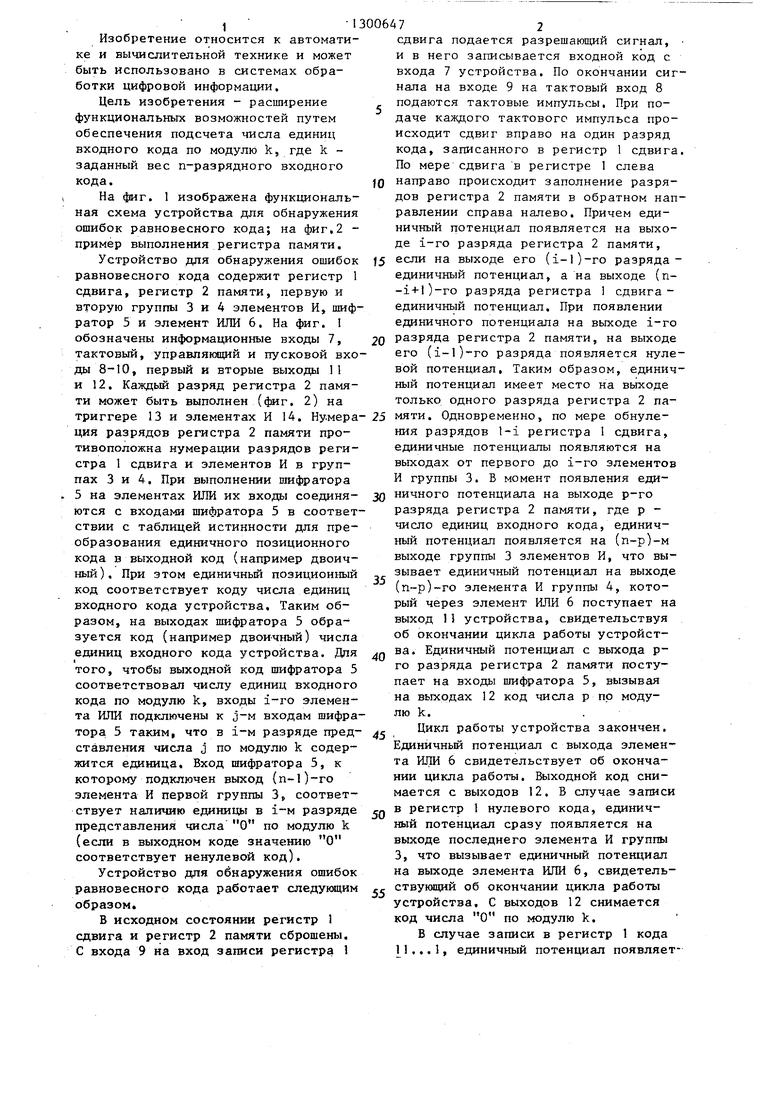

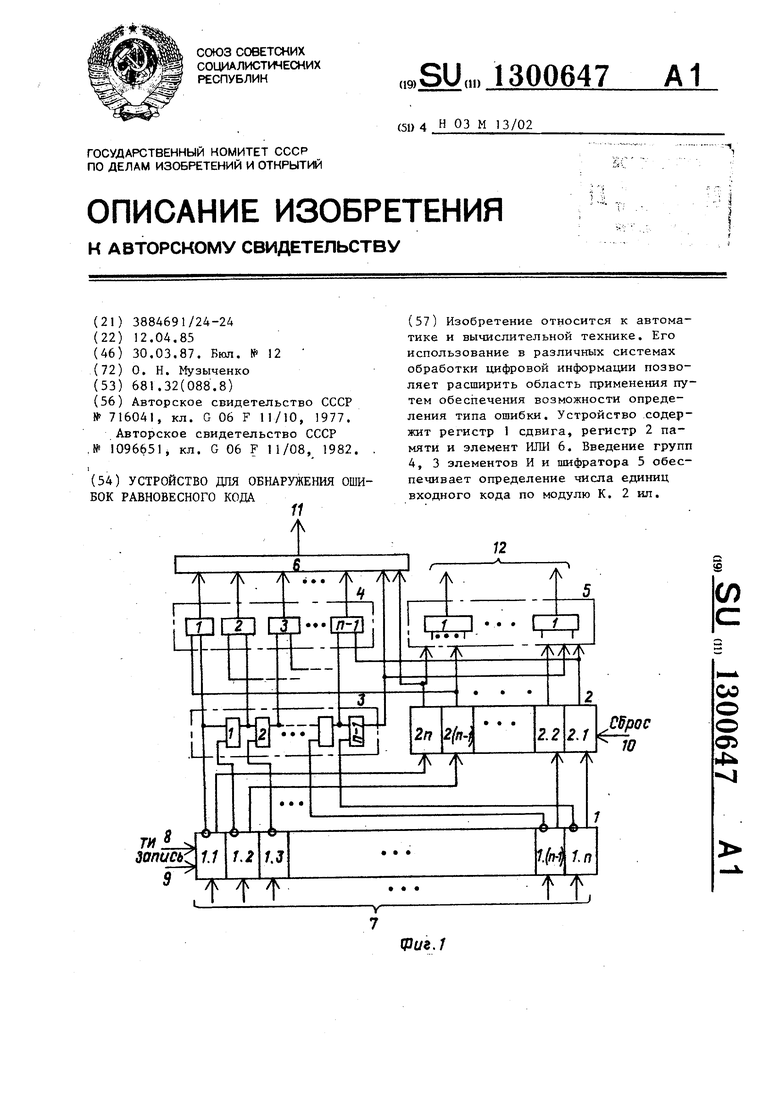

На фиг. 1 изображена функциональная схема устройства для обнаружени ошибок равновесного кода; на фиг,2 пример выполнения регистра памяти.

Устройство для обнаружения ошибо равновесного кода содержит регистр сдвига, регистр 2 памяти, первую и вторую группы 3 и 4 элементов И, ширатор 5 и элемент ИЛИ 6. На фиг. обозначены информационные входы 7, тактовый, управляющий и пусковой вхды 8-10, первый и вторые выходы 11 и 12. Каждый разряд регистра 2 памяти моркет быть выполнен (фиг. 2) на

триггере 13 и элементах И 14. Нумера- 25 мяти. Одновременно, по мере обнулеция разрядов регистра 2 памяти противоположна нумерации разрядов регистра 1 сдвига и элементов И в группах 3 и 4. При выполнении шифратора 5 на элементах ИЛИ их входы соединяются с входами шифратора 5 в соответствии с таблицей истинности для преобразования единичного позиционного кода в выходной код (например двоичный). При этом единичный позиционный код соответствует коду числа единиц входного кода устройства. Таким образом, на выходах шифратора 5 образуется код (например двоичный) числа единиц входного кода устройства. Дпя того, чтобы выходной код шифратора 5 соответствовал числу единиц входного кода по модулю k, входы 1-го элемента ИЛИ подключены к J-M входам шифратора. 5 таким, что в i-м разряде представления числа j по модулю k содержится единица. Вход шифратора 5, к которому подключен выход {n-l)-ro элемента И первой группы 3, соответствует наличию единицы в i-м разряде представления числа О по модулю k (если в выходном коде значению О соответствует ненулевой код).

Устройство для обнаружения ошибок равновесного кода работает следующим образом.

В исходиом состоянии регистр 1 сдвига и регистр 2 памяти сброшены. С входа 9 на вход записи регистра 1

5

0

сдвига подается разрешающий сигнал, и в него записывается входной код с входа 7 устройства. По окончании сигнала на входе 9 на тактовый вход 8 подаются тактовые импульсы. При подаче каждого тактового импульса происходит сдвиг вправо на один разряд кода, записанного в регистр 1 сдвига. По мере сдвига в регистре 1 слева направо происходит заполнение разрядов регистра 2 памяти в обратном направлении справа налево. Причем единичный потенциал появляется на выходе i-ro разряда регистра 2 памяти, если на выходе его (i-l)-ro разряда - единичный потенциал, а на выходе (п- -i + l)-ro разряда регистра 1 сдвига- единичньш потенциал. При появлении единичного потенциала на вькоде i-ro разряда регистра 2 памяти, на выходе его (i-l)-ro разряда появляется нулевой потенциал;. Таким образом, единичный потенциал имеет место на вьлходе только одного разряда регистра 2 па0

5

0

5

0

5

ния разрядов t-i регистра 1 сдвига, единичные потенциалы появляются на выходах от первого до i-ro элементов И группы 3. В момент появления единичного потенциала на выходе р-го разряда регистра 2 памяти, где р - число единиц входного кода, единичный потенциал появляется на (п-р)-м выходе группы 3 элементов И, что вызывает единичный потенциал на выходе (п-р)-го элемента И группы 4, который через элемент ИЛИ 6 поступает на выход 11 устройства, свидетельствуя об окончании цикла работы устройства. Единичный потенциал с выхода р- го разряда регистра 2 памяти поступает на входы шифратора 5, вызывая на выходах 12 код числа р по модулю k..

Цикл работы устройства закончен. Единичный потенциал с выхода элемента ИЛИ 6 свидетельствует об окончании цикла работы. Выходной код снимается с выходов 12. В случае записи в регистр 1 нулевого кода, единичный потенциал сразу появляется на выходе последнего элемента И групгы 3, что вызывает единичный потенциал на выходе элемента ИЛИ 6, свидетельствующий об окончании цикла работы устройства, С выходов 12 снимается код числа О по модулю k.

В случае записи в регистр 1 кода 1 1 ... 1, единичный потенциал появляется на выходе п-го разряда регистра 2 памяти, что вызывает единичный потенциал на выходе элемента ИЛИ 6, свидетельствующий об окончании цикла работы. С выходов шифратора 5 снимается код числа п по. модулю k.

Таким образом обеспечивается контроль числа единиц двоичного кода по модулю k на входах устройства.

Формула изобретения

Устройство для обнаружения ошибок равновесного кода, содержащее зле- мент ИЛИ, выход которого является первым выходом устройства, регистр сдвига, прямые выходы разрядов которого с п-го по (n-k+l)-й, где п и k- соответственно разрядность и вес входного кода, соединены с первого по k-й информационными входами регистра памяти соответственно, информационные входы регистра сдвига является информационными входами устройства, тактовый и управляюи ий входы регистра сдвига и вход обнуления регистра памяти являются соответственно тактовым, управляющим и пусковым входами устройства, отличающ е е с я тем, что, с целью распшре-30 шифратора, выходы которого являются ния области применения за счет обес- вторыми выходами устройства.

печения возможности определения типа ошибки, в устройство введены 1иифра- тор и группы элементов И, прямые выходы разрядов регистра сдвига с (п- -k)-ro по первый соединены с информационными входами разрядов регистра памяти соответственно с (k+l)-ro по п-й, инверсный выход первого разряда регистра сдвига соединен с первыми

входами первых элементов И групп, выход каждого элемента И первой группы, кроме последнего, подключен к первым входам последуюпщх элементов И первой и второй групп, инверсные выходы

разрядов регистра сдвига с второго по п-й соединены с вторыми входами элементов И первой группы соответственно с первого по (п-1)-й, выходы разрядов регистра памяти с (n-i)-ro

по первый подключены к вторым входам элементов И второй группы соответственно с первого по (п-1)-й, выходы которых, выход (n-l)-ro элемента И первой группы и выход п-го разряда

регистра памяти подключены к соотвёт- ствукжщм входам элемента ИЛИ, выхода разрядов регистра памяти и выход (п- -l)-ro элемента И первой группы соег , динены с соответствукнцими входами

12./1

2.()

Фиг.г

Составитель О. Ревинский Техред А.Кравчук

Заказ 1160/56Тираж 902

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

Корректор Г, Решетник

.Подписное

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля равновесного кода | 1985 |

|

SU1339900A1 |

| Система передачи и приема информации с коррекцией ошибок | 1985 |

|

SU1311036A1 |

| Устройство для вычисления минимального покрытия | 1990 |

|

SU1815634A1 |

| Устройство для сопряжения @ -датчиков с ЭВМ | 1986 |

|

SU1327114A1 |

| Устройство для обнаружения ошибок в параллельном @ -разрядном коде | 1984 |

|

SU1168948A1 |

| Устройство для поиска информации | 1989 |

|

SU1686464A1 |

| Цифровой фильтр | 1986 |

|

SU1387016A1 |

| Устройство для моделирования распределения приоритетов | 1986 |

|

SU1352499A1 |

| Устройство для реализации быстрых преобразований в базисах дискретных ортогональных функций | 1985 |

|

SU1292005A1 |

| Устройство для умножения по модулю 2 @ -1 | 1985 |

|

SU1304019A1 |

| Устройство для определения количества едениц в двоичном числе | 1977 |

|

SU716041A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| .Авторское свидетельство СССР ,№ 1096651, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1987-03-30—Публикация

1985-04-12—Подача