113

Изобретение относится к автоматике и вычислительной технике и может быть использовано в системах передачи и обработки информации,

Цель изобретения - повышение достоверности передачи.

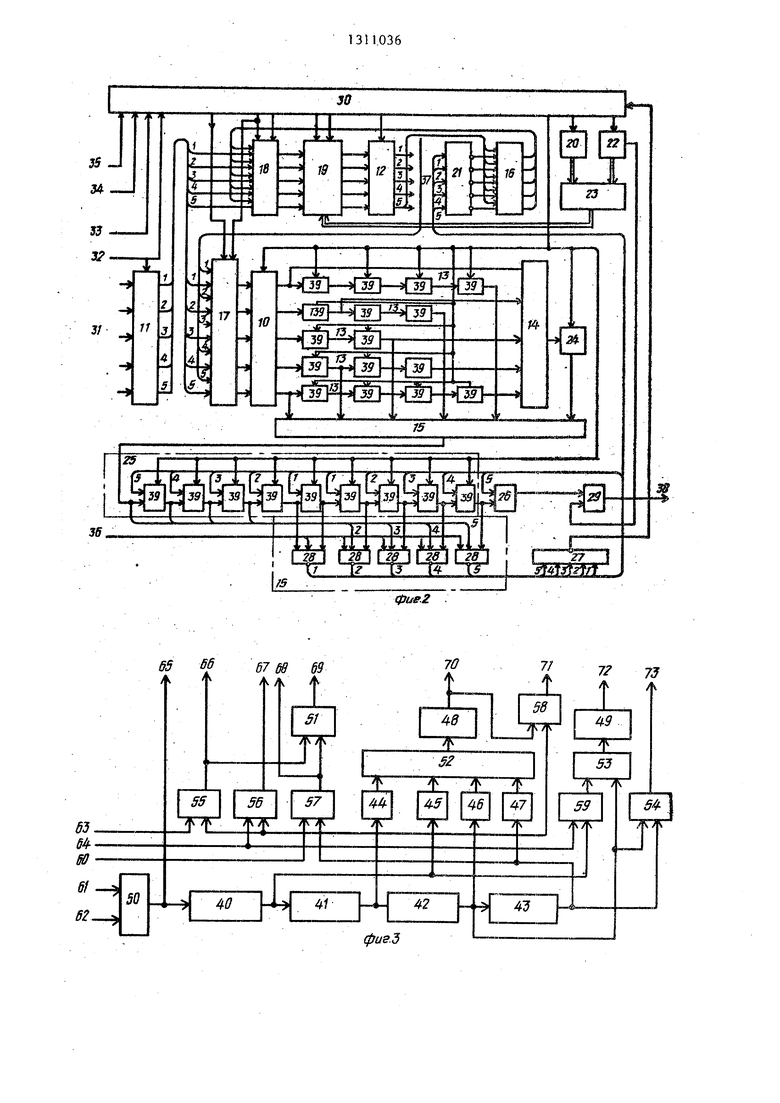

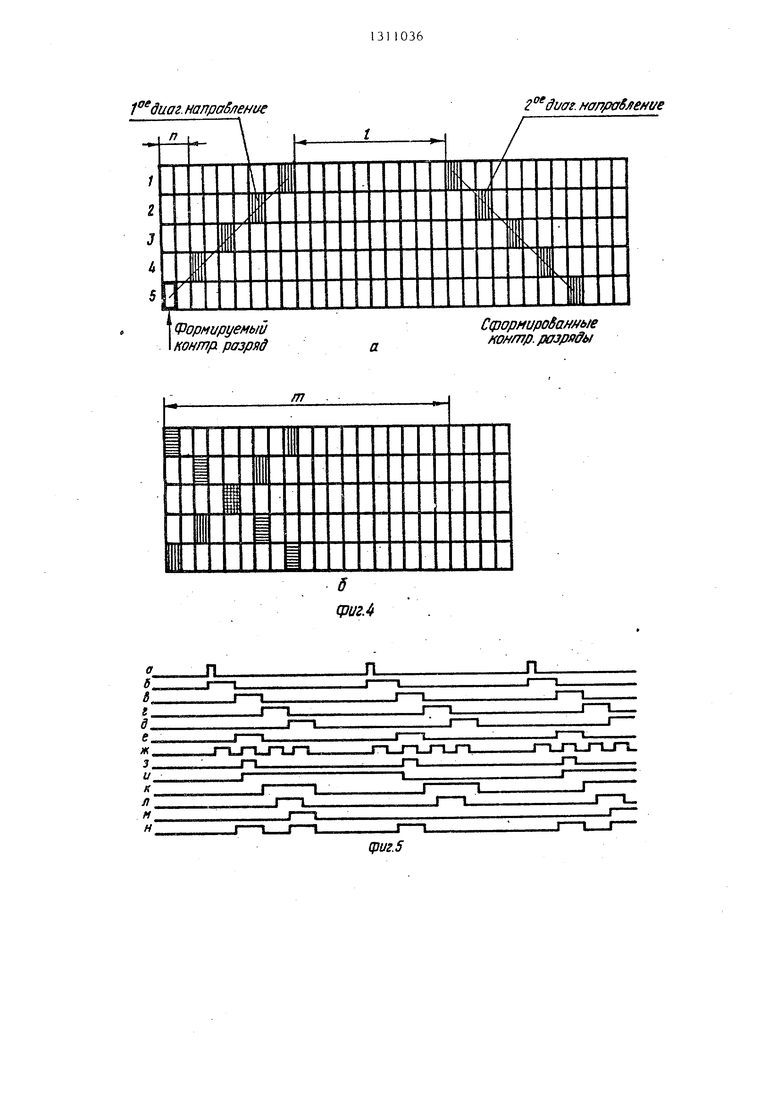

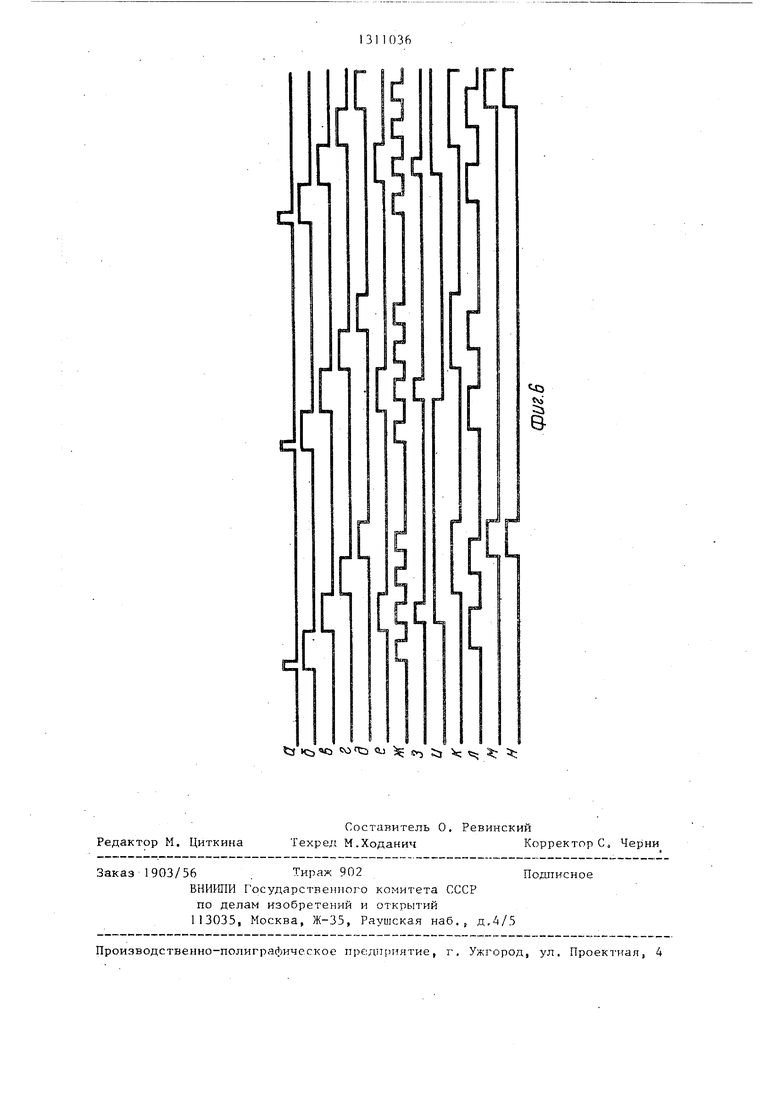

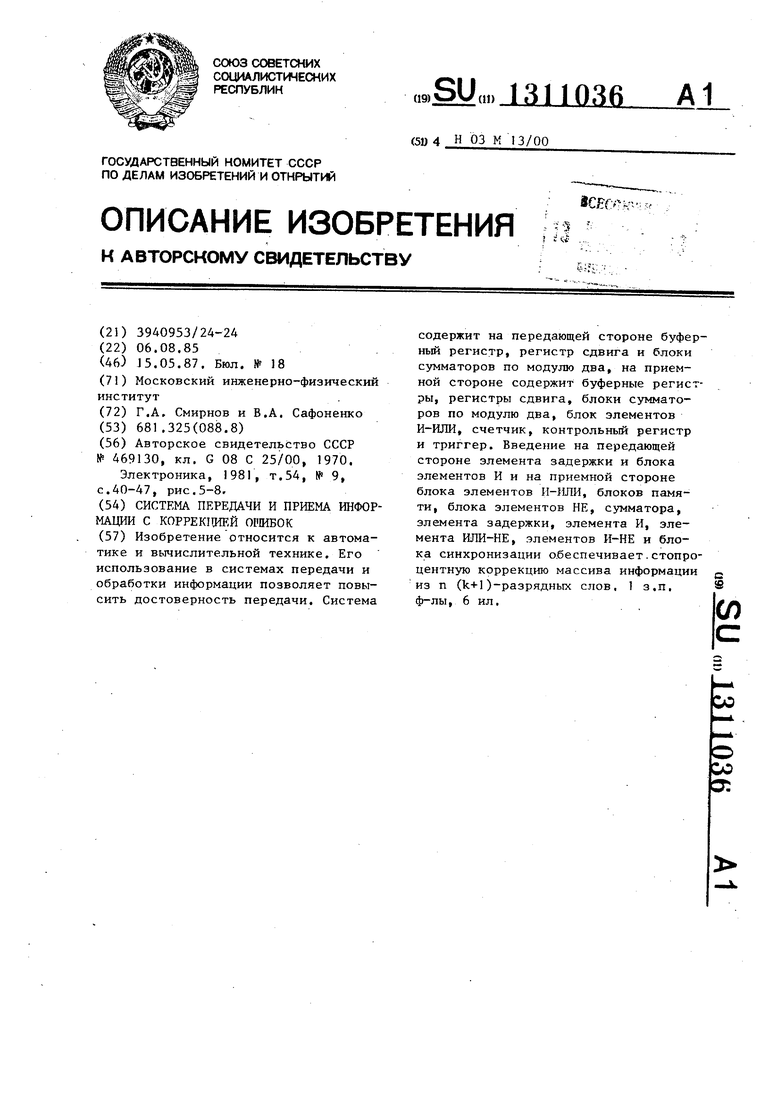

На фиг.1 и 2 изображены функциональные, схемы соответственно передающей и приемной сторон; на фиг.З - схема блока синхронизации; на фиг,4- диаграмма формирования диагональных векторов; на фиг.З и 6 - временные диаграммы работы блока синхронизации на приемной стороне в режимах соответственно приема и коррекции информации .

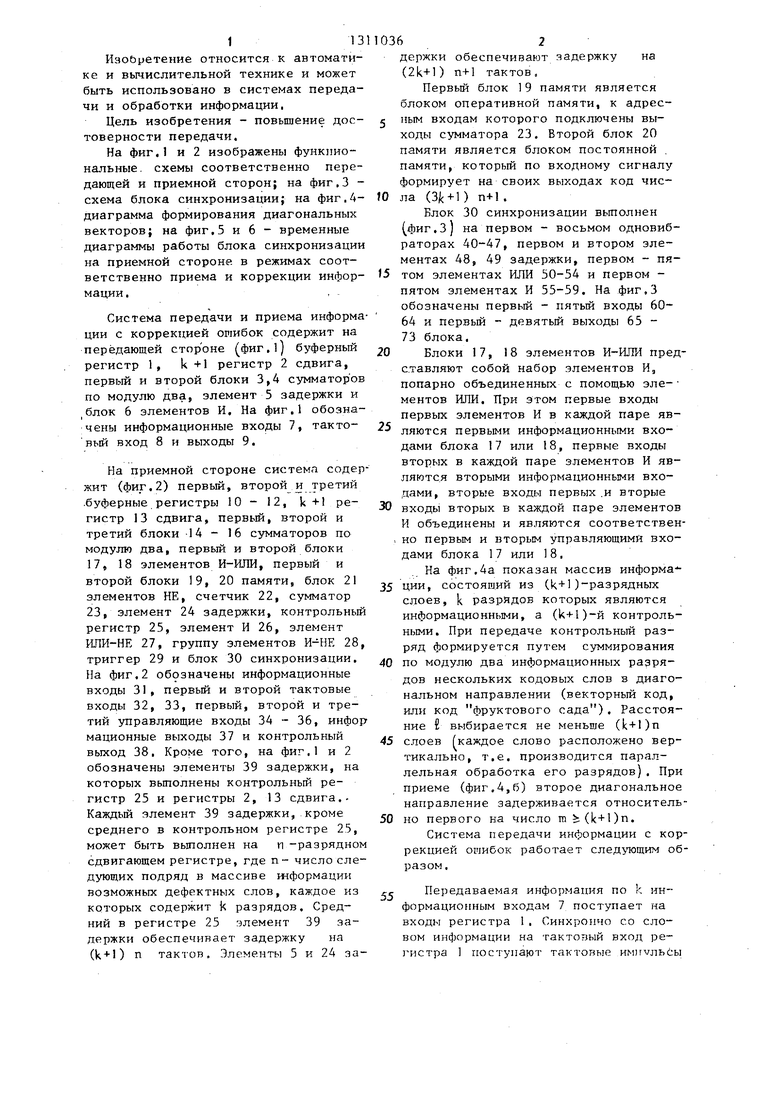

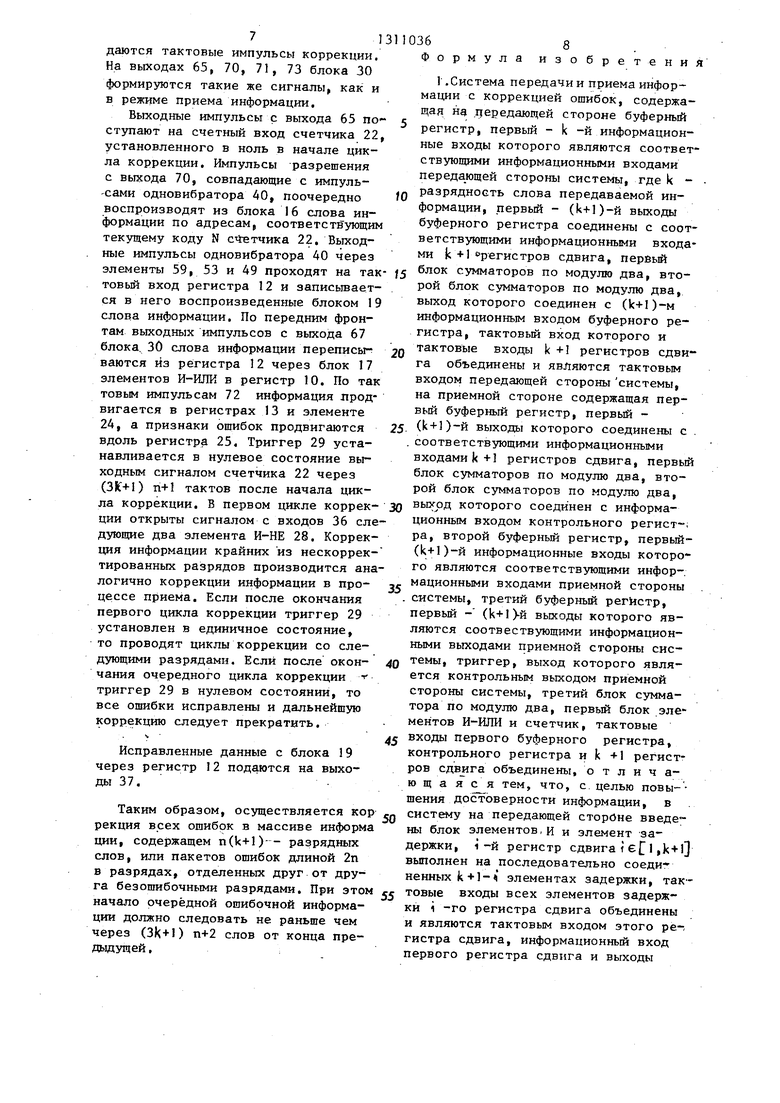

Система передачи и приема информации с коррекцией ошибок содержит на передающей стор оне (фиг.1) буферный регистр 1, k +1 регистр 2 сдвига, первый и второй блоки 3,4 сумматор ов по модулю два, элемент 5 задержки и ,блок 6 элементов И. На фиг,1 обозначены информационные входы 7, такто- вый вход 8 и выходы 9.

На приемной стороне система содержит (фиг.2) первый, второй и третий .буферные регистры 10 - 12, k +1 регистр 13 сдвига, первый, второй и третий блоки -14 - 16 сумматоров по модулю два, первый и второй блоки 17, 18 элементов И-ИЛИ, первый и второй блоки 19, 20 памяти, блок 21 элементов НЕ, счетчик 22, сумматор 23, элемент 24 задержки, контрольный регистр 25, элемент И 26, элемент ИЛИ-НЕ 27, группу элементов И-НЕ 28, триггер 29 и блок 30 синхронизации. На фиг.2 обозначены информационные входы 31, первьй и второй тактовые входы 32, 33, первый, второй и третий управляющие входы 34 - 36, инфор мационные выходы 37 и контрольный выход 38. Кроме того, на фиг.1 и 2 обозначены элементы 39 задержки, на которых выполнены контрольный регистр 25 и регистры 2, 13 сдвига.. Каждый элемент 39 задержки, кроме среднего в контрольном регистре 25, может быть выполнен на п -разрядном сдвигающем регистре, где п число следующих подряд в массиве И1формации возможных дефектных слов, каждое из которых содержит k разрядов. Средний в регистре 25 элемент 39 задержки обеспечивает задержку на (k+1) п тактов. Элементы 5 и 24 за62

держки обеспечивают задержку на (2k+) п+1 тактов,

Первый блок 19 памяти является блоком оперативной памяти, к адресиым входам которого подключены выходы сумматора 23. Второй блок 20 памяти является блоком постоянной памяти, который по входному сигналу формирует на своих выходах код числа (3fe+l) п+.

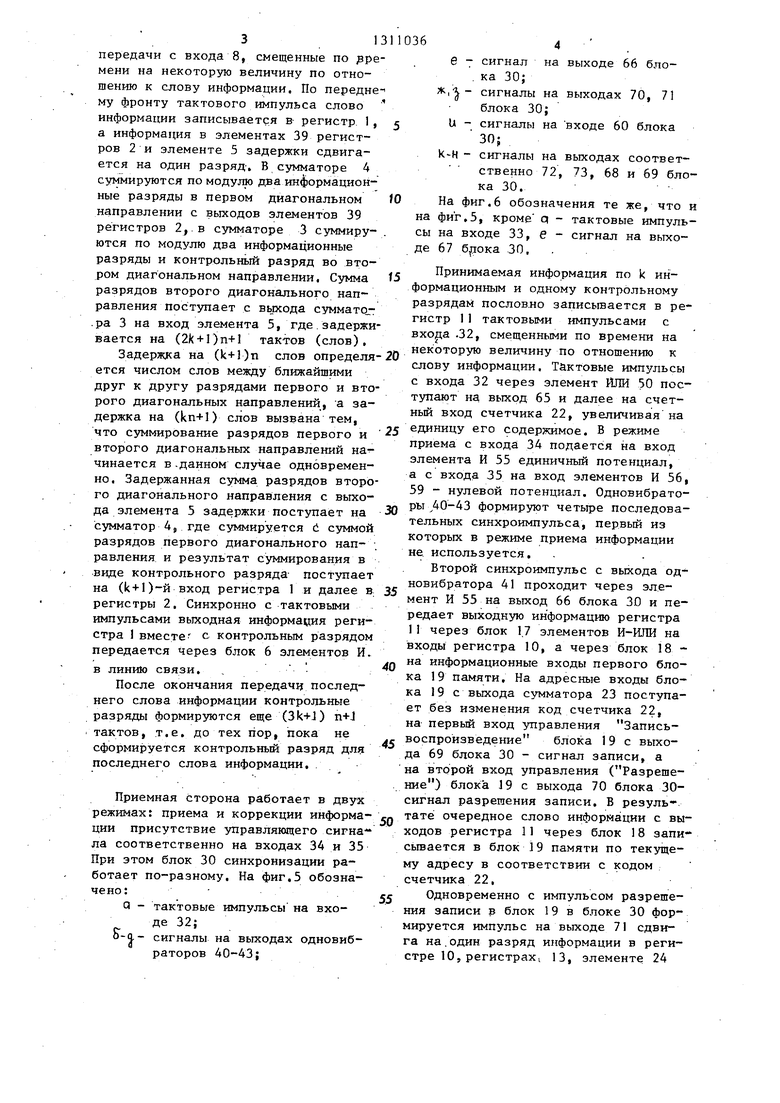

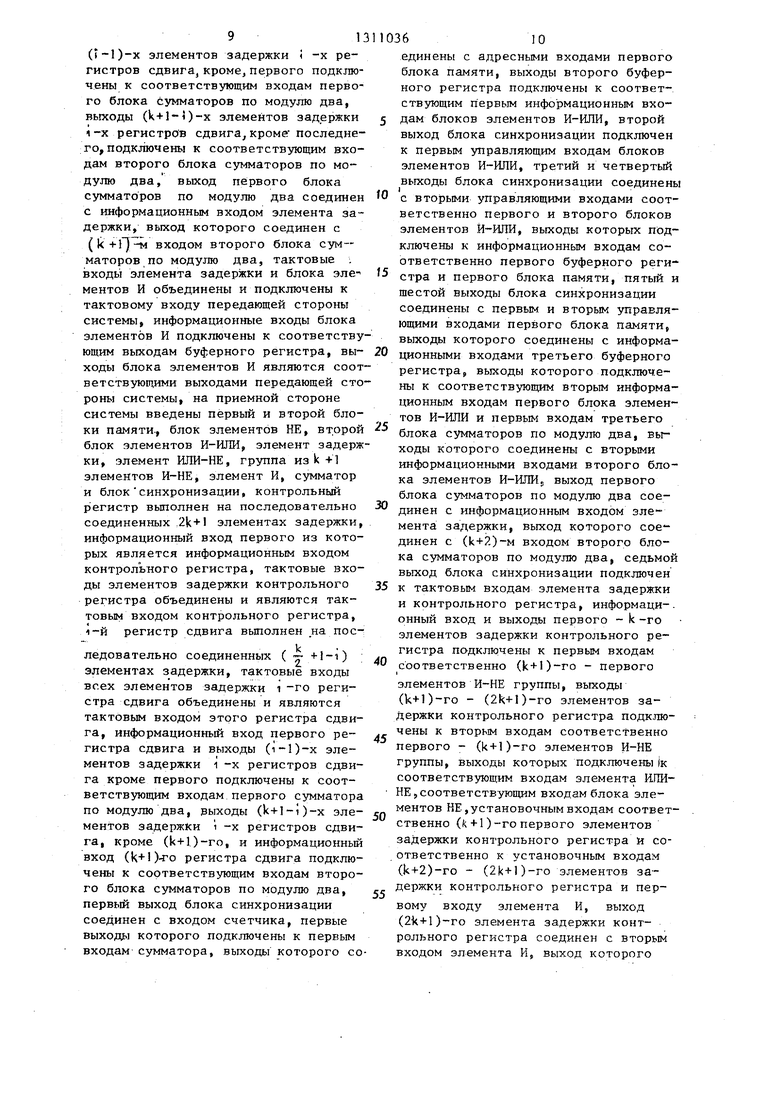

Блок 30 синхронизации выполнен (фиг.З) на первом - восьмом одновиб- раторах 40-47, первом и втором элементах 48, 49 задержки, первом - пятом элементах ИЛИ 50-54 и первом - пятом элементах И 55-59. На фиг.З обозначены первый - пятый входы 60- 64 и первый - девятый выходы 65 - 73 блока.

Блоки 17, 18 элементов И-ИЛИ пред- с.тавляют собой набор элементов И, попарно объединенных с помощью эле- ментов ИЛИ. При этом первые входы первых элементов И в каждой паре являются первыми информационными входами блока 17 или 18, первые входы вторых в каждой паре элементов И являются вторыми информационными входами, вторые входы первых .и вторые

входы вторых в каждой паре элементов И объединены и являются соответствен- но первым и вторым управляющими входами блока 17 или 18,

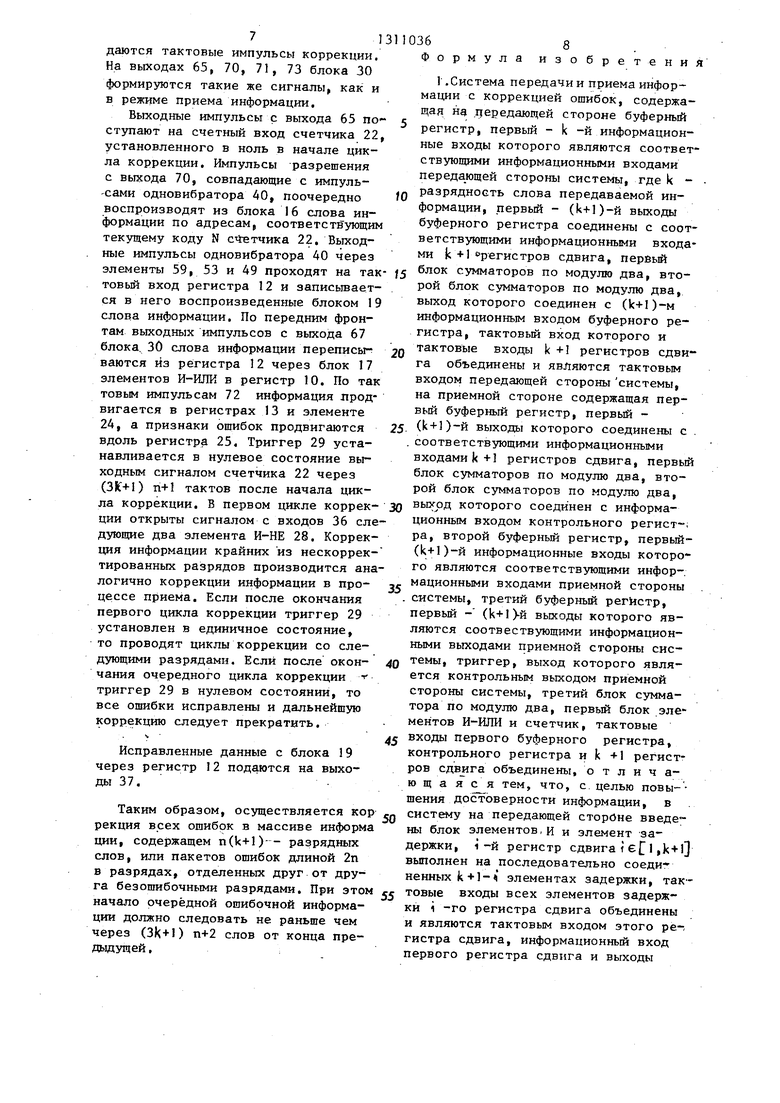

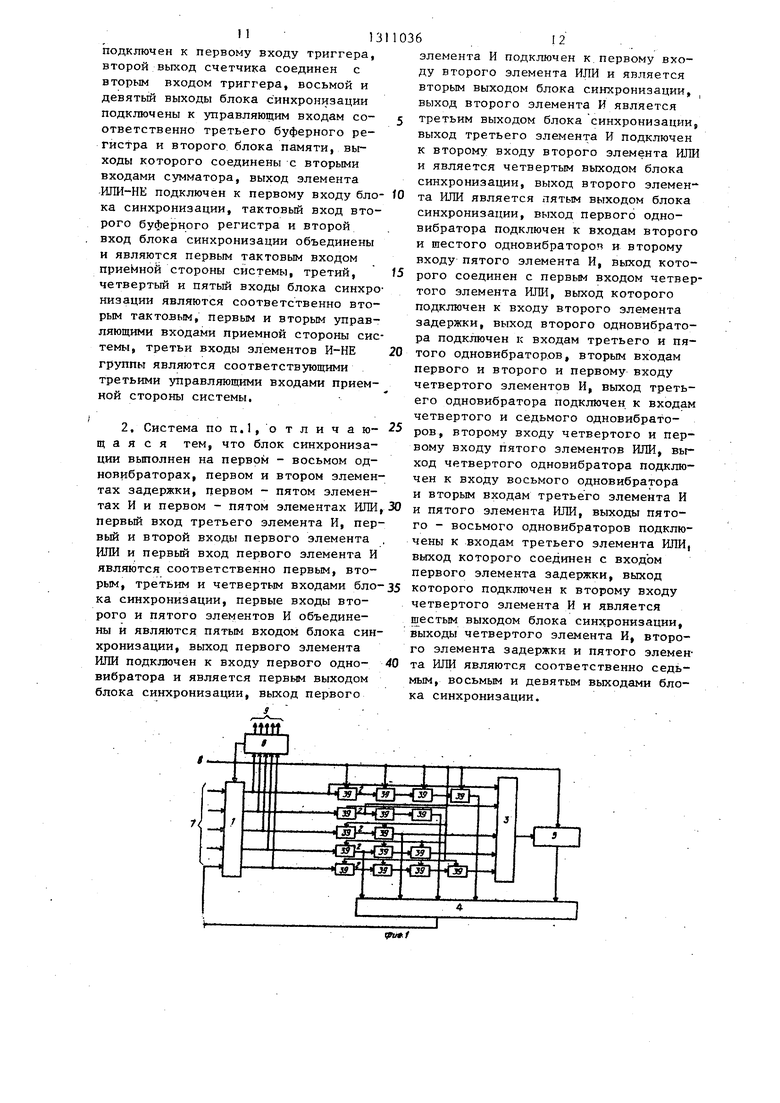

На фиг.4а показан массив информации, состояший из (k+1)разрядных слоев, k разрядов которых являются информационными, а (k+l)-й контрольными. При передаче контрольный разряд формируется путем суммирования

по модулю два информационных разрядов нескольких кодовых слов в диагональном направлении (векторньш код, или код фруктового сада). Расстояние выбирается не меньше (k+I)n

слоев fкaждoe слово расположено вертикально, т.е. производится параллельная обработка его разрядов). При приеме (фиг,4,б) второе диагональное направление задерживается относительно первого на число m b(k+l)n.

Система передачи информации с коррекцией ошибок работает следующим образом .

Передаваемая информапия по k информационным входам 7 поступает на входы регистра 1, Синхронно со словом информации на тактовый вход регистра 1 поступают тактовые ИМПУЛЬСЫ

31

передачи с входа 8, смещенные по ре мени на некоторую величину по отношению к слову информации. По передне му фронту тактового импульса слово информации записывается в регистр 1, а информация в элементах 39 регистров 2 и элементе 5 задержки сдвигается на один разряд-, В сумматоре 4 суммируются по модуш) два информационные разряды в первом диагональном направлении с выходов элементов 39 регистров 2,. в сумматоре 3 суммируются по модулю два информационные разряды и контрольньгй разряд во втором диагональном направлении. Сумма разрядов второго диагонального направления поступает с выхода суммато - .ра 3 на вход элемента 5| где.задерживается на (2)( + 1)п+1 тактов (слов).

Задержка на (k+l)n слов определяется числом слов между ближайшими друг к другу разрядами первого и второго диагональных направлений, а задержка на (kn+l) слов вызвана тем, что суммирование разрядов первого и второго диагональных направлений начинается в-данном случае одновременно. Задержанная сумма разрядов второго диагонального направления с выхода элемента 5 задержки поступает на сумматор 4, где суммируется ci суммой разрядов первого диагонального нап- равления и результат суммирования в виде контрольного разряда- поступает на (k + l)-й вход регистра 1 и далее В регистры 2, Синхронно с тактовыми импульсами выходная информация регистра 1 вместе с контрольным разрядом передается через блок 6 элементов И.

в линию связи, , После окончания передачи последнего слова информации контрольные разряды формируются еще (3k+J) n+J : тактов, т.е, до тех пор, пока не сформируется контрольный разряд для последнего слова информации,.

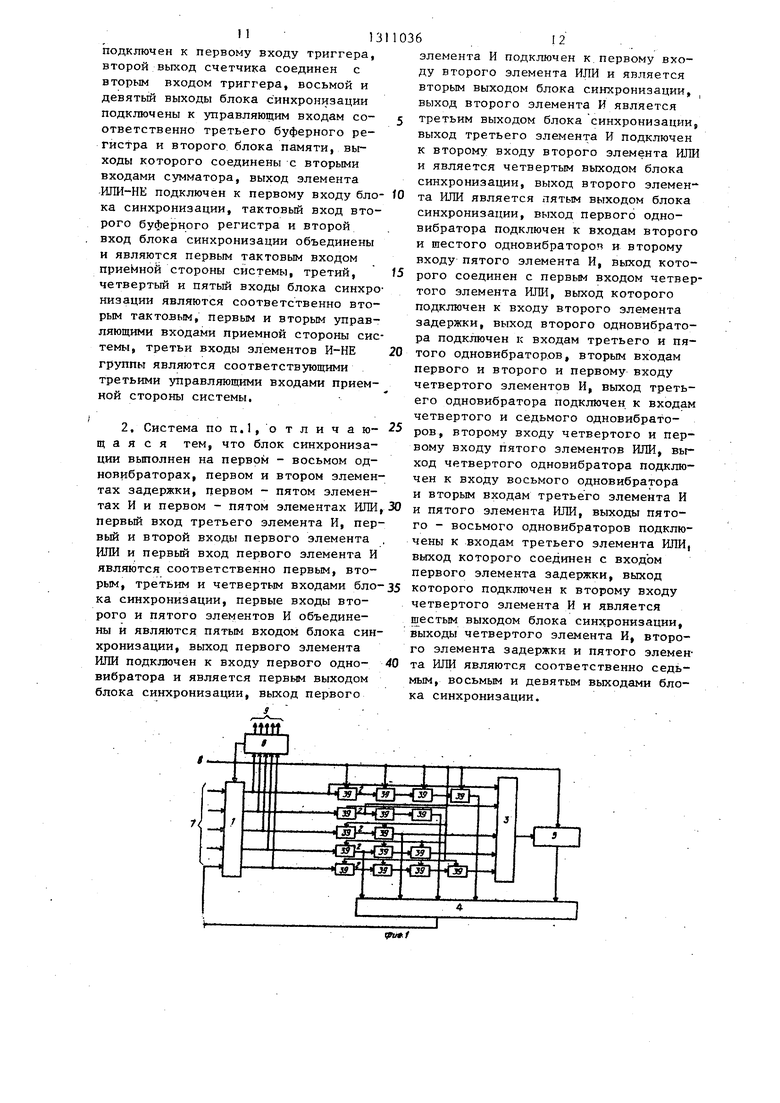

Приемная сторона работает в двух режимах: приема и коррекции информации присутствие управляющего сигнала соответственно на входах 34 и 35 При этом блок 30 синхронизации работает по-разному. На фиг,5 обозначено:

Q - тактовые импульсы на входе 32;

Ь-а- сигналы на выходах одновиб- раторов 40-43;

10364

е - сигнал на выходе 66 бло. ка 30; ж, сигналы на выходах 70, 71

блока 30; U - сигналы на входе 60 блока

30;

k H - сигналы на выходах соответственно 72, 73, 68 и 69 блока 30,

0 На фиг,6 обозначения те же, что и на фиг,5, кроме q - тактовые импульсы на входе 33, е - сигнал на выходе 67 брока 30, .

, Принимаемая информация по k формационным и одному контрольному разрядам пословно записьшается в регистр 11 тактовыми импульсами с входа .32, смещенными по времени на

f. некоторую величину по отношению к слову информации. Тактовые импзшьсы с входа 32 через элемент ИЛИ 50 поступают на выход 65 и далее на счет- ньш вход счетчика 22, увеличивая на

5 единицу его содержимое, В режиме приема с входа 34 подается на вход элемента И 55 единичный потенциал, а с входа 35 на вход элементов И 56, 59 - нулевой потенциал, Одновибратол ры 40-43 формируют четьфе последовательных синхроимпульса, первый из которых в режиме приема информации не. используется.

Второй синхроимпульс с выхода од- новибратора 41 проходит через элемент И 55 на выход 66 блока 30 и передает выходную информацию регистра 11 через блок 17 элементов И-ИЛИ на

входы регистра 10, а через блок 18 Q на информационные входы первого блока 19 памяти. На адресные входы блока 19 с выхода сумматора 23 поступает без изменения код счетчика 22, на первый вход управления Записьс воспроизведение блока 19 с выхода 69 блока 30 - сигнал записи, а на второй вход управления (Разреше- . ние) блока 19 с выхода 70 блока 30- сигнал разрешения записи, В резуль тате очередное слово информации с выходов регистра 11 через блок 18 записьшается в блок 19 памяти по текущему адресу в соответствии с кодом счетчика 22,

Одновременно с импульсом разрешения записи в блок 19 в блоке 30 формируется импульс на выходе 71 сдвига на.один разряд информации в регистре 10, регистрах 13, элементе 24

5

5

513

и в регистре 25. Б сумматоре.15 суммируется по модулю два информационные и контрольный разряды в первом диагональном направлении, в сумматоре 14 суммируются информационные и контрольный разряды во втором диагональном направлении. Сумма разрядов второго диагонального направления, задержанная элементом 24 на (2k+l) п+1 тактов, суммируется по модулю два в сумматоре 15 с суммой разрядов первого диагонального направления. На выходе сумматора 15 формируется или единичный сигнал нарушения четности суммы по модулю два разрядов двух диагональных направлений, или нулевой сигнал при сохранении четности суммы разрядов двух диагональных направлений. Единичные и нулевые сигналы с.умматора 15 являются признаками наличия и отсутствия ошибок и-последовательно запоминаются в контрольном регистре 25.

Каждый ошибочньй разряд представлен в регистре 25 двумя единичными признаками, которые располагаются через определенное количество разрядов друг от друга в зависимости от номера дефектного разряда. Импульсами с выхода 71 блока 30 признаки ошибок продвигаются в регистре 25 от его входа к выходу. На элементах И-НЕ 28 производится определение попарно совпадающих единичных признако ошибок, Наличие ошибок в каждом разряде слова определяется одним из элементов 28, соответствующим этому разряду, В процессе приема информации контролируется наличие попарно совпадающих ошибок в двух крайних разрядах, Дпя этого на третьи входы двух соответствующих элементов 28 посту- пает единичный потенциал управляющей команды с входов 36, а на третьи входы остальных элементов 28 поступает нулевой потенциал. При наличии совпадающих признаков ошибок на выходе соответствующего элемента 28 устанавливается нулевой потенциал, который поступает на установочные входы (k- -2)-ro - ()-ro элементов 39 задержки или элемента И 26, запрещая передачу совпадающих признаков ошибок в следующий разряд.регистра 25. Нулевой сигнал с выхода элемента И-НЕ 28 через элемент ИЛИ-НЕ. 27 поступает на первый вход блока 30, участвуя в образовании

6

сигнала на выходе 69 и формируя сигнал на выходе 68. В блоке 30 с по- моо1ЬЮ одновибраторов 42 и 43 формируется сигнал на выходе 73, поступающий на вход второго блока 20 памяти По .этому сигналу на выходе блока 20 формируется код (3k+On+l , который в сумматоре 23 вь(читается из кода N счетчика 22. По сигналу с вы

хода 70, совпадающему с импульсом одновибратора 42, в блоке 19 производится воспроизведение по адресу N-()n-l слова информации, которое по переднему фронту импульса 73

записывается в регистр 12 и поступает на первые входы двухвходовых сумматоров по модулю два блок 16. На вторые входы сумматоров блока 16 поступают проинвертированные блоком 21 сигналы с выходов элементов И-НЕ 28, При наличии совпадающих признаков ошибок на второй вход соответствующего суматтора блока 16 поступает единичный сигнал. На выходах блока 16 образуется слово информации, скорректированное по первому разрядам, которое через блок 18 по сигналу с выхода 68 поступает на информационные входы блока 19,

где и записывается по тому же адре50

су импульсом разрешения с выхода 70 совпадающим с выходным сигналом од- новибратора 43

Если признаки ошибок не совпали

35 на эл.ементах И-НЕ 28, то элемент ИЛИ-НЕ 27 формирует нулевой сигнал, элемент И 57 блока 30 не вырабатывает на выходе 68 сигнала передачи информации с выхода блока 16 через

40 блок 18, а на выходе 70 - сигнала записи информации в блок 19, Слово информации по данному адресу в блоке 19 остается без изменений.

Таким образом производится коррекция всех слов принимаемой информации. После окончания приема в блоке 19 буд.ет записан весь массив при- нятой информации, скорректированный в первом и (k+1) разрядах. При наличии нескорректированных ошибок они проходят на выход регистра 25 и устанавливают триггер 29 в единичное состояние. В этом случае необходимо

провести дополнительную коррекцию информации, записанной в блоке 19.

Для проведения коррекции на вход 35 подается единичный потенциал„ на вход 34 - нулевой, а по входу 33 по

7

даются тактовые импульсы коррекции. На выходах 65, 70, 71, 73 блока 30 формируются такие же сигналы, как и в режиме приема информации.

Выходные импульсы с выхода 65 поступают на счетный вход счетчика 22 установленного в ноль в начале цикла коррекции. Импульсы разрешения с выхода 70, совпадающие с импуль- -сами одновибратора 40, поочередно

воспроизводят из блока 16 слова информации по адресам, соответствующи

тек5тцему коду N сг1 тчика 22, Выходные импульсы одновибратора 40 через элементы 59, 53 и 49 проходят на та товьй вход регистра 12 и записьгоает ся в него воспроизведенные блоком 1 слона информации. По передним фронтам выходных импульсов с выхода 67 блока. 30 слова информации переписьп ваются из регистра 12 через блок 17 элементов И-ИЛК в регистр 10, По та товым импульсам 72 информация продвигается в регистрах 13 и элементе 24, а признаки ошибок продвигаются вдоль регистра 25, Триггер 29 устанавливается в нулевое состояние выходным сигналом счетчика 22 через (3lf+l) п+1 тактов после начала цикла коррекции, В первом цикле коррекции открыты сигналом с входов 36 слдующие два элемента И-НЕ 28, Коррекция информации крайних из нескоррек тированных разрядов производится анлогично коррекции информации в про- це1ссе приема. Если после окончания первого цикла коррекции триггер 29 установлен в единичное состояние, то проводят циклы коррекции со следующими разрядами. Если после окончания очередного цикла коррекции - триггер 29 в нулевом состоянии, то все ошибки исправлены и дальнейшую коррекцию следует прекратить.

Исправленные данные с блока 19 через регистр 12 подаются на выходы 37,

45 входы первого буферного регистра, контрольного регистра и k +1 регистров сцвкга объединены, отличающаяся тем, что, с. целью повы-шения достоверности информации, в Таким образом, осуществляется кор „ систему на передающей стороне введе

ны блок элементов, и и элемент -за- держки, i-и регистр сдвига т ef 1 ,k-«-l вьшолнен на последовательно соединенных k + 1 - i элементах задержки, такрекция всех ошибок в массиве информа ции, содержащем n(k+l)-- разрядных слов, или пакетов ошибок длиной 2п в разрядах, отделенных друг от друга безошибочными разрядами. При этом товые входы всех элементов задерж- начало очерёдной ошибочной информа- ки i -го регистра сдвига объединены ции должно следовать не раньше чем и являются тактовым входом этого ре-, через (3k+l) п+2 слов от конца пре- гистра сдвига, информационньй вход дыдущей,первого регистра сдвига и выходы

мула

8 зоб

р е т е и и я

Фор

5

1 .Система передачи и приема информации с коррекцией ошибок, содержащая на .цередающей стороне буферный регистр, первый - k -и информационные входы которого являются соответствующими информационными входами переда ющей стороны системы, где k - разрядность слова передаваемой информации, первый - (k+)-й выходы буферного регистра соединены с соответствующими информационными входами k+1 регистров сдвига, первьй

блок сумматоров по модулю два, второй блок сумматоров по модулю два, выход которого соединен с (k+I)-M информационным входом буферного регистра, тактовый вход которого и тактовые входы k +1 регистров сдвига объединены и являются тактовым входом передающей стороны системы, на приемной стороне содержащая первый буферный регистр, первый - (k+l)й выходы которого соединены с . соответствующими информационными входами k+1 регистров сдвига, первый блок сумматоров по модулю два, второй блок сумматоров по модулю два, выход которого соединен с информационным входом контрольного регист- ра, второй буферный регистр, первьй- (k+l)й информационные входы которого являются соответствующими информационными входами приемной стороны системы, третий буферньй регистр, первьй - (k+l)-й выходы которого являются соотвествующими информационными выходами приемной стороны системы, триггер, выход которого является контрольным выходом приемной стороны системы, третий блок сумматора по модулю два, первьй блок элементов И-ИЛИ и счетчик, тактовые

5 входы первого буферного регистра, контрольного регистра и k +1 регистров сцвкга объединены, отличающаяся тем, что, с. целью повы-0

5

0

0

ны блок элементов, и и элемент -за- держки, i-и регистр сдвига т ef 1 ,k-«-l вьшолнен на последовательно соединенных k + 1 - i элементах задержки, тактовые входы всех элементов задерж- ки i -го регистра сдвига объединены и являются тактовым входом этого ре-, гистра сдвига, информационньй вход первого регистра сдвига и выходы

(i-l)-x элементов задержки i -х регистров сдвига, KpoMBj первого подключены к соответствующим входам первого блока сумматоров по модулю два, выходы (k+l-i)-x элементов задержки i-x регистров сдвига, кроме последнего, подключены к соответствующим входам второго блока сумматоров по модулю два, выход первого блока сумматоров по модулю два соединен с информационным входом элемента задержки, выход которого соединен с (k+l J-M входом второго блока сумматоров по модулю два, тактовые : входы элемента задержки и блока элв ментов И объединены и подключены к тактовому входу передающей стороны системы, информационные входы блока элементов И подключены к соответствующим выходам буферного регистра, выходы блока элементов И являются соответствующими выходами передающей стороны системы, на приемной стороне системы введены пёрвьш и второй блоки памяти., блок элементов НЕ, второй блок элементов И-ИЛИ, элемент задержки, элемент ИЛИ-НЕ, группа изk + элементов И-НЕ, элемент И, сумматор и блок синхронизации, контрольный регистр выполнен на последовательно соединенных .2k+l элементах задержки, информационный вход первого из которых является информационным входом контрольного регистра, тактовые входы элементов задержки контрольного регистра объединены и являются тактовым входом контрольного регистра, 1-й регистр сдвига вьшолнен на посkледовательно соединенных (

элементах задержки, тактовые входы всех элементов задержки i -го регистра сдвига объединены и являются тактовым входом этого регистра сдвига, информационный вход первого регистра сдвига и выходы (i-l)-x элементов задержки 1 -х регистров сдвига кроме первого подключены к соответствующим входам первого сумматора по модулю два, выходы (k+l-i)-x элементов задержки i -х регистров сдвига, кроме (k+l)-ro, и информационный вход (К+1)о регистра сдвига подключены к соответствующим входам второго блока сумматоров по модулю два, первый выход блока синхронизации соединен с входом счетчика, первые выходы которого подключены к первым входам сумматора, выходы которого соединены с адресными входами первого блока памяти, выходы второго буферного регистра подключены к соответствующим первым информационным вхо- дам блоков элементов И-ИЛИ, второй выход блока синхронизации подключен к первым управляющим входам блоков элементов И-ИЛИ, третий и четвертьй выходы блока синхронизации соединены

с вторыми управляющими входами соответственно первого и второго блоков элементов Й-ШТИ, выходы которых подключены к информационным входам соответственно первого буферного регистра и первого блока памяти, пятый и

5

0

5

0

5

щестой выходы блока синхронизации соединены с первым и вторым управляющими входами первого блока памяти, выходы которого соединены с информа0 ционными входами третьего буферного регистра, выходы которого подключены к соответствующим вторым информационным входам первого блока элементов И-ИЛИ и первым входам третьего блока сумматоров по модулю два, выходы которого соединены с вторьти информационными входами второго блока элементов И-ИЛИд выход первого блока сумматоров по модулю два соединен с информационным входом элемента задержки, выход которого соединен с (k+2)-M входом второго блока сумматоров по модулю два, седьмой выход блока синхронизации подключен

5 к тактовым входам элемента задержки и контрольного регистра, информаци-. онный вход и выходы первого - k-го элементов задержки контрольного регистра подключены к первьм входам

соответственно (k+I)-ro - первого элементов И-НЕ группы, выходы (k+l)-ro - (2k+I)-ro элементов задержки контрольного регистра подключены к вторым входам соответственно первого - (k+l)-ro элементов И-НЕ

группы, выходы которых подключены JK

соответствующим входам элемента ИПИ- НЕ, соответств утащим входам блока элементов НЕ, установочным входам соответственно (k+1 )-го первого элементов задержки контрольного регистра и соответственно к установочным входам (k+2)-ro - (2k+l)-ro элементов задержки контрольного регистра и первому входу элемента И, выход (2k+l)-ro элемента задержки контрольного регистра соединен с вторым входом элемента И, выход которого

подключен к первому входу триггера, второй выход счетчика соединен с вторым входом триггера, восьмой и девятый выходы блока синхронизации подключены к управляющим входам со- ответственно третьего буферного регистра и второго блока памяти, выходы которого соединены с вторыми входами сумматора, выход элемента ИЛИ-НЕ подключен к первому входу бло- ка синхронизации, тактовый вход второго буферного регистра и второй вход блока синхронизации объединены и являются первым тактовым входом приемной стороны системы, третий, четвертый и пятьш входы блока синхронизации являются соответственно вторым тактовым, первым и вторым управляющими входами приемной стороны системы, третьи входы элементов И-НЕ группы являются соответствующими третьими управляющими входами приемной стороны системы.

2. Система по п.1, о т л и ч а ю- щ а я с я тем, что блок синхронизации выполнен на первом - восьмом од- новибраторах, первом и втором элементах задержки, первом - пятом элементах И и первом - пятом элементах ИЛИ первый вход третьего элемента И, первый и второй входы первого элемента ИЛИ и первый вход первого элемента И являются соответственно первым, вторым, третьим и четвертым входами блока синхронизации, первые входы второго и пятого элементов И объединены и являются пятым входом блока синхронизации, выход первого элемента ИЛИ подключен к входу первого одно- вибратора и является первым выходом блока синхронизации, выход первого

f

элемента И подключен к первому входу второго элемента ИЛИ и является вторым выходом блока синхронизации, , выход второго элемента И является третьим выходом блока синхронизации, выход третьего элемента И подключен к второму входу второго элемента ИЛИ и является четвертым выходом блока синхронизации, выход второго элемента ИЛИ является пятым выходом блока синхронизации, выход первого одно- вибратора подключен к входам второго и шестого одновибратороп и второму входу пятого элемента И, выход которого соединен с первым входом четвертого элемента ИЛИ, выход которого подключен к входу второго элемента задержки, выход второго одновибрато- ра подключен к входам третьего и пятого одновибратор.ов, вторым входам первого и второго и первому входу четвертого элементов И, выход третьего одновибратора подключен к входам четвертого и седьмого одновибрато- ров, второму входу четвертого и первому входу пятого элементов ИЛИ, выход четвертого одновибратора подключен к входу восьмого одновибратора и вторым входам третьего элемента И и пятого элемента ИЛИ, выходы пятого - восьмого одновибраторов подключены к входам третьего элемента ИЛИ, выход которого соединен с входом первого элемента задержки, выход которого подключен к второму входу четвертого элемента И и является шестым выходом блока синхронизации, выходы четвертого элемента И, второго элемента задержки и пятого элемента ИЛИ являются соответственно седьмым, восьмым и девятым выходами блока синхронизации.

дил1

фие.2 .

. направление

Формируемый KOHmpL разряд

6 (риг.4

2 диаг. поправление

Сформированные тнтр. /хгзряды

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ ЗАПИСИ-ВОСПРОИЗВЕДЕНИЯ МНОГОКАНАЛЬНОЙ ЦИФРОВОЙ ИНФОРМАЦИИ | 1995 |

|

RU2107953C1 |

| Декодер мажоритарного двоичного кода | 1988 |

|

SU1566488A1 |

| Декодирующее устройство | 1989 |

|

SU1681388A1 |

| Устройство обнаружения и исправления ошибок в кодах Рида-Соломона | 1986 |

|

SU1381719A1 |

| Устройство для исправления стираний | 1989 |

|

SU1633498A1 |

| Декодирующее устройство линейного циклического кода | 1990 |

|

SU1718386A1 |

| Устройство для контроля цифровых узлов | 1989 |

|

SU1645958A2 |

| Устройство контроля ошибок многоканальной аппаратуры магнитной записи | 1987 |

|

SU1529285A1 |

| Декодирующее устройство | 1988 |

|

SU1522415A1 |

| Пороговый декодер сверточного кода | 1989 |

|

SU1667264A1 |

Изобретение относится к автоматике и вычислительной технике. Его использование в системах передачи и обработки информации позволяет повысить достоверность передачи. Система содержит на передающей стороне буферный регистр, регистр сдвига и блоки сумматоров по модулю два, на приемной стороне содержит буферные регистры, регистры сдвига, блоки сумматоров по модулю два, блок элементов И-ИЛИ, счетчик, контрольный регистр и триггер. Введение на передающей стороне элемента задержки и блока элементов И и на приемной стороне блока элементов И-1ШИ, блоков памяти, блока элементов НЕ, сумматора, элемента задержки, элемента И, элемента ИЛИ-НЕ, элементов И-НЕ и блока синхронизации обеспечивает.стопроцентную коррекцию массива информации ИЗ п (k+I)-разрядных слов. 1 з.п. ф-лы, 6 ил. (Л

tзкъ«o ifx:з u 5в э::5 г

Составитель О. Ревинский

Редактор М, Циткина

Техред М.Ходанич

Заказ 1903/56 . Тираж 902Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д,4/5

Производственно-полиграфическое П1)едпрнятие, г. Ужгород, ул. Проектная, 4

Корректоре. Черни

| Контрольное устройство приема информации | 1972 |

|

SU469130A1 |

| Топка с несколькими решетками для твердого топлива | 1918 |

|

SU8A1 |

| Электроника, 1981, т.54, № 9, с.40-47, рис.5-8, | |||

Авторы

Даты

1987-05-15—Публикация

1985-08-06—Подача