113399002

Изобретение относится к автоматике Устройство работает следующим оби вычислительной технике и может бытьразом.

использовано в системах обработки В исходном состоянии регистр 1

цифровой информации, сброшен с входа 9, на вход записи

Цель изобретения состоит в упроще-регистра 1 сдвига подается разрешаюнии устройства.щий потенциал (сигнал), и в регистр 1

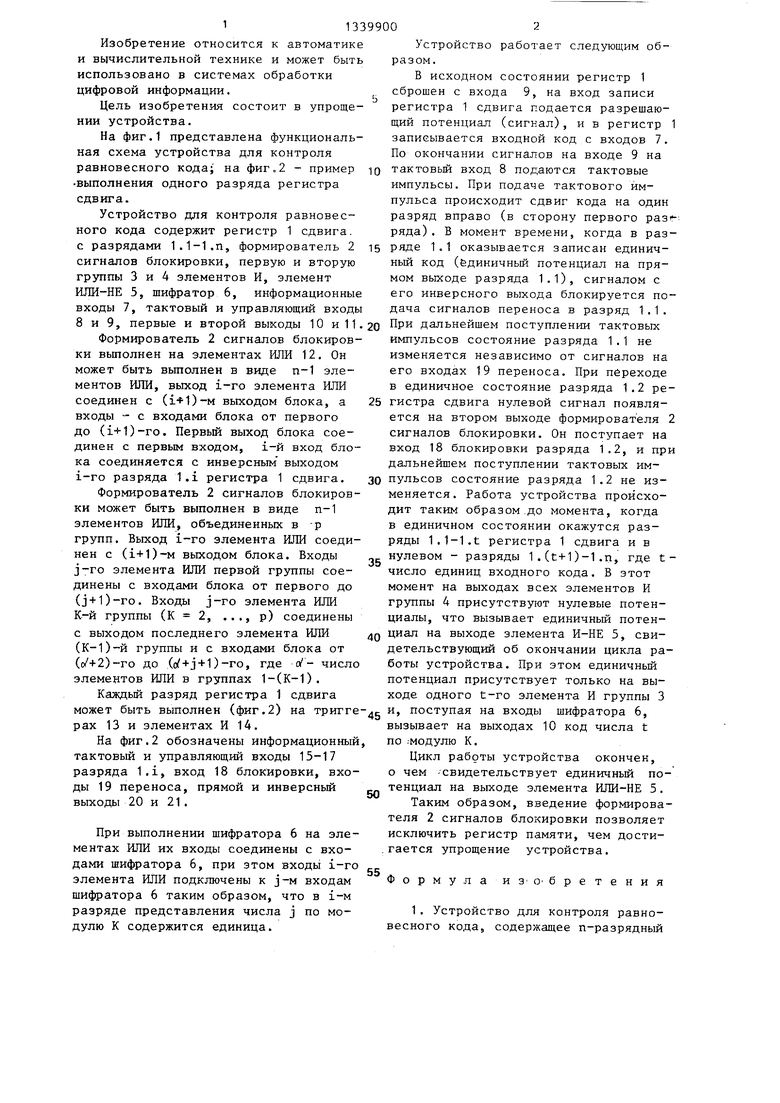

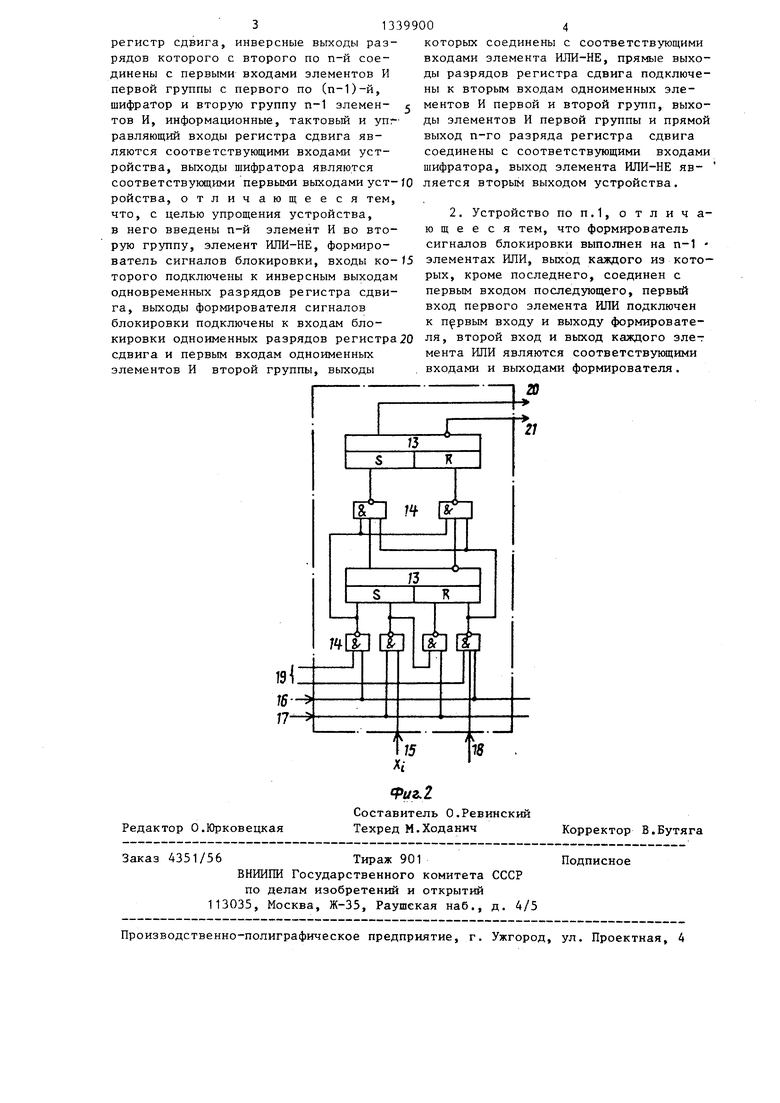

На фиг.1 представлена функциональ-записывается входной код с входов 7.

ная схема устройства для контроляПо окончании сигналов на входе 9 на

равновесного кода; на фиг.2 - пример Qтактовьй вход 8 подаются тактовые

выполнения одного разряда регистраимпульсы. При подаче тактового имсдвига.пульса происходит сдвиг кода на один

Устройство для контроля равновес-разряд вправо (в сторону первого раз

ного кода содержит регистр 1 сдвига.ряда). В момент времени, когда в разс разрядами 1.1-l.n, формирователь 2 igряде 1.1 оказывается записан единичсигналов блокировки, первую и вторуюный код (ЕДИНИЧНЫЙ потенциал на прягруппы 3 и 4 элементов И, элементмом выходе разряда 1.1), сигналом с

ИЛИ-НЕ 5, шифратор 6, информационныеего инверсного выхода блокируется повходы 7, тактовый и управляющий входыдача сигналов переноса в разряд 1.1.

8 и 9, первые и второй выходы 10 и 11, 20При дальнейшем поступлении тактовых

Формирователь 2 сигналов блокиров-импульсов состояние разряда 1.1 не ки выполнен на элементах ИЛИ 12. Онизменяется независимо от сигналов на может быть вьтолнен в виде п-1 эле-его входах 19 переноса. При переходе ментов ИЛИ, выход i-ro элемента РШИв единичное состояние разряда 1.2 ре- соединен с ()-м выходом блока, а 25гистра сдвига нулевой сигнал появля- входы - с входами блока от первогоется на втором выходе формирователя 2 до (1+1)-го. Первый выход блока сое-сигналов блокировки. Он поступает на динен с первым входом, i-й вход бло-вход 18 блокировки разряда 1.2, и при ка соединяется с инверсным выходомдальнейшем поступлении тактовых им- 1-го разряда 1.1 регистра 1 сдвига. зопульсов состояние разряда 1.2 не изФормнрователь 2 сигналов блокиров-меняется. Работа устройства происхо- ки может быть выполнен в виде п-1дит таким образом ,до момента, когда элементов ИЛИ, объединенных в -рв единичном состоянии окажутся раз- групп. Выход 1-го элемента ИЛИ соеди-ряды 1.1-1.t регистра 1 сдвига и в нен с (1+1)-м выходом блока. Входы „ нулевом - разряды 1.(t+1)-1.n, где t- j-ro элемента ИЖ первой группы сое-число единиц входного кода. В этот динены с входами блока от первого домомент на выходах всех элементов И (j+1)-ro. Входы j-ro элемента ИЛИгруппы 4 присутствуют нулевые потен- К-й группы (К 2, ..., р) соединеныциалы, что вызывает единичный потен- с выходом последнего элемента ИЛИ 40 выходе элемента И-НЕ 5, сви- (К-1)-й группы и с входами блока отдетельствующий об окончании цикла ра- ((/+2)-го до ((/+j + 1)-ro, где -о/ - числоботы устройства. При этом единичньш элементов ИЛИ в группах 1-(К-1).потенциал присутствует только на выКаждьй разряд регистра 1 сдвигаходе одного t-ro элемента И группы 3

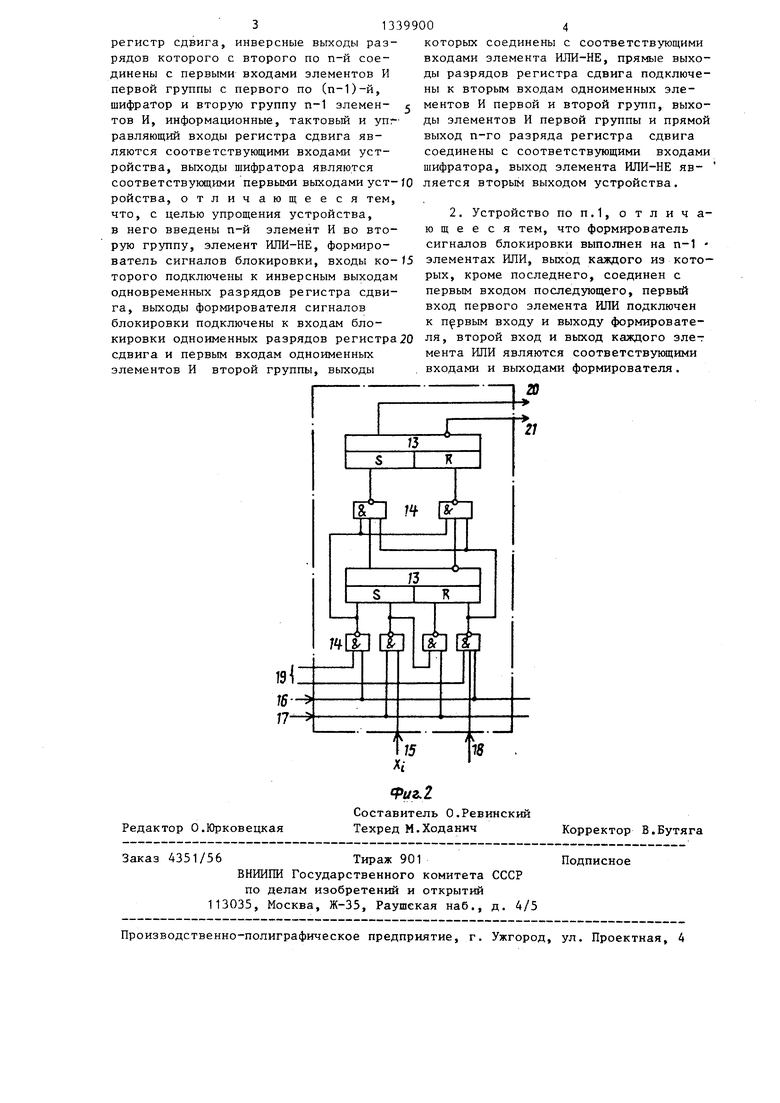

может быть выполнен (фиг.2) на тригге- gи, поступая на входы шифратора 6,

pax 13 и элементах И 14.вызывает на выходах 10 код числа t

На фиг.2 обозначены информационный,по :модулю К.

тактовый и управляющий входы 15-17 Цикл работы устройства окончен, разряда 1.1, вход 18 блокировки, вхо-о чем -свидетельствует единичный поды 19 переноса, прямой и инверсньй тенциал на выходе элемента ИЛИ-НЕ 5. выходы 20 и 21.Таким образом, введение формирователя 2 сигналов блокировки позволяет

При выполнении щифратора 6 на эле-исключить регистр памяти, чем достиментах ИЛИ их входы соединены с вхо-.гается упрощение устройства, дами шифратора 6, при этом входы 1-го

элемента РШИ подключены к j-м входамФормулаиз О бретения шифратора 6 таким образом, что в 1-м

разряде представления числа j по мо- 1 . Устройство для контроля равнодулю К содержится единица.весного кода, содержащее п-разрядный

которых соединены с соответствующ входами элемента ИЛИ-НЕ, прямые в ды разрядов регистра сдвига подкл ны к вторым входам одноименных эл ментов И первой и второй групп, в ды элементов И первой группы и пр выход п-го разряда регистра сдви соединены с соответствующими вхо шифратора, выход элемента ИЛИ-НЕ

регистр сдвига, инверсные выходы разрядов которого с второго по п-й соединены с первыми входами элементов И первой группы с первого по (п-1)-й, шифратор и вторую группу п-1 элементов И, информационные, тактовый и упг равляющий входы регистра сдвига являются соответствующими входами устройства, выходы шифратора являются соответствукхцими первыми выходами уст-JO ляется вторым выходом устройства, ройства, отличающееся тем, что, с целью упрощения устройства, в него введены п-й элемент И во вторую группу, элемент ИЛИ-НЕ, формирователь сигналов блокировки, входы ко-J5 торого подключены к инверсным выходам одновременных разрядов регистра сдвига, выходы формирователя сигналов блокировки подключены к входам блокировки одноименных разрядов регистра 20 сдвига и первым входам одноименных элементов И второй группы, выходы

2. Устройство по п.1, о т л и ю щ е е с я тем, что формировател сигналов блокировки выполнен на п элементах ИЛИ, выход каждого из к рых, кроме последнего, соединен с первым входом последующего, первь вход первого элемента ИЛИ подключ к первым входу и выходу формирова ля, второй вход и выход каждого э мента ИЛИ являются соответствующи входами и выходами формирователя.

Редактор О.Юрковецкая

Заказ 4351/56Тираж 901

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

которых соединены с соответствующими входами элемента ИЛИ-НЕ, прямые выходы разрядов регистра сдвига подключены к вторым входам одноименных элементов И первой и второй групп, выходы элементов И первой группы и прямой выход п-го разряда регистра сдвига соединены с соответствующими входами шифратора, выход элемента ИЛИ-НЕ яв-

ляется вторым выходом устройства,

ляется вторым выходом устройства,

2. Устройство по п.1, о т л и ч а- ю щ е е с я тем, что формирователь сигналов блокировки выполнен на п-1 элементах ИЛИ, выход каждого из которых, кроме последнего, соединен с первым входом последующего, первьй вход первого элемента ИЛИ подключен к первым входу и выходу формирователя, второй вход и выход каждого элет мента ИЛИ являются соответствующими входами и выходами формирователя.

х,- fuz.Z

Составитель О.Ревинский Техред М.Ходаннч

Подписное

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для организации очереди | 1986 |

|

SU1434431A2 |

| Устройство для поиска информации | 1989 |

|

SU1686464A1 |

| Устройство переменного приоритета | 1983 |

|

SU1151964A1 |

| Устройство ассоциативного кодирования и объемного сжатия информации | 1987 |

|

SU1441484A1 |

| Устройство для распределения групповых заявок по процессорам | 1985 |

|

SU1254485A1 |

| Устройство для организации доступа к ресурсам | 1988 |

|

SU1608663A1 |

| Устройство для организации очереди | 1987 |

|

SU1479930A2 |

| Устройство для упорядочивания @ чисел | 1986 |

|

SU1339548A1 |

| Устройство для управления реконфигурацией резервированной вычислительной систем | 1989 |

|

SU1718398A1 |

| Многоканальное устройство приоритета для распределения заявок по процессорам | 1985 |

|

SU1327105A1 |

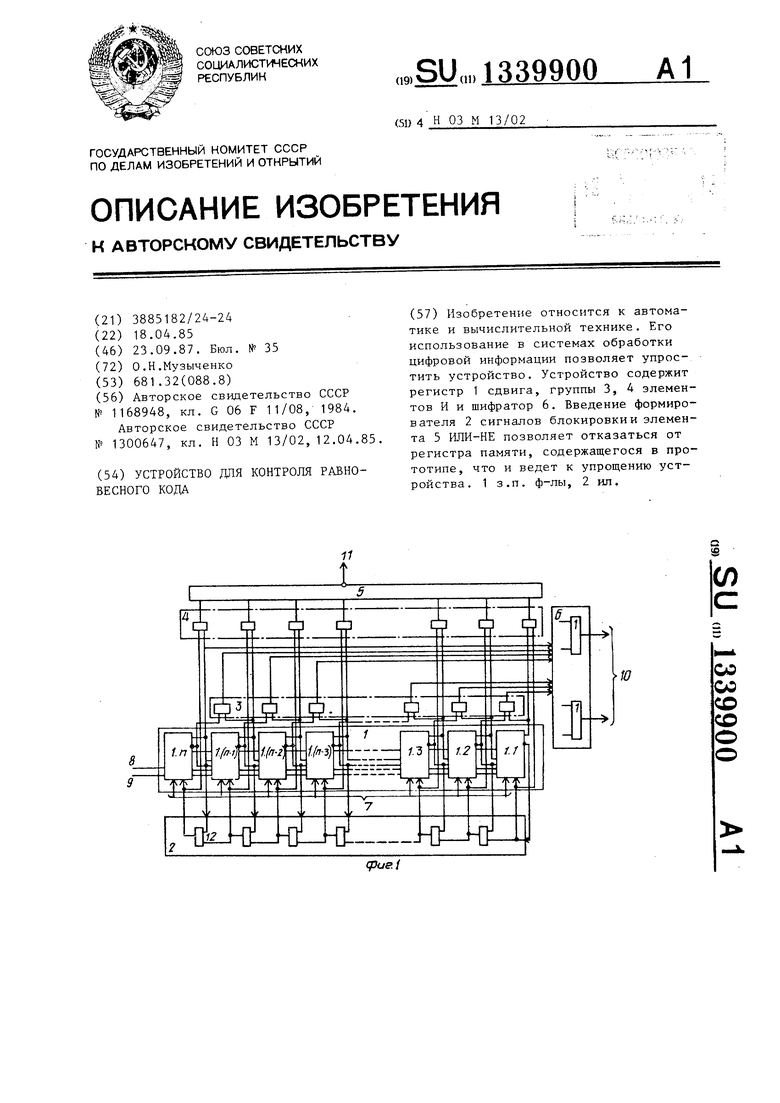

Изобретение относится к автоматике и вычислительной технике. Его использование в системах обработки цифровой информации позволяет упростить устройство. Устройство содержит регистр 1 сдвига, группы 3, 4 элементов И и шифратор 6. Введение формирователя 2 сигналов блокировки и элемента 5 ИЛИ-НЕ позволяет отказаться от регистра памяти, содержащегося в прототипе, что и ведет к упрощению устройства. 1 з.п. ф-лы, 2 ил. Ю со со со со

| Устройство для обнаружения ошибок в параллельном @ -разрядном коде | 1984 |

|

SU1168948A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для обнаружения ошибок равновесного кода | 1985 |

|

SU1300647A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1987-09-23—Публикация

1985-04-18—Подача