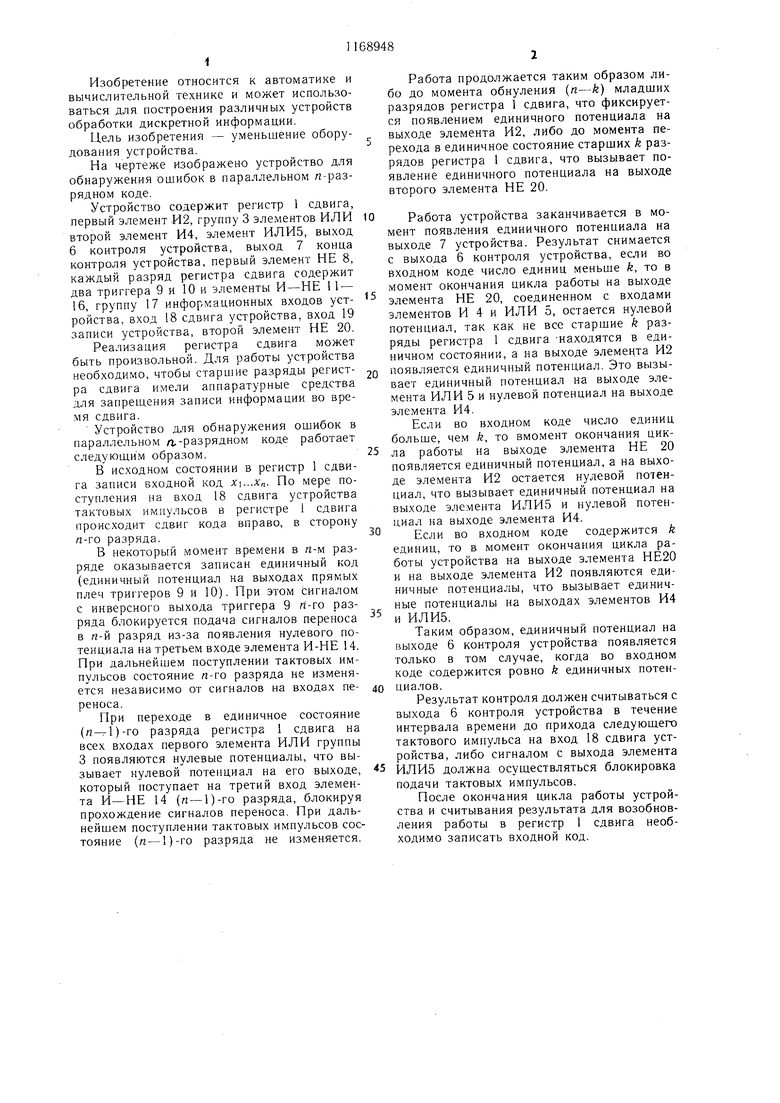

Изобретение относится к автоматике и вычислительной технике и может использоваться для построения различных устройств обработки дискретной информации. Цель изобретения - уменьшение оборудования устройства. На чертеже изображено устройство для обнаружения ошибок в параллельном л-разрядном коде. Устройство содержит регистр 1 сдвига, первый элемент .И2, группу 3 элементов ИЛИ второй элемент И4, элемент ИЛИ5, выход 6 контроля устройства, выход 7 конца контроля устройства, первый элемент НЕ 8, каждый разряд регистра сдвига содержит два триггера 9 и 10 и элементы И-НЕ 11 - 16, группу 17 информационных входов устройства, вход 18 сдвига устройства, вход 19 записи устройства, второй элемент НЕ 20. Реализация регистра сдвига может быть произвольной. Для работы устройства необходимо, чтобы старшие разряды регистра сдвига имели аппаратурные средства для запрещения записи информации во время сдвига. Устройство для обнаружения ошибок в параллельном /г-разрядном коде работает следуюш.им образом. В исходном состоянии в регистр 1 сдвига записи входной код х...Хп. По мере поступления на вход 18 сдвига устройства тактовых импульсов в регистре 1 сдвига происходит сдвиг кода вправо, в сторону п-го разряда. В некоторый момент времени в п-м разряде оказывается записан единичный код (единичный потенциал на выходах прямых плеч триггеров 9 и 10). При этом сигналом с инверсного выхода триггера 9 п-го разряда блокируется подача сигналов переноса в п-й разряд из-за появления нулевого потенциала на третьем входе элемента И-НЕ 4. При дальнейшем поступлении тактовых импульсов состояние rt-ro разряда не изменяется независимо от сигналов на входах переноса. При переходе в единичное состояние (n-rl)-ro разряда регистра 1 сдвига на всех входах первого элемента ИЛИ группы 3 появляются нулевые потенциалы, что вызывает нулевой потенциал на его выходе, который поступает на третий вход элемента И-НЕ 14 (п-1)-го разряда, блокируя прохождение сигналов переноса. При дальнейшем поступлении тактовых импульсов состояние (п-1)-го разряда не изменяется. Работа продолжается таким образом либо до момента обнуления (п-k) младших разрядов регистра 1 сдвига, что фиксируется появлением единичного потенциала на выходе элемента И2, либо до момента перехода в единичное состояние старших k разрядов регистра 1 сдвига, что вызывает появление единичного потенциала на выходе второго элемента НЕ 20. Работа устройства заканчивается в момент появления единичного потенциала на выходе 7 устройства. Результат снимается с выхода 6 контроля устройства, если во входном коде число единиц меньше k, то в момент окончания цикла работы на выходе элемента НЕ 20, соединенном с входами элементов И 4 и ИЛИ 5, остается нулевой потенциал, так как не все старшие k разряды регистра 1 сдвига -находятся в единичном состоянии, а на выходе элемента И2 появляется единичный потенциал. Это вызывает единичный потенциал на выходе элемента ИЛИ 5 и нулевой потенциал на выходе элемента И4. Если во входном коде число единиц больше, чем /г, то вмомент окончания цикла работы на выходе элемента НЕ 20 появляется единичный потенциал, а на выходе элемента И2 остается нулевой потенциал, что вызывает единичный потенциал на выходе элемента ИЛИ5 и нулевой потенциал на выходе элемента И4. Если во входном коде содержится k единиц, то в момент окончания цикла работы устройства на выходе элемента НЕ20 и на выходе элемента И2 появляются единичные потенциалы, что вызывает единичные потенциалы на выходах элементов И4 и ИЛИ5. Таким образом, единичный потенциал на выходе 6 контроля устройства появляется только в том случае, когда во входном коде содержится ровно k единичных потенциалов. Результат контроля должен считываться с выхода 6 контроля устройства в течение интервала времени до прихода следуюшего тактового импульса на вход 18 сдвига устройства, либо сигналом с выхода элемента ИЛИ5 должна осуществляться блокировка подачи тактовых импульсов. После окончания цикла работы устройства и считывания результата для возобновления работы в регистр 1 сдвига необходимо записать входной код.

| название | год | авторы | номер документа |

|---|---|---|---|

| Сумматор @ частотно-импульсных сигналов | 1982 |

|

SU1156068A1 |

| Пороговое устройство (его варианты) | 1984 |

|

SU1352449A1 |

| СПОСОБЫ ВЫПОЛНЕНИЯ ЭЛЕМЕНТАРНЫХ ВЫЧИСЛИТЕЛЬНЫХ ОПЕРАЦИЙ (ЭВО) И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2012 |

|

RU2505850C2 |

| Устройство для обнаружения ошибок в параллельном п-разрядном коде | 1986 |

|

SU1325482A2 |

| Устройство для перебора сочетаний | 1986 |

|

SU1370655A1 |

| Селектор импульсов по длительности | 1980 |

|

SU911718A2 |

| Устройство для сортировки чисел | 1984 |

|

SU1223221A1 |

| СЧЕТЧИК ИМПУЛЬСОВ (СИ) | 2015 |

|

RU2579524C1 |

| Формирователь разновесных кодов | 1985 |

|

SU1297031A1 |

| Устройство для моделирования сетевых графов | 1982 |

|

SU1065858A1 |

УСТРОЙСТВО ДЛЯ ОБНАРУЖЕНИЯ ОШИБОК В ПАРАЛЛЕЛЬНОМ J /-PAЗPЯДHOM КОДЕ, содержащее первый элемент НЕ, элемент ИЛИ, два элемента И, регистр сдвига, каждый разряд которого содержит два триггера и шесть элементов И-НЕ, причем первые входы первого и второго элементов И-НЕ всех разрядов регистра сдвига объединены и являются входом сдвига устройства, первые входы третьего и четвертого элементов И-НЕ всех разрядов регистра сдвига объединены и являются входом записи устройства, в каждом разряде регистра сдвига выходы первого и третьего элементов И-НЕ соединены соответствующими единичными входами первого триггера, прямой и инверсный выходы которого соединены соответственно с первыми входами соответственно пятого и шестого элементов И-НЕ, выходы которых соединены соответственно с единичным и нулевым входами второго триггера, вторые входы пятого и шестого элементов И-НЕ всех разрядов регистра сдвига объединены и через первый элемент НЕ соединены с входом сдвига устройства, в каждом разряде регистра сдвига выход третьего элемента И- НЕ соединен с вторым входом четвертого элемента И-НЕ, вторые входы первого и второго элементов И-НЕ каждого г-го разряда регистра сдвига соединены соответственно с прямым и инверсным выходами второго триггера (i--l)-ro разряда регистра сдвига (), вторые входы первого и второго элементов И-НЕ первого разряда регистра сдвига соединены с шинами нулевого и единичного потенциалов соответственно, в каждом разряде регистра сдвига выходы второго и четвертого элементов И- НЕ соединены с соответствующими входами первого триггера, вторые входы третьих элементов И-НЕ всех разрядов регистра сдвига образуют группу информационных входов устройства, инверсные выходы вторых триггеров (n-k) младших разрядов регистра сдвига (k - число единичных символов в коде k из п) соединены с входами первого элемента И, выход которого (О соединен с первыми входами второго элемен(Л та И и элемента ИЛИ, выходы которых являются соответственно контрольным выходом и выходом конца контроля устройства, отличающееся тем, что, с целью уменьшения оборудования устройства, оно содержит группу элементов ИЛИ и второй элемент НЕ, причем инверсный выход второго триггера п-го разряда регистра сдвига соединен с третьим входом второго элемента И-НЕ О5 п-го разряда регистра сдвига и первым входом первого элемента ИЛИ группы, выход сх со каждого /-ГО элемента ИЛИ группы ( 4.К-2) соединен с первым входом (j+l)-ro элемента ИЛИ группы, выход (к-1)-го эле00 мента ИЛИ группы через второй элемент НЕ соединен с вторыми входами второго элемента И и элемента ИЛИ, инверсный выход второго триггера и третий вход второго элемента И-НЕ каждого (п-J)-ro разряда регистра сдвига () соединены соответственно с вторым входом и выходом t-ro элемента ИЛИ группы.

| Устройство для контроля параллельного двоичного кода на четность | 1974 |

|

SU530332A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для обнаружения ошибок в параллельном @ -разрядном коде | 1982 |

|

SU1096651A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1985-07-23—Публикация

1984-02-28—Подача