(Л

4; IND

оо

Од

ом;

сдвига, счетчик 9, мультиплексоры 10-12, блок 13 анализа и контроля, элементы И 14-17, элементы НЕ 18,19, триггер 20, элемент И 21, элементы ИЛИ 22, 23, элементы И 24-26, входы 27-29 тактирующих сигналов, входы 30-33 цифр множителя и множимого.

выходы 34, 35 цифр результата, выход 36 сигнала ошибки. Устройство функционирует в избыточной двоичной системе счисления с цифрами . Чередование цифр результата выполняется по строгим правилам, 2 ил.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для умножения в избыточной двоичной системе | 1982 |

|

SU1059568A1 |

| Устройство для умножения | 1985 |

|

SU1305667A1 |

| Устройство для умножения | 1985 |

|

SU1278838A1 |

| Устройство для умножения | 1985 |

|

SU1254473A1 |

| Арифметическое устройство | 1988 |

|

SU1578708A1 |

| Устройство для выполнения операций умножения и деления | 1980 |

|

SU955038A1 |

| Устройство для умножения | 1975 |

|

SU640292A1 |

| Устройство для умножения | 1976 |

|

SU603989A1 |

| Арифметическое устройство | 1977 |

|

SU669353A1 |

| ПРОГРАММИРУЕМЫЙ ЦИФРОВОЙ ФИЛЬТР | 1994 |

|

RU2097828C1 |

Изобретение относится к вычислительной технике и может быть использовано в цифровых вычислительных машинах и устройствах. Цель изобретения повышение достоверности работы за. спет обеспечения функционального контроля устройства. Устройство содержит сумматор 1 сомножителей, ре- . гистр 2 множимого, регистр 3 результата, сумматор 4 результата, группу 5 мультиплексоров,регистр 6 множителя, регистр 7 константы, регистр 8

Изобретение относится к вычислительной технике и может быть использовано в цифровых вычислительных машинах и устройствах.

Цель изобретения - повьппение дос- товерности работы за счет обеспечения функционального контроля устройства умножения.

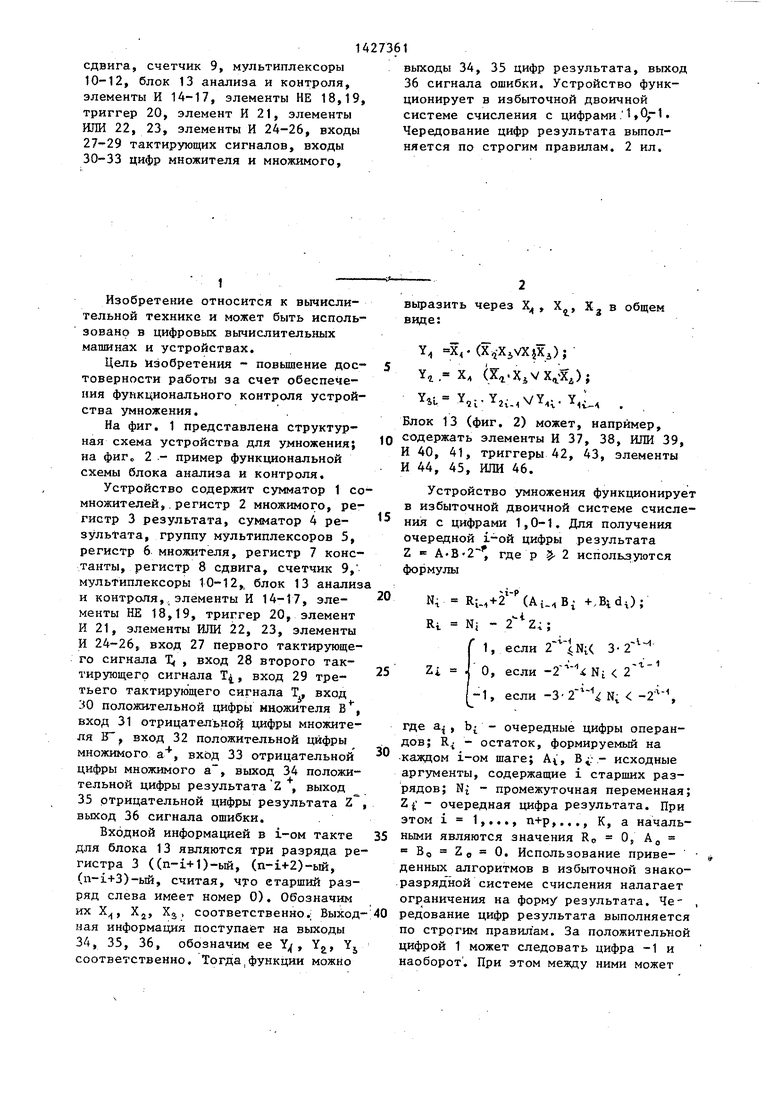

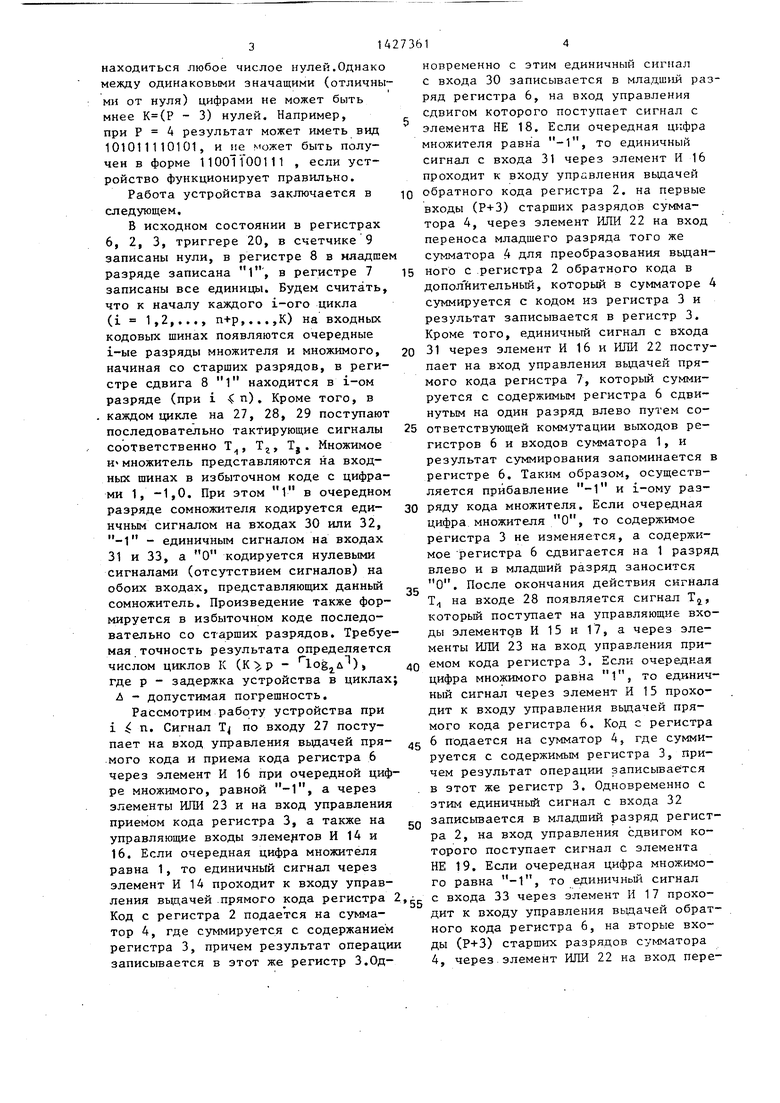

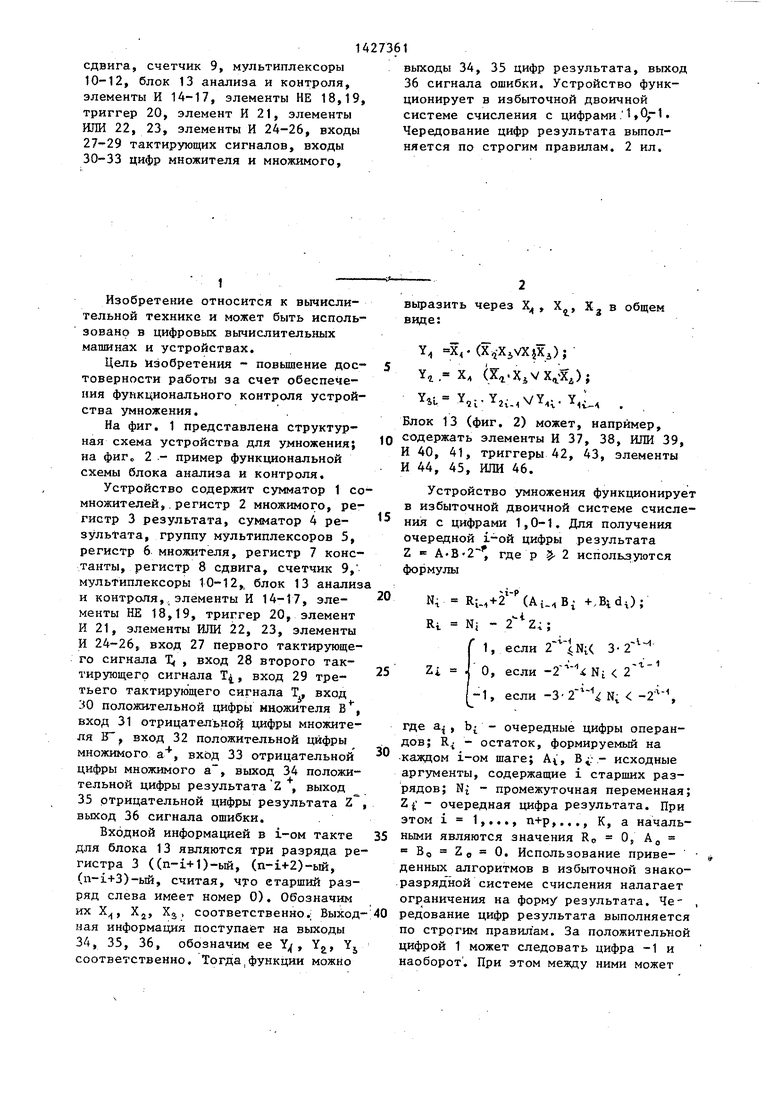

На фиг. 1 представлена структурная схема устройства для умножения; на фиго 2 - пример функциональной схемы блока анализа и контроля.

Устройство содержит сумматор 1 сомножителей, . регистр 2 множимого, регистр 3 результата, сумматор 4 результата, группу мультиплексоров 5, регистр 6 множителя, регистр 7 константы, регистр 8 сдвига, счетчик 9, мультиплексоры 10-12,, блок 13 анализ и контроля,. элементы И 14-17, эле- менты НЕ 18,19, триггер 20, элемент И 21, элементы ИЛИ 22, 23, элементы И 24-26, вход 27 первого тактирующего сигнала 1 , вход 28 второго тактирующего сигнала Т, вход 29 третьего тактирующего сигнала Т, вход 30 положительной цифры множителя В, вход 31 отрицательно цифры множителя В вход 32 положительной цифры множимого , вхьд 33 отрицательной цифры множимого а, выход 34 положительной цифры результата Z , выход 35 отрицательной цифры результата Z выход 36 сигнала ошибки.

Входной информацией в i-ом такте для блока 13 являются три разряда регистра 3 ((п-1+1)-ьш, (п-1+2)-ый, (п-1+3)-ый, считая, что старший разряд слева имеет номер 0). Обозначим их Х, Xj, Xj , соответственно.; Выход ная информахщя поступает на выходы 34, 35, 36, обозначим ее Y, Y, Yj соответственно. Тогда функции можно

выразить через Х , Х, Х в общем виде:

Y Х. (X -XjVXjXi); Y,t. X, a-i-XiVX i); Y,i. Y,.,Y2,.,VY,..Y,;, .

Блок 13 (фиг. 2) может, например, содержать элементы И 37, 38, ИЛИ 39, И 40, 41, триггеры 42, 43, элементы И 44, 45, ИЛИ 46.

Устройство умножения функционирует в избыточной двоичной системе счисления с цифрами 1,0-1. Для получения очередной i-ой цифры результата Z А В где р 2 используются формулы

N, ., Bi -b.BidO; Ri Nj -

Zi .

1, если 0, если

-1, если -3-2 N, -2

где a, b - очередные цифры операндов; R - остаток, формируемый на каждом i-oM шаге; А, исходные аргументы, содержащие i старших разрядов; Nj - промежуточная переменная; Zj, - очередная цифра результата. При этом i 1,..., п+р,.... К, а начальными являются значения RO О, Ад BO Zo 0. Использование приведенных алгоритмов в избыточной знако- разрядной системе счисления налагает ограничения на форму результата. Че редование цифр результата выполняется по строгим правилам. За положитель юй цифрой 1 может следовать цифра -1 и наоборот. При этом между ними может

3142736

находиться любое числое нулей.Однако между одинаковыми значащими (отличными от нуля) цифрами не может быть мнее К(Р - 3) нулей. Например, при Р 4 результат может иметь вид 101011110101, и lie может быть получен в форме 11 oof 100111 , если устройство функционирует правильно.

Работа устройства заключается в IQ следующем,

В исходном состоянии в регистрах 6, 2, 3, триггере 20, в счетчике 9 записаны нули, в регистре 8 в младшем

разряде записана 1 , в регистре 7 записаны все единицы. Будем считать, что к началу каждого i-oro цикла (i 1,2,..,, п+р,...,К) на входных кодовых шинах появляются очередные i-ые разряды множителя и множимого, начиная со старших разрядов, в регистре сдвига 8 1 находится в i-ом разряде (при i - п), Кроме того, в каждом цикле на 27, 28, 29 поступают последовательно тактирующие сигналы соответственно Т, Т, Т,. Множимое и множитель представляются на входных шинах в избыточном коде с цифрами 1, -1,0. При этом 1 в очередном разряде сомножителя кодируется еди- нчным сигналом на входах 30 или 32, -1 - единичным сигналом на входах 31 и 33, а О кодируется нулевыми сигналами (отсутствием сигналов) на обоих входах, представляющих данный сомножитель. Произведение также формируется в избыточном коде последовательно со старших разрядов. Требуемая точность результата определяется числом циклов К ( - й), где р - задержка устройства в циклах Д - допустимая погрешность.

Рассмотрим работу устройства при i п. Сигнал Т по входу 27 поступает на вход управления вьщачей пря- мого кода и приема кода регистра 6 через элемент И 16 при очередной цифре множимого, равной -1, а через элементы ИЛИ 23 и на вход управления приемом кода регистра 3, а также на управляющие входы злeмe тoв И 14 и 16. Если очередная цифра множителя равна 1, то единичньй сигнал через элемент И 14 проходит к входу управления вьиачей .прямого кода регистра Код с регистра 2 подается на сумматор 4, где суммируется с содержанием регистра 3, причем результат операци записывается в этот же регистр З.Од-

новременно с этим единичный сигнал с входа 30 записывается в младший разряд регистра 6, на вход управления сдвигом которого поступает сигнал с элемента НЕ 18. Если очередная цифра множителя равна -1, то единичный

сигнал с входа 31 через элемент И 16 проходит к входу управления выдачей обратного кода регистра 2. на первые входы (Р+3) старших разрядов сумматора 4, через элемент ИЛИ 22 на вход переноса младшего разряда того же сумматора 4 для преобразования вьщан- ного с регистра 2 обратного кода в допол нительный, который в сумматоре 4 суммируется с кодом из регистра 3 и результат записывается в регистр 3, Кроме того, единичный сигнал с входа 31 через элемент И 16 и ИЛИ 22 поступает на вход управления вьщачей прямого кода регистра 7, которьш суммируется с содержимым регистра 6 сдвинутым на один разряд влево путем соответствующей коммутации выходов регистров 6 и входов сумматора 1, и результат суммирования запоминается в регистре 6, Таким образом, осуществляется прибавление -1 и i-ому разряду кода множителя. Если очередная цифра множителя О, то содержимое регистра 3 не изменяется, а содержимое регистра 6 сдвигается на 1 разряд влево и в младший разряд заносится О. После окончания действия сигнала Т на входе 28 появляется сигнал Тд,, который поступает на управляющие входы элементов И 15 и 17, а через элементы ИЛИ 23 на вход управления приемом кода регистра 3. Если очередная цифра множимого равна 1, то единичный сигнал через элемент И 15 проходит к входу управления вьщачей прямого кода регистра 6. Код с регистра 6 подается на сумматор 4, где суммируется с содержимым регистра 3, причем результат операции записьшается в этот же регистр 3. Одновременно с этим единичньй сигнал с входа 32 записьшается в младший разряд регистра 2, на вход управления сдвигом которого поступает сигнал с элемента НЕ 19. Если очередная цифра множимого равна -1, то единичньш сигнал с входа 33 через элемент И 17 проходит к входу управления вьщачей обратного кода регистра 6, на вторые входы (Р+3) старших разрядов сумматора 4, через.элемент ИЛИ 22 на вход переноса младших разрядов того же сум- матера для преобразования выданного с регистра 6 обратного кода в дополнительный. Этот код суммируется в сумматоре 4 с кодом из регистра 3 и результат записьгоается в регистр 3. Кроме того, единичный сигнал с,входа 31 через э пементыИ 17 и ИЛИ 22 поступает на вход управления выдачей пря- мого кода регистра 7, который суммируется с содержимым регистра 2, сдвинутым на один разряд влево путем соответствующей коммутации выходов регистра 2 и входов .сумматора 1, и результат суммирования запоминается в регистр 2, Такрщ образом, осуществляется прибавление -1 к i-ому разряду кода множимого.. Если очередная цифра множимого О, то содержимое регистра 3 не изменяется, а содержимое регистра 2 сдвигается на один разряд влево и в младший разряд заносится О. При наличии сигналов Т

или Tij группа мультиплексоров 5 пропускает, информацию с выходов сумматора 4 на входы регистра 3 без преобразования. По тактирующему сигналу Т происходит сдвиг на один разряд влево кода в регистре 8 и код на i-oM-шаге будет равен весу 1

После окончания действия сигнала T,j на входе 29 появляется сигнал Tj , которьй поступает на управляющие входы группы мультиплексоров 5 и код с выходов сумматора 4 поступает на входы регистра формирования результата 3 со сдвигом на два разряда влево. Сигнал Tj через элементы И 21 и ИЛИ 23 поступает на вход управления приемами кода регистра 3, а также через элемент И 21 поступает на вход счетчика 9 и на тактовый вход блока 13.

Код со счетчика 9 поступает на управляющие входы мультиплексоров 10, 11, 12, которые пропускают в блок 13 на i-oM такте (п-1+1)-ый, (п-1+2)-ый, (п-1+3)-ьш разряды регистра 3 соответственно. Блок 13 вьщает на выходы 35,34 значения очередной цифры результата. Если Z 1, то единичный сигнал через элемент И 25 проходит к входу- уЛравления выдачей прямого кода регистра 8, код с весом 1 для i-oro такта поступает на вход сумматора 4, где суммируется с содержанием .регистра 3, результат записьгоается в тот же регист

5 0

5

0

5

5

5

, ТО работа устройства изменяется при появлении сигналов и Tj., Триггер 20 устанавливается

при появлений сигнала Tj еди3 со сдвигом на два разряда влево с помощью группы му 1ьтиплексорОБ 3. Если Z J 1, то единичный си..гнал через элемент И 26 проходит к входу управления выдачей обратного кода регистра 8, к входу переноса младшего разряда сумматора 4 через элемент ИЛИ 22 для вычитания из кода регистра 3 в i-o-M такте 1. Результат с сумматора 4 через . груТппу мультиплексоров 5 записывается со сдвигом на два разряда влево в регистр 3. Если очередная цифра результата О,то код с регистра 3 проходит через сумматор 4 и группу мультиплексоров 5, сдвигаясь на два разряда влево.

Если i п. не Т,

в 1 и

:ничный сигнал через элемент И 24 пос- гупает на вход управления сдвигом регистра 3, причем в первый разряд регистра 3 сдвиг происходит из третьего разряда того же регистра 3. Таким образом, осуществляется нахождение остатка Ri. Так как код на выходе счетчика 9 не изменяется, то мультиплексоры 10, 11, 12 будут пропускать в блок 13 три старших разряда. На выходе блока 13 будут формироваться очередные разряды произведения.

Блок 13 работает следующим образом, В .i-oM TaKfe элементы И 37, 38-40, 41 и ИЛИ 39 формирует, очередную цифру результата по следующему правилу. Цифра результата равна О, 1, если содержимое трех анализируе- 0 мых разрядов сумматора 4 равно 001 или 010, -1, если содержимое трех старших разрядов равно 110 или 101, О - в остальных случаях. Цифры результата поступают на выходы 34, 35. Цепочка: триггер 42, элемент И 44 обнаруживает комбинацию цифр 11 в коде результата. Цепочкаг триггер 43, элемент И 45 обнаруживает комбинацию ТТ. В случае обнаружения Q ошибочной комбинации (11 или IT) сигналы с элементов И 44, 45 поступают на элемент ИЛИ 46, выход которого является выходом 36 ошибки.

В устройстве происходит обнаружение констатных неисправностей (1 или О) в любом блоке, участвующем в формировании результата. Отказы 6 схеме контроля и схемах управления также будут зафиксированы, так как

нарушится раэрешенньв порядок следования цифр результата.

вход которого соединен с входом счетчика и с выходом четвертого элемента И, первый вход которого соединен с инверсным выходом триггера, прямой выход которого, соединен с первым Устройство для умножения, содержа- входом пятого элемента И, выход котоФормула и.зобретени

щее регистр множимого, регистр мно-. жителя, сумматор результата, сумматор

рого соединен с входом управления сдвигом регистра результата, выходы

рого соединен с входом управления сдвигом регистра результата, выходы

сомножителей, регистр результата, ю регистр сдвига, элементы И, причем выходы разрядов регистров множимого и множителя подключены соответственно ;к первым и вторым входам соответствующих разрядов сумматора результата, 15 этих мультиплексоров соединены с ин- третьи входы которых подключены к вы формационными входами блока анализа ходам соответствующих разрядов регистра результата, первые и вторые входы разрядов сумматора сомножителей подключены к выходам разрядов соответст- 2о тельной цифры результата устройства, венно регистров множимого и множите- второй выход соединен с первым входом ля, выходы разрядов сумматора сомножителей подключены к входам разрядов -регистров множителя и множимого, отличающееся тем, что, с 25 целью повышения достоверности работы устройства за счет обеспечения функционального контроля устройства, в него введены регистр константы, три мультиплексора, группа мультиплексо- ЗО ми входами седьмого и второго элемен- ров, триггер, счетчик, блок анализа тов И, третьим выходом второго элемента ИЛИ, входом управления сдвигом регистра сдвига, выход (п+2)-го разряда которого соединен с единичным входом триггера, вход второго тактирующего сигнала устройства соединен с входом управления вьщачей информации регистра множителя, первыми входами восьмого и третьего элементов И, вторым входом второго элемента

разрядов которого соединены с информационными входами первого, второго и третьего мультиплексоров, управляющие входы которых соединены с выходами разрядов счетчика, а выходы

и контроля, п ервый выход которого соединен с первым входом шестого элемента И и является выходом положивторого элемента И и является выходом отрицательной цифры результата устройства, третий выход блока анализа и контроля является выходом сигнала ошибки устройства, вход первого тактирующего сигнала устройства соединен с входом управления выдачей информации регистра множимого, с первы35

и контроля, элементы ИЛИ, НЕ, причем третьи входы разрядов сумматора сомножителей соединены с выходами.разрядов регистра константы, вход управления выдачей прямого кода которого соединен с входом переноса младшего разряда сумматора результата и с выходом первого элемента ИЛИ, первый вход которого соединен с выходом пер- Q

вого элемента И и с входом управления вьщачей обратного кода регистра сдвига, выходы разрядов которого соединены с третьими входами соответствующих

ШШ, вход третьего тактирующего сигнала устройства соединен с управляющими входами мультиплексоров группы, вторыми входами шестого,пер- разрядов сумматора результата, первые .g вого, пятого и четвертого элементов и вторые входы (Р+3)-х старших разря- И, тактовьм входом блока анализа и дов сумматора результата (Р - задержка получения разряда результата) соединены с выходами второго и третьего элементов И соответственно и с вторым и третьим входами первого эле- . мента ИЛИ соответственно, выходы разрядов сумматора результата соединены с информационными входами мультиплексоров группы, выходы которых соедине- вьщачей обратного кода которого сое- ны с входами разрядов регистра резуль- динен с выходом третьего элемента И, тата соответственно, вход управления приемом кода которого соединен с выходом второго элемента ИЛИ, первый

50

контроля, выход седьмого элемент И соединен с входом управления вьщачей прямого кода регистра множимого,вход управления выдачей обратного кода которого соединен с выходом второго элемента И, входом первого элемента НЕ, входом управления приемом кода регистра множителя, вход управления

входом второго элемента НЕ, входом управления приемом кода регистра мноЖИМОГ01, вход управления сдвигом которого соединен с входом управления сдвигом регистра результата, выходы

этих мультиплексоров соединены с ин- формационными входами блока анализа тельной цифры результата устройства, второй выход соединен с первым входо ми входами седьмого и второго элемен тов И, третьим выходом второго элемента ИЛИ, входом управления сдвигом регистра сдвига, выход (п+2)-го разряда которого соединен с единичным входом триггера, вход второго тактирующего сигнала устройства соединен с входом управления вьщачей информации регистра множителя, первыми входами восьмого и третьего элементов И, вторым входом второго элемента

этих мультиплексоров соединены с ин- формационными входами блока анализа тельной цифры результата устройства, второй выход соединен с первым входо ми входами седьмого и второго элемен тов И, третьим выходом второго элемента ИЛИ, входом управления сдвигом регистра сдвига, выход (п+2)-го разряда которого соединен с единичным входом триггера, вход второго тактирующего сигнала устройства соединен с входом управления вьщачей информации регистра множителя, первыми входами восьмого и третьего элементов И, вторым входом второго элемента

разрядов которого соединены с информационными входами первого, второго и третьего мультиплексоров, управляющие входы которых соединены с выходами разрядов счетчика, а выходы

этих мультиплексоров соединены с ин- формационными входами блока анализа тельной цифры результата устройства, второй выход соединен с первым входом ми входами седьмого и второго элемен- тов И, третьим выходом второго элемента ИЛИ, входом управления сдвигом регистра сдвига, выход (п+2)-го разряда которого соединен с единичным входом триггера, вход второго тактирующего сигнала устройства соединен с входом управления вьщачей информации регистра множителя, первыми входами восьмого и третьего элементов И, вторым входом второго элемента

и контроля, п ервый выход которого соединен с первым входом шестого элемента И и является выходом положиэтих мультиплексоров соединены с ин- формационными входами блока анализа тельной цифры результата устройства, второй выход соединен с первым входом ми входами седьмого и второго элемен- тов И, третьим выходом второго элемента ИЛИ, входом управления сдвигом регистра сдвига, выход (п+2)-го разряда которого соединен с единичным входом триггера, вход второго тактирующего сигнала устройства соединен с входом управления вьщачей информации регистра множителя, первыми входами восьмого и третьего элементов И, вторым входом второго элемента

второго элемента И и является выходом отрицательной цифры результата устройства, третий выход блока анализа и контроля является выходом сигнала ошибки устройства, вход первого тактирующего сигнала устройства соединен с входом управления выдачей информации регистра множимого, с первыю15 2о 25 ЗО

35

Q

ШШ, вход третьего тактирующего сигнала устройства соединен с управляющими входами мультиплексоров группы, вторыми входами шестого,пер- g вого, пятого и четвертого элементов И, тактовьм входом блока анализа и вьщачей обратного кода которого сое- динен с выходом третьего элемента И,

0

контроля, выход седьмого элемент И соединен с входом управления вьщачей прямого кода регистра множимого,вход управления выдачей обратного кода которого соединен с выходом второго элемента И, входом первого элемента НЕ, входом управления приемом кода регистра множителя, вход управления

ШШ, вход третьего тактирующего сигнала устройства соединен с управляющими входами мультиплексоров группы, вторыми входами шестого,пер- вого, пятого и четвертого элементов И, тактовьм входом блока анализа и вьщачей обратного кода которого сое- динен с выходом третьего элемента И,

входом второго элемента НЕ, входом управления приемом кода регистра мноШШ, вход третьего тактирующего сигнала устройства соединен с управляющими входами мультиплексоров группы, вторыми входами шестого,пер- вого, пятого и четвертого элементов И, тактовьм входом блока анализа и вьщачей обратного кода которого сое- динен с выходом третьего элемента И,

ЖИМОГ01, вход управления сдвигом которого соединен с выходом второго , элемента НЕ, выход восьмого элемента И соединен с входом ущ5авления вьщачей прямого кода регистра множителя, вход управления сдвигом которого соединён с выходом первого элемента НЕ, второй вход седьмого элемента И соединен с информационньм входом регистра множителя и является входом положительной цифры множителя

П 1 n-H-i ni-2-i 12 11 Ю

устройства, второй вход восьмого элемента И соединен с информационным ВХОДОМ регистра множимого и является входом положительной цифры множимого устройства, второй вход второго элемента И является входом сзтрицатель- ной цифры множителя устройства,второй вход третьего элемента И является входом отрицательной цифры множимого устройства.

Фиг. 2

| Множительное устройство последовательного действия | 1973 |

|

SU451079A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для умножения | 1976 |

|

SU603989A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1988-09-30—Публикация

1986-06-16—Подача