1

1305689Изобретение относится к вычислительной технике и может быть использовано в системах автоматизированного контроля распределенного типа, вчдст- ности в системах дистанционного об- служивания ЭВМ гибких автоматизированных производств.

Цель изобретения - повышение быстродействия контроля.

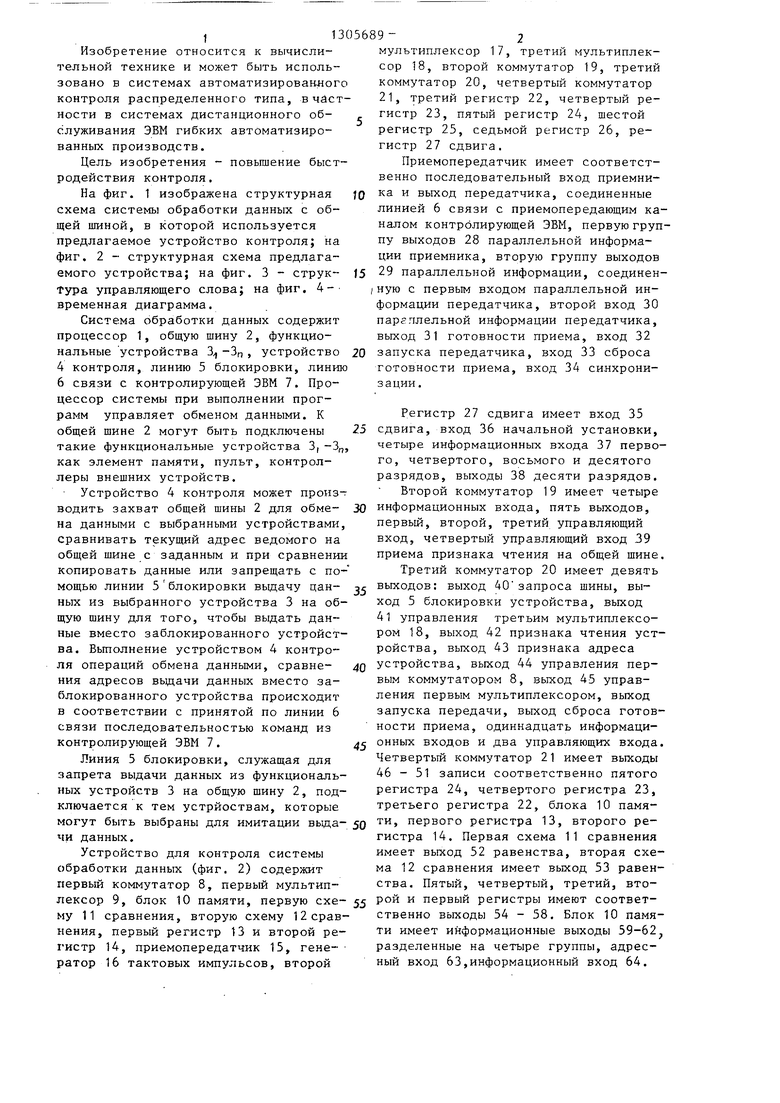

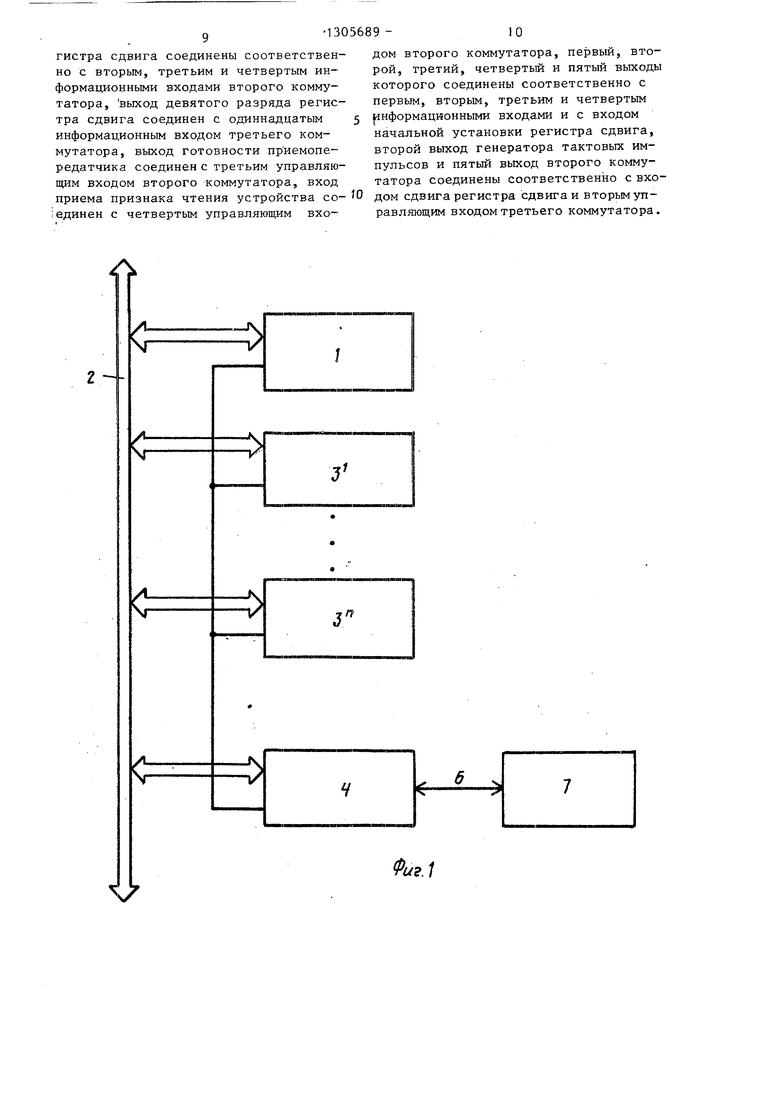

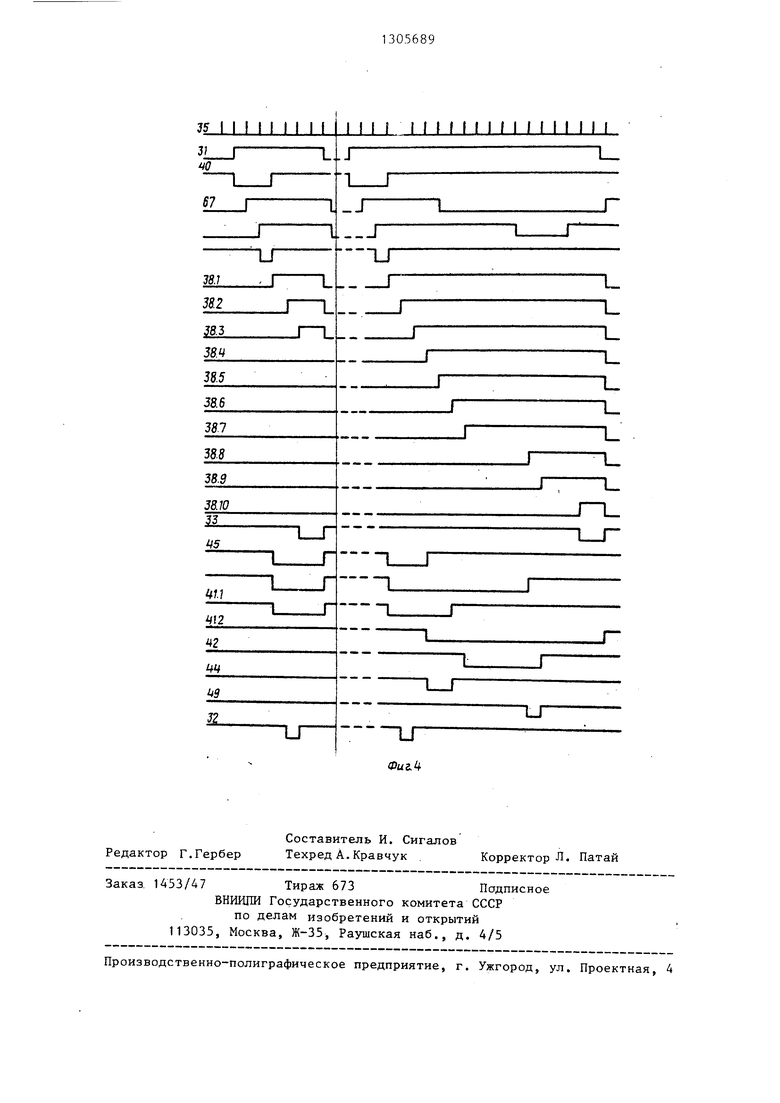

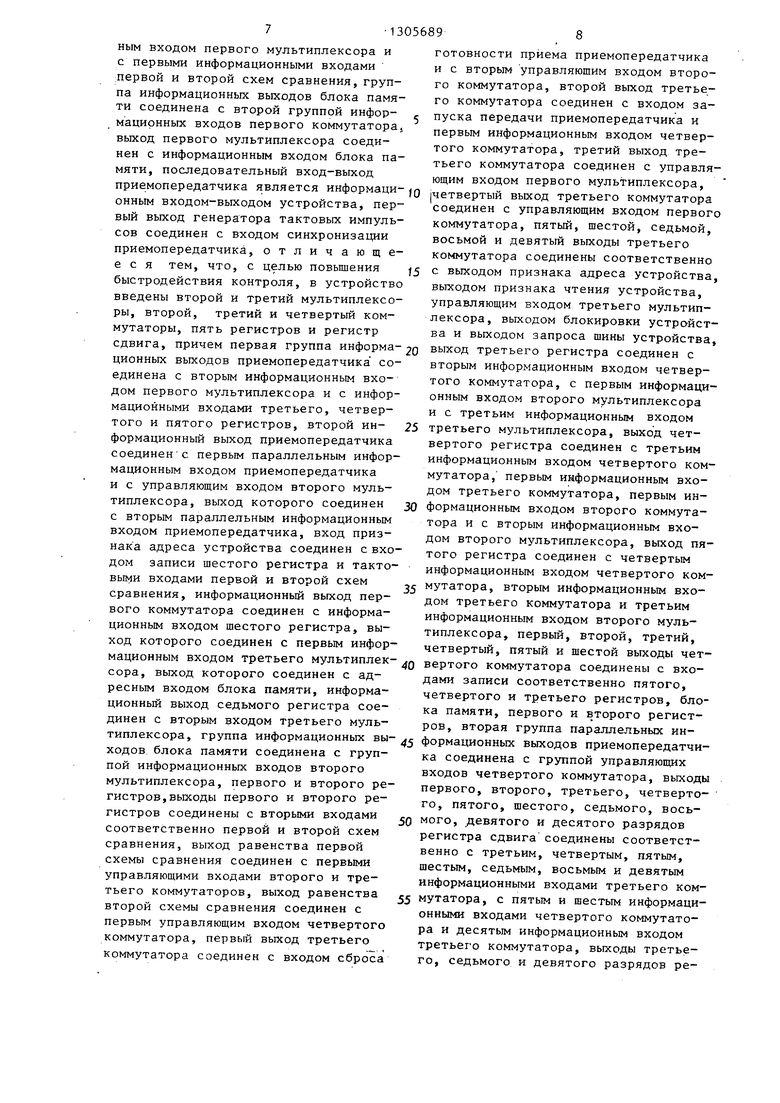

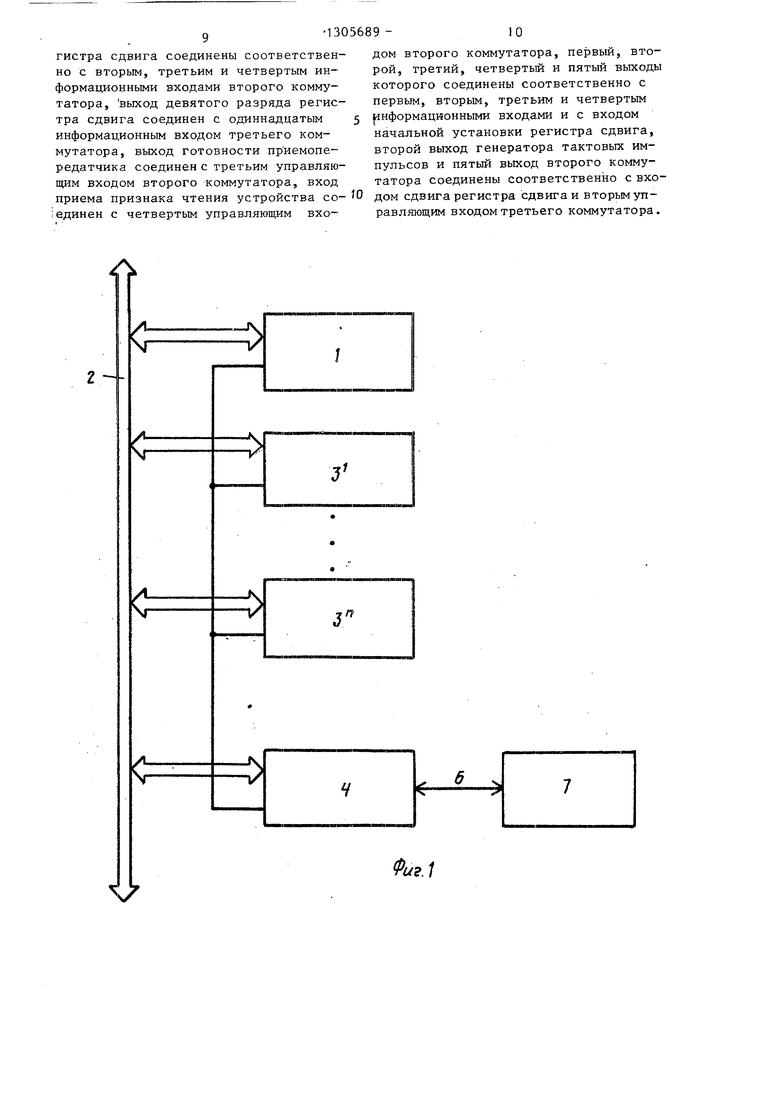

На фиг. 1 изображена структурная JQ схема системы обработки данных с общей шиной, в которой используется предлагаемое устройство контроля; на фиг. 2 - структурная схема предлагаемого устройства; на фиг. 3 - струк- 15 тура управляющего слова; на фиг. 4- временная диаграмма.

Система обработки данных содержит процессор 1, общую шину 2, функциональные устройства , устройство 20 4 контроля, линию 5 блокировки, линию 6 связи с контролирующей ЭВМ 7. Процессор системы при выполнении программ управляет обменом данными. К общей шине 2 могут быть подключены 25 такие функциональные устройства 3, -3,, как элемент памяти, пульт, контроллеры внешних устройств.

Устройство 4 контроля может производить захват общей шины 2 для обме- 30 на данными с выбранными устройствами, сравнивать текущий адрес ведомого на общей шине с заданным и при сравнении копировать данные или запрещать с по- мощью линии 5 блокировки выдачу цан- ных из выбранного устройства 3 на общую шину для того, чтобы вьщать данные вместо заблокированного устройства. Вьтолнение устройством 4 контроля операций обмена данными, сравне- 40 НИН адресов вьщачи данных вместо заблокированного устройства происходит в соответствии с принятой по линии 6 связи последовательностью команд из контролирующей ЭВМ 7.45

Линия 5 блокировки, служащая для запрета выдачи данных из функциональных устройств 3 на общую шину 2, подключается к тем устрйоствам, которые

35

мультиплексор 17, третий мультиплексор 18, второй коммутатор 19, третий коммутатор 20, четвертый коммутатор 21, третий регистр 22, четвертый регистр 23, пятый регистр 24, шестой регистр 25, седьмой регистр 26, регистр 27 сдвига.

Приемопередатчик имеет соответственно последовательный вход приемника и выход передатчика, соединенные линией 6 связи с приемопередающим каналом контролирующей ЭВМ, первую группу выходов 28 параллельной информации приемника, вторую группу выходов 29 параллельной информации, соединен- (ную с первым входом параллельной информации передатчика, второй вход 30 паргллельной информации передатчика, выход 31 готовности приема, вход 32 запуска передатчика, вход 33 сброса готовности приема, вход 34 синхронизации.

Регистр 27 сдвига имеет вход 35 сдвига, вход 36 начальной установки, четыре информационных входа 37 первого, четвертого, восьмого и десятого разрядов, выходы 38 десяти разрядов.

Второй коммутатор 19 имеет четыре информационных входа, пять выходов, первый, второй, третий управляющий вход, четвертый управляющий вход 39 приема признака чтения на общей шине.

Третий коммутатор 20 имеет девять выходов: выход 40 запроса шины, выход 5 блокировки устройства, выход 41 управления третьим мультиплексором 18, выход 42 признака чтения устройства, выход 43 признака адреса устройства, выход 44 управления первым коммутатором 8, выход 45 управления первым мультиплексором, выход запуска передачи, выход сброса готовности приема, одиннадцать информационных входов и два управляющих входа. Четвертый коммутатор 21 имеет выходы 46 - 51 записи соответственно пятого регистра 24, четвертого регистра 23, третьего регистра 22, блока 10 памямогут быть выбраны для имитации выда- первого регистра 13, второго речи данных.гистра 14. Первая схема 11 сравнения

Устройство для контроля системыимеет выход 52 равенства, вторая схеобработки данных (фиг. 2) содержитма 12 сравнения имеет выход 53 равенпервый коммутатор 8, первый мультип-ства. Пятый, четвертый, третий, втолексор 9, блок 10 памяти, первую схе- 55Р° первый регистры имеют соответму 11 сравнения, вторую схему 12срав-ственно выходы 54 - 58. Блок 10 памянения, первый регистр 13 и второй ре-ти имеет информационные выходы 59-62,

гистр 14, приемопередатчик 15, гене- разделенные на четыре группы, адресратор 16 тактовых импульсов, второйный вход 63,информационный вход 64.

5

0 5

0 0 5

5

мультиплексор 17, третий мультиплексор 18, второй коммутатор 19, третий коммутатор 20, четвертый коммутатор 21, третий регистр 22, четвертый регистр 23, пятый регистр 24, шестой регистр 25, седьмой регистр 26, регистр 27 сдвига.

Приемопередатчик имеет соответственно последовательный вход приемника и выход передатчика, соединенные линией 6 связи с приемопередающим каналом контролирующей ЭВМ, первую группу выходов 28 параллельной информации приемника, вторую группу выходов 29 параллельной информации, соединен- (ную с первым входом параллельной информации передатчика, второй вход 30 паргллельной информации передатчика, выход 31 готовности приема, вход 32 запуска передатчика, вход 33 сброса готовности приема, вход 34 синхронизации.

Регистр 27 сдвига имеет вход 35 сдвига, вход 36 начальной установки, четыре информационных входа 37 первого, четвертого, восьмого и десятого разрядов, выходы 38 десяти разрядов.

Второй коммутатор 19 имеет четыре информационных входа, пять выходов, первый, второй, третий управляющий вход, четвертый управляющий вход 39 приема признака чтения на общей шине.

Третий коммутатор 20 имеет девять выходов: выход 40 запроса шины, выход 5 блокировки устройства, выход 41 управления третьим мультиплексором 18, выход 42 признака чтения устройства, выход 43 признака адреса устройства, выход 44 управления первым коммутатором 8, выход 45 управления первым мультиплексором, выход запуска передачи, выход сброса готовности приема, одиннадцать информационных входов и два управляющих входа. Четвертый коммутатор 21 имеет выходы 46 - 51 записи соответственно пятого регистра 24, четвертого регистра 23, третьего регистра 22, блока 10 памя3-1

Первый коммутатор 8 имеет двунаправленные шины 65, информационный выход 66. Вход 67 признака адреса устройства служит для записи текущего адреса в шестой регистр 25 и тактирования схем 11 и 12 сравнения. Шестой регистр 25 имеет выход 68, седьмой регистр 26 имеет выход 69.

Устройство контроля системы обработки данных с общей шиной работает следующим образом.

Принятый по линии 6 связи последовательный код байта-преобразуется приемопередатчиком 15 в параллельный код и вьщается на группы выходов 28 и 29 приемника в соответствии с форматом фиг. 3, где управляющее поле байта на выходах 29(5-8 бит), информационное поле байта на вькодах 28( -4 бит). Отработка принятого байта- команды происходит в следующей последовательности:

прием байта, содержащего команду чтения /записи регистра, захват общей шины;

передача в контролирующую ЭВМ 7 ответного байта подтверждения;

вьшолнение команд, записанных в служебные регистры 23 и 24;

освобождение общей шины 2.

Служебные регистры 22 - 24 адресуются непосредственно из управляющего поля - выходы 29, а операционные регистры в блоке 10 памяти - косвенно через регистр 22, который позволяет адресовать 16 операционных регистров. Чтение/запись операционных регистров из контролирующей ЭВМ 7 осуществляется по тетрадам (4 бита) последовательностью байтов команд.

Прием байта приемопередатчиком 15 сопровождается появлением сигнала

Готовность приема с выхода 31, ко- сброс готовности приема, сбрасывающий

торый проходит через коммутатор 19 на вход 36 начальной установки регистра 27 сдвига и разблокирует его для сдвига: при этом на выходе 40

сигнал 31 готовность приема приемопередатчика 8, низкий уровень которого обнуляет регистр 27 сдвига.

Последовательность выбора регистров, содержащих адреса операционных регистров после приема команды чтения/записи по общей шине, определяется сигналами 41.1, 41.2 на входе 41 управления мультиплексора 18. Высокий

50

Последовательность выбора регистров, содержащих адреса операционных регистров после приема команды чтения/записи по общей шине, определяется сигналами 41.1, 41.2 на входе 41 управления мультиплексора 18. Высокий

коммутатора 20 появляется сигнал запроса общей шины 2. В первый триггер регистра 27 сдвига происходит запись 1, тактируемая сигналом 35 генератора 16. При сдвиге последовательно устанавливаются в 1 остальные триг-сс уровень этих сигналов в исходном сос- геры - выходы 38.1, - 38.10, по кото- тоянии (после сброса регистра 27 сдви- рым формируются коммутаторами 19 - 2 1 ) обеспечивает передачу адреса из все сигналы цикла управления устрой- регистра 25 текущего адреса ведомого ством 4.на общей шине на вход 63 адреса блока

5 0

5

0

5

0

Цикл управления включает в себя последовательно сигнал 32 - запуск передатчика приемопередатчика 15, по переднему фронту которого стробирует- ся запись данных в регистре устройства 4, выбираемом коммутатором 21, а по заднему фронту этого сигнала записанная информация передается через мультиплексор 17 на вход 30 приемопе- редатчика 15 для передачи подтверждения .

Выбор регистров для записи осуществляется ко 1мутатором 21 в соответствии с управляющим полем байта по выходам 46 - 51. Запись адресов из операционных регистров в регистры 13 и 14 происходит по сигналам 50 и 51, формируемым при записи в определенные операционные регистры адресов ср аанения.

Коммутация данных с выходов 28 приемопередатчика 15 на вход соответствующей тетрады операционного регистра блока 10 памяти происходит при низком уровне сигнала на входе 45 управления мультиплексора 9.

В формате ответного байта подтверждения повторяется управляющее поле принятого байта - группа выходов 29, информационное поле в команде чтения определяется прочитанным кодом тетрады регистра,в команде записи -, записанным кодом тетрады, передаваемым через мультиплексор 17 на вход 30 приемопередатчика 15 для передачи.

Адрес операционного регистра из регистра 22 выбирается через мультиплексор 18, управляемый по входу 41.

Если в принятом байте не содержится команда чтения/записи регистра выбранного устройства на общей шине, то после передачи подтверждения коммутатором 20 вырабатыв ается сигнал 33

сброс готовности приема, сбрасывающий

0

сигнал 31 готовность приема приемопередатчика 8, низкий уровень которого обнуляет регистр 27 сдвига.

Последовательность выбора регистров, содержащих адреса операционных регистров после приема команды чтения/записи по общей шине, определяется сигналами 41.1, 41.2 на входе 41 управления мультиплексора 18. Высокий

сс уровень этих сигналов в исходном сос- тоянии (после сброса регистра 27 сдви- ) обеспечивает передачу адреса из регистра 25 текущего адреса ведомого на общей шине на вход 63 адреса блока

10 памяти. При выполнении обмена по общей шине обеспечивается следующая последовательность переключения адресов блока 10 памяти:

адрес из регистра 22;

адрес из регистра 26 фиксированных адресов., определяющий операционный регистр, содержащий адрес ведомого устройства;

адрес из регистра 26 фиксированных JQ адресов 5 определяющий операционный регистр для чтения/записи данных ведомого устройства.

Адрес из регистра 25 используется при операции копирования и имитации выдачи данных выбранного устройства, так как в него всегда заносятся младшие разряды адреса ведомого по сигналу kl признак адреса. Адрес из регистра 22 - при чтении/записи тетра- 2п ды операционного регистра, адреса из регистра 26 - для указания адреса и данных при обмене с выбранным устройством на общей шине.

На временной диаграмме показано 5 чтение данных из устройства с заданным адресом после захвата общей шины 2. При этом устройством 4 вырабатывается сигнал 43 признака адреса на ши1305689 6

имитации 56.4 регистра 23 команд в коммутаторе 20 формируется сигнал 44 выдачи через коммутатор 8 из операционного регистра на общую шину данных вместо заблокированного устройства. Блокировка устройства с заданным адресом на общей шине 2 осуществляется после установки первого разряда 54.1 регистра 24 операций.

Операция имитации может быть выполнена без блокировки чтения данных из устройств а с указанным адресом на общей шине. Для этого используется запись новых данных после захвата об- 15 щей шины в регистр того устройства, которое принимает прочитанные данные, причем захват общей шины происходит по сравнению с заданным адресом блокировки. Триггер для запуска такой имитации входит в коммутатор 19. При сравнении адреса блокировки чтения (сигналы 53 и 39) триггер устанавливается в О и высокий уровень с его выхода проходит через элемент ИЛИ на выход 36 и запускает цикл регистра 27 сдвига, в котором захватывается общая шина 2 и происходит запись новых данных, а затем триггер устанавливается в исходное состояние 1

не 2, сигнал 44 выдачи адреса ведомо-JQ сигналом 33. При приеме такой команды

го из операционного регистра с адресом из регистра 26 через коммутатор 8, сигнал 42 - признака чтения данных. Данные принимаются одновременново все тетрады операционного регистра данных через коммутатор 8 и мультиплексор 9 по высокому уровню сигнала на входе 45 управления мультиплексора 9.

Запись всех тетрад осуществляется одновременной подачей сигналов 49,1- 49.4 коммутатора 21. Цикл завершается сигналом 33 Сброс готовности приема .

При операции копирования данных (наблюдение) не выполняется захват шины, а. по совпадению сигналов 52 сравнения адресов наблюдения и признака 39 чтения или записи данных, выбираемого в зависимости от состояния второго разряда 54.2 регистра 24,формируются сигналы-49.1-49.4 записи во все тетрады.

При операции имитации по сигналу 53 сравнения адресов блокировки (без захвата шины) формируется сигнал 5 блокировки на время действия сигнала 67 признака адреса, а по сигналу 39 признака чтения данных и готовности

записи с готовностью имитации она записывается в регистр 23 команд, но не выполняется, так как готовность имитации 55.1 блокирует ее выполнение, при наличии сигнала 31 готовности приема.

Адрес регистра, принявшего прочитанные данные, и новые данные записываются в соответствующие операционные регистры, используемые при чтении/записи по общей шине.

В этом случае возможна имитация вьщачи данных без линии 5 блокировки, которая может быть исключена.

Формула изобретения

Устройство для контроля системы обработки данных, содержащее первый коммутатор, первый мультиплексор,блок памяти, первую и вторую схемы сравнения, первый и второй регистры, генератор тактовых импульсов и приемопередатчик, причем группа информаци- онных входов-вькодов устройства через двунаправленную магистраль соединена с первой группой информационных входов первого коммутатора, вьгход которого соединен с первым информационным входом первого мультиплексора и с первыми информационными входами первой и второй схем сравнения, группа информационных выходов блока памяти соединена с второй группой информационных входов первого коммутатораj выход первого мультиплексора соединен с информационным входом блока памяти, последовательный вход-выход приемопередатчика является информаци- онным входом-выходом устройства, первый выход генератора тактовых импульсов соединен с входом синхронизации приемопередатчика, отличающееся тем, что, с целью повышения быстродействия контроля, в устройство введены второй и третий мультиплексоры, второй, третий и четвертый коммутаторы, пять регистров и регистр сдвига, причем первая группа информационных выходов приемопередатчика соединена с вторым информационным входом первого мультиплексора и с информационными входами третьего, четвертого и пятого регистров, второй ин- формационный выход приемопередатчика соединен С первым параллельным информационным входом приемопередатчика и с управляющим входом второго мультиплексора, выход которого соединен с вторым параллельным информационным входом приемопередатчика, вход признака адреса устройства соединен с входом записи шестого регистра и тактовыми входами первой и второй схем сравнения, информационный выход первого коммутатора соединен с информационным входом шестого регистра, выход которого соединен с первым информационным входом третьего мультиплек- сора, выход которого соединен с адресным входом блока памяти, информационный выход седьмого регистра соединен с вторым входом третьего мультиплексора, группа информационных вы- ходов блока памяти соединена с группой информационных входов второго мультиплексора, первого и второго регистров, выходы первого и второго регистров соединены с вторыми входами соответственно первой и второй схем сравнения, выход равенства первой схемы сравнения соединен с первыми управляющими входами второго и третьего коммутаторов, выход равенства второй схемы сравнения соединен с первым управляющим входом четвертого коммутатора, первый выход третьего коммутатора соединен с входом сброса

5 о 5 о Q с -

5

готовности приема приемопередатчика и с вторым управляющим входом второго коммутатора, второй выход третьего коммутатора соединен с входом запуска передачи приемопередатчика и первым информационным входом четвертого коммутатора, третий выход третьего коммутатора соединен с управляющим входом первого мультиплексора, |четвертый вьосод третьего коммутатора соединен с управляющим входом первого коммутатора, пятый, шестой, седьмой, восьмой и девятый выходы третьего коммутатора соединены соответственно с выходом признака адреса устройства, выходом признака чтения устройства, управляющим входом третьего мультиплексора, выходом блокировки устройства и выходом запроса шины устройства, выход третьего регистра соединен с вторым информационным входом четвертого коммутатора, с первым информационным входом второго мультиплексора и с третьим информационным входом третьего мультиплексора, выкод четвертого регистра соединен с третьим информационным входом четвертого коммутатора, первым информационным входом третьего коммутатора, первым информационным входом второго коммутатора и с вторым информационным входом второго мультиплексора, выход пятого регистра соединен с четвертым информационным входом четвертого коммутатора, вторым информационным входом третьего коммутатора и третьим информационным входом второго мультиплексора, первый, второй, третий, четвертый, пятый и шестой выходы четвертого коммутатора соединены с входами записи соответственно пятого, четвертого и третьего регистров, блока памяти, первого и второго регистров, вторая группа параллельных информационных выходов приемопередатчика соединена с группой управляющих входов четвертого коммутатора, выходы первого, второго, третьего, четвертого, пятого, шестого, седьмого, восьмого, девятого и десятого разрядов регистра сдвига соединены соответственно с третьим, четвертым, пятым, шестым, седьмым, восьмым и девятым информационными входами третьего коммутатора, с пятым и шестым информационными входами четвертого коммутатора и десятым информационным входом третьего коммутатора, выходы третьего, седьмого и девятого разрядов регистра сдвига соединены соответственно с вторым, третьим и четвертым информационными входами второго коммутатора, выход девятого разряда регистра сдвига соединен с одиннадцатым информационным входом третьего коммутатора, выход готовности приемопередатчика соединен с третьим управляющим входом второго коммутатора, вход приема признака чтения устройства со;единен с четвертым управляющим вхо

J

V

3

::

О

дом второго коммутатора, первый, второй, третий, четвертый и пятый выходы которого соединены соответственно с первым, вторым, третьим и четвертым информационными входами и с входом начальной установки регистра сдвига, второй выход генератора тактовых импульсов и пятый выход второго коммутатора соединены соответственно с входом сдвига регистра сдвигай вторымуп- равляющим входом третьего коммутатора.

-:

Фи.

Упробщащее поле OQuma

ин(рорпоционное ftoAe байта

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для отладки программ микроЭВМ | 1989 |

|

SU1815643A1 |

| Устройство для сопряжения ЦВМ с группой абонентов | 1988 |

|

SU1559349A1 |

| Устройство для сопряжения ЭВМ с периферийными устройствами | 1988 |

|

SU1566359A1 |

| Устройство для обмена информацией между ЭВМ и периферийными устройствами | 1989 |

|

SU1777145A2 |

| Устройство для обмена информацией | 1982 |

|

SU1118992A1 |

| Устройство для сопряжения ЭВМ с линиями связи | 1988 |

|

SU1536393A1 |

| Устройство для обмена данными между электронно-вычислительной машиной и абонентами | 1985 |

|

SU1277125A1 |

| Устройство для сопряжения ЭВМ с линиями связи | 1991 |

|

SU1784989A1 |

| Устройство для сопряжения вычислительной машины с каналами связи | 1983 |

|

SU1140125A1 |

| Система ввода-вывода для микропрограммируемой ЭВМ | 1988 |

|

SU1667084A1 |

Изобретение относится к вычислительной технике и может быть использовано в системах автоматизированного контроля распределенного типа.Цель изобретения - повышение быстродействия устройства. Устройство имеет процессор, общую шину, функциональные устройства, устройство контроля, линию блокировки, линию связи, контролирующую ЭВМ. Устройство для контроля содержит первый коммутатор, мультиплексор, блок памяти, первую и вторую схемы,сравнения, первый и второй регистры, приемопередатчик, генератор тактовых импульсов, второй, третий мультиплексоры, второй, третий, чет- вертьтй коммутаторы,с третьего по седьмой регистры, регистр сдвига. 4 ил. СЛ С

1-ъапись/ о-чтение 1 - опер, рег,

о-слуя{,рег. Номер

CflfXOUHOZO

регистра или

номер твтраЪы

операционного

решстра

содврмимов

тетрады

операционного

регистра или

длужа6нои

регистра

Регистр адреса

операционного

регистра

Регистр яоионЭ

1- tomotMoctffit

sf.t

имитации 1- Ьнешнев

IjClflpOf CntflO

t- Чтение по нагистраяи

t-лопись по магистрали

Регистр операций

l-pa peuittHUS имитации 1 - наблюдение при Чтении

О- наблюдение при записи

Редактор Г.Гербер

Составитель И. Сигалов

Техред А.Кравчук . Корректор Л. Патай

Заказ. 1453/47 Тираж 673Подписное

ВНШЩИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

| Microprocessing and Micropro- gramamming, 1982, № 9, p | |||

| Способ очищения амида ортотолуолсульфокислоты | 1921 |

|

SU315A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-04-23—Публикация

1985-04-12—Подача