1 .1

Изобретение относится к вычислительной технике и может найти применение в информационно-измерительнглх системах.

Цель изобретения - расширен1(2 области применения за счет обеспечения дополнительной возможности преобразования обратных кодов.

На чертеже приведена функциональная схема устройства.

Преобразователь содержит входной регистр 1, блок 2 переключателей, .резистивную. матрицу 3, источник 4 опорного напряжения, переключат1зль 5 элемент И 6, операционный усилитель 7, ifflBepTop 8 тока, информационную 9, управляющую 1 О и выходную 11 .

Преобразователь работает следующим образом.

Входной знакопеременный код посту пает на информационную шину 9. Лри этом сигнал логической 1 на уирав- ля1ои.1ем входе любого из переключателе блока 2 обеспечивает подключение соответствующего выхода резистивной матрицы 3 к суммирующей точке операционного усилителя 7, а сигнал логического О его подключение к инвертору 8 тока.

.

При преобразовании обратного кода на управляющую щину 10 устройства подается сигнал логической 1, В этом случае выходной сигнал элемента И 6 определяется состоянием прямого выхода первого (знакового) разряда Б;ХОД- ного регистра 1. Если преобразуется положительное число ()5 элемент И 6 закрыт, первый выход резист:-:зной матрицы 3 подключен к суг-с-шрующему входу операционного усилителя 1, а (п+1)-й выход - к входу инверто 5а 8 тока. Суммарный ток I-, формируемый на первых выходах блока 2 переключателей, определяется выражением

,-U-f,

J-R 1

1.

где и

СП

а;

2-+ i: as2-.-a,2з 2.

напряжение источника ., значение разряда входного кода-.

2 Uon - .

- взвешенный

через

матрицы

ток, протека с1щий

(п+1)-й резистор 2

3, подключенньш ключевым

элементом 5 к первой выхс.:1ной шине при значении а.

Суммарный ток 1, формируемый на вторых выходах блока 2 переключателей, определяется выражением

||Л а,

.,-% а. .2-

R

Sri

-J.

ля

Ток на суммирующем входе усштите- 7 определяется выражением

п

f-(5.-a,)2-. lie .(a,:5,).

a

20

,5 где

д - число, представленное обратным п-разрядным двоичным кодом в виде „.. а„. Выходное напряжение при преобразовании обратного двоичного кода имеет вид,

- --|72 - UOH при ,512

вых

йв тт

512 °

при

0

5

0

где - разрядность входного кода.

При преобразовании дополнительного кода на управляющую mimy 10 уст-, ройства подается сигнал логического О, В этом случае элемент И 6 закрыт и независимо от состояния знакового разряда входного кода (п+1)-й выход матрицы 3 подключается переключателем 5 на время преобразования к входу инвертора 8„

Токи I, l и этом определи- ются выражепиями„

Поп Г - - -1 .

i..2

Г R L

а,. 2

Г

-R а, -J.I Ucn i --

1Л

Z- ад 2

5; 2

,

а,)

21 (as- 35)

X

X 2

-S + 1

- 7

Uon д J- R-A.

где .-A - число, представленное дополнительным кодом.

Выходное напряжение при преобразовании дополнительного двоичного кода имеет вид

5ЫХ

NAB ттм

512

N,6

Аб

512 512

1,

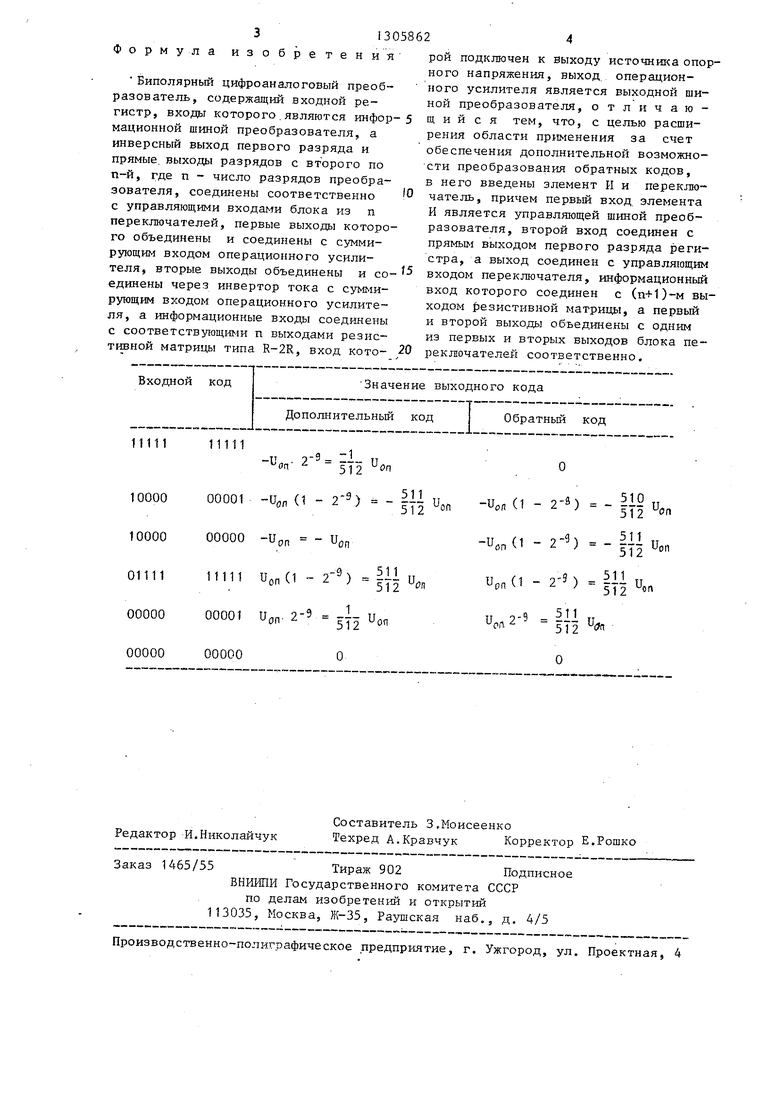

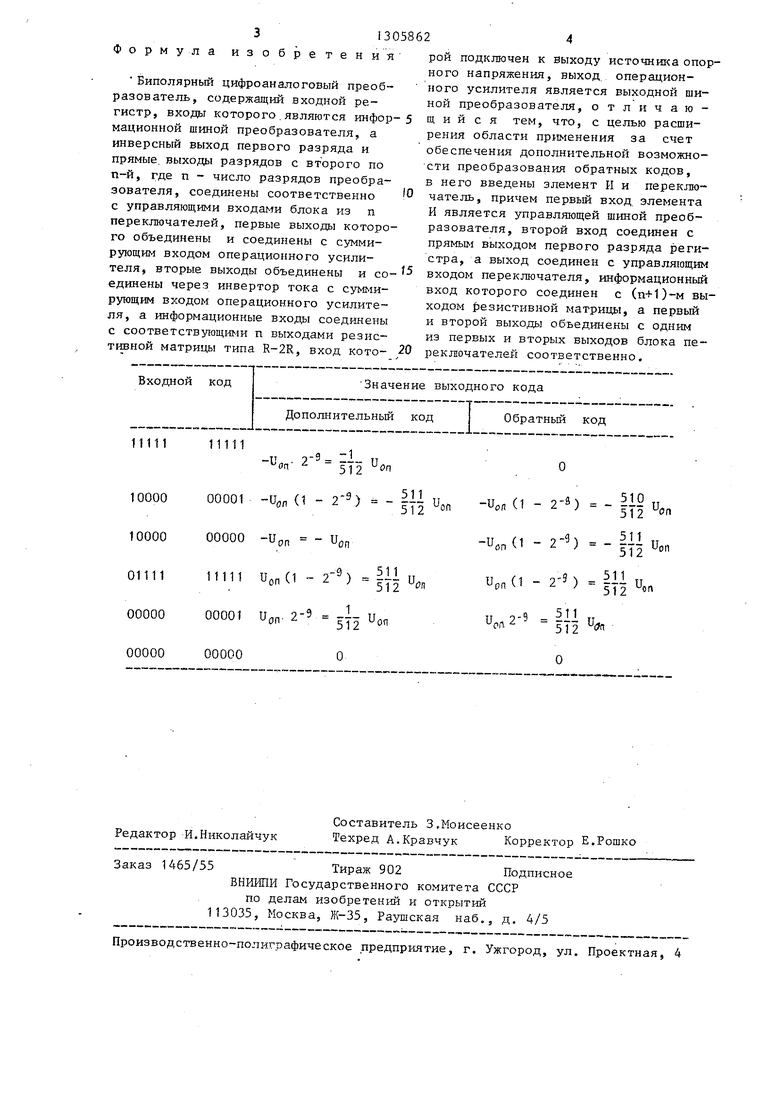

Значения выходного сигнала преобразователя, соответствующие типичньм входным кодам, приведены в таблице.

Формула изобретения

Биполярный цифроаналоговый преобразователь, содержащий входной регистр, входы которого.являются информационной шиной преобразователя, а инверсный выход первого разряда и прямые, выходы разрядов с второго по п-й, где п - число разрядов преобразователя, соединены соответственно с управляющими входами блока из п переключателей, первые выходы которого объединены и соединены с суммирующим входом операционного усилителя, вторые выходы объединены и со единены через инвертор тока с суммирующим входом операционного усилителя, а информационные входы соединены с соответствующими п выходами резис- тивной матрицы типа R-2R, вход кото,

11111

11111

- -I- ТТ

512

Редактор И.Николайчук

Составитель З.Моисеенко

Техред А.КравчукКорректор Е.Рошко

Заказ 1465/55Тираж 902Подписное

ВНИИПИ Государственного комитета СССР

по изобретен™ и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

10

5 f5

20

рои подключен к выходу источника опорного напряжения, выход, операционного усилителя является выходной шиной преобразователя, отличающийся тем, что, с целью расширения области применения за счет обеспечения дополнительной возможности преобразования обратных кодов, в него введены элемент И и переключатель, причем первый вход элемента И является управляющей шиной преобразователя, второй вход соединен с прямым выходом первого разряда регистра, а выход соединен с управляющим входом переключателя, информационный вход которого соединен с (п+1)-м выходом {)езистивной матрицы, а первый и второй выходы объединены с одним из первых и вторых выходов блока переключателей соответственно.

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифро-аналоговый преобразователь | 2017 |

|

RU2648579C1 |

| Двоично-десятичный цифроаналоговый преобразователь | 1987 |

|

SU1575313A1 |

| Устройство для преобразования координат | 1985 |

|

SU1247901A1 |

| Обращенный цифроаналоговый преобразователь с резистивной матрицей R-2R | 1986 |

|

SU1345347A1 |

| Устройство для синусно-косинусного цифро-аналогового преобразования | 1983 |

|

SU1129632A1 |

| Устройство контроля цифроаналоговых преобразователей | 1990 |

|

SU1777238A1 |

| Устройство цифроаналогового преобразования | 1987 |

|

SU1524180A1 |

| Цифроаналоговый преобразователь | 1988 |

|

SU1543546A1 |

| Функциональный преобразователь | 1985 |

|

SU1267445A2 |

| Устройство для синусно-косинусного преобразования кода в напяжение | 1982 |

|

SU1089588A1 |

Изобретение относится к вычислительной технике и может найти применение в информационно-измерительных системах. Цель изобретения - расширение области применения за счет обеспечения дополнительной возможности преобразования обратных кодов. Преобразователь содержит входной регистр 1, блок 2 переключателей, резистивную матрицу 3, источник 4 опорного напряжения, переключатель 5, элемент И 6, операционньй усилитель 7, инвертор 8, тока, 1-шформационнуи шину 9, управляющую шину 10 и выходную шину 11. В зависимости от вида преобразуемого кода (обратного или дополнительного) с учетом его знака введенный в преобразователь элемент И 6 управляет с помощью переключателя 5 (п+1)-м разрядом резистивной матрицы 3, аналогичным младшему разряду, что обеспечивает преобразование указанных кодов без методической погрешности. 1 ил., 1 табл. О 9 (Л с со о ел 00 Р 1чЭ

| Федорков Б.Г., Телец В.А., Дег- тяренко В,П | |||

| Микроэлектронные цифро- аналоговые и аналого-цифровые преобразователи.- М.: Радио и связь, 1984, с; 45-51 | |||

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Справочник по цифро- аналоговым и аналого-цифровым преобразователям./ Под ред | |||

| Ю.А.Рюжина.- М.: Радио и связь, 1982, рис | |||

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| , (54) БИПОЛЯРНЫЙ ЦИФРОАНАЛОГОВЫЙ ПРЕОБРАЗОВАТЕЛЬ | |||

Авторы

Даты

1987-04-23—Публикация

1985-05-06—Подача