Изобретение относится к области экспериментального определения динамических характеристик инерционных объектов и может быть использовано при исследовании и наладке различных устройств систем автоматического регулирования (например, следящих систем,.фильтров и т. п.).

Цель изобретения - повышение точности измерения чистого запаздывания инерционного- объекта при ступенчатом входном сиг- :нале, особенно для высокодинамических звеньев систем регулирования.

Устройство позволяет определять чистое запаздывание инерционных объектов, передаточные функции которых имеют вид

ь

(Р)Гр-Т1(

или

т,-+Ш+-1-

При ступенчатом сигнале на их входе. При этом сначала фиксируются через равные промежутки времени At значения выходного сигнала исследуемого объекта. В случае, когда передаточная функция объекта имеет вид (1), необходимо зафиксировать всего два значения, а в случае, когда передаточная функция объекта имеет вид (2) - четыре значения выходного сигнала объекта. Эти значения можно зафиксировать на любом участке переходной характеристики объекта (за исключением установившегося значения). Затем из уравнений, которые для объекта () имеют вид

(3)

(4)

y,k - у,, а для объекта (2)

y:k| + yoks - уг; y2ki + yiks - УЗ,

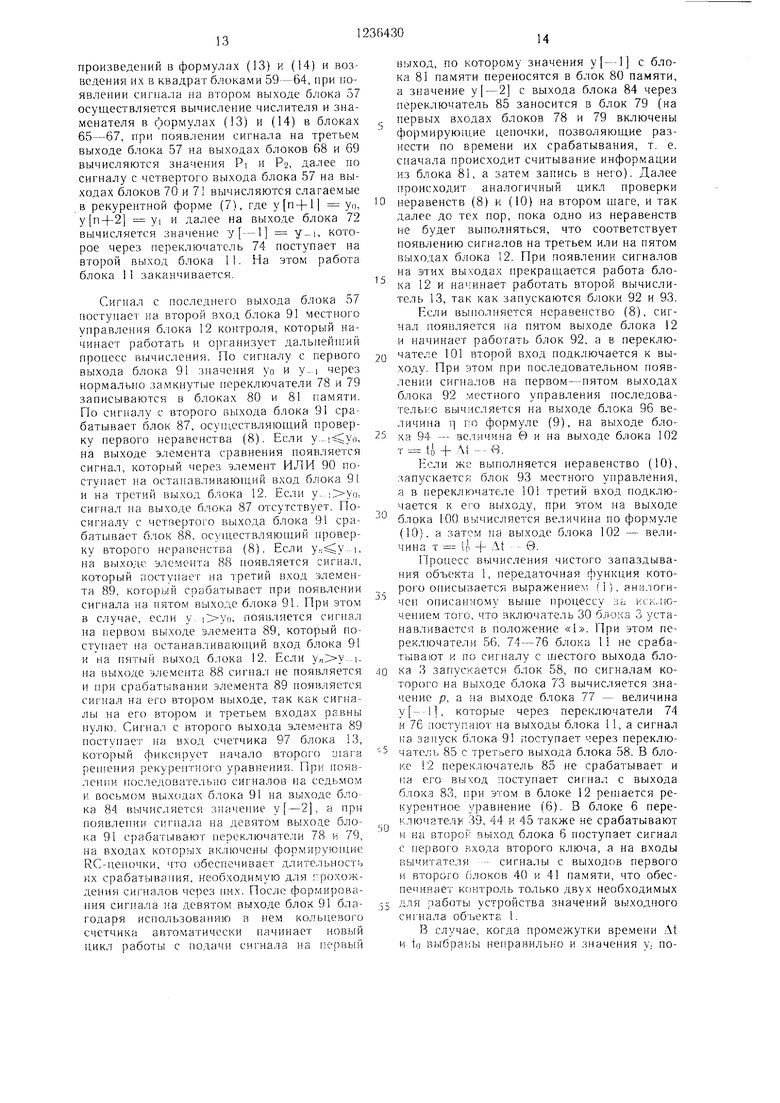

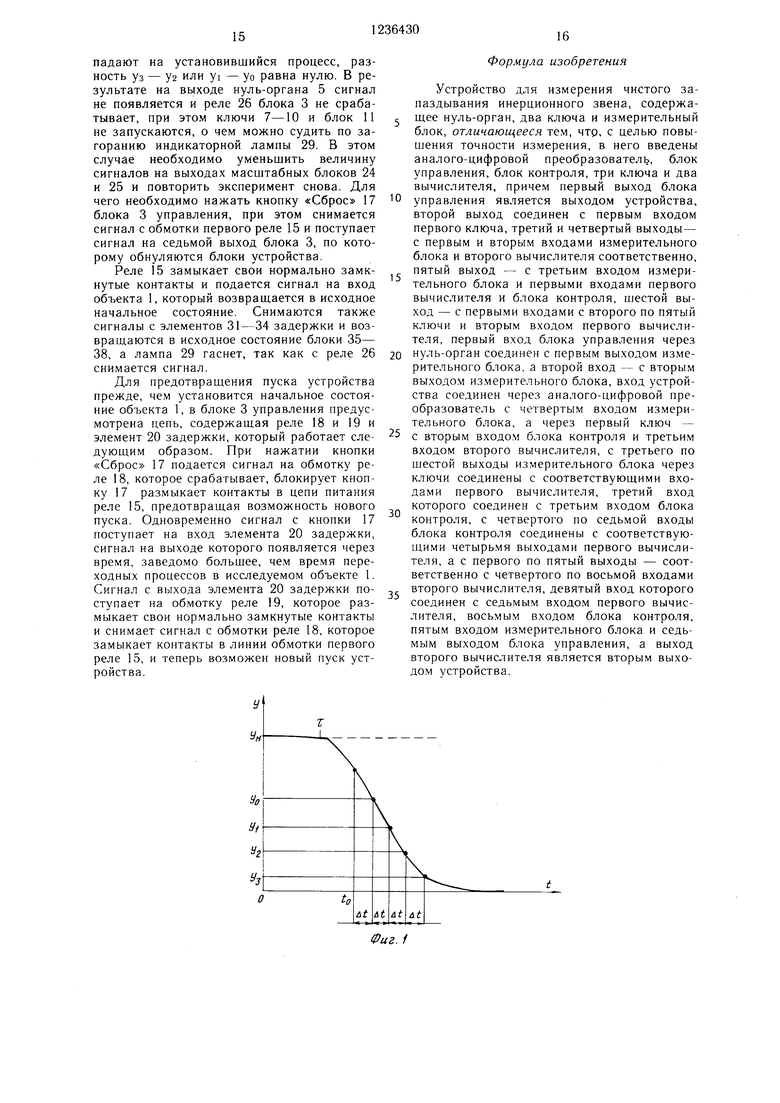

где У - зафиксированные значения выходного сигнала объекта (фиг. I), определяются промежуточные коэффициенты k, k|, kj и коэффициенты

Р1ь К.

J k;

(5

которые являются коэффициентами рекурентных уравнений, определяюидих переход ные характеристики соответственно для об ь- ектов (1) и (2)

--- + li;Сб)

У п - piy п -f 1 Р2У п -f 2, (7)

гдеп О, 1 N.

Эти уравнения получают в результате отображения ре111ений непрерывных дифференциальных уравнений, соответствуюпдих выражениям (1) и (2), наблюдаемым в дискретные моменты времени t to, ti, ., tN, не соответствующие им дискретные (реку

0

рентные) уравнения. При этом можно показать, что решения непрерывных уравнений, взятые в дискретные моменты времени, связаны с решениями дискретных уравнений коэффициентами k, ki, k, определяемыми с помощью уравнений (3) и (4).

Приняв теперь время to за начальный момент, где уо, у + 1 yi, и решая уравнения (6) и (7) в убывающем отсчете, т. е. определяя значения у - 1, , ..., , получим дискретные значения переходной функции объекта, предшествующие первому зафиксированному значению уо. При движемся по кривой переходной характеристики в сторону убывания непрерывного времени, т. е. t 0. Определив момент времени, когда первое значение равно у„, получаем время чистого запаздывания.

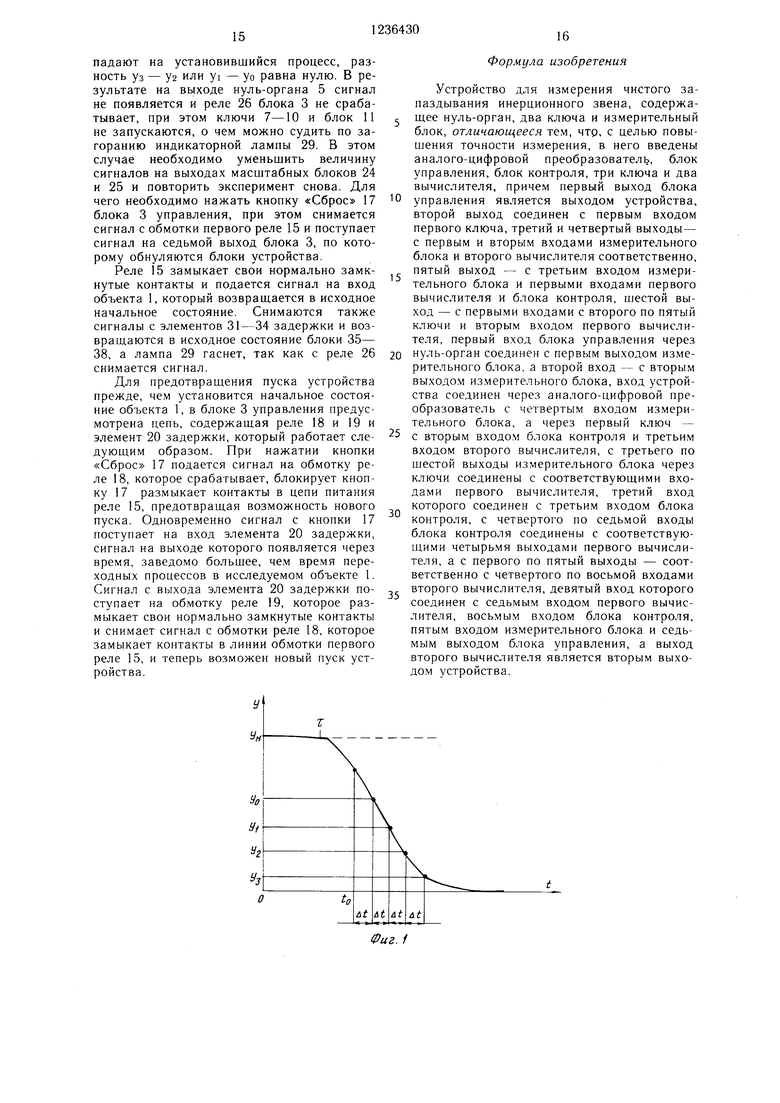

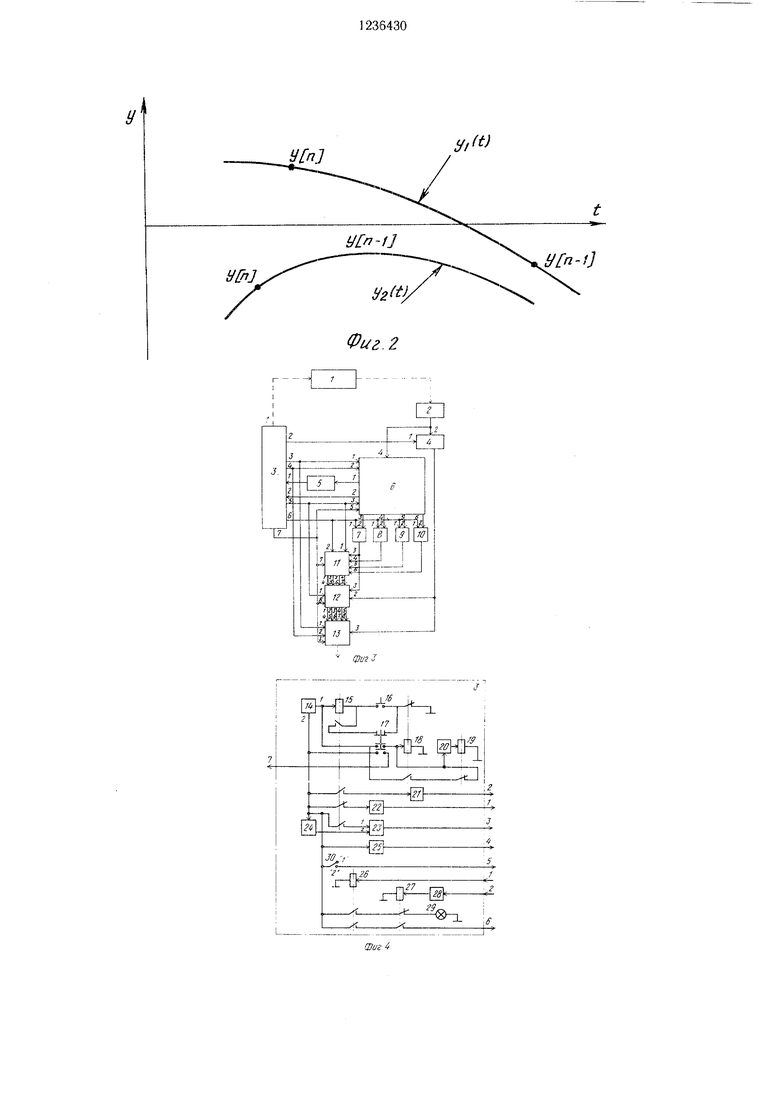

Однако, вследствие неточности при считывании значений может возникнуть ошибка, т. е. не получится значение Уп- Здесь могут возникнуть два случая подхода к установившемуся начальному значению, которые показаны на фиг. 2 - кривая yi(t) переходит через уп, а кривая y2(t) не доходит до УП- Поэтому в устройстве осуществляется контроль значений решений рекурентных уравнений.

Если

y(-N у

30

у,..

(8)

то вычисляется дополнительная величина

в At(N

(9)

где

ylirb l i3J/jL

+ li

Этот случай соответствует случаю кривой yi(t), а формула (9) реализует алгоритм аппроксимации кривой отрезком прямой и деление оси времени на части. Есл и

,(lo;

то

B /U N. Этот случай соответствует кривой-у2 t.

Ч:нстое запаздывание определяется по формуле T to--e.(11)

В предлагаемом устройстве для измерения чистого запаздывания в зависимости от вида передаточной функции динамического объекта осуществляется измерение либо двух, либо четырех значений его выходного сигнала при подаче на вход ступенчатого сигнала. Затем рещаются рекурентные уравнения в обратном отсчете, что соответствует движению по кривой переходной функции объекта к начальному состоянию. Коэффициенты рекурентных уравнений определяются по зафиксированным значениям выходного сигнала объекта. Решение уравнений продолжается до тех пор, пока не будет получено значение, наиболее близкое к начальному установившемуся значению выходного сигнала объекта. После чего осуществ- ляется процедура уточнения момента достижения переходной характеристикой начального значения, по которому определяется величина чистого запаздывания.

Таким образом, в предлагаемом устройстве величина чистого запаздывания опре- деляется по значениям переходной характеристики, взятым в моменты времени, когда их величины значительны. При этом влияние нелинейности и помех выходных датчиков объектов во много раз меньше, чем на начальном участке и их влияние на результат незначительно. Кроме того, в устройстве предусмотрены специальные меры, также исключаюш,ие влияние неточностей считывания сигналов, что существенно повышает точность определения чистого запаздывания по сравнению с известным устройством. Точность определения чистого запаздывания с помошью предлагаемого устройства не зависит от его величины и одинакова как для больших, так и для очень малых т.

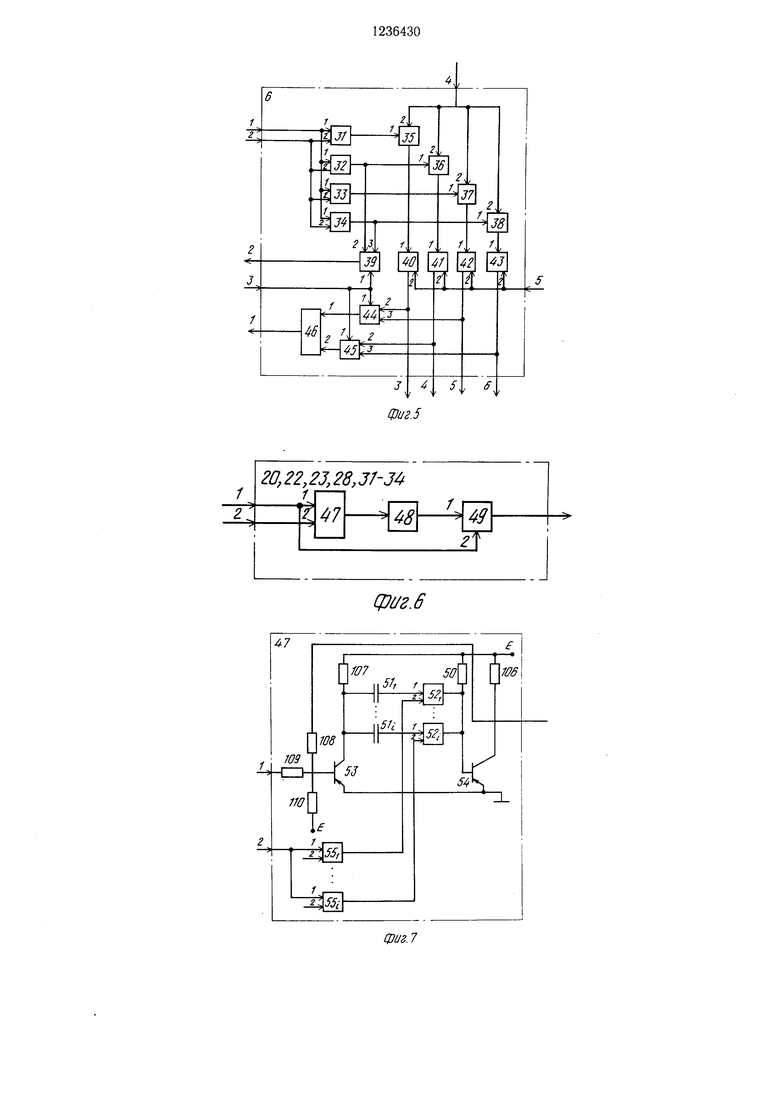

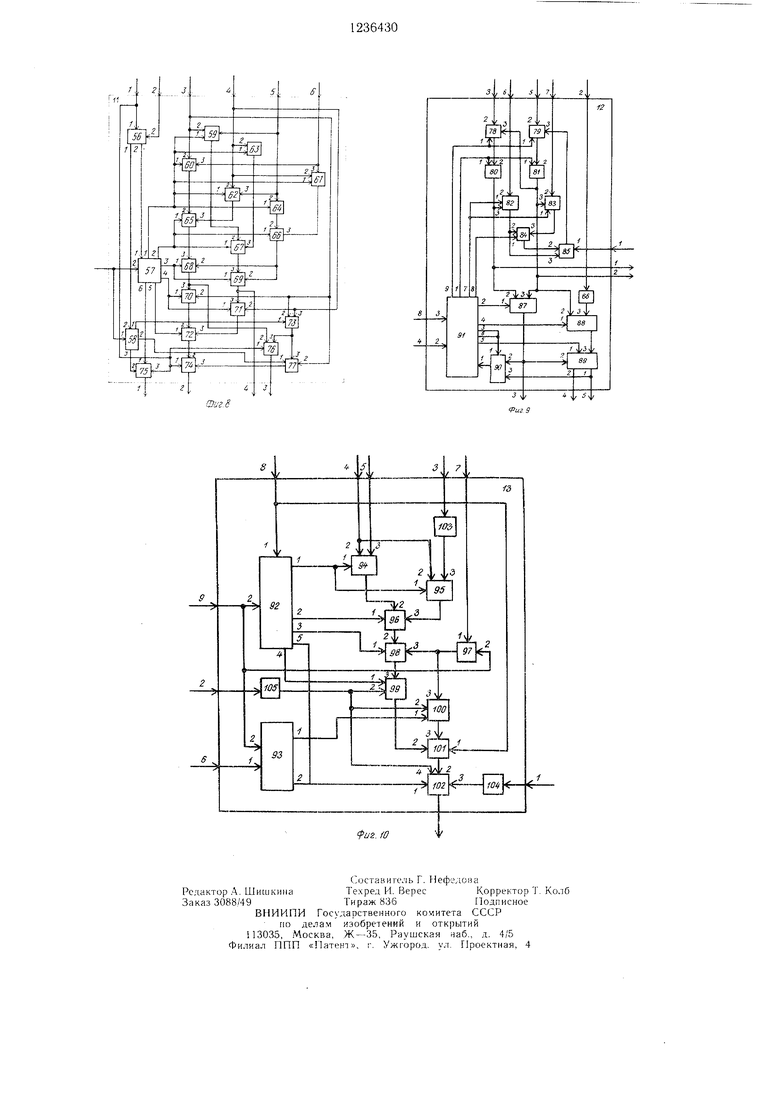

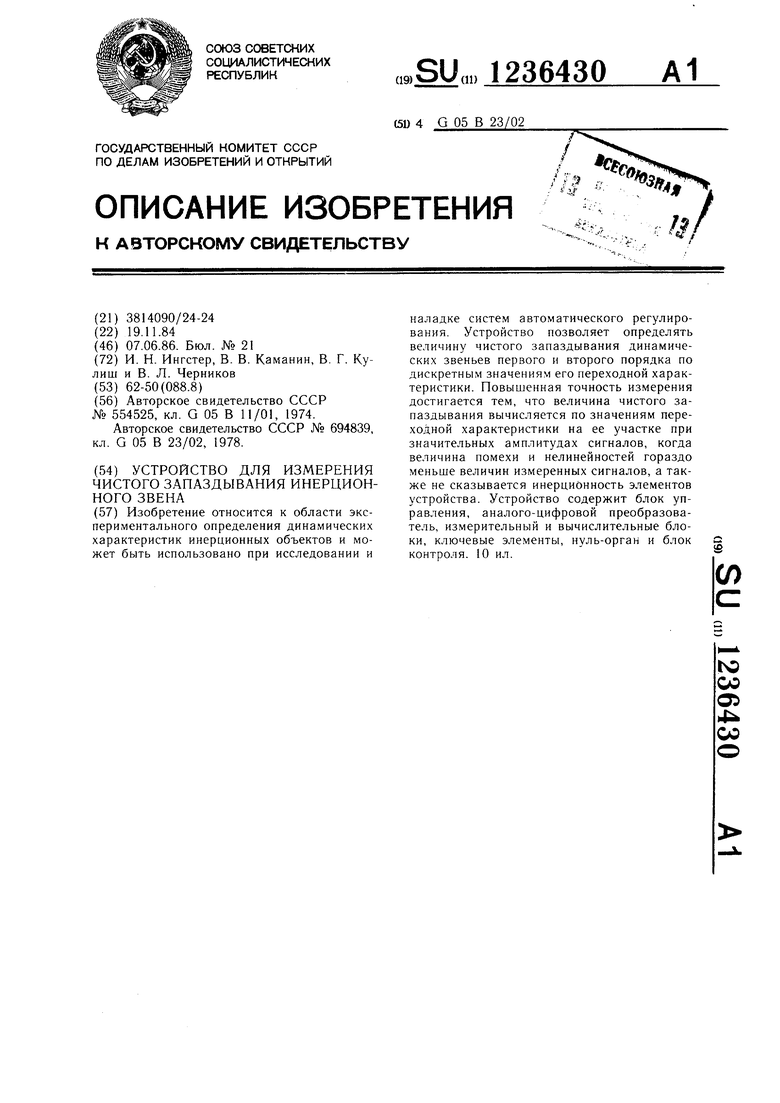

На фиг. 1 и 2 представлены графики переходного процесса и переходных функций; на фиг. 3-10 - структурные схемы устройства и его отдельных блоков.

Устройство содержит исследуемый объект 1, первый аналого-цифровой преобразователь 2, блок 3 управления, первый ключ 4, нуль-орган 5, измерительный блок 6, ЕВТО- рой-пятый ключи 7-iO, первый вычислитель 11 начальных условий, блок 12 контроля, второй вычислитель 13 времени чистого запаздывания, источник 14 напряжений, пер- вое реле 15, кнопку «Пуск 16, кнопку «Сброс 17, второе и третье реле 18 и 9, первый элемент 20 задержки, дифференцирующую цепочку 21, второй и третий элементы 22 и 23 задержки, масштабные блоки 24 и 25, четвертое и пятое реле 26 и 27, четвертый элемент 28 задержки, индикаторную лампу 29, включатель 30, пятый- восьмой элементы 31-34 задержки, шестой-девятый ключи 35-38, первый переключатель 39, первый-четвертый блоки 40-43 памяти, второй и третий переклю- чатели 44 и 45, первый вычитатель 46, реле 47 времени, инвертор 48, первый элемент 49 совпадения, резистор 50, конденсатор 51, десятый ключ 52, первый и второй транзисторы 53 и 54, первый элемент 55 сравнения, четвертый переключатель 56, первый и второй блоки 57 и 58 местного управления, первый-четвертый блоки 59-62 умножения, первый и второй квадраторы 63 и 64, второй-четвертый вычитателя 65-67, первый и второй блоки 68 и 69 деления, пятый и шестой блоки 70 и 71 умножения, первый сумматор 72, третий блок 73 деления, пятый-седьмой переключатели 74-76, второй

,

0

5

. 0 Q 5

0

сумматор 77, восьмой и девятый переключатели 78 и 79, пятый и шестой блоки 80 и 81 памяти, седьмой и восьмой блоки 82 и 83 умножения, третий сумматор 84, десятый переключатель 85, седьмой блок 86 памяти, второй и третий элементы 87 и 88 сравнения, второй элемент 89 совпадения, элемент ИЛИ 90, третий-пятый блоки 91-93 местного управления, пятый и шестой вычитате- ли 94 и 95, четвертый блок 96 деления, счетчик 97, седьмой вычитате,дь 98, девятый и десятый блоки 99 и 100 умножения, переключатель 101, седьмой вычитатель 102, восьмой блок 103 памяти, второй и третий аналого-цифровые преобразователи 104 и 05, резисторы 106-ПО.

В предлагаемом устройстве в качестве исследуемого объекта 1 могут использоваться различные приборы и блоки систем автоматического управления, передаточные функции которых описываются выражениями (1) или (2). К таким устройствам можно отнести например, следящие системы, усилители, фильтры и т. п.

Аналого-цифровой преобразователь 2 предназначен для преобразования выходного сигнала объекта 1 в цифровой двоичный код, число разрядов которого равно К (например, 15). В качестве аналого-цифрового гфеобразователя используется преобразователь напряжения в код с поразрядным кодированием.

Блок 3 управления состоит из источника 14 напряжений, пяти реле 15. 18, 19, 26 и 27. двух KHOiioK «Пуск 16 н «Сброс 17, четырех элементов 20, 22, 23 и 28 задержки, двух масц табны блоков 24 и 25, индикаторной лампы 29. дифференцирующей цепочки 21 и включателя 30. Первый выход источника 14 напряжений через обмотки и контакты реле 15, 18 и 19, кнопки 16 и 17 и элемент 20 задержки подключен к нулевой шине. Второй выход источника 14 напряжений через нормал.ьно разомкнутые контакты реле 15 и блок 21 подключен к второму выходу блока 3 управления, через нормально замкнутые контакты реле 15 и элемент 22 задержки - к первому выходу блока 3 управления, через нормально разомкнутые контакты реле 15 и элемент 23 задержки - к третьему выходу блока 3 управления, через масштабный блок 24 - к второму входу элемента 23 задержки, через масштабный блок 25 - к четвертому выходу блока 3 управления, через включатель 30 - к пятому выходу блока 3 управления, через нормально разомкнутые контакты реле 26 и 27 - к шестому выходу блока 3, через нормально разомкнутые контакты реле 26, нормально замкнутые контакты реле 27 и лампу 29 - к нулевой шине, а через контакты кнопки 17 - к седьмому выходу блока 3 управления. Первый вход блока 3 соединен через обмотку реле 26 с нулевой шиной, а второй

вход блока 3 подключен к нулевой шине через элемент 28 задержки и обмотку реле 27.

Первое реле 15 имеет три нормально разомкнутых и один нормально замкнутый контакты, второе реле 18 имеет один нормально разомкнутый и один нормально замкнутый контакты, третье реле 19 - один нормально замкнутый контакт, четвертое реле 26 - два нормально разомкнутых контакта, а пятое реле 27 - один нормально замкнутый и один нормально разомкнутый контакты. Элементы 20, 22 и 28 задержки являются неуправляемыми элементами, а элемент 23 - управляемым.

Элементы 20, 22, 23 и 28 задержки представляют собой последовательно соединенные реле 47 времени, инвертор 48 и элемент 49 совпадения, выход которого является выходом блоков 20, 22, 23 и 28, а второй вход соединен с входом реле 47 времени и входом элементов 20, 22, 23 и 28. Элемент 23 задержки содержит реле 47 времени с вторым (управляющим) входом, который является вторым входом .элемента 23 (фиг. 6).

Реле 47 времени элементов 20, 22 и 28 содержит два транзистора 53 и 54, на базу перво1 0 из которых подается входной сигнал, а его коллектор через конденсатор 5 подключен к базе второго транзистора 54, с коллектора которого снимается выходной сигнал. За счет выбора емкости конденсатора обеспечивается требуемая задержка выходного сигма. Ш. Реле 47 времени эле.мента 23 задержки содержит (фиг. 7), кроме того, i элементов 55 сравнения, первые входы которых соединены с вторым входом реле 47, а на вторые входы подаротся напряжения, отличаюп;иеся на величину , а выходы эле.ментов сравнения соединены с вторыми входами i ключей 52, включенных между i конденсаторами 51 и базой транзистора 54. В качестве к, 1ючей 52 используются бесконтактные полупроводниковые реле, а в качестве элементов 55 сравнения - триггеры Шмидта с различными смеп ениями, что позволяет получить их срабатывание при различных управляющих напряжениях.

Масн табные блоки 24 и 25 служат для установки требуемых величин времени начала измерения to и нро.межутка времеш между измерениями Д1 и представляют собой резистивные делители напряжений. Элемент 21 представляет собой дифференци- руюн;ую RC-цепочку.

Нуль-орган 5 представляет собой триггер Шмидта с нулевым смещением и сигнал на его выходе появляется тогда, когда сигнал на его входе отличен от нуля, что соответствует случаю, ког да измеряемые значения выходного сигнала исследуемого об ь- екта 1 не попали на установившееся значение.

Измерительный блок 6 содежит четыре элемента 31-34 задержки, четыре ключа

0

5

0

0

5

0

5

0

5

35-38, три переключателя 39, 44 и 45, четыре блока 40-43 памяти и вычитатель 46. Первый и второй входы блока 6 соединены с первыми и вторы.ми входами элементов 31-34, выходы которых соединены с первыми входами ключей 35-38, вторые входы которых соединены с четвертым входом блока 6, третий вход которого соединен с первыми входами переключателей 39, 44 и 45, а второй и третий входы переключателя 39 соединены с выходами второго и четвертого блоков 32 и 34, а его выход является вторым выходом блока 6, первый выход которого соединен с выходом блока 46, первый и второй входы которого соединены с выходами переключателей 44 и 45 соответственно, вторые входы которых соединены с выходами первого и третьего блоков 40 и 42, а третьи входы - с выходами второго и четвертого блоков 4 и 43, а пятый вход блока 6 соединен с вторыми входами блоков 40-43 памяти.

Элементь 31-34 выполнены аналогично управляемому элементу 23 блока 3. Отличие состоит в том, что конденсаторы 51 эле.мента 32 выбираются в два раза больше, чем элемента 31, а элементов 33 и 34 - в три и четыре раза больше, чем элемента 31, что позволяет получить задержку сигнала эле- менто.м 32 2Л1, элементом 33 ЗД1, эле.мен- том 34 4At.

Ключи 35-38 блока 6, а также ключи 4, 7-10 содержат k (по числу разрядов используемого кода) идентичпых бесконтактных ключей, у которых второй вход подключается к выходу, когда на первый (управляю- П.1ИЙ) вход подается напряжение. Переключатели 39., 44 и 45 представляют собой релейные переключатели, у которых при подаче напряжения на обмотку (первый вход) третий вход подключается к их выходам, а в противном случае второй вход соединен с выходом. Переключател-и 44 и 45 содержат k (по числу разрядов используемого кода) реле.

Блоки 40-43 памяти предназначены для хранения измеренных значений выходного сигнала объекта 1 в определенные моменты времени и состоят каждый из k RS-триг- геров. Триггеры не имеют тактируюнхего вх(да и поэтому запоминают только первое значение входного сигнала. Вторые входы блоков 40-43 служат для подачи обнуляющего сигнала.

Вычитатель 46 содержит аналоговый блок вычитания, выход которого является выходом блока 46, а его входы через преобразователи код-напряжение соединены с первым и вторым входами блока 46 соответственно.

Вычислитель 11 предназначен для вычисления значений коэффипиентов Р, по формулам (5), где вычисляются в результате решения (3) и (4)

Р УО

У

р, у - УзУ1

p, У2 - УзУ1

и первого значения по формулам (6) и (7).

Вычислитель 11 содержит два блока 57 и 58 местного управления, четыре переключателя 56, 74-76, семь блоков 59-62, 70, 71 и 77, два квадратора 63 и 64, три зычита- теля 65-67, сумматор 72, три блока 68, 69 и 73 деления. Первый вход блока 11 соединен с первыми входами переключателей 56, 74-76, а второй вход переключателя 56 соединен с вторым входом блока 11, первый выход - с первым входом блока 58, второй выход - с первым входом блока 57, второй вход которого соединен с вторым входом блока 58 и седьмым входом вычислителя I, первый выход - с первыми входами блоков 59-64, второй выход - с первыми входами блоков 65-67, третий выход - с первыми входами блоков 68 и 69, четвертый выход - с первыми входами блоков 70 и 71, пятый, шестой выходы - с первыми входами блоков 72 и 75 соответственно, а первый, второй и третий выходы блока 58 - с первыми входами блоков 73 и 77 и вторым входом блока 75 соответственно. Третий вход блока 11 соединен с вторыми входами бло- ков 60, 59, 70, 73 и 77, четвертый вход блока 11 - с вторыми входами блоков 61-63 и 71 и третьим входом блока 73, пятый вход - с третьими входами блоков 59 и 62 и вторым входом блока 64, выход которого соединен с вторым входом блока 66, третий вход которого соединен через блок 61 с шестым входом блока 11 и третьим входом бло- ка 60, а выход - с вторыми входами блоков 68 и 69, третьи входы которых соединены с выходами блоков 65 и 67 соответственно, а второй и третий входы блока 65 соединены с выходами блоков 60 и 62, а второй и третий входы блока 67 - с выходами блоков 59 и 63. Выход блока 68 через блок 76 и выход блока 69 соединены с третьим и четвертым выходами блока 11 и через блоки 70 и 71 - с вторым и третьим входами блока 72 соответственно, выход которого соединен с вторым входом блока 74, третий вход которого через блок 77 соединен с выходом блока 73 и третьим входом блока 76, а выход - с вторым выходом блока 11, первый выход которого является выходом блока 75.

Переключатели 56 и 75 являются релейными переключателями, у которых первый

10

, 20 40 о 55

вход подключен к обмотке и является управляющим, а переключатель 74 содержит k идентичных релейных переключателей, у которых первый вход также является управляющим.

Блоки 57 и 58 местного управления служат для управления работой всех арифметических блоков вычислителя 1 в режимах, когда передаточная функция объекта 1 описывается выражениями (2) и (1) и представляет собой кольцевой счетчик, содержащий генератор синхроимпульсов и триггеры, выходы которых являются выходами блоков 57 и 58. Первые входы блоков 57 и 58 соединены с запускающими входами генератора, а вторые - с обнуляющими входами триггеров.

Блоки 59-73, 76 и 77 вычислителя II представляют собой цифровые арифметические устройства, у которых первые (управляющие) входы соединены с входом устройства синхронизации блока, организующего процесс выполнения операции, а другие входы предназначены для ввода данных. Блоки 59-73 являются блоками универсального типа, у которых результат записывается и хранится в выходном регистре после выполнения операции данного цикла. Блоки 70, 71 и 73 являются также ивертирующими.

Блок 12 контроля предназначен для контроля выполнения неравенств (8) и (10) при решении рекурентных уравнений (6) и (7) и содержит блок 91 местного управления, три переключателя 78, 79 и 85, три блока 80, 81 и 86 памяти, два блока 82 и 83 умножения, сумматор 84, два элемента 87 и 88 сравнения, элемент 89 совпадения и элемент ИЛИ 90. Первый вход блока 12 соединен с первым входом переключателя 85, выход которого соединен с третьим входом блока 79, второй вход - с выходом блока 83, третий вход - с выходом блока 84, первый вход которого соединен с восьмым выходом блока 91 местного управления, первый-седьмой и девятый выходы которого соединены с первыми входами блоков и элементов 80, 81, 87, 90, 88, 82, 83, 84, 78 и 79 соответственно, первый вход которого соединен с выходом элемента ИЛИ 90, второй и третий входы - с четвертым и восьмым входами блока 12, третий и пятый входы которого через последовательно включенные блоки 78 и 80, 79 и 81 соединены с первым и вторым выходами блока 12 и вторым и третьим входами элемента 87, выход которого соединен с вторыми входами блоков 90 и 91 и третьим выходом блока 12, третий вход элемента 87 соединен с вторым входом элемента 88, выход которого соединен с третьим входом элемента 89, а третий вход через блок 86 - с вторым входом блока 12, шестой и седьмой входы которого соединены с вторыми входами блоков 82 и 83, выходы которых соединены с вторым и третьим входами блока 84, а

третьи входы - с выходами блоков 80 и 81 соответственно, а третий вход блока 83 соединен также с третьим входом блока 78. Пятый выход блока 12 соединен с первым выходом элемента 89 и третьим входом элемента ИЛИ 90, а четвертый выход является вторым выходом элемента 89.

Блок 91 местного управления предназначен для управления работой блока 12 и аналогичен блокам 57 и 58. Первый его вход соединен с останавливающим входом генератора, второй вход - с запускающим входом, а третий - с обнуляющими входами триггеров.

Отличие блока 91 состоит в том, что он замкнут, т. е. не останавливается после формирования импульса на последнем выходе, а повторяет цикл формирования импульсов на всех выходах снова.

Переключатели 78, 79 и 85 содержат по k идентичных релейных переключателей, у которых первые входы соединены с обмотками реле.

Блоки 80 и 81 памяти предназначены для хранения промежуточных значений переменных при решении рекурентных уравнений и содержат по k RS-триггеров. Блоки 80, 81 и 84 аналогичны арифметическим блокам вычислителя П. Блоки 82 и 83 являются одновременно инвертирующими.

Элементы 87 и 88 представляют собой логические схемы сравнения, содержащие триггеры входного регистра, вентили, три схемы совпадения, инвертор, сумматор и триггеры выходного регистра. Сигналы на их выходах появляются в случаях, когда сигнал на третьем входе меньше сигнала на втором входе.

Элемент 89 совпадения представляет собой цифровой блок умножения с двумя выходами, сигнал на первом выходе появляется в случае, когда сигналы на втором и третьем не равны, а на втором выходе - в случае, когда сигналы на втором и третьем входах равны нулю.

Блок 86 памяти представляет собой регистр памяти, выполненный на RS-триггерах, и запоминает значение сигнала, поступающего на их вход.

Второй вычислитель 13 предназначен для вычисления величины чистого запаздывания по формулам (9) - (11) при учете, что to to -)- At и содержит два блока 92 и 93 местного управления, четыре блока 94, 95, 98 и 102 вычитания, два блока 99 и 100 умножения, два аналого-цифровых преобразователя 104 и 105, блок 96 деления, переключатель 101 и счетчнк 97. Восьмой вход вычислителя 13 соединен с первыми входами блоков 101 и 92, первый-пятый выходы которого соединены с первыми входами блоков 94-96, 98, 99 и 102 соответственно, а второй вход - с девятым входом вычислителя 13, вторым входом блока 97 и вторым

C)

0

5

0

О

5

0

5

ВХОДОМ блока 93 местного управления, первый и второй выходы которого соединены с первыми входами блоков 100 и 102 соот- ветстЕ1енно, а первый вход является шестым входом вычислителя 13. Четвертый и пятый входы вычислителя 13 являются вторым и третьим входами блока 94, выход которого соединен с вторым входом блока 96, выход которого соединен с вторым входом блока 98, а третий вход соединен с выходом блока 95, второй вход которого соединен с вторым входом блока 94, а третий вход через блок 103 соединен с третьим входом блока 13, седьмой вход которого через блок 97 соединен с третьими входами блоков 98 и 100, выходы которых соединены с третьими входами блоков 99 и 101 соответственно, выход последнего соединен с вторым входом блока 102, выход scoTOporo является выходом блока 13, а третий вход через блок 104 соединен с первым входом блока 13, второй вход которого соединен через блок 105 с вторыми входами блоков 99 и 100 и четвертым входом блока 102.

Блоки 92 и 93 местного управления аналогичны по своей структуре блокам 57 и 58, отличаются только количеством выходов и предназначены для управления процессом вычисления чистого запаздывания по формулам (9) - (И). Первый вход у них является запускающим, а второй - обнуляющим. Все блоки 94-96, 98-104 идентичны аналогичным блокам, описанным выше. Счетчик 97 предназначен для подсчета количества шагов решения рекурентных уравнений и представляет собой счетчик импульсов, содержащий m последовательно включенных триггеров. Начальное состояние счетчика устанавливается равным единице. Второй вход предназначен для возвращения счетчика в начальное состояние.

Устройство для измерения чистого запаздывания динамического объекта работает следующим образом.

В зависимости от априорной информации, шеющейся о передаточной функции исследуемого объекта 1, включатель 30 блока 3 управления устанавливается в положение «1, если объект 1 описывается выражением (1), и в положение «2, если объект описывается выражением (2). Если передаточная функция объекта 1 имеет вид (2). то сигнал с второго выхода блока 14 через переключатель 30 поступает на пятый выход блока 3 управления, с которого он поступает на переключатели 56, 74-76 блока 1, которые определяют его работу в режиме вычисления Р| и Ро по формулам (13) и (14) и решения уравнения (7). У переключателя 56 второй вход подключается к второму выходу, у переключателя 75 третий вход подключается к его выходу, а у переключателей 74 и 76 второй вход подключается к его выходу. Сигнал с пятого выхода блока 3 управления поступает также па третий вход блока 6,

в котором срабатывают переключатели 39, 44 и 45 и подключают третьи входы к их выходам, а также срабатывает переключатель 85 блока 12 и подключает его второй вход к выходу.

Зная также примерную длительность переходного процесса объекта 1, устанавливают с помощью масштабного блока 24 время to первого измерения, а с помощью мас- щтабного блока 25 - сигнал, пропорциональный промежутку времени между моментами измерения сигнала на выходе объекта 1 At. Величины to и At выбираются из условия, чтобы измеренные значения сигнала на выходе объекта 1 не попали на установившееся значение, где работа устройства невозможна.

При нажатии кнопки «Пуск 16 в блоке 3 управления срабатывает реле 15 и замыкает свои нормально разомкнутые контакты и кнопка 16 блокируется. Вторые контакты реле 15 замыкаются и скачкообразный сигнал поступает на цепочку 21, на выходе которой формируется импульс, поступающий через второй выход блока 3 на первый вход ключа 4, который замыкается, и сигнал, равный начальному установившемуся состоянию объекта 1, поступает на блоки 86 и 103 памяти блоков 12 и 13 и запоминается на них. Ширина импульса на выходе цепочки 21 выбирается из условия работы одного такта блока 2. Размыкаются первые нормально замкнутые контакты реле 15 и сигнал с первого выхода блока 3 (а, соответственно, и с входа объекта 1) снимается скачком через время, соответствующее задержке элемента 22 (это время выбирается большим времени срабатывания ключа 4). При снятии скачком сигнала с выхода объекта 1 сигнал на его выходе представляет собой переходный процесс. Одновременно со снятием входного сигнала объекта 1 подается сигнал на третий выход бл.ока 3 через управляющий элемент 23 задержки, величина времени задержки которого устанавливается равной to, и начинается процесс измерения выходного сигнала объекта 1. Сигнал с третьего выхода блока 3 поступает на входы элементов 31-34 задержки блока 6.

Элементы задержки устройства работают следующим образом.

Сигнал с первого входа элемента задержки поступает на первый вход реле 47 времени. При подаче сигнала на базу транзистора 53 он открывается, конденсаторы 51 оказываются подключенными параллельно эмиттерно- базовому переходу транзистора 54. Количество конденсаторов 51, подключенных к схеме, определяется количеством сработавших ключей 52, которое в свою очередь определяется количеством сработавших элементов 55 сравнения, определяемым величиной сигнала на втором входе элемента задержки. Конденсаторы 51 оказываются подключенными к эмиттерно-базовому переходу тран5

зистора 54 положительно заряженной пластиной к базе. Транзистор 54 запирается и находится в закрытом состоянии до тех пор, пока конденсаторы 51 не разрядятся через резистор 50. Когда окончится процесс разрядки конденсаторов 51, появляется базовый ток транзистора 54, последний открывается и сигнал на выходе отсутствует. Та.ким образом, выдержка времени зависит от постоянной времени Т RsoCsi. Включение ре0 ле 47 времени совместно с логическими элементами - инвертором 48 и элементом 49 совпадения обеспечивает появление сигналов на выходе элементов задержки с некоторыми запаздываниями по отношению к входному сигналу. Задержки сигналов элементов 31-34 равны соответственно Л{; 2At; ЗАги 4At.

Сигналы с выходов элементов 31-34 задержки поступают на первые входы ключей 35-38, которые открываются и подклю0 чают выход исследуемого объекта 1 через аналого-цифровой преобразователь 2 к входам блоков 40-43 памяти. Блоки 40-43 памяти запоминают только первое значение поступившего на их вход сигнала и не реагируют на последующие, так как на триггеры

5 блоков 40-43 памяти не подаются тактирующие импульсы. Сигналы с выходов блоков 42 и 43 памяти поступают на входы вы- читателя 46, на входе которого вычисляется разность УЗ - у2. Если уз - у-2 О, т. е. измеренные значения выходного сигнала объекта не попали на установившееся значение объекта 1, срабатывает нуль-орган 5 и появляется сигнал на его выходе. Реле 26 срабатывает и замыкает свои нормально разомкнутые контакты, а на обмотку реле 27 поступает через элемент 28 задержки сигнал с первого входа ключа 38, соответствующий моменту подачи на него сигнала. Величина времени задержки элемента 28 выбирается большей времени срабатывания реле 26 и срабатывания блока 46. Реле 27 срабатывает

0 и также замыкает свои нормально разомкнутые контакты, и сигнал поступает на пятый выход блока 3 управления, а лампа 29 не загорается, так как разомкнуты контакты реле 27. Таким образом, на шестом выходе блока 3 появляется сигнал, поступающий на первые входы ключей 7-10, которые срабатывают, и сигналы с выходов блоков 40-43 памяти поступают на входы вычислителя 11.

Одновременно сигнал с шестого выхода блока 3 управления поступает через переключатель 56 на запускающий вход блока 57 местного управления вычислителя 11. На выходах блока 57 последовательно появляются сигналы, которые организуют вычисле- 5 ния коэффициентов Р| и Р2 по формулам (13) и (14) и первого, значения у - 1. При появлении сигнала на первом выходе блока 57 осуществляется вычисление всех

0

5

0

произведений в фор1мулах (13) и (14) и возведения их в квадрат блоками 59-64, при появлении сигнала на втором выходе блока 57 осуществляетея вычисление числителя и знаменателя в формулах (13) и (14) в блоках 65-67, при появлении сигнала на третьем выходе блока 57 на выходах блоков 68 и 69 вычисляются значения PI и Р-з, далее по сигналу с четвертого выхода блока 57 на выходах блоков 70 и 71 вычисляются слагаемые в рекурентной форме (7), где у п-|-1| уо, У| и далее на выходе блока 72 вычисляется значение у -1 У-i, которое через переключатель 74 поступает на второй выход блока 11. На этом работа блока 11 заканчивается.

Сигнал с последнего выхода блока 57 поступает на второй вход блока 91 честного управления блока 12 контроля, который начинает работать и организует дальнейншй процесс вычисления. По сигналу с первого выхода блока 91 зпачения уо и у-i через нормально замкнутые переключатели 78 и 79 записываются в блоках 80 и 81 памяти. По сигналу с второго выхода блока 9i срабатывает блок 87, осуществляющий проверку первого неравенства (8). Если y..-,, на выходе элемента с|)авнения появляется сигнал, который через 9леме}1т ИЛИ 90 поступает на останавливаюнлий вход блока 91 и на третий выход блока 12. Если у- (i, сигнал на выходе блока 87 отсутствует. По- сигналу с четвертого выхода блока 9 сра- батьпзает блок 88, осун ествляющий проверку второго неравенства (8). Если у., на выходе элемента 88 появляется сигнал, который поступает на третий вход элемента 89, который срабат1э1вает при появле11ии сигнала на пятом выходе блока 91. При этом в случае, если у , появ;1яется сипгал на первом выходе эле.мента 89, который по- CTvTiaeT на останавливаюнлий вход блока 91 и на пятый выход блока 12. Если Уп -У--1. на выходе элемента 88 сигнал не появляется и при срабатывании эле.мента 89 появляется сигнал на его втором выходе, так как сигналы на его втором и третьем входах равны нулю. Си нал с второго выхода элемента 89 поступает на вход счетчика 97 блока 13, который фиксирует 1{ачало второго uiara ре1нения ;)екурептного уравнения. При появлении последовательно сигналов на седьмом и восьмом выходах блока 91 на выходе блока 84 вычисляется з ачение , а npvi появлении сигнала на девятом выходе блока 91 срабатывают переключатели 78 к 79, на входах которых включены ф Орм}Ц) юп.1ие RC.-neno4KH, что обеспечивает длите,пьност их срабатыва 1ия, необходимую для прохождения сигналов че)ез . После формирования сигнала на .девятом выходе блок 91 благодаря использованию в нем кольцевого счетчика автоматически начинает новый цикл работы с подачи сигнала на первый

5

выход, по которому значения с блока 81 памяти переносятся в блок 80 памяти, а значение у - 2 с выхода блока 84 через переключатель 85 заносится в блок 79 (на . первых входах блоков 78 и 79 включены формирующее цепочки, позволяющие разнести по времени их срабатывания, т. е. сначала происходит считывание информации из блока 81, а затем запись в него). Далее происходит аналогичный цикл проверки

0 неравенств (8) и (0) на втором шаге, и так далее до тех пор, пока одно из неравенств не будет выполняться, что еоответствует появлению сигналов на третьем или на пятом выходах блока 12. При появлении сигналов на этих выходах прекращается работа блока 12 и начинает работать второй вычислитель 13, так как запускаются блоки 92 и 93. Если вьпюлняется неравенство (8), сигнал появляется на пятом выходе блока 12 и начинает работать блок 92, а в переклюп чателе 101 второй вход подключается к выходу. При этом при последовательном появлении сигналов на первом-пятом выходах блока 92 .местного управления последова- телы-;о вычисляется на блока 96 величина Т по формуле (9), на выходе бло5 ка 94 - величина в и на выходе блока 102 т. li + Д1 --в.

Если же выполняется неравенство (10), .запускается блок 93 местного управления, а в переключателе 10 третий вход подключается к его выходу, при этом на выходе

О-

б.пока 100 вычисляется величина по формуле (10), а затем на выходе блока 102 - величина т In -f At - в.

Процесс вычисления чистого запаздывания объекта 1, передаточная функция которого описывается выражением (1), аналоги чен описанному выше процессу за кск.лю- чепием того, что включатель 30 блока 3 устанавливается в положение «1. При этом переключатели 56. 74-76 блока 11 не срабатывают к но сигналу с шестого выхода блоfj ка 3 запускается блок 58, по сигналам которого на выходе блока 73 вычисляется значение р, а на выходе блока 77 - величина 1, которые через переключатели 74 и 76 fiocTynaiOT на выходы блока 11, а сигнал на запуск блока 91 поступает через переклю5 чате.чь 85 с третьего выхода блока 58. В блоке 12 переключатель 85 не срабатывает и на его выход поступает сигнал с выхода блока 83, прн этом в блоке 2 ре1нается ре- курентное уравнение (6). В блоке 6 пере,. ключатели 39, 44 и 45 также не срабатывают и на второк выход блока 6 поступает сигнал с первого входа второго ключа, а на входы вычитателя - сигналы с выходов первого и второго блоков 40 и 41 памяти, что обеспечивает контроль только двух необходимых

5 для работы устройства значений выходного сигнала I.

В случае, когда промежутки времени At и to Bbi6paF;b неправильно и значения у: попадают на установившийся процесс, разность УЗ - У2 или У| - УО равна нулю. В результате на выходе нуль-органа 5 сигнал не появляется и реле 26 блока 3 не срабатывает, при этом ключи 7-10 и блок 11 не запускаются, о чем можно судить по загоранию индикаторной лампы 29. В этом случае необходимо уменьшить величину сигналов на выходах масштабных блоков 24 и 25 и повторить эксперимент снова. Для чего необходимо нажать кнопку «Сброс 17 блока 3 управления, при этом снимается сигнал с обмотки первого реле 15 и поступает сигнал на седьмой выход блока 3, по которому обнуляются блоки устройства.

Реле 15 замыкает свои нормально замкнутые контакты и подается сигнал на вход объекта 1, который возвраш,ается в исходное начальное состояние. Снимаются также сигналы с элементов 31-34 задержки и возвращаются в исходное состояние блоки 35- 38, а лампа 29 гаснет, так как с реле 26 снимается сигнал.

Для предотвращения пуска устройства прежде, чем установится начальное состояние объекта 1, в блоке 3 управления предусмотрена цепь, содержащая реле 18 и 19 и элемент 20 задержки, который работает следующим образом. При нажатии кнопки «Сброс 17 подается сигнал на обмотку реле 18, которое срабатывает, блокирует кнопку 17 размыкает контакты в цепи питания реле 15, предотвращая возможность нового пуска. Одновременно сигнал с кнопки 17 поступает на вход элемента 20 задержки, сигнал на выходе которого появляется через время, заведомо больщее, чем время переходных процессов в исследуемом объекте 1. Сигнал с выхода элемента 20 задержки поступает на обмотку реле 19, которое размыкает свои нормально замкнутые контакты и снимает сигнал с обмотки реле 18, которое замыкает контакты в линии обмотки первого реле 15, и теперь возможен новый пуск устройства.

Формула изобретения

Устройство для измерения чистого запаздывания инерционного звена, содержащее нуль-орган, два ключа и измерительный блок, отличающееся тем, чтр, с целью повышения точности измерения, в него введены аналого-цифровой преобразователь, блок управления, блок контроля, три ключа и два вычислителя, причем первый выход блока

управления является выходом устройства, второй выход соединен с первым входом первого ключа, третий и четвертый выходы- с первым и вторым входами измерительного блока и второго вычислителя соответственно, пятый выход - с третьим входом измерительного блока и первыми входами первого вычислителя и блока контроля, шестой выход - с первыми входами с второго по пятый ключи и вторым входом первого вычислителя, первый вход блока управления через

нуль-орган соединен с первым выходом измерительного блока, а второй вход - с вторым выходом измерительного блока, вход устройства соединен через аналого-цифровой преобразователь с четвертым входом измерительного блока, а через первый ключ -

с вторым входом блока контроля и третьим входом второго вычислителя, с третьего по шестой выходы измерительного блока через ключи соединены с соответствующими входами первого вычислителя, третий вход которого соединен с третьим входом блока контроля, с четвертого по седьмой входы блока контроля соединены с соответствующими четырьмя выходами первого вычислителя, а с первого по пятый выходы - соответственно с четвертого по восьмой входами второго вычислителя, девятый вход которого соединен с седьмым входом первого вычислителя, восьмым входом блока контроля, пятым входом измерительного блока и седьмым выходом блока управления, а выход второго вычислителя является вторым выходом устройства.

y,(t)

Фиг. 2

| название | год | авторы | номер документа |

|---|---|---|---|

| Способ определения параметров передаточной функции линейного динамического звена и устройство для его осуществления | 1986 |

|

SU1377826A1 |

| Устройство для определения параметров динамического звена | 1987 |

|

SU1478194A1 |

| Устройство для определения параметров динамического звена | 1983 |

|

SU1160372A1 |

| Устройство для определения параметров передаточной функции линейного динамического объекта | 1988 |

|

SU1585782A1 |

| Устройство для определения коэффициента усиления динамического объекта | 1984 |

|

SU1211700A1 |

| Анализатор частотных характеристик | 1985 |

|

SU1307373A1 |

| Адаптивная система регулирования объекта с нестационарной характеристикой,например,дуговой сталеплавильной печи | 1983 |

|

SU1068891A1 |

| Устройство для определения параметров линейных динамических объектов | 1991 |

|

SU1837259A1 |

| Адаптивное регулирующее устройство | 1982 |

|

SU1064271A1 |

| Устройство для определения параметров динамического звена второго порядка | 1984 |

|

SU1231489A1 |

Изобретение относится к области экспериментального определения динамических характеристик инерционных объектов и может быть использовано при исследовании и наладке систем автоматического регулирования. Устройство позволяет определять величину чистого запаздывания динамических звеньев первого и второго порядка по дискретным значениям его переходной характеристики. Повышенная точность измерения достигается тем, что величина чистого запаздывания вычисляется по значениям переходной характеристики на ее участке при значительных амплитудах сигналов, когда величина помехи и нелинейностей гораздо меньше величин измеренных сигналов,а также не сказывается инерционность элементов устройства. Устройство содержит блок управления, аналого-цифровой преобразователь, измерительный и вычислительные блоки, ключевые элементы, нуль-орган и блок контроля. 10 ил. Ш (Л ю оо О5 4;: СА:)

гп I-I гН

-HIFi

,2

ф1/г.6

/7(7

| Устройство для определения динамических характеристик линейных объектов | 1974 |

|

SU554525A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

| Устройство для измерения параметров инерционных звеньев систем регулирования | 1978 |

|

SU694839A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

Авторы

Даты

1986-06-07—Публикация

1984-11-19—Подача