Изобретение относится к вычислительной технике и может быть использовано в процессорах ЭВМ и систем, ориентированных на переработку больших массивов разнородной информации.

Цель изобретения - повышение быстродействия устройства.

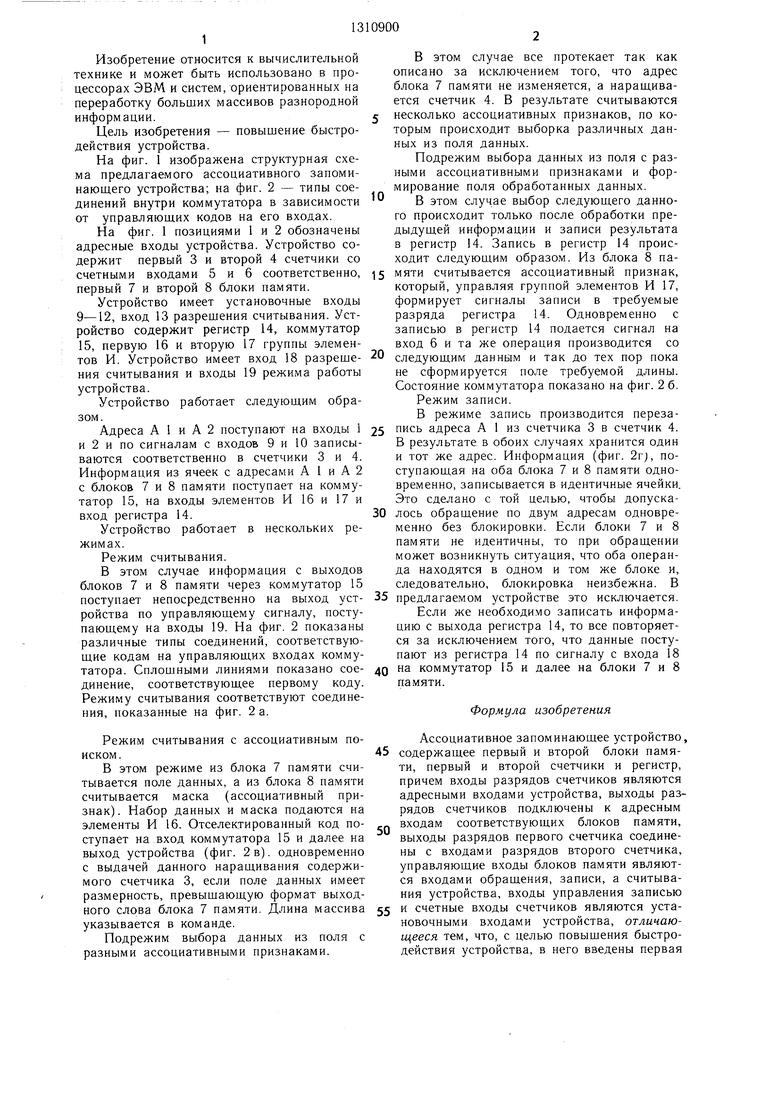

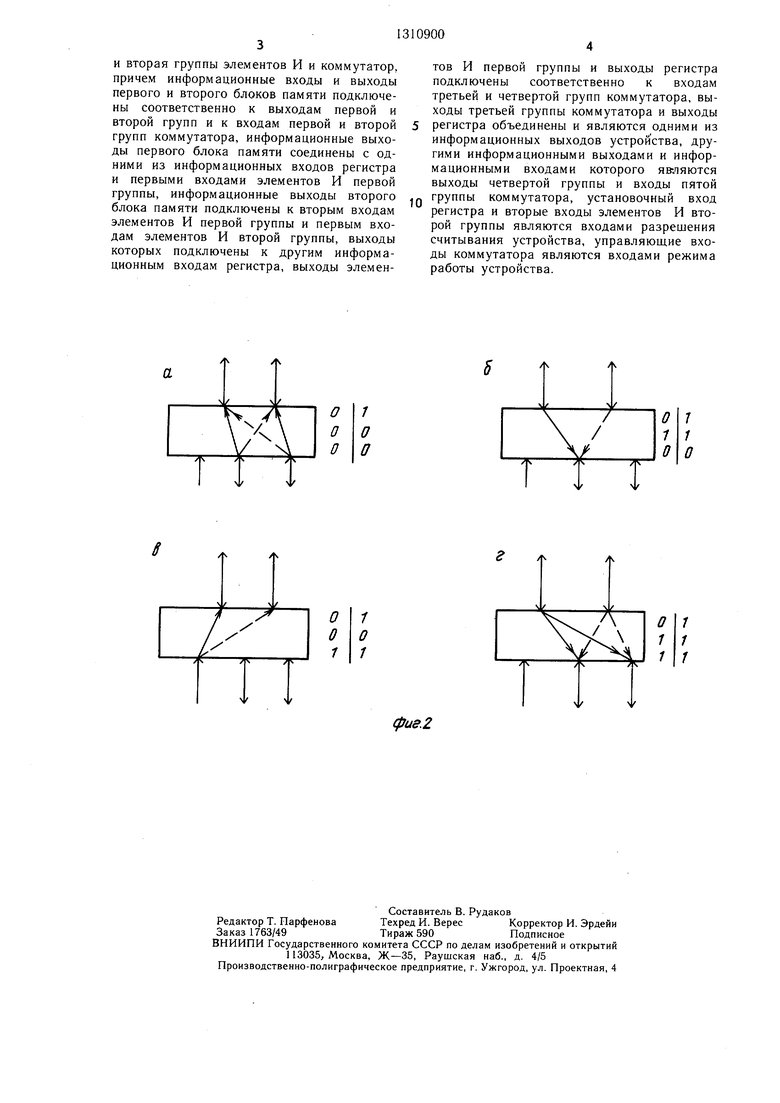

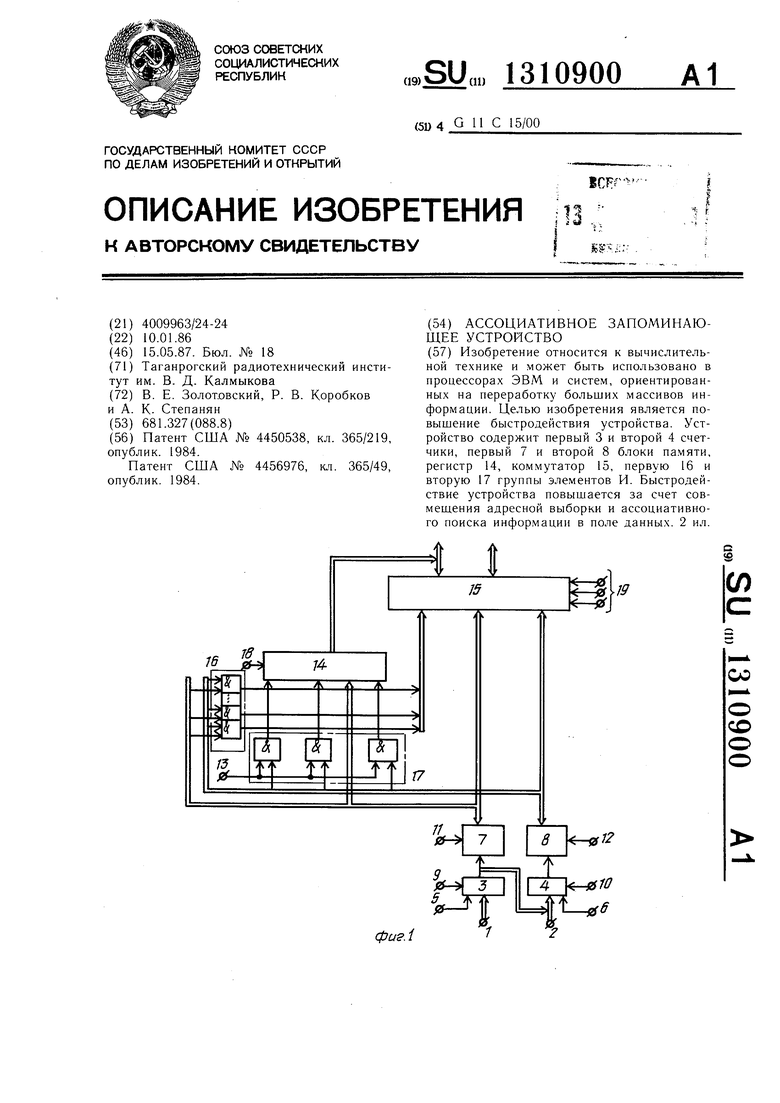

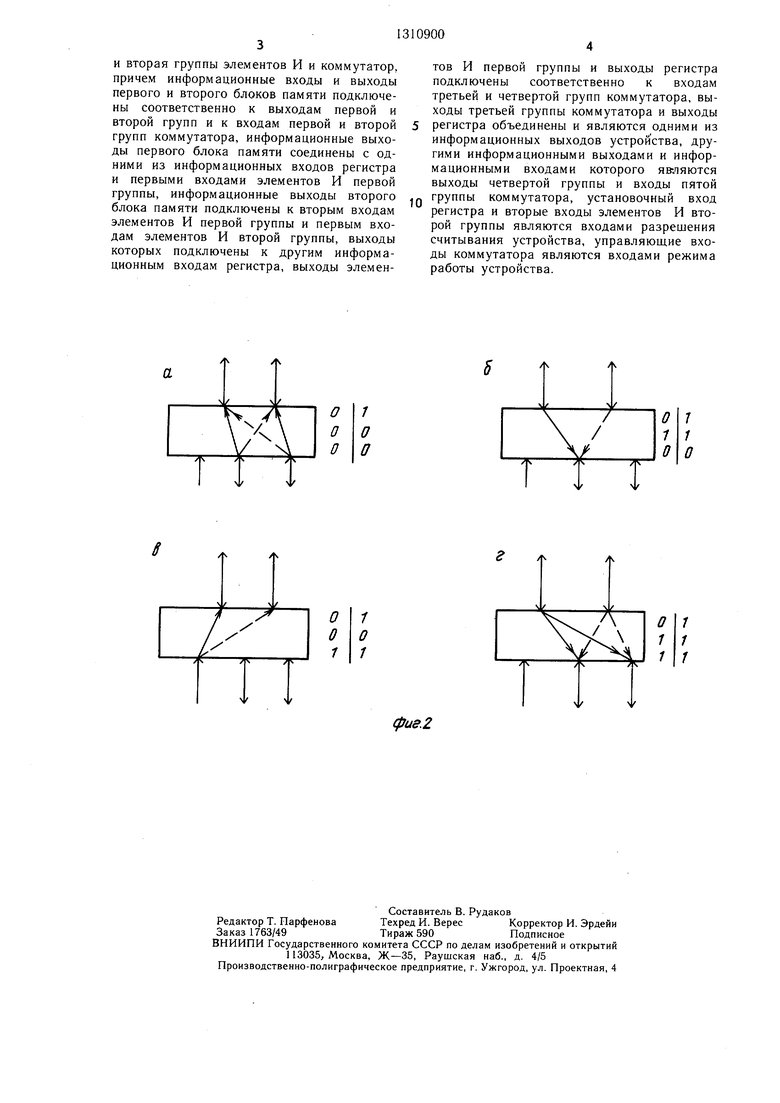

На фиг. 1 изображена структурная схема предлагаемого ассоциативного запоминающего устройства; на фиг. 2 - типы соединений внутри коммутатора в зависимости от управляющих кодов на его входах.

На фиг. 1 позициями 1 и 2 обозначены адресные входы устройства. Устройство содержит первый 3 и второй 4 счетчики со счетными входами 5 и 6 соответственно, первый 7 и второй 8 блоки памяти.

Устройство имеет установочные входы 9-12, вход 13 разрешения считывания. Устройство содержит регистр 14, коммутатор 15, первую 16 и вторую 17 группы элемен10

15

В этом случае все протекает так как описано за исключением того, что адрес блока 7 памяти не изменяется, а наращивается счетчик 4. В результате считываются несколько ассоциативных признаков, по которым происходит выборка различных данных из поля данных.

Подрежим выбора данных из поля с разными ассоциативными признаками и формирование поля обработанных данных.

В этом случае выбор следующего данного происходит только после обработки предыдущей информации и записи результата в регистр 14. Запись в регистр 14 происходит следующим образом. Из блока 8 памяти считывается ассоциативный признак, который, управляя группой элементов И 17, формирует сигналы записи в требуемые разряда регистра 14. Одновременно с записью в регистр 14 подается сигнал на вход 6 и та же операция производится со

тов И. Устройство имеет вход 18 разреше- следующим данным и так до тех пор пока ния считывания и входы 19 режима работы не сформируется поле требуемой длины.

Состояние коммутатора показано на фиг. 2 б.

устройства.

Устройство работает следующим образом.

Адреса А 1 и А 2 поступают на входы 1 и 2 и по сигналам с входов 9 и 10 записываются соответственно в счетчики 3 и 4. Информация из ячеек с адресами А 1 и А 2 с блоков 7 и 8 памяти поступает на коммутатор 15, на входы элементов И 16 и 17 и вход регистра 14.

Устройство работает в нескольких режимах.

Режим считывания.

В этом случае информация с выходов блоков 7 и 8 памяти через коммутатор 15 поступает непосредственно на выход устройства по управляющему сигналу, поступающему на входы 19. На фиг. 2 показаны различные типы соединений, соответствующие кодам на управляющих входах коммутатора. Сплошными линиями показано сое- динение, соответствующее первому коду. Режиму считывания соответствуют соединения, показанные на фиг. 2 а.

Режим считывания с ассоциативным поиском.

В этом режиме из блока 7 памяти считывается поле данных, а из блока 8 памяти считывается маска (ассоциативный признак). Набор данных и маска подаются на элементы И 16. Отселектированный код поступает на вход коммутатора 15 и далее на выход устройства (фиг. 2 в), одновременно с выдачей данного наращивания содержимого счетчика 3, если поле данных имеет размерность, превышающую формат выходного слова блока 7 памяти. Длина массива указывается в команде.

Подрежим выбора данных из поля с разными ассоциативными признаками.

5

В этом случае все протекает так как описано за исключением того, что адрес блока 7 памяти не изменяется, а наращивается счетчик 4. В результате считываются несколько ассоциативных признаков, по которым происходит выборка различных данных из поля данных.

Подрежим выбора данных из поля с разными ассоциативными признаками и формирование поля обработанных данных.

В этом случае выбор следующего данного происходит только после обработки предыдущей информации и записи результата в регистр 14. Запись в регистр 14 происходит следующим образом. Из блока 8 памяти считывается ассоциативный признак, который, управляя группой элементов И 17, формирует сигналы записи в требуемые разряда регистра 14. Одновременно с записью в регистр 14 подается сигнал на вход 6 и та же операция производится со

следующим данным и так до тех пор пока не сформируется поле требуемой длины.

5

дд

Состояние коммутатора показано на фиг. 2 б.

Режим записи.

В режиме запись производится перезапись адреса А 1 из счетчика 3 в счетчик 4. В результате в обоих случаях хранится один и тот же адрес. Информация (фиг. 2г, поступающая на оба блока 7 и 8 памяти одновременно, запись вается в идентичные ячейки. Это сделано с той целью, чтобы допуска- 30 лось обращение по двум адресам одновременно без блокировки. Если блоки 7 и 8 памяти не идентичны, то при обращении может возникнуть ситуация, что оба операнда находятся в одном и том же блоке и, следовательно, блокировка неизбежна. В предлагаемом устройстве это исключается.

35

Если же необходимо записать информацию с выхода регистра 14, то все повторяется за исключением того, что данные поступают из регистра 14 по сигналу с входа 18 на коммутатор 15 и далее на блоки 7 и 8 памяти.

Формула изобретения

Ассоциативное запоминающее устройство, содержащее первый и второй блоки памяти, первый и второй счетчики и регистр, причем входы разрядов счетчиков являются адресными входами устройства, выходы разрядов счетчиков подключены к адресным входам соответствующих блоков памяти, выходы разрядов первого счетчика соединены с входами разрядов второго счетчика, управляющие входы блоков памяти являются входами обращения, записи, а считывания устройства, входы управления записью и счетные входы счетчиков являются установочными входами устройства, отличающееся тем, что, с целью повыщения быстродействия устройства, в него введены первая

и вторая группы элементов И и коммутатор, причем информационные входы и выходы первого и второго блоков памяти подключены соответственно к выходам первой и второй групп и к входам первой и второй групп коммутатора, информационные выходы первого блока памяти соединены с одними из информационных входов регистра и первыми входами элементов И первой

тов И первой группы и выходы регистра подключены соответственно к входам третьей и четвертой групп коммутатора, выходы третьей группы коммутатора и выходы регистра объединены и являются одними из информационных выходов устрой ства, другими информационными выходами и информационными входами которого яв-ляются выходы четвертой группы и входы пятой

группы, информационные выходы второго группы коммутатора, установочный вход блока памяти подключены к вторым входамрегистра и вторые входы элементов И второй группы являются входами разрешения считывания устройства, управляющие входы коммутатора являются входами режима работы устройства.

элементов И первой группы и первым входам элементов И второй группы, выходы которых подключены к другим информационным входам регистра, выходы элементов И первой группы и выходы регистра подключены соответственно к входам третьей и четвертой групп коммутатора, выходы третьей группы коммутатора и выходы регистра объединены и являются одними из информационных выходов устрой ства, другими информационными выходами и информационными входами которого яв-ляются выходы четвертой группы и входы пятой

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство | 1980 |

|

SU942141A2 |

| Устройство для моделирования структурно-сложных объектов | 1984 |

|

SU1234845A1 |

| Устройство для фиксации трассы выполнения программы | 1983 |

|

SU1136170A1 |

| Устройство для поиска информации в памяти | 1985 |

|

SU1309041A1 |

| Устройство для отладки программ | 1983 |

|

SU1290334A1 |

| Ассоциативно-адресное оперативное запоминающее устройство | 1987 |

|

SU1451773A1 |

| Устройство для моделирования графов | 1983 |

|

SU1126967A1 |

| Ассоциативное оперативное запоминающее устройство | 1989 |

|

SU1714682A1 |

| Ассоциативное оперативное запоминающее устройство | 1988 |

|

SU1667155A1 |

| Центральный процессор | 1991 |

|

SU1804645A3 |

Изобретение относится к вычислительной технике и может быть использовано в процессорах ЭВМ и систем, ориентированных на переработку больших массивов информации. Целью изобретения является повышение быстродействия устройства. Устройство содержит первый 3 и второй 4 счетчики, первый 7 и второй 8 блоки памяти, регистр 14, коммутатор 15, первую 16 и вторую 17 группы элементов И. Быстродействие устройства повышается за счет сов- мешения адресной выборки и ассоциативного поиска информации в поле данных. 2 ил. о о

0

т

о

о 1

| Патент США № 4450538, кл | |||

| Станок для нарезания зубьев на гребнях | 1921 |

|

SU365A1 |

| Колосниковая решетка с чередующимися неподвижными и движущимися возвратно-поступательно колосниками | 1917 |

|

SU1984A1 |

| Патент США № 4456976, кл | |||

| Станок для нарезания зубьев на гребнях | 1921 |

|

SU365A1 |

| Колосниковая решетка с чередующимися неподвижными и движущимися возвратно-поступательно колосниками | 1917 |

|

SU1984A1 |

Авторы

Даты

1987-05-15—Публикация

1986-01-10—Подача