113

Изобретение относится к области вычислительной техники и может быть использовано в вычислительных системах для сопряжения каналов ввода-вывода ЭВМ с внешними устройствами (абонентами).

Цель изобретения заключается в повышении скорости обмена информацией и расширении функциональных возмож- ностей устройства за счет обеспечения возможности изменения формата принимаемых и передаваемых данных.

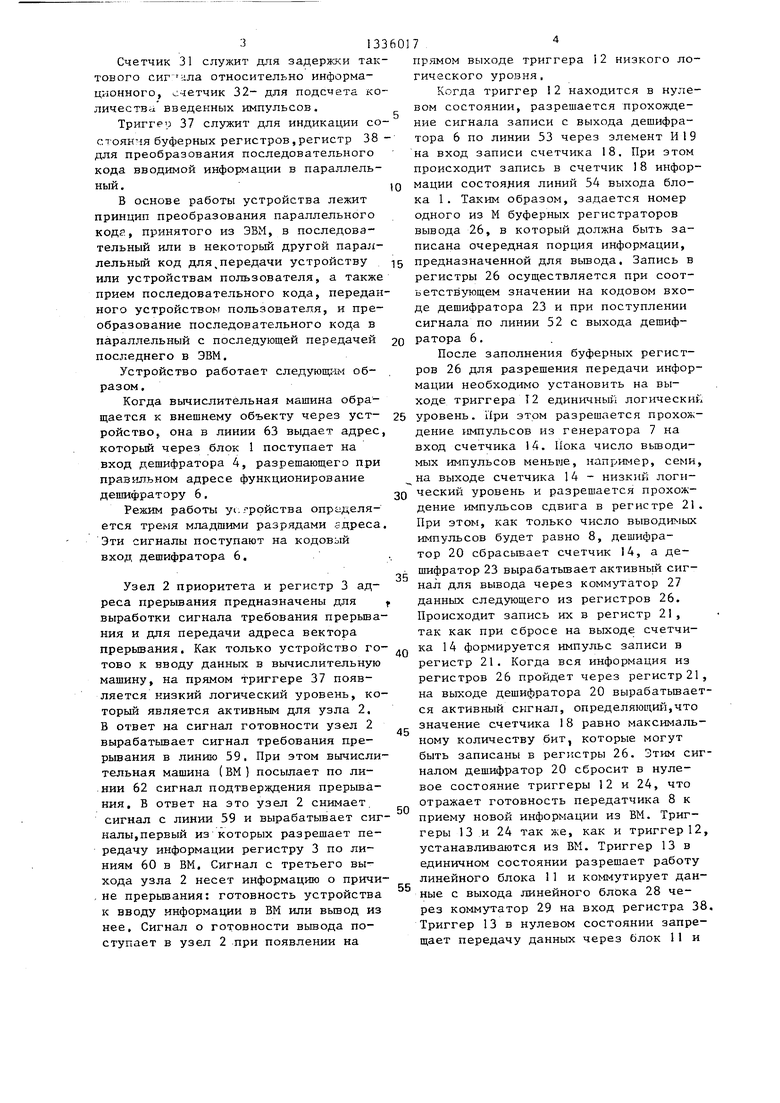

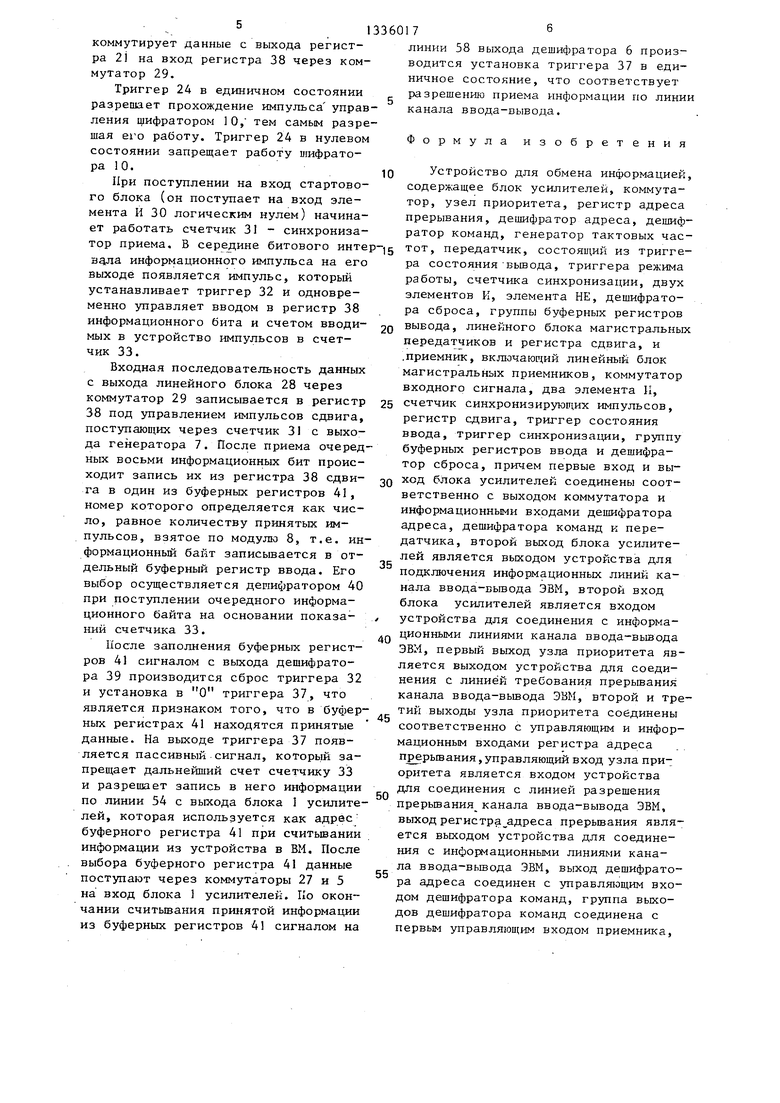

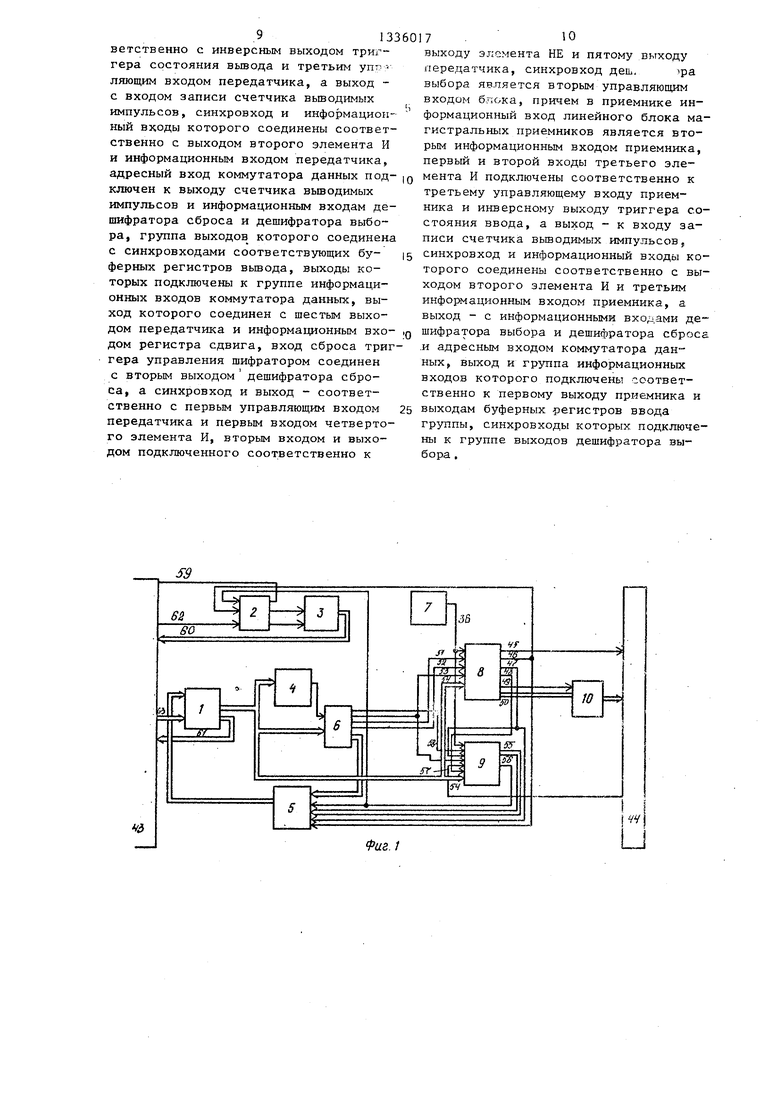

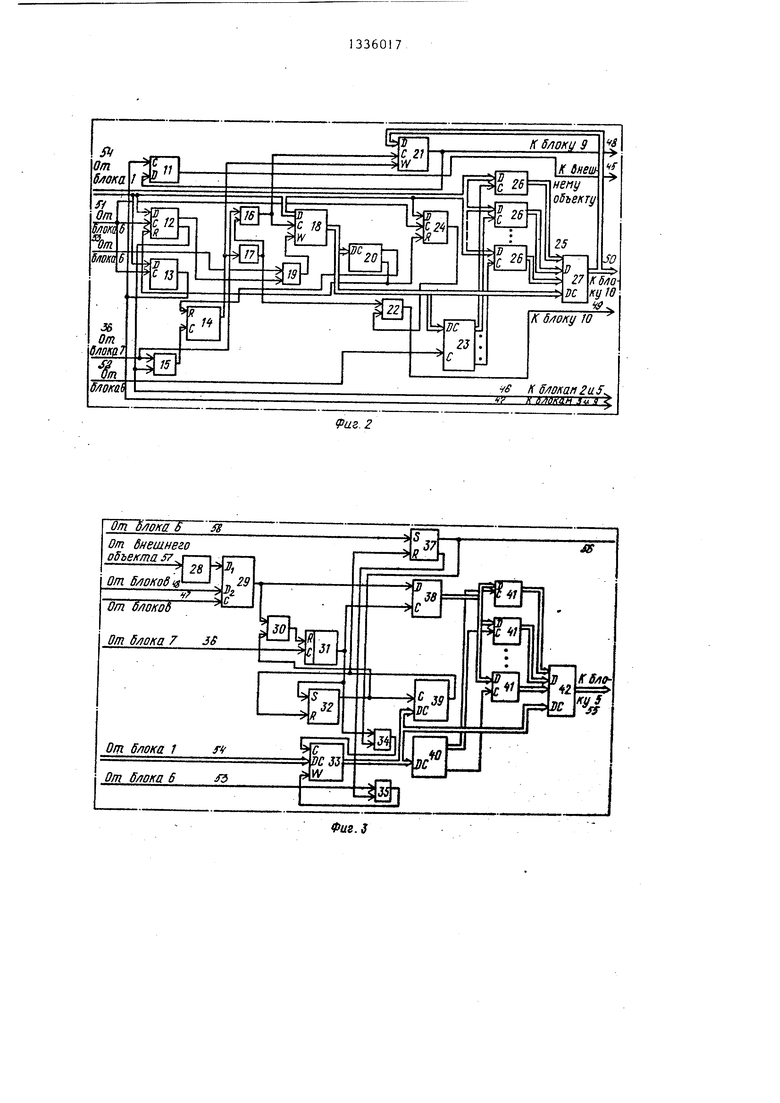

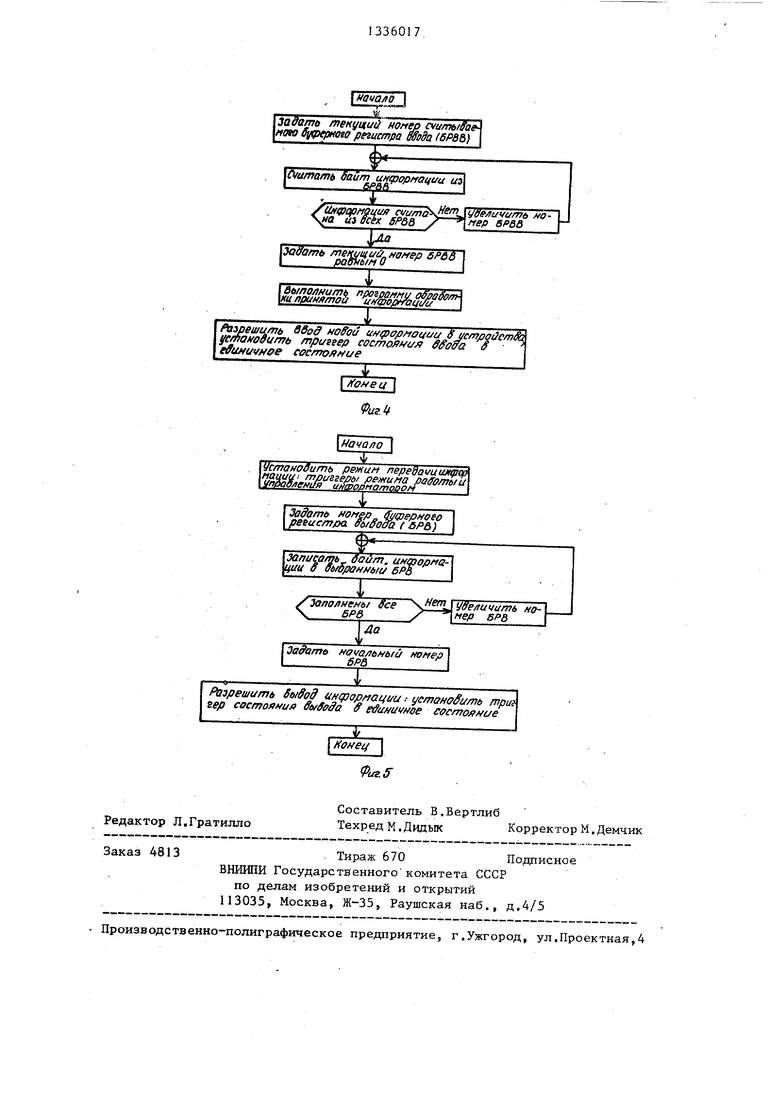

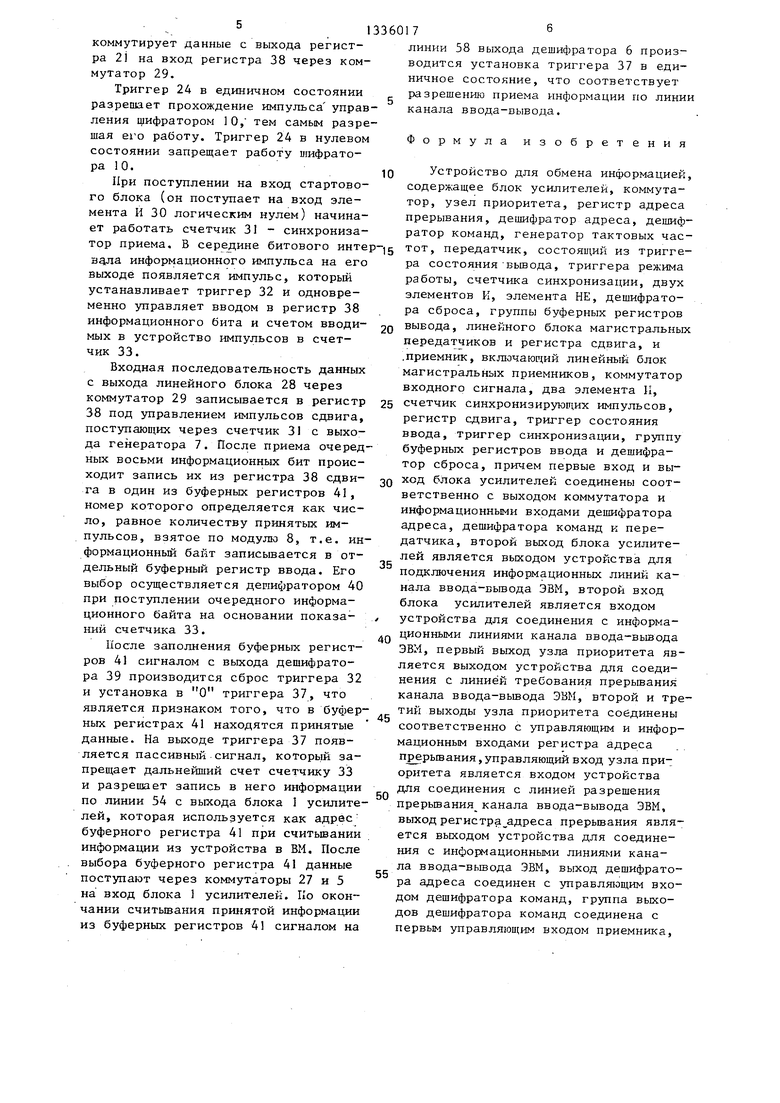

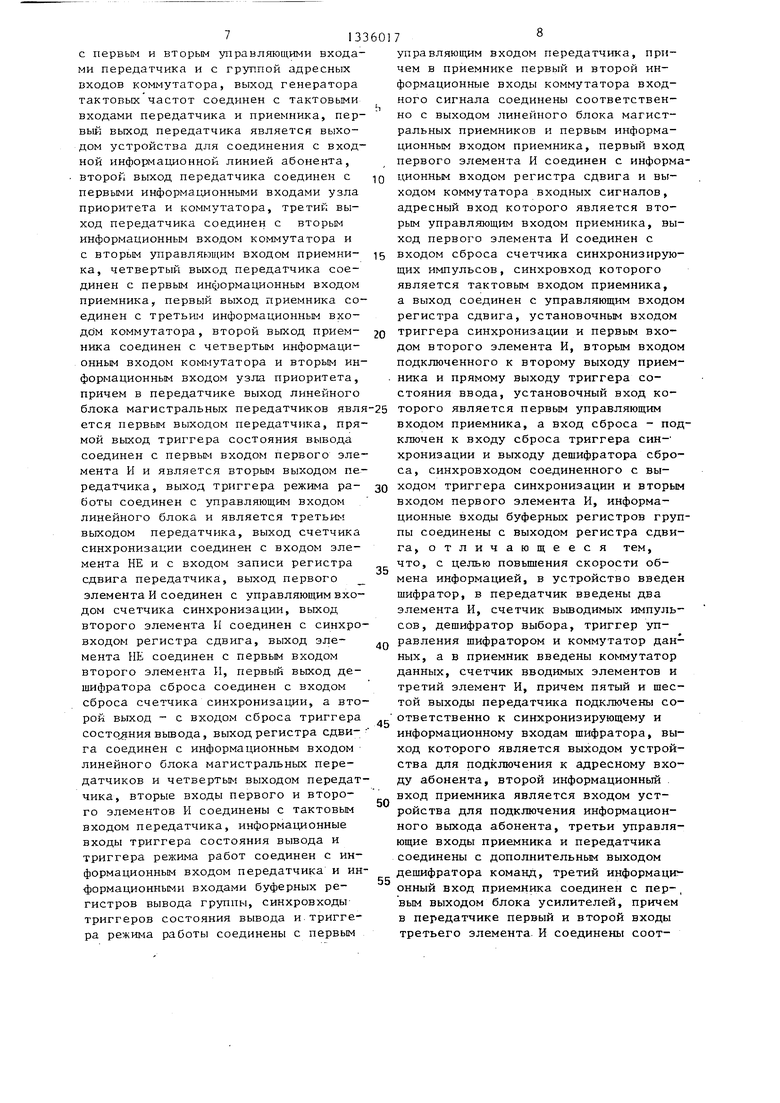

На фиг.1 представлена блок-схема устройства; на фиг;2 и 3 - функцио- нальные схемы передатчика и приемника; соответственно; на фиг. 4 и 5 - блок-схемы алгоритмов обслуживания циклов ввода и вьшода информации.

Устройство (фиг,) содержит блок усилителей, узел 2 приоритета, регистр 3 адреса прерьшания, дешифратор 4 адреса, коммутатор 5, дешифратор 6 команд, генератор 7 тактовьш частот, передатчик 8, приемник 9 и шифратор 10,

Передатчик 8 (фиг.2) содержит линейный блок 1I магистральных передатчиков, триггер 12 состояний вьшода, триггер 3 режима работы, счетчик 14 синхронизации, первый, второй элементы И 15 и 16, элемент НЕ 17, счетчик 18 вьшодимых импульсов, третий элемент И 19, дешифратор 20 сброса, регистр 21 сдвига, четвертый элемент И 22, дешифратор 23 выброса, триггер 24 управления шифратором, выходы 25 буферных регистров 26 вьшода группы, коммутатор 27 данных,

Приемник 9 содержит (фнг.З) линейный блок 28 магистральных приемников коммутатор 29 входного сигнала, первый элемент И 30, счетчик 31 синхронизирующих импульсов, триггер 32 син хронизации, счетчик 33 вьюодимых им- пульсов, второй и третий элементы И 34 и 35 тактовый вход 36 приемника, триггер 37 состояния ввода, per: гистр 38 сдвига, дешифратор 39 сброса, дешифратор 40 выбора, буферные регистры 40 выбора, буферные регистры 41 ввода группы, коммутатор 42 данных.

На чертежах обозначены также канал 43 ввода-вьшода ЭВМ и абонент 44 выходы 45-50 и входы 51-54 передатчика 8, выходы 55 и 56 и первые информационный и управляюпо й входы 57

01

Q

5

0 5

о Q

0

5

72

и 58 приемника 9, линии 59-63 связей устройства с каналом 43.

Блок 1 осуществляет Согласование уровней сигналов канала 43 и устройства.

Узел 2 приоритета предназначен для выработки сигнала требования прерьшания и управляющих сигналов для регистра 3 адреса прерьшания,который служит для передачи в ЦВМ адреса вектора прерывания.

Дешифратор 6 команд определяет режим работы устройства в зависимости от адреса обращения вычислительной машины к устройству.

Генератор 4 тактовых частот вклю- . чает в себя, например, стабилизированный кварцем генератор и делитель частоты, реализуемый на интегральных схемах счетчиков, и обеспечивает варьирование скорости обмена информацией через канал обмена.

Передатчик 8 служит для вьшода информации, а.приемник 9 - для ввода информации в устройство от абонента.

Шифратор 10 может быть.реализован в виде, например, постоянного запоминающего устройства и позволяет передавать закодированную информацию в одно или несколько устройств.

Линейный блок I1 передатчика служит для согласования уровней сигналов, передаваемых из устройства к внешнему объекту.

Счетчик 18 служит дли подсчета количества импульсов, переданных из устройства.

Дешифратор 20 сброса служит для обеспечения циклической работы счетчика 14 и всего передатчика 8 в целом.

Регистр 21 сдвига передатчика слу- лсит для преобразования параллельного кода в последовательный.

Триггер 24 управления шифратором служит для выработки управляющего сигнала для блока 10. Если триггер установлен в единичное состояние, то тем самым разрешается прохождение разрешающего сигнала на выход 49.

Буферные регистры 26 (всего М ре- , гистров) служат для хранения информации, предназначенной для передачи из вычислительной машины во внешнее устройство .

Линейный блок 28 служит для согласования сигналов, принимаемых устройством от внешнего устройства.

13

Счетчик 31 служит для задержки тактового сиг --1ла относительно информационного, счетчик 32- для подсчета количества введенных импульсов.

Триггер 37 служит для индикации состояния буферных регистров,регистр 38 для преобразования последовательного кода вводимой информации в параллельный .

В основе работы устройства лежит принцип преобразования параллельного кода, принятого из ЭВМ, в последовательный или в некоторьш другой параллельный код для,передачи устройству или устройствам пользователя, а также прием последовательного кода, переданного устройством пользователя, и преобразование последовательного кода в параллельный с последующей передачей последнего в ЭВМ.

Устройство работает следующим образом ,

Когда вычислительная машина обращается к внешнему объекту через уст- ройство. она в линии 63 вьщает адрес которьй через блок 1 поступает на вход дешифратора 4, разрешающего при npassfflbHOM адресе функционирование дешифратору 6.

Режим работы yt. ройства определяется тремя младшими разрядами адреса Эти сигналы поступают на кодовый вход дешифратора 6.

Узел 2 приоритета и регистр 3 адреса прерывания предназначены для выработки сигнала требования прерьюа- ния и для передачи адреса вектора прерьшания. Как только устройство го- тово к вводу данных в вычислительную машину, на прямом триггере 37 появляется низкий логический уровень, который является активным для узла 2. В ответ на сигнал готовности узел 2 вырабатьтает сигнал требования прерывания в линию 59, При этом вычислительная машина (ВМ ) посылает по линии 62 сигнал подтверждения прерывания, В ответ на это узел 2 снимает, сигнал с линии 59 и вырабатьтает сигналы,первый из которых разрешает передачу информации регистру 3 по линиям 60 в ВМ, Сигнал с третьего выхода узла 2 несет информацию о причи- , не прерьшания: готовность устройства к вводу информации в ВМ или вьшод из нее. Сигнал о готовности вьшода поступает в узел 2 при появлении на

5 0

5

...

5

0

5

7

прямом выходе триггера 12 низкого логического уровня.

Когда триггер 12 находится в нулевом состоянии, разрешается прохождение сигнала записи с выхода дешифратора 6 по линии 53 через элемент И 19 на вход записи счетчика 18. При этом происходит запись в счетчик 18 информации состояния линий 54 выхода блока 1. Таким образом, задается номер одного из М буферных регистраторов вывода 26, в который должна быть записана очередная порция информации, предназначенной для вьшода. Запись в регистры 26 осуществляется при соответствующем значении на кодовом входе дешифратора 23 и при поступлении сигнала по линии 52с выхода дешифратора 6.

После заполнения буферных регистров 26 для разрешения передачи информации необходимо установить на выходе триггера 12 единичный логический уровень. При этом разрешается прохождение импульсов из генератора 7 на вход счетчика 14. Пока число вьшоди- мых импульсов меньше, например, семи, на выходе счетчика 14 - низкий логический уровень и разрешается прохождение импульсов сдвига в регистре 21. При этоь, как только число выводимых импульсов будет равно 8, дешифратор 20 сбрасывает счетчик 14, а дешифратор 23 вырабатьшает активный сигнал для вывода через коммутатор 27 данных следующего из регистров 26. Происходит запись их в регистр 21, так как при сбросе на выходе счетчика 14 формируется импульс записи в регистр 21. Когда вся информация из регистров 26 пройдет через регистр 21, на выходе дешифратора 20 вырабатьшает- ся активный сигнал, определяющий,что значение счетчика 18 равно максимальному количеству бит, которые могут быть записаны в регистры 26. Этим сигналом дешифратор 20 сбросит в нулевое состояние триггеры 12 и 24, что отражает готовность передатчика 8 к приему новой информации из ВМ. Триггеры 13 и 24 так же, как и триггер 12, устанавливаются из ВМ. Триггер 13 в единичном состоянии разрешает работу линейного блока 11 и коммутирует данные с выхода линейного блока 28 через коммутатор 29 на вход регистра 38. Триггер 13 в нулевом состоянии запрещает передачу данных через блок 11 и

коммутирует данные с выхода регистра 21 на вход регистра 38 через коммутатор 29.

Триггер 24 в единичном состоянии разрешает прохождение импульса управления шифратором 10, тем самым разрешая ei o работу. Триггер 24 в нулевом состоянии запрещает работу шифратора 10.

При поступлении на вход стартового блока (он поступает на вход элемента И 30 логическим нулем) начинает работать счетчик 31 - синхрониза20

25

30

35

тор приема. В битового интер- д тот, передатчик, состоящий из тригге- В4ла информационного импульса на его Выходе появляется импульс, который устанавливает триггер 32 и одновременно управляет вводом в регистр 38 информационного бита и счетом вводимых в устройство импульсов в счетчик 33.

Входная последовательность данных с выхода линейного блока 28 через коммутатор 29 записывается в регистр 38 под управлением импульсов сдвига, поступающих через счетчик 31 с выхода генератора 7. После приема очередных восьми информационных бит происходит запись их из регистра 38 сдвига в один из буферных регистров 41, номер которого определяется как число, равное количеству прршятых импульсов, взятое по модулю 8, т.е. информационный байт записывается в отдельный буферный регистр ввода. Его выбор осуществляется дешифратором 40 при поступлении очередного информационного байта на основании показаний счетчика 33.

После заполнения буферных регистров 41 сигналом с выхода дешифратора 39 производится сброс триггера 32 и установка в О триггера 37, что является признаком того, что в буферных регистрах 41 находятся принятые данные. На выходе триггера 37 появляется пассивный сигнал, который запрещает дальнейший счет счетчику 33 и разрешает запись в него информации по линии 54 с выхода блока 1 усилителей, которая используется как адрес буферного регистра 41 при считьюании информации из устройства в ВМ. После выбора буферного регистра 41 данные поступают через коммутаторы 27 и 5 на вход блока 1 усилителей. По окончании считьюания принятой информации из буферных регистров 41 сигналом на

40

45

50

55

ра состояния вьшода, триггера режима работы, счетчика синхронизации, двух элементов И, элемента НЕ, дешифратора сброса, группы буферных регистров вывода, линейного блока магистральных передатчиков и регистра сдвига, и .приемник, включаюр;ий линейный блок магистральных приемников, коммутатор входного сигнала, два элемента И, счетчик синхронизирующих импульсов, регистр сдвига, триггер состояния ввода. Триггер синхронизации, группу буферных регистров ввода и дешифратор сброса, причем первые вход и выход блока усилителей соединены соответственно с выходом коммутатора и информационными входами дешифратора адреса, дешифратора команд и передатчика, второй выход блока усилителей является выходом устройства для подключения информационных линий канала ввода-БЬшода ЭВМ, второй вход блока усилителей является входом устройства для соединения с информационными линиями канала ввода-вьшода ЭВМ, первый выход узла приоритета является выходом устройства для соединения с линией требования прерывания канала ввода-вьшода ЭйМ, второй и третий выходы узла приоритета соединены соответственно с управляющим и информационным входами регистра адреса прерьшания, управляющий вход узла приоритета является входом устройства для соединения с линией разрешения прерьтания канала ввода-вывода ЭВМ, выход регистра адреса прерьшания является выходом устройства для соединения с инфогмационными линиями канала ввода-вьшода ЭВМ, выход дешифратора адреса соединен с управляющим входом дешифратора команд, группа выходов дешифратора команд соединена с первым управляющим входом приемника.

линии 58 выхода дешифратора 6 производится установка триггера 37 в единичное состояние, что соответствует разрешению приема информации по линии канала ввода-вывода.

Формула изобретения

Устройство для обмена информацией, содержащее блок усилителей, коммутатор, узел приоритета, регистр адреса прерывания, дешифратор адреса, дешифратор команд, генератор тактовых час

тот, передатчик, состоящий из тригге-

ра состояния вьшода, триггера режима работы, счетчика синхронизации, двух элементов И, элемента НЕ, дешифратора сброса, группы буферных регистров вывода, линейного блока магистральных передатчиков и регистра сдвига, и .приемник, включаюр;ий линейный блок магистральных приемников, коммутатор входного сигнала, два элемента И, счетчик синхронизирующих импульсов, регистр сдвига, триггер состояния ввода. Триггер синхронизации, группу буферных регистров ввода и дешифратор сброса, причем первые вход и выход блока усилителей соединены соответственно с выходом коммутатора и информационными входами дешифратора адреса, дешифратора команд и передатчика, второй выход блока усилителей является выходом устройства для подключения информационных линий канала ввода-БЬшода ЭВМ, второй вход блока усилителей является входом устройства для соединения с информационными линиями канала ввода-вьшода ЭВМ, первый выход узла приоритета является выходом устройства для соединения с линией требования прерывания канала ввода-вьшода ЭйМ, второй и третий выходы узла приоритета соединены соответственно с управляющим и информационным входами регистра адреса прерьшания, управляющий вход узла приоритета является входом устройства для соединения с линией разрешения прерьтания канала ввода-вывода ЭВМ, выход регистра адреса прерьшания является выходом устройства для соединения с инфогмационными линиями канала ввода-вьшода ЭВМ, выход дешифратора адреса соединен с управляющим входом дешифратора команд, группа выходов дешифратора команд соединена с первым управляющим входом приемника.

713

с первым и вторым управляющими входами передатчика и с группой адресных входов коммутатора, выход генератора

тактовых частот соединен с тактовыми

входами передатчика и приемника, первый выход передатчика является выходом устройства для соединения с входной информационной линией абонента, второй выход передатчика соединен с первыми информационными входами узла приоритета и коммутатора, третий выход передатчика соединен с вторым информационным входом коммутатора и с вторым управляющим входом приемника, четвертый выход передатчика соединен с первым информационным входом приемника, первый выход приемника соединен с третьи:- информационным входим коммутатора, второй выход приемника соединен с четвертым информационным входом коммутатора и вторым информационным входом узла приоритета, причем в передатчике выход линейного блока магистральных передатчиков явл ется первым выходом передатчика, прямой выход триггера состояния вывода соединен с первым входом первого элемента И и является вторым выходом передатчика, выход триггера режима работы соединен с управляющим входом линейного блока и является тpeтьи выходом передатчика, выход счетчика синхронизации соединен с входом элемента НЕ и с входом записи регистра сдвига передатчика, выход первого элемента И соединен с управляющим входом счетчика синхронизации, выход второго элемента И соединен с синхро входом регистра сдвига, выход элемента НЕ соединен с первым входом второго элемента И, первый выход дешифратора сброса соединен с входом сброса счетчика синхронизации, а второй выход - с входом сброса триггера состо ния вьшода, выход регистра сдвига соединен с информационным входом линейного блока магистральных передатчиков и четвертым выходом передатчика, вторые входы первого и второго элементов И соединены с тактовым входом передатчика, информационные входы триггера состояния вывода и триггера режима работ соединен с информационным входом передатчика и информационными входами буферных регистров вывода группы, синхровходы триггеров состояния вывода и триггера режима работы соединены с первым

0

5

0

01

ь

25

0

7«

управляющим входом передатчика, причем в приемнике первый и второй информационные входы коммутатора входного сигнала соединены соответственно с выходом линейного блока магистральных приемников и первым информационным входом приемника, первый вход первого элемента И соединен с информационным входом регистра сдвига и выходом коммутатора входных сигналов, адресный вход которого является вторым управляющим входом приемника, выход первого элемента И соединен с входом сброса счетчика синхронизирующих импульсов, синхровход которого является тактовым входом приемника, а выход соединен с управляющим входом регистра сдвига, установочные входом триггера синхронизации и первым входом второго элемента И, вторым входом подключенного к второму выходу приемника и прямому выходу триггера состояния ввода, установочный вход которого является первым управляющим входом приемника, а вход сброса - подключен к входу сброса триггера син- хронизации и выходу дещифратора сброса, синхровходом соединенного с выходом триггера синхронизации и вторым входом первого элемента И, информационные входы буферных регистров группы соединены с выходом регистра сдвига,

отличающееся

тем,

что, с целью повышения скорости обмена информацией, в устройство введен шифратор, в передатчик введены два элемента И, счетчик вьшодимых импульсов, дешифратор выбора, триггер управления шифратором и коммутатор данных, а в приемник введены коммутатор данных, счетчик вводимых элементов и третий элемент И, причем пятый и шестой выходы передатчика подключены соответственно к синхронизирующему и информационному входам шифратора, выход которого является выходом устройства для подключения к адресному входу абонента, второй информационный вход приемника является входом устройства для подключения информационного выхода абонента, третьи управляющие входы приемника и передатчика соединены с дополнительным выходом ешифратора команд, третий информац1г- онный вход приемника соединен с пер-, вым выходом блока усилителей, причем в передатчике первый и второй входы третьего элемента. И соединены соот.9133

ветственно с инверсным выходом триггера состояния вьшода и третьим уп- ляющим входом передатчика, а выход - с входом записи счетчика вьшодимых импульсов, синхровход и информациол- ный входы которого соединены соответственно с выходом второго элемента И и информационным входом передатчика, адресный вход коммутатора данных под- ключен к выходу счетчика вьшодимых импульсов и информационным входам дешифратора сброса и дешифратора выбора, группа выходов которого соединена с синхровходами соответствующих бу- ферных регистров вьшода, выходы которых подключены к группе информационных входов коммутатора данных, выход которого соединен с шестым выходом передатчика и информационным вхо- дом регистра сдвига, вход сброса триггера управления шифратором соединен с вторым выходом дешифратора сброса, а синхровход и выход - соответственно с первым управляющим входом передатчика и первым входом четвертого элемента И, вторым входом и выходом подключенного соответственно к

1

7 .10

выходу элемента НЕ и пятому выходу передатчика, синхровход деш, )ра выбора является вторым управляющим входом блока, причем в приемнике информационный вход линейного блока магистральных приемников является вторым информационным входом приемника, первый и второй входы третьего элемента И подключены соответственно к третьему управляющему входу приемника и инверсному выходу триггера состояния ввода, а выход - к входу записи счетчика вьшодимых импульсов, синхровход и информационный входы которого соединены соответственно с выходом второго элемента И и третьим информационным входом приемника, а выход - с информационными входами дешифратора выбора и дешифратора сброса И адресньп входом коммутатора данных, выход и группа информационных входов которого подключены соответственно к первому выходу приемника и выходам буферных регистров ввода группы, синхровходы которых подключены к группе выходов дешифратора выбора ,

Заваглй fneHymut номер cvum/faf- ною буферного регистра тда (бРдй}

Cvuirtaatb байт uHtpopffaifuu u)

BfiBRI

ия evum

на Sifcfx SP&&

Задать (иег„ номер SP&B pQSvt/iiO

Выполнить npozpOMMU offsai m киаринагпоа g/%yg/ 4w J

Разрешить SSod HOffoa u gjopno uu SycmfloilcmKi танодить триггер cocfnof i/Jf ffffoaa f effuMtfVHOf состояние

Начало ±.

Остановить решим nepeoawuMjiqp нации триггера/ ретима oaffomttu Vgv u/woffffarnoDOM

Задот1 peeucmpa

записать . байт, информв- цаи о oiitopOMjfb/u б fa

I

/ поанмы See N,

yeffamo Hova/itHbtiJ WHep

jL

1 - -

Разрешить имфор тации установить триг- ъер состоянид ffu/fffffa ff effuffuwoe состоя ае

Редактор Л.Гратилло

j KoHeij I Фиг.5

Составитель В.Вертлиб

Техред М.Дидык Корректор М.Демчик

Заказ 4813Тираж 670Подписное

ВНИШИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д.4/5

Производственно-полиграфическое предприятие, г.Ужгород, ул.Проектная,4

нача/ о

й.,

i ge/iuvumb o- fiep BftSB

/(онец

Фиг. it

ермоео (йРб}

I

ы See N,

Увеличить но- мер БРВ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения вычислительной машины с линиями связи | 1985 |

|

SU1262512A1 |

| Устройство для сопряжения ЭВМ с датчиками состояния телефонных линий связи | 1984 |

|

SU1265786A1 |

| Информационно-управляющая система центрального теплового пункта жилых общественных и промышленных зданий | 1987 |

|

SU1511751A1 |

| Устройство для сопряжения ЭВМ с общей магистралью | 1987 |

|

SU1456963A1 |

| Устройство для сопряжения ЭВМ с магистралью локальной сети | 1987 |

|

SU1411764A1 |

| Устройство для имитации неисправностей | 1987 |

|

SU1444775A1 |

| Электронная вычислительная машина | 1988 |

|

SU1520533A1 |

| Устройство для сопряжения двух цифровых вычислительных машин | 1979 |

|

SU868741A1 |

| Многоканальное устройство управления вводом информации в микроЭВМ | 1984 |

|

SU1234844A1 |

| Устройство для сопряжения ЭВМ с абонентом | 1990 |

|

SU1702380A1 |

Изобретение относится к вычислительной технике и может быть использовано в вычислительных системах для сопряжения ЭВМ с внешними устройствами, работающими последовательным кодом. Цель изобретения - повышение быстродействия обмена информацией и расширение функциональных возможностей, устройства, за счет обеспечения возможности изменения формата принимаемых и передаваемых данных. Устройство, содержит блок усилителей, узел приоритета, регистр адреса прерывания, дешифра тор адреса, коммутатор, дешифратор команд, генератор тактовых частот, передатчик, приемник, шифраг тор. Для осуществления вьшода информации передатчик содержит линейный блок, триггер состояния вьшода, триг- гер режима, счетчик синхронизации, элементы И, элемент НЕ, счетчшс передаваемых импульсов, дешифратор сброса, регистр сдвига, дешифратор выбора, триггер управления шифратором, группу буфернбгх регистров вьшода, коммутатор данных. Для осуществления ввода информации приемник содержит линейный блок, коммутатор входного сигнала, элементы И, счетчик синхронизации, триггер синхронизации, счетчик вводимых импульсов, триггер состо яния ввода, регистр сдвига, дешифра- .тор сброса,дешифратор выбора, группу буферных регистров ввода, комму- , татор данных. В основе работы устройства лежит принцип преобразо1вания параллельного кода, принятого от ЭВМ, в параллельный или последовательный код для передачи внешнему устройству, а также прием последовательного ко- . да, переданного внешним устройстве, и преобразование его в параллельный с последующей передачей последнего в ЭВМ, 5 ил. . -о (Л со оо О5

| Патент США № 4004279, кл | |||

| Способ отопления гретым воздухом | 1922 |

|

SU340A1 |

| USA, 1977, р,27 | |||

Авторы

Даты

1987-09-07—Публикация

1986-04-03—Подача