ции соединены соответственно с входами дешифратора, выход дешифратора соединен с вторым выходом устройства, выход элемента ИЛИ соединен с вторыми входами первого делителя и второго вычитателя, выходы которых подключены соответственно к третьему и четвертому выходам устройства.

2. Устройство по п.1, о т л и ч а ю щ е 6 с я тем, что блок задержки содержит в каждом регистре памяти триггеры по числу разрядов кода, и

42063

элемент задержки, первые входы триггеров являются соответствующими входами регистров памяти, выходы - выходами регистров памяти .объединенные-, вторые входы триггеров всех регистров памжти, кроме последнего, соединены с выходом соответствующего элемента задержки, вход элемента задержки предпоследнего регистра памяти объединен с объединенными вторыми входами триггеров последнего регистра памяти и подключен к синхронизирующему входу блока задержки.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ ФОРМИРОВАНИЯ ЭТАЛОННОЙ КАРТЫ МЕСТНОСТИ ДЛЯ НАВИГАЦИОННЫХ СИСТЕМ | 1992 |

|

RU2022355C1 |

| СПОСОБ УПРАВЛЕНИЯ ДУБЛИРОВАННОЙ СИСТЕМОЙ С ЗАДЕРЖКОЙ И УСТРОЙСТВО, ЕГО РЕАЛИЗУЮЩЕЕ | 1999 |

|

RU2147162C1 |

| Устройство для определения параметров распределения случайных величин | 1981 |

|

SU1084811A1 |

| Сглаживающее устройство | 1984 |

|

SU1265797A1 |

| Цифровой фильтр | 1990 |

|

SU1739483A1 |

| Статистический анализатор | 1987 |

|

SU1425716A1 |

| АВТОМАТИЧЕСКИЙ СЛЕДЯЩИЙ ДЕЛИТЕЛЬ ПЕРИОДОВ ИМПУЛЬСНЫХ СИГНАЛОВ | 1992 |

|

RU2105410C1 |

| Устройство для контроля достоверности результатов измерений | 1985 |

|

SU1300530A1 |

| ТЕЛЕВИЗИОННЫЙ КООРДИНАТОР | 1987 |

|

SU1521242A1 |

| Адаптивное устройство для сокращения избыточности цифровой информации | 1983 |

|

SU1136201A1 |

1. УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ДОСТОВЕРНОСТИ ТЕЛЕМЕТРИЧЕСКОЙ ИНФОРМАЦИИ, содержащее элемент ИЛИ и в каждом канале обработки информации блок задержки, вычитатель, элемент И, блок сравнения, квадратор и сумматор, первые входы блока задержки и вычитателя объединены и подключены к первому входу канала обработки информации, выход блока задержки сое- ; динен с вторым входом вычитателя, выходы вычитателя и элемента И соединены соответственно с первым и вторым выходами канала обработки информации, первый вход первого канала обработки информации соединен с первым входом устройства, первый выход каждого предыдущего канала обработки информации соединен с первым входом каждого последующего канала обработки информации, вторые выходы каналов обраббтки информации подключены к соответствующим входам элемента ИЛИj выход которого соединен- с первым выходом устройства, о тл и ч а|6щ е е ся тем, что, , с целью повышения достоверности контроля телеметрической информации, в устройство введены делитель, делитель частоты, вычитатель, дешифратор и в каждом канале обработки информации делитель-частоты, вычитатель, дешифратор и в.каждом канале обработки информации делитель, делитель частоты, блоки памяти и умножитель, в. каждом канале обработки информации выход вычитателя через последовательно соединенные делитель частоты и квадратов подключены к первому входу сумматора, выход сумматора соединен с первым входом умножителя, второй вход умножителя соединен с выходом первого блока памяти, выход умножителя соединен с первыми входами делителя и элемента И и с третьим .выходом канала обраS ботки информации, выход делителя со(Л С единен с первым входом блока, сравнения, второй и третий входы которого соединены соответственно с выходами второго и третьего блоков памяти, выход блока сравнения соединен с вторым входом элемента И, вторые входы блока задержки, сумматора и делителя соединены соответственно с вторым, третьим и четвертым входами канала обработки информации, вторые входы каналов обработки информации объединены с входом делителя частоты и подключены к второму входу устройства, вйход делителя частоты подключен к третьим входам каналов обработки информации,, третий выход каждого последующего канала обработки информации соединен с четвертым входом каждого предыдущего канала обработки информации, третий выход Первого канала обработки информации соединен с первыми входами делителя и вычитателя, вторые выходы каналов обработки информа

1

Изобретение относится к автоматике,вычислительной технике .и измерительной технике и может быть| использовано в системах обработки телеизмерений для верификации поступающей информации.

Известно устройство для контроля достоверности информации, которое содержит К параллельных цепей, каждая из которых включает элементы задержки вычитатели, блок определения абсолютной разности, сумматор, блок нормиро вания, блок сравнения, элемент И, элемент ЗАПРЕТ, вход первого элемента задержки соединен с выходом вычитателя предыдущей параллельной цепи и с первым входом вычитателя соответствующей параллельной цепи, выход которого подключен к первому входу блока определения абсолютной разности и через второй элемент задержки к второму входу блока определения абсолютной разности, выход которого через последовательно соединенные сумматор и блок нормирования соединен с входами соответствующих блоков сравнения и элемента И, выход которого подключен ко входу элемента ИЛИ, выход блока сравнения подключен к первым входам соответствующих элементов ЗАПРЕТ, выходы которых соеди нены соответственно с вторыми входами элементов И LiJ.

Недостаток данного устройства заключен в том,, что последовательные разности с ростом порядка разности К испытывают усиливающуюся отри1 тельную корреляцию, это приводит

к понижению эффективности определяемых оценок среднеквадратического отклонения.

Усиливающийся статистический разброс сравниваемых оценок способствует увеличению вероятности неверного определения степени полинома, которым может быть описана низкочастотная составляющая {тренд ).

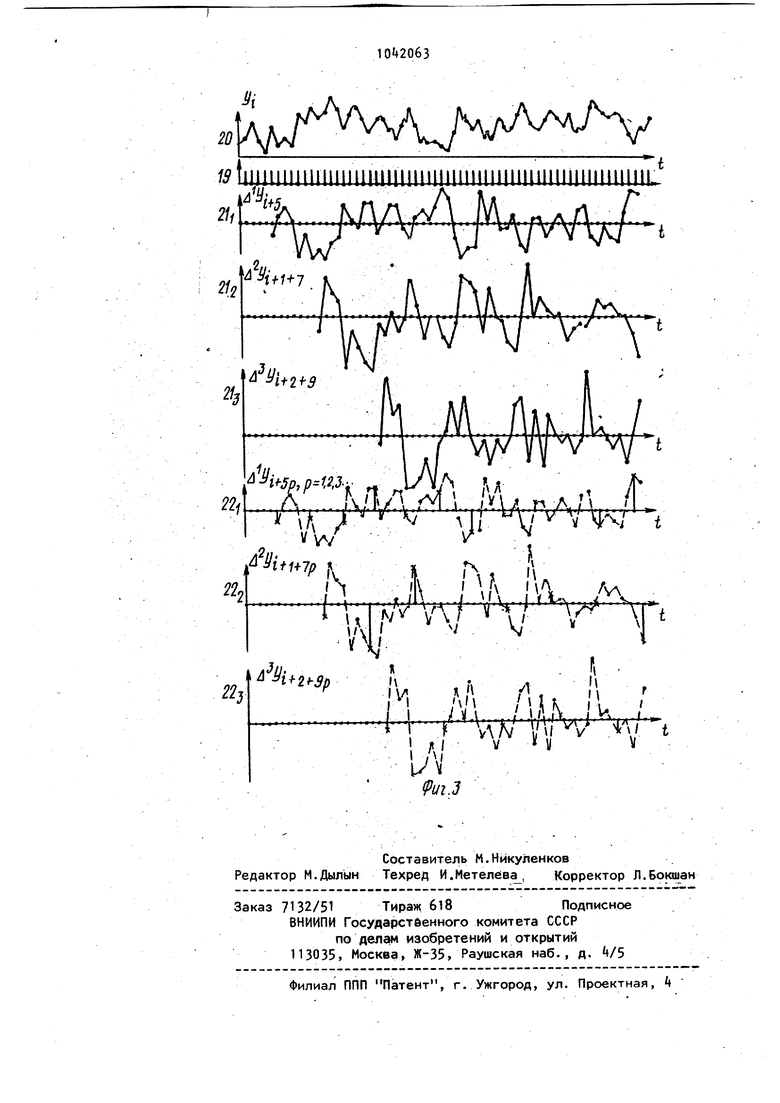

Наиболее близким по технической сущности к предлагаемому является устройство, содержащее первый элемен ИЛИ и К каналов обработки информаци первый из которых состоит из первого элемента задержки, вход которого объединен с первым входом первого блокаопределения абсолютной разност и подключен к входу устройства, выхо первого элемента задержки соединен с вторым входом первого блока определения абсолютной разности, выход которого через последовательно соединенные первый сумматор и блок нормирования соединен с первыми входами первого элемента И и первого блока сравнения, выход которого соединен со вторым входом первого элемента И, каждый из последюущих (К-1) каналов обработки информации состоит из первого элемента, вход и выход которого соединены соответственно с первым и вторым входами вычитателя, выход которого .соединен непосредственно с первым и через второй элемент задержки с вторыми входами первого блока определения абсолютной разности, выход которого через последовательно соединенные первый сумматор и блок нормирования соединен с первыми входами первого элемента И и первого блока сравнения, выход первого блока сравнения соединен с первым входом элемента ЗАПРЕТ,выход которого соединен с вторым входом первого элемента И, вход первого элемента задержки второго канала обработки информации подключен к вх ду устройства, вход первого элемент задержки каждого из последующих К каналов обработки информации соедин с выходом вычитателя предыдущего ка ла обработки информации, второй вхо первого блока сравнения каждого из К каналов обработки соединен с выхо дом блока нормирования последующего канала обработки информации, вто рой вход элемента ЗАПРЕТ каждого из К -1 каналов обработки информации соединен с выходом первого блока сравнения предыдущего канала обработки информации, выходы первыхэлементов И всех К каналов обработки информации соединены с соответствующими входами первого элемента ИЛИ, выход которого соединен с первым выходом устройства, выход первого элемента задержки соединен с первым входом вычитателя, выход которого непосредственно и через второй элемент задержки соединен соответственно с первым и вторым входами блока определения абсолютно разности, вход первого элемента задержки объединен с вторым входом вычитателя и подключен к выходу вымитателя К-го канала обработки информации, вход третьего элемента задержки объединен с первыми входами первого и второго блока определе ния абсолютной разности соединен с выходом третьего элемента задержки, выход второго блока определения абс лютной разности соединен с первым входом второго сумматора, второй вх которого соединен с выходом первого блока определения абсолютной разнос ти, выход второго сумматора через последовательно соединенные первый блок определения вероятности и квад ратор соединен с первым входом втор го блока сравнения, второй вход кот рого соединен с выходом второго бло ка определения вероятности, выход второго блока сравнения соединен с первым входом второго элемента И, второй вход которого соединен с выходом первого блока, вход второго 3 блока определения вероятности каждого из К каналов обработки информации соединен с выводом первого блока определения разности последующего камала обработки информации, выход второго элемента И каждого из К каналов обработки информации соединен с соответствующим входом торого элемента ИЛИ,выход которого соединен с вторым выходом устройства t2J. Однако известные устройства не предполагают использование высокой избыточности результатов телеизмерения для устранения корреляции .между случайными процессами, полученными при К -кратном применении к исследуемому процессу разностного оператора. Целью изобретения является повышение достоверности контроля телеметрической информации. Поставленная цель достигается тем, что в устройство, содержащее элемент ИЛИ и в каждом канале обработки информации блок задержки, вычитатель, элемент И, блок сравнения, квадратор и сумматор, первые входы блока задержки и вычитателя объединены и подключены к первому входу канала обработки информации, выход блока за- держки соединен с вторым входом вычитателя, выходы вычитателя и элемента И соединены соответственно с первым и вторым выходами канала обработки информации, первый вход первого канала обработки информации соединен с первым входом устройства,первый выход каждого предыдущего канала обработки информации соединен с первым входом каждого лоследующего канала обработки информации, вторые выходы каналов обработки информации соединены с соответствующими входами элемента ИЛИ, выход которого соединен с первым выходом устройства, введены делитель, делитель частоты, вычитатель, дешифратор и в каждом ; канале обработки информации делитель, делитель частоты, блоки памяти, умножитель, в каждом канале обработки информации выход вучитателя через последовательно соединенные делитель частоты и квадратор подключен к первому входу сумматора, выход сумматора соединен с первым входом умножителя, второй вход умножителя соединен с выходом первого блока памяти, выход умножителя соединен с первыми входами делителя и элемента И и с третьим выходом канала обработки информации, выход делителя соединен с первым входом блока сравнения, второй и тре тий входы которого соединены соответ ственно с выходами второго и третьег блоков памяти, выход блока сравнения соединен с вторым входом элемента И, вторые входы блока задержки,сумматор и делителя соединены соответственно с вторым, третьим и четвертым входами канала обработки информации, вторые входы каналов обработки информации объединены с входом делителя частоты и подключены к третьим входа каналов обработки информации, третий выход каждого последующего канала обработки информации соединен с четвертым входом каждого предыдущего канала обработки информации, третий выход первого канала обработки инфор мации соединен с первыми входами делителя и вычитателя, вторые входы ка налов обработки информации .соединены соответственно с входами дешифратора, выход дешифратора соединен с вто рым выходом устройства, выход зп€мента ИЛИ соединен с вторыми входами первого делителя и второго вычитател выходы которых подключены соответственно к третьему и четвертому выхо дам устройства.Блок задержки содержит в каждом регистре памяти триггеры по числу разрядов кода и элемент задержки, первые входы триггеров являются соответствующими входами регистров памяти, выходы - выходами регистров памяти, объединенные вторые входы триггеров всех регистров памяти, кроме последнего, соединены с выходом соответствующего элемента задержки, вход элемента задержки предпоследнего регистра памяти объединен вторыми входами триггеров последнего регистра памяти к синхронизирующему входу блока задержки. Теоретическая основа заключается в том, что для последовательности дискретизированных значений , i - 1, 2, 3..N-K К-раЬностей, полученных путем К-кратного применения к исследуемому случайному процессу разностного оператора ./ f +V Vr(t) (t) m , п t 4...+ о(-ю1р-тренА,(if быстроменяющаяся составляющая случайного процесса; селектируются отсчеты, отстоящие друг от друга на интервалы 2К + 3 с индексами i+-K, 1+К-«-(), i-H + 2(2K+3),i+K+3(),..., К- а для последовательности Д , i 1 ,2,3,... N-K-1 (К + 1)-х разностей селектируются значения с индексами i+k+-1 ,(K+1|-f3,UK-i-H+2 2(, i4K-Hi l 2{K-t1)H-3,... и определяется отношение дисперсий в соседних каналах обработки информации: ,lV-%.) N-K-1 К-И 2() 2K42. C(/. N-K f. К 2K-3 2K IK ,5 - усредненные суммы квадратов селектированных разностей К7ГО и (К + 1)-го порядков; 2i исло сочетаний из2| по i ; Щ, суммирование соответствущих селектированных разностей. Отношение дисперсий (2) подчинено акону Фишера-Снедекора -и быстро схоится с увеличением порядка разости К к нормальному закону со редним, равным нулю и среднеквадраическим отклонением )р-КН). -(3)| олином f который описывается а исследуемом интервале анализа ренд, имеет наивысшую степень (), если для отношения дисперий (2) справедливо следующее нераенство , ,l№i,F(5., И) . %-(:/ де F (viK - с недекоров с кое отношение исперсий для уровня значимости S с числом степеней свободы п (N-K-1)/ (2К + 3). При выполнении неравенства (k) ценка дисперсии D|(Y) , вычисленой в К-ом канале обработки информации, представляет собой оцен ку дисперсии быстроменяющейся .(шумовой ) составляпщей исследуемо;Го случайного процесса y-j, в то .время, как оценка дисперсии U-ifyj .вычисленной в первом канале, характеризует дисперсию суммарного процесса (1). , , , . Л}, Отношение дисперсий 06 пред ставляет собой модифицированный Крите рий Аббе (1), а разность D, ,- Dxt-s)j характеризует оценку дисперсии тренда. На фиг.1 приведена структурная схема устройства; на фиг,2 - структурная схема блока задержки; на фиг.З графики, поясняющие работу устройства Устройство содержит блоки 1 задержки , внчитатели 2, квадраторы 3, сумматоры t, делители 5 частоты на (2К + 3), блоки 6 памяти, умножители 7, делители 3, блоки 9 сравнения,блоки 10 и 11 памяти, элемент 12 И., каналы 13 обработки информации, дешифратор 1, элемент 15 ИЛИ, делитель 16, вычитатель 17, делитель 18 часто ты, входы 19 и 20 устройства, входы 21 блоков 1 задержки, выходы 22, 23 и 2 соответственно делителей 5 часто ты, умножителей 7, блоков 1 задержки вь1ходы 25, 26, 27 и 28 устройства. Блоки 1 задержки включают в себя регистры 29 памяти, которые состоят из триггеров 30 и элементов 31 задержки. Работа устройства состоит- в следу щем. Информационный параметр, достоверность восстановления которого на яриемной стороне необходимо оценить, подают на вход20 устройства. Исследу емый случайный процесс У.. , представ ленный в цифровой форме, подвергается последовательной обработке в вычитателях 2, где определяются разности между непосредственно поступаю щими и задержанными в блоках 1 задержки значениями: ..).7 Д.2 )4Э (HK)+{2(M 3jJБлоки 1 задержки, число которых равно (к + 1), обеспечивает задержку С1О времени значений исследуемого процесса, соответствующую интервалам 5 Т, 7 Г , 9 Т. . .2 (К + 1 ) Т, гделТ. , - t - период следования синхронизирующих импульсов (фиг.З, вход 19). Разности, вычисленные в вычитателях 2, поступают на вход соответствующих делителей 5 частоты, осуществляющих с целью устранения корреляционной зависимости прореживание в (2К + 3) раз значений преобразованных случайных процессов: 1 Д (p4l) Ч1 7р Н-1ч-7р 1Н + 7(рМ) н2+9р ) K+f-Kv. Л У}4К+ 2( VK42( i+K-f 2((p+l) где р 0,1,2,3... Разности (6) между селектированными значениями преобразованных случайных процессов возводятся в квадраторах 3 в квадрат и накапливаются в сумматорах k за установленные делителем 18 частоты интервалы усреднения, обеспечивающие накопление в .сумматоре k первого канала обработки информации N значений случайного процесса A Vi45p Осреднение и нормирование вычисленных сумм квадратов (2) производится в умножителях 7 путем / умножения на соответствующие оэффициенты 2К + 3 (N-K), хранящиеся в блоках 6 памяти. В делителях 8 определяются отношения средних квадратов селектированных разностей, вычисленных в предшествующем и в последующем каналах обработки информации. Результаты деления сравниваются в блоках 9 сравнения со значениями NK хранящимися в блоках 10 памяти. При нахождении результата деления в пределах установленных допусков , определяемых неравенством (k) и задаваемых блоками 10 и 11 памяти, -на выходе блока 9 сравнения К-го канала формируется сигнал, открывающий элемент И 12 для прохождения рценки среднего квадратов разностей, вычисленного в сумматоре на вход умножителя 7- После осред нения и нормирования в умножителе 7 среднего квадратов разностей коэффициентом 2к+3/С2к; (N-К) оценка диспер сии быстроменяющейся соетавляющей случайного процесса вывадится через Элемент ИЛИ 15 на выход 28 устройства и поступает на соответ ствующий номеру канала обработки информации вход дешифратора , на выходе которого формируется код наивысшей степени полинома f(t). Нормированное среднее квадратов разност между селектированными знамениями, вычисленное в первом канале обработки информации lC.2{b)(.S{pM)f.() поступает на входы делителя 16 и вычитателя 17- На выходе делителя 16 определяют статистику оС представляющую собой модифицированный критерий Аббе, а на выходе вычитателя 17 дисперсию тренда: f(} 3) . Работа блока 1 задержки заключена в следующем. Знамения случайного процесса,пред ставленные п .-разрядным двоичным кодом, записываются в первый регистр 29 памяти (фиг.2) Запись производится параллельным кодом, при .котором в каждый из триггеров 30 записывается соответствующий разряд кода. Импуль- 35 сами синхронизации (фиг.З, вход 19) h -разрядный двоичный код значения случайного процесса, записанный в первом регистре 29 памяти, последозвательно переписывается в последующие регистра памяти. При этом в вычитатель 2К-го канала поступает из блока 1 задержки .знамение случайного процесса -у.(): задержанное относительно знамения, поступающего на его второй вход, на тактов, определяемых импульсами синхронизации.. После вывода числа из (2К + 3)-го регистра памяти и обнуления его триггеров соответствующим j-ым импульсом синхронизации тем же синхроимпульсом, но прошедшим через (2К + 2) элемент 31 задержки, переписывается число из (2К + 2) регистра 29 памяти в (2К + 3) регистр. Перезапись j-м импульсом синхронизации, задержанным в элементах задержки 31. производится до тех пор, пока не перепишется значение из первого регистра памяти во второй. При этом а первый регистр 29 памяти записано следующее знамение дискретизированного случайного процесса. Предлагаемое устройство позволяет за счет устранения корреляции между случайными процессами, полученными в результате последовательного разностного преобразования, по результатам измерений, обладающих избыточностью, повысить достоверности определения степени полинома, описывающег поведение информационного параметра, и достоверность критерия Аббе, оценок дисперсий быстроменяющейся и медленноменяющейся составляющих исследуемого случайного процесса.

дЖ,

« F -t г V Uf

i

fv Л,

In Л n Aj

1

j-uyy v Yi ;---i f,

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Топка с несколькими решетками для твердого топлива | 1918 |

|

SU8A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Авторское свидетельство СССР № , кл | |||

| Топка с несколькими решетками для твердого топлива | 1918 |

|

SU8A1 |

Авторы

Даты

1983-09-15—Публикация

1982-04-30—Подача