(5) УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ЭЛЕМЕНТАРНЫХ ФУНКЦИЙ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления элементарных функций | 1983 |

|

SU1145340A1 |

| Устройство для вычисления функций в модулярном коде | 1985 |

|

SU1278839A1 |

| Конвейерное устройство для потенцирования массивов двоичных чисел | 1984 |

|

SU1191909A1 |

| Устройство для вычисления тригонометрических функций с плавающей запятой | 1986 |

|

SU1425661A1 |

| Устройство для интерполяции | 1984 |

|

SU1171807A1 |

| Устройство для вычисления функций | 1985 |

|

SU1280391A1 |

| Устройство для вычисления квадратного корня | 1984 |

|

SU1191908A1 |

| Устройство для интерполяции | 1984 |

|

SU1215118A1 |

| Вычислительное устройство | 1986 |

|

SU1322270A1 |

| Конвейерное устройство для вычисления логарифмической и экспоненциальной функций | 1982 |

|

SU1027722A1 |

1

Изобретение относится к вычислительной технике и может быть исполь зовано при разработке специализированных и универсальных вычислительных машин, при введении в состав операций ЭВМ специальных команд типа sin X, cos X, tg х, ctg х, arcsin х, е , In X, sh X, arsh х, (Ifx) и тому подобных.

Известен цифровой вычислитель ций тангенса и котангенса, содержащий И-разрядный регистр аргумента, постоянное запоминающее устройство, блок управления, блок умножения, регистры промежуточных результатов, блок деле- Is ния, элементы ИЛИ, выходной perHCTp lJ

Недостатком известного устройства является невозможность- вычисления гиперболических, логарифмических и гих функций.

Наиболее близким к изобретению по технической сущности является устройство для вычисления экспоненциальной функции, содержащее два одноразрядных сумматора-вычитателя комбинационного типа, два накопительных регистра, блок односторонней памяти, вентили, сдвигающий регистр, блок определения знака псевдочастного, блок анализа сходимости (схема сравнения, блок управления, блок сброса и блок повторений итераций 23.

Недостатком известного устройства является узкая специализация. Для создания процессора, выполняющего вычисления тригонометрических, круговых, показательных, логарифмических, гиперболических и обратных гиперболических функций, требуются большие затраты оборудования.

Целью изобретения является расширение класса решаемых задач за счет возможности дополнительного вычисления устройством тригонометрических, гиперболических и логарифмических функций.

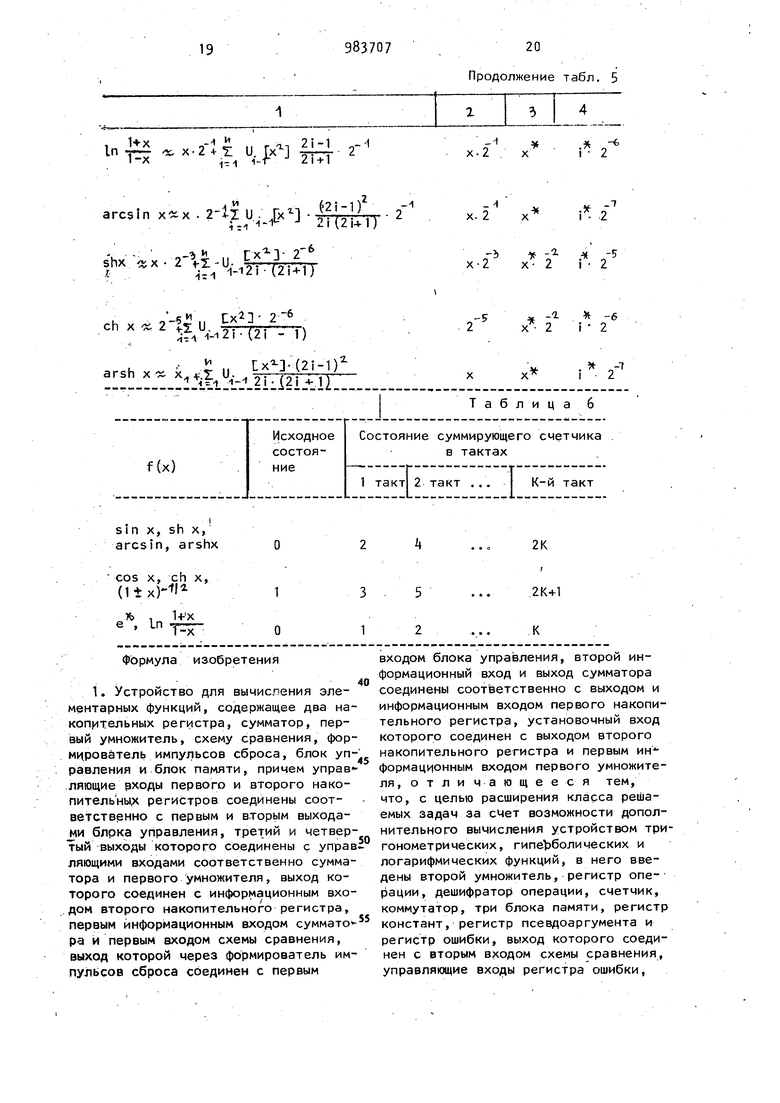

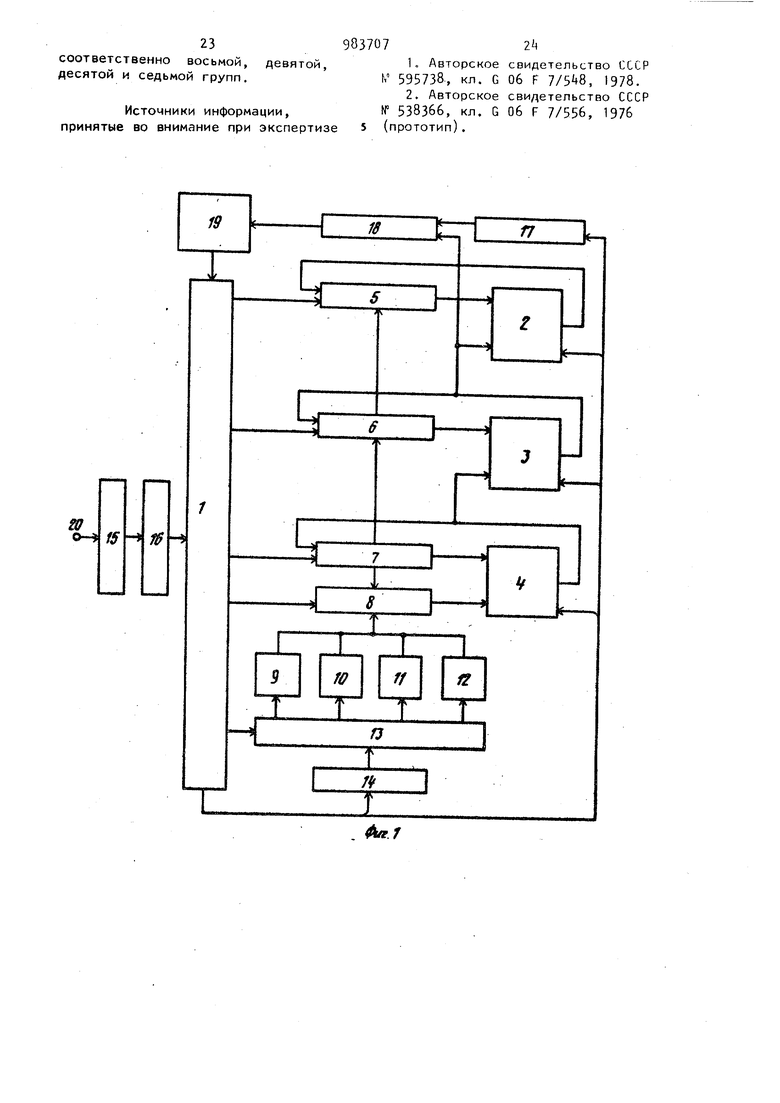

Поставленная цель достигается тем, что в устройство для вычисления элементарных функций, содержащее два накопительных регистра, сумматор, первый умножитель, схему сравнения, формирователь импульсов сброса, блок управления и блок памяти, причем управляющие входы первого и второго накопительных регистров соединены соответственно с первым и вторым выходами блока управления, третий и четвертый выходы которого соединены с управляющими входами соответственно сумматора и первого умножителя, выход которого соединен с информационным входом второго накопительного регистра, первым информационным входом сумматора и первым входом схемы сравнения , выход которой через формирователь импульсов сброса соединен с первым входом блока управления, второй информационный вход и выход сумматора соединены соответственно с выходом и информационным входом первого накопительного регистра, установочный вход которого соединен с выходом второго накопительного регистра и первым информационным входом первого умножителя, дополнительно введены второй умножитель, регистр операции, дешифратор операции, счетчик, коммутатор, три блока памяти, регистр констант, регистр псевдоаргумента и регистр ошибки, выход которого соединен с вторым входом схемы сравнения, управляющие входы регистра ошибки, второго умножителя, счетчика, коммутатора, регистра констант и регистра псевдоаргумента соединены соответственно с пятого по десятый выходами блока управления, второй вход которого соединен через дешифратор операции с выходом регистра операции, выход счетчика соединен с информационным входом коммутатора, выходы с первого по четвертый которого соединены с входами соответственно с первого по четвертый блоков памяти, выходы которых соединены с первым информационным входом регистра констант, второй информационный вход которого соединен с выходом регистра псевдоаргумента и первым -информационным входом второго умножителя, второй информационный вход которого соединен с выходом регистра констант, выход второго умножителя соединен с информационным входом регистра псевдоаргумента, выход которого соединен с установочным входом второго накопительного регистра, второй информационный вход первого умножителя соединен с выходом второго умножителя. .

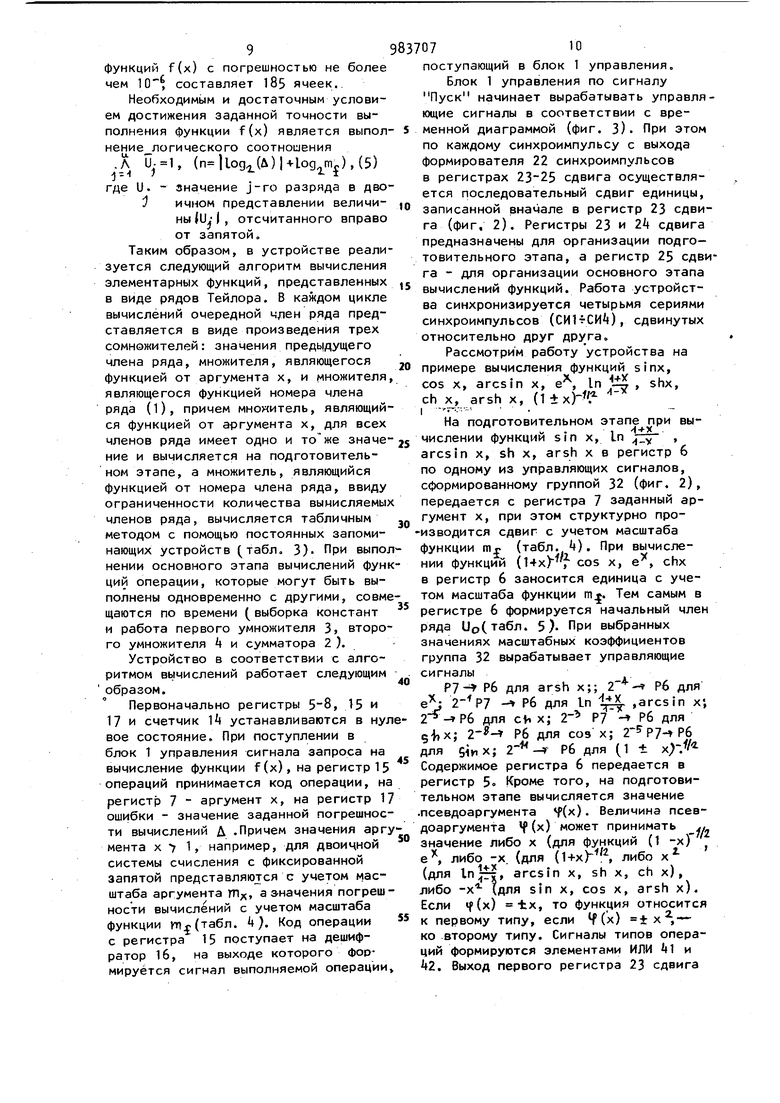

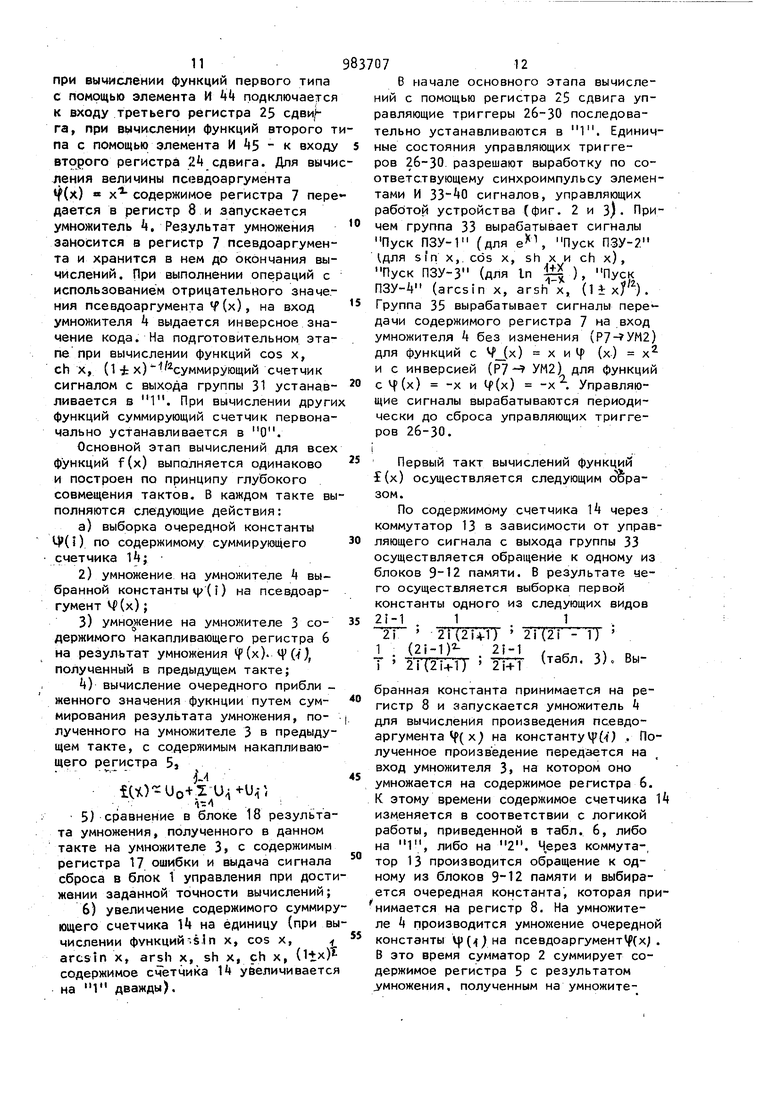

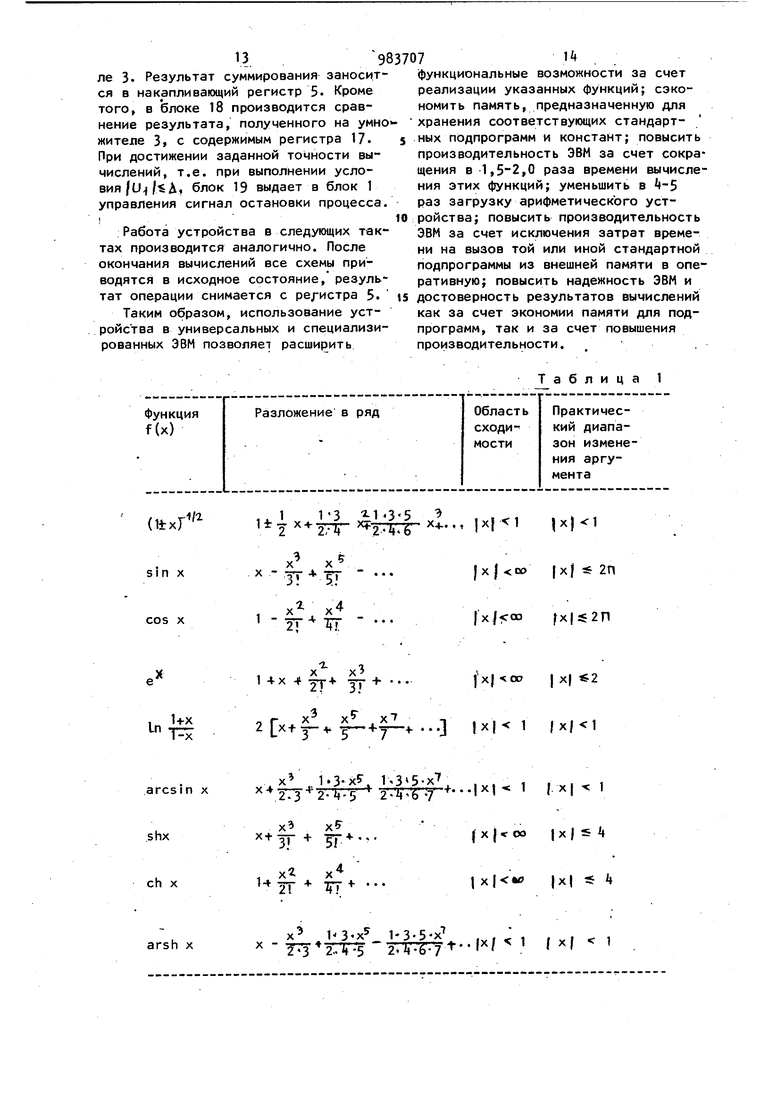

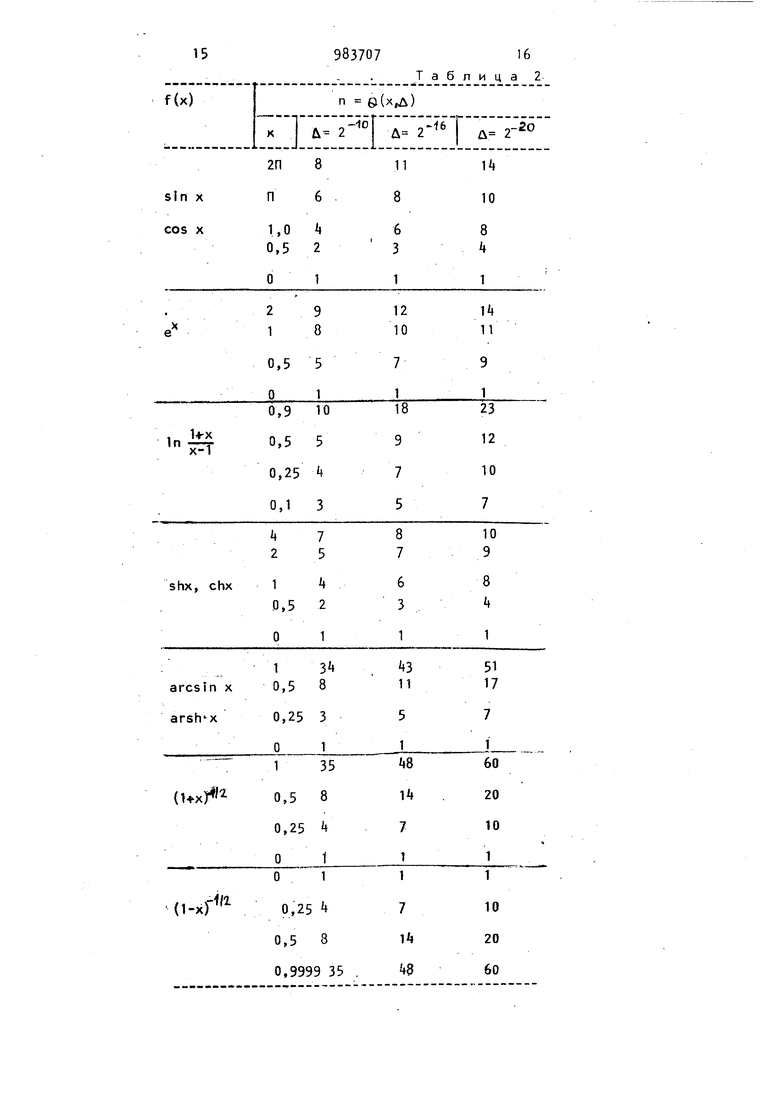

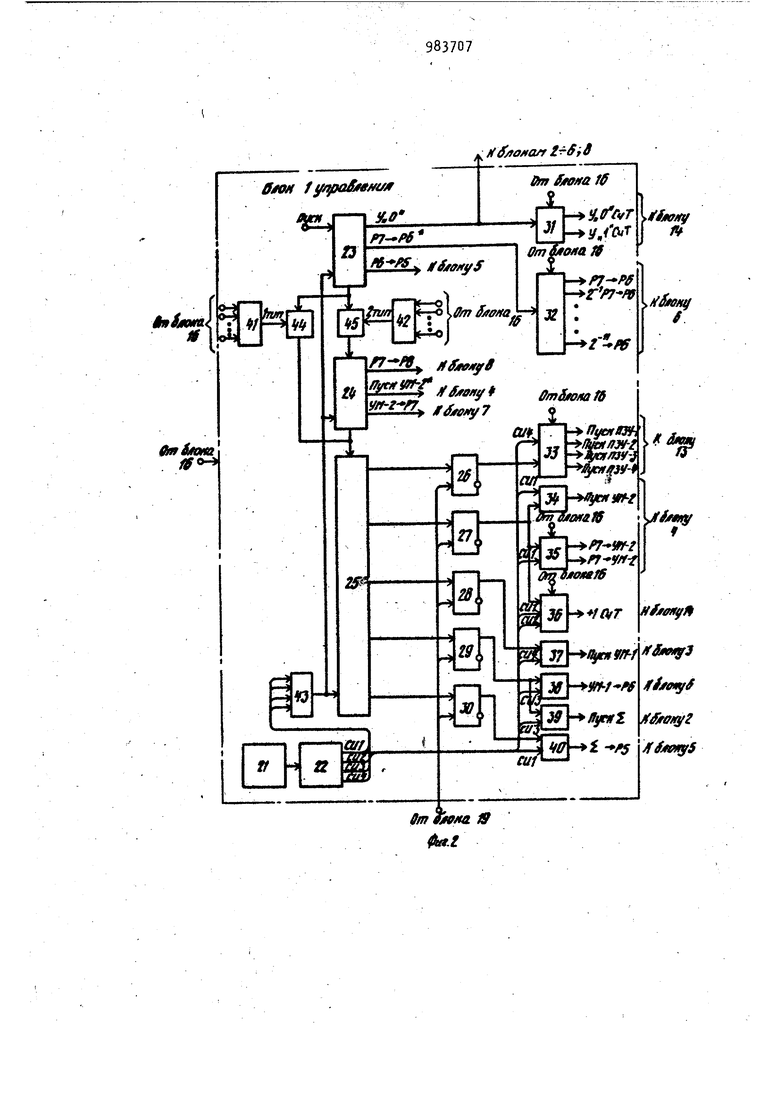

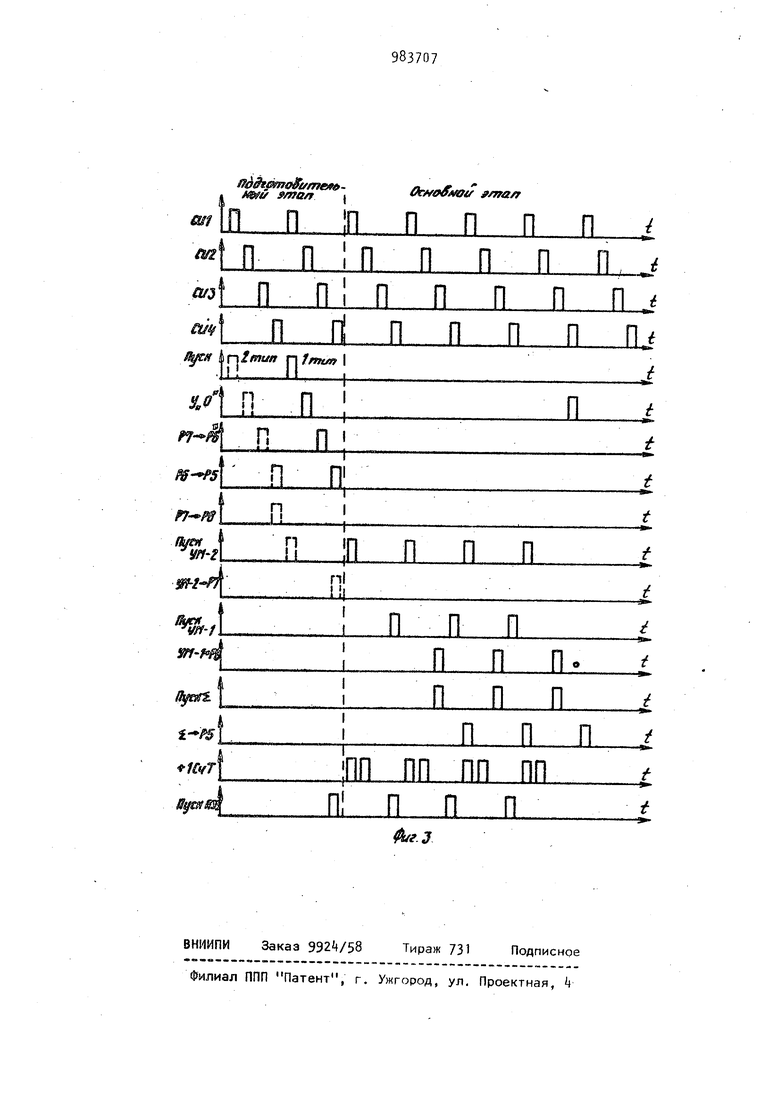

Причем блок управления содержит генератор импульсов, формирователь синхроимпульсов, три сдвиговых регистра, пять триггеров, десять групп элементов И, три элемента ИЛИ и два элемента И, входы первого и второго элементов ИЛИ и первые входы элементов И с первой по пятую групп соединены с вторым входом блока управления, выход генератора импульсов соединен с входом формирователя синхроимпульсов, выходы с первого по четвертый которого соединены с входами третьего элемента ИЛИ, выход которого соединен с синхровходами регистров сдвига, выход переполнения первого регистра сдвигд. соединен с первыми входами первого и второго элементов И, вторые входы которых соединены с выхода ми соответствующих элементов ИЛИ, выход первого элемента И соединен с информационным входом второго регистра сдвига, выход переполнения которого подключен к информационному входу третьего регистра сдвига и выходу второго элемента И,выходы разрядов с первого по пятый третьего регистра сдвига соединены с первыми входами соответственно с первого по пятый триггеров вторые входы которых подключены к первому входу блока управления, выходы первого и второго разрядов первого регистра сдвига соединены с вторыми входами элементов И соответственно первой и второй групп, выход первого триггера соединен с вторыми входами элементов И третьей группы, третьи входы которых соединены с четвертым выходом формирователя синхроимпульсов, выход второго триггера соединен с вторыми входами элементов И четвертой и пятой групп и первыми входами элементов И шестой группы, вторые входы которых соединены с первым выходом формирователя синхроимпульсов, третьими входами элементов И четвертой и пятой групп и первыми входами элементов И. седьмой группы, вторые входы которых соединены с выходом пятого триггера, четвертые входы элементов И пятой группы соединены с вторым выходом формирователя синхроимпульсов, четвертый выход соединен с первыми входами элементов И восьмойгруппы, вторые входы которых соединены с выходом третьего триггера., выход четвевтого Уриггера соединен с первыми входами элементов И девятой и десятой групп, вторые входы которых подключены к третьему выходу формирователя синхроимпульсов выход первого разряда первогб регигстра сдвига соединен с первым, вторым, третьим, четвертым, шестым и девятым выходами блока управления, выход третьего разряда первого регистра сдвига соединен с первым выходом блока управлений, выходы разрядов ,с первого по третий второго регистра сдвига .соединены соответственно с девятым, шестым и десятым выхсдами блока управления , выходы элементов И первой группы соединены с седьмым выходом iблока управления, с вторым выходом которого соединены вЬ1ХОды элементов второй группы, Ьыходы элементов И тре тьей группы соединены с восьмым выходом блока управления, шестой выход которого соединен с выходами элементов И четвертой и шестой групп, выходы элементов И пятой группы соединены с седьмым выходом блока управления, четвертый, второй, третий ипервый выходы которого соединены с выходами элементов И соответственно восьмой, девятой, десятой и седьмой групп. На фиг. 1 представлена блок-схема устройства; на фиг. 2 - блок управления; на фиг. 3 -. временные диаграммы работы отдельных блоков. Устройство для вычисления элементтарных функций содержит блок 1 управ„ления, сумматор 2, умножители 3 J, регистры 5 и 6 накопительные, регистр 7 псевдоаргумента, регистр 8 констант, блоки 9-12 памяти, коммутатор .13. счетчик 1, регистр 15опер ции,дешифратор 16 операции,регистр 17 ошибки, схему 18 сравнения, формирова тель 19 импульсов сброса и .вход 20 устройства. Блок управления содержит генератор 21 импульсов, формирователь 22 синхроимпульсов, регистры 23-25 сдвига, триггеры 26-30, группы элементов И, элементы ИЛИ , элементы И i и its. На временной диаграмме ( фиг. 3) поясняющей работу устройства, изображены ЭПЮ0Ы следующих управляющих си|- налов: -синхроимпульсы на выходе фор7 мирователя синхроимпульсов (СИ1-СИ, , импульс Пуск, импульс сброса сигналы пуска первого и второго умножителей, сумматора, блока памяти (Пуск УМ-1, Пуск УМ-2,Пускт:, Пуск ПЗУ, сигналы передачи содержимого одного регистра на другой, сигналы результата умножения и суммирова ния на накопительные регистры ( Р7-гР6, Р6 -Г Р5, Р7 РЗ, УМ-1 - Р6, УМ-2- Р 7, Х- Р5), сигналы увеличения содержимого счетчика на единицу (+1 СчТ)., Формирователь 19 предназначен для преобразования потенциального сигнала со cxef« i 18 сравнения, поступающего при достижении заданной точности вычислений, в импульсный, и выдачи его в блок 1 управления для сброса триггеров блока управления, и содержит генератор одиночных импульсов ( ГОИ и схему распределения сигналов сброса. Схема распределения сигна;юв сброса задерживает сигналы сбросачуправляющих триггеров 29 и ,30 на время работы сумматора 2 и передачи результата суммирования с сумматора в регистр 5. Вычисление функций в предложенном устройстве основано на использовании свойств рядов Тейлора, заключающихся в том, что: а) при вычислении рядов для различных функций выполняют.ся 6динакоК)1е промежуточные действия ( это дает возможность использовать один и тот же блок односторонней, памяти для вычисления различных функций); б ) быстрая сходимость рядов обеспечивает малую емкость блоков односторонней памяти, Tpигoнoмetpичecкиe, круговые,показательные, логарифмические, гиперболические и обратные гиперболические функции с помсяцью преобразований Тейлора могут быть записаны в виде бесконечного степ(знного ряда. Разложения некоторых из этих функций в ряд Тейлора, обл;эсти сходимости рядов и практические диапазоны изменений аргумента X приведены в табл.- 1. Для вычисления функций f(x) с заданной погрешностью ik требуется вычислить п первых членов ряда. Зависимость Y ,&) количества первых членов ряда, которые должны быть учтены при расчете, от диапазона из- 7менения аргумента х и заданной погре ности вычислений Д приведены в табл. Вычисление функций, приведенных в табл. 1, удобно производить по рекурентным формулам вида f (х )), (1) ,,. .где X, . - реальные значения аргумента и номера члена ря да соответственно; п а г-г г оеаТг г f (х) - значение функций; и - значение 1-го члена ря.„,.,,. 1р(х),Ч(1Г- множители, зависящие от . 1„(. , Выражения для t|)(x) и ) приве дены в табл. 3. Для рассматриваемых функций рекурентные соотношения, например для дв ичной системы счисления с фиксирован ной запятой, имеют вид ex).,4cxmo (Wty.)4(.) где щ, ,т ,п1 ,т ,т. - масштабные коэф Uo U Ч л фициенты для функций и аргументов;f 1, если UQ 1 DO I т.,если U,, q(x). Диапазоны изменения реальных значений функций и аргументов и соответ , ствующие им масштабы приведены в . табл. Ц, где А - величина, определяю щая диапазон изменения реальных значений функции f(x), В - определяет диапазон изменения значении 1-го чле на ряда U:, С - диапазон изменения р альных значений аргумента х, 3)- диа пазон изменения количества первых членов ряда, которые должны быть учтены при расчёте. При вычислении функций«по рекурентным формулам должны выполняться условия mj « max т, т . (3) Конкретные рекурентные соотношения для вычислении функций с учетом , масштабов приведены в табл. 5° В квадратных скобкйх указаны действия подготовительного этапа, которые сво дятся к вычислению величины СЧ(Х)(Х) €(4) При выполнении основного этапа операций действия, связанные с вы078числением функции Ц (|) и сравнением величины сд выполняются одновременно с другими Анализ сходимости рядов (табл. 2) показывает, что для вычисления функций f(x) с заданной погрешностью Д в практическом диапазоне и. менения аргумента X требуется вычислить ограниченное число первых членов ряда. Это позволяет воспользоваться табличным методом вычисления функции Ч () / г- с помощью блоков памяти (ЬП). При рассмотрении функций Ч () (табл. 3) оказывается, что для различных функций f(x) J функции Ш() описываются одной и той же формулой . (например, sinx и shx; cosx и chx, arcsinx и arshxX. Это позволяет использовать одни и те же БП, хранящие значения lf(i), для вычисления различных функций МПервый БП (БП-1) используется при вычислении функции е. В каждом такте на вход БП-1 подается значение 1, являющееся адресом ячейки, а на выходе снимается обратная величина 1/i. Количество ячеек БП-1 равно 14 (табЛо 2), а разрядность каждой ячейки зависит от точности представления функции Ч (i) и не превышает разрядности, необходимой для представления аргумента х Второй БП (БП-2) используется при вычислении функций sinx, cosx, shx, Он состоит из 28 ячеек (табл.2). в нечетных ячейках с адресами (2i-1) записаны значения 1/2 {21 -1), а в четных ячейках с адресами 2i - значения 1/21 (21+1). Третий БП (.БП-3) используется при .. .вычислении функции ЕИ :р. и содержит 23 ячейки (табл„ 2), вкоторых - ii-t исаны величины . Четвертый БП (БП-Ц) используется при вычислении функций arcsinx, arshx и (1±хГ и содержит 120 ячеек. В ячейках с четными адресами записаны величины (2i-1)/2i ,(2i4l), необходимые для вычисления функций arcsinx, arshx, а в ячейках с Нечет„у адресами - величины (2i-l)/2i, необходимые для вычисления функций (1ixГ Таким образом, суммарная емкость всех БП, обеспечивающих вычисление 9 функций f(x) с погрешностью не более чем составляет 185 ячеек,. Необходимым и достаточным условием достижения заданной точности выполнения функции f(x) является выполнение логического соотношения .Л , (., (Д) m-), (5) - -i / - I где и. - значение j-ro разряда в дво ичном представлении величины (Uy I , отсчитанного вправо от запятой. Таким образом, в устройстве реализуется следующий алгоритм вычисления элементарных функций, представленных в виде рядов Тейлора. В каждом цикле вычислений очередной член ряда представляется в виде произведения трех сомножителей: значения предмдущего члена ряда, множителя, являющегося функцией от аргумента х, и множителя, являющегося функцией номера члена ряда (1), причем мноиитель, являющийся функцией от аргумента х, для всех членов ряда имеет одно и тоже значение и вычисляется на подготовительном этапе, а множитель, являющийся функцией от номера члена ряда, ввиду ограниченности количества вычисляемых членов ряда, вычисляется табличным методом с помощью постоянных запоминающих устройств (табл. 3). При выпол нении основного этапа вычислений функ ций операции, которые могут быть выполнены одновременно с другими, совме щаются по времени (выборка констант и работа первого умножителя 3, второго умножителя 4 и сумматора 2 ). Устройство в соответствии с алгоритмом вь1числений работает следующим образом. Первоначально регистры , 15 и 17 и счетчик 14 устанавливаются в нул вое состояние. При поступлении в блок 1 управления сигнала запроса на вычисление функции f(х), на регистр 15 операций принимается код операции, на регистр 7 - аргумент х, на регистр 17 ошибки - значение заданной погрешности вычислений Д .Причем значения аргу мента X 7 1, например, для двоичной системы счисления с фиксированной запятой представляются с учетом масштаба аргумента т, а значения погрешности вычислений с учетом масштаба функции П(табл. 4). Код операции с регистра 15 поступает на дешифратор 16, на выходе которого формируется сигнал выполняемой операции. 70710 поступающий в блок 1 управления, Блок 1 управления по сигналу Пуск начинает вырабатывать управляющие сигналы в соответствии с временной диаграммой (фиг. 3). При этом по каждому синхроимпульсу с выхода формирователя 22 синхроимпульсов в регистрах сдвига осуществляется последовательный сдвиг единицы, записанной вначале в регистр 23 сдвига (фиг, 2). Регистры 23 и 24 сдвига предназначены для организации подготовительного этапа, а регистр 25 сдвига - для организации основного этапа вычислений функций. Работа устройства синхронизируется четырьмя сериями синхроимпульсов (CHIrCHi), сдвинутых относительно друг друга. Рассмотрим работу устройства на примере вычисления функций sinx, cos X, arcs in х, . In 1i , shx, ch X, arsh x, (ItxHC Ha подготовительном этапе при функций sin х. In Зу arcsin X, sh х, arsh х в регистр «э по одному из управляющих сигналов, сформированному группой 32 (фиг. 2), передается с регистра 7 заданный аргумент X, при этом структурно производится сдвиг с учетом масштаба функции т. (табл.,4). При вьтислеНИИ функций (НхИ) cos X, е , chx в регистр 6 заносится единица с учетом масштаба функции т. Тем самым в регистре 6 формируется начальный член ряда УоСтабл. 5). При выбранных значениях масштабных коэффициентов группа 32 вырабатывает управляющие сигналы Р7- Рб для arsh х;; Рб для 7. )-PJ - р6 для 1п IfL ,arcs in х , e-j 2 для сЬ х; 2 Р7 - Рб для д-Ьх; Рб для соз х; Рб для (1 ± х;- /ДЛЯ sinx; 2 Содержимое регистра 6 передается в регистр 5 Кроме того, на подготовительном этапе вычисляется значение псевдоаргумента S(x). Величина псевдоаргумента fCx) может принимать значение либо х (для функций (1 -х) е , либо -X. (для (1+хИ, либо х (для InjfTx arcsin х, sh х, ch х), либо (для sin X, cos х, arsh х). Если f(x) tx, то функция относится к первому типу, если Ч (х) ±х,- ко второму типу. Сигналы типов операций формируются элементами ИЛИ 41 и 42. Выход первого регистра 23 сдвига при выиислении функций первого типа с помощью элемента И kk подключается к входу третьего регистра 25 сдви,га, при вычислении функций второго т па с помощью элемента И А5 - к входу второго регистра 2 сдвига. Для вычи ления величины псевдоаргумента х содержимое регистра 7 пере дается в регистр 8 и запускается умножитель t. Результат умножения заносится в регистр 7 псевдоаргумента и хранится в нем до окончания вычислений. При выполнении операций с использованием отрицательного значения псевдоаргумента Ч (х), на вход умножителя 4 выдается инверсное значение кода. На подготовительном этапе при вычислении функций cos х, ch X, (1-t х) суммирующий счетчик сигналом с выхода группы 31 устанавливается в 1. При вычислении други функций суммирующий счетчик первоначально устанавливается в О. Основной этап вычислений для всех функций f(х) выполняется одинаково и построен по принципу глубокого совмещения тактов. В каждом такте вы полняются следующие действия: а) выборка очередной константы t)(l) по содержимому суммирующего счетчика 14; 2)умножение на умножителе Ц выбранной константы IP{i) на псевдоаргумент Ч (х); 3)умножение на умножителе 3 содержимого накапливающего регистра 6 на результат умножения f (х). Ч (-f), полученный в предыдущем такте; k) вычисление очередного прибли женного значения фукнции путем сумМирования результата умножения, полученного на умножителе 3 в предыдущем такте, с содержимым накапливающего регистра 5 :)U iU)-Uo-i-.lUH-«-Ur i- . . 5) сравнение в блоке 18 результата умножения, полученного в данном такте на умножителе 3, с содержимым регистра 17 ошибки и выдача сигнала сброса в блок 1 управления при дости жении заданной точности вычислений; 6) увеличение содержимого суммиру ющего счетчика Т на единицу (при вы числении ФУНКЦИЙ.5In X, cos X, arcsln X, arsh х, sh х, ch х, (Нх) содержимое счетчика 1 у&еличивается на 1 дважды). в начале основного этапа вычислений с помощью регистра 25 сдвига управляющие триггеры 26-30 последовательно устанавливаются в 1. Единичные состояния управляющих триггеров 26-30. разрешают выработку по соответствующему синхроимпульсу элементами И сигналов, управляющих работой устройства (фиг. 2 и з). Причем группа 33 вырабатывает сигналы Пуск ПЗУ-1 (для е Пуск ПЗУ-2 для sm x,.cos X, sh X и ch х), Пуск ПЗУ-3 (для In li| ), Пуск ПЗУ-4 (arcsin X, arsh х, (lixr). Группа 35 вырабатывает сигналы передачи содержимого регистра 7 на вход умножителя 4 без изменения () для функций с Ч (х) X и IP (х) х и с инверсией ( УМ2) для функций с Ч(х) -X и Ч (х) -X . Управляющие сигналы вырабатываются периодически до сброса управляющих триггеров 26-30. I Первый такт вычислений функций €(х) осуществляется следующим образом. По содержимому счетчика 14 через коммутатор 13 в зависимости от управляющего сигнала с выхода группы 33 осуществляется обращение к одному из блоков 9-12 памяти. В результате аего осуществляется выборка первой константы одного из следующих видов 21-1 1 1 „ ;. 2I(2i4-T) 2i(2i - 1) 1 . (21-1) 21-1 (табл. з). ВыТ 2i(2W) 2i-fr бранная константа принимается на регистр 8 и запускается умножитель 4 для вычисления произведения псевдоаргумента Ц( х на константу Ц(-}) . Полученное произведение передается на вход умножителя 3i на котором оно умножается на содержимое регистра 6. К этому времени содержимое счетчика 14 изменяется в соответствии с логикой работы, приведенной в табл. 6, либо на 1, либо на 2. Через коммута-, тор 13 производится обращение к одному из блоков 9-12 памяти и выбирается очередная константа, которая принимается на регистр 8. На умножителе 4 производится умножение очередной константы Ц)(/{) на пceвдoapгyмeнт f(x . В это время сумматор 2 суммирует содержимое регистра 5 с результатом множения, полученным на умножителе 3. Результат суммирования заносит ся в накапливающий регистр 5. Кроме того, в блоке 18 производится сравнение результата, полученного на yMHO жителе 3, с содержимым регистра 17. При достижении заданной точности вы числений, т.е. при выполнении условия А, блок 19 выдает в блок 1 управления сигнал остановки процесса Работа устройства в следующих так тах производится аналогично. После окончания вычислений все схемы приводятся в исходное состояние, резуль тат операции снимается с ре/-истра 5. Таким образом, использование устройства в универсальных и специализированных ЭВМ позволяет расширить

14: X i;|- i:|:| xI.,, )1

1/1

(Itxr

sin X

cos X

1 4х 4 ЗУ-

х . Х7

Ux

2 xtf | Ш г1 ---1Ч« |х|.,

X

х5

3 5f + + ... |х|

arshxк - . V..:.|... (X/ 1 /х|

|х I tso |х| :S 2П ;х|:$2П

)х) оо I х| «2

у-ц. ... 1Х| 1

|x)s4 функциональные возможности за счет реализации указанных функций; сэкономить память, предназначенную для хранения соответствующих стандартных подпрограмм и констант; повысить производительность ЭВМ за счет сокращения в 1,,0 раза времени вычисления этих функций; уменьшить в раз загрузку арифметического устройства; повысить производительность ЭВМ за счет исключения затрат времени на вызов той или иной стандартной подпрограммы из внешней памяти в оперативную; повысить надежность ЭВМ и достоверность результатов вычислений как за счет экономии памяти для подпрограмм, так и за счет повышения производительности. Таблица 1 k

98370716

15

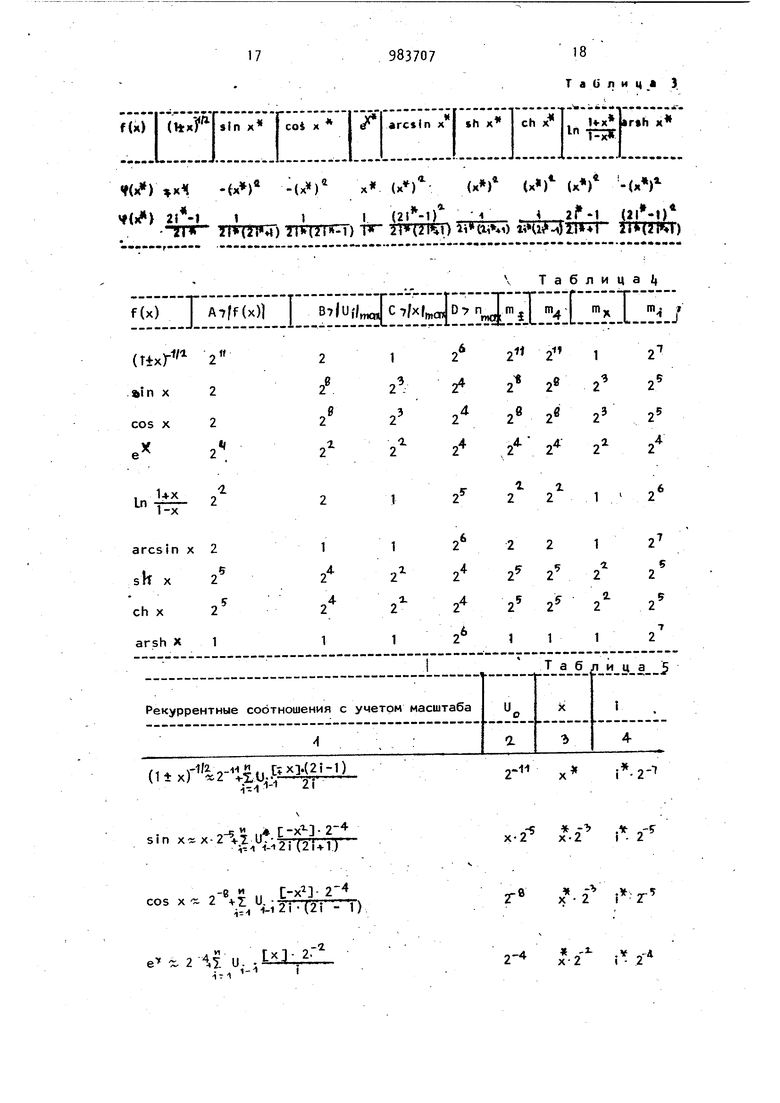

Таблица 2 «f() -tx) -{х)X (х) V( 2i -l1 1 ()

т а U л и ц А 3 (х) 1х«Л (xV -(xV ( агс,1пххх.2-1Ьа -|тТтТТ

X. 2U-U

shx J, Vi2I-()

.{

с 9

ch X ct , Ь$ J

.(2i - Т)

1; п i:xn-(2i-i)

arsh х- i .г II Lx j-A/:i-lj

..l: :lliA-j.2hl2i±Tl

sin X, sh X, arcsin, arshx

cos X, ch X, (1±хИ

Ux

x

In Формула изобретения 1, Устройство для вычисления элементарных функций, содержащее два накопительных регистра, сумматор, первый умножитель, схему сравнения, формцрователь импульсов сброса, блок управления и блок памяти, причем управляющие рходы первого и второго накопительны регистров соединены соответственно с первым и вторым выхода ми блрка управления, третий и четвер тый выходы которого соединены с управ ляющими входами соответственно сумматора и первого умножителя, выход которого соединен с информационным входом второго накопительного регистра, первым информационным входом суммато ра и первым входом схемы сравнения, выход которой через формирователь импульсов сброса соединен с первым

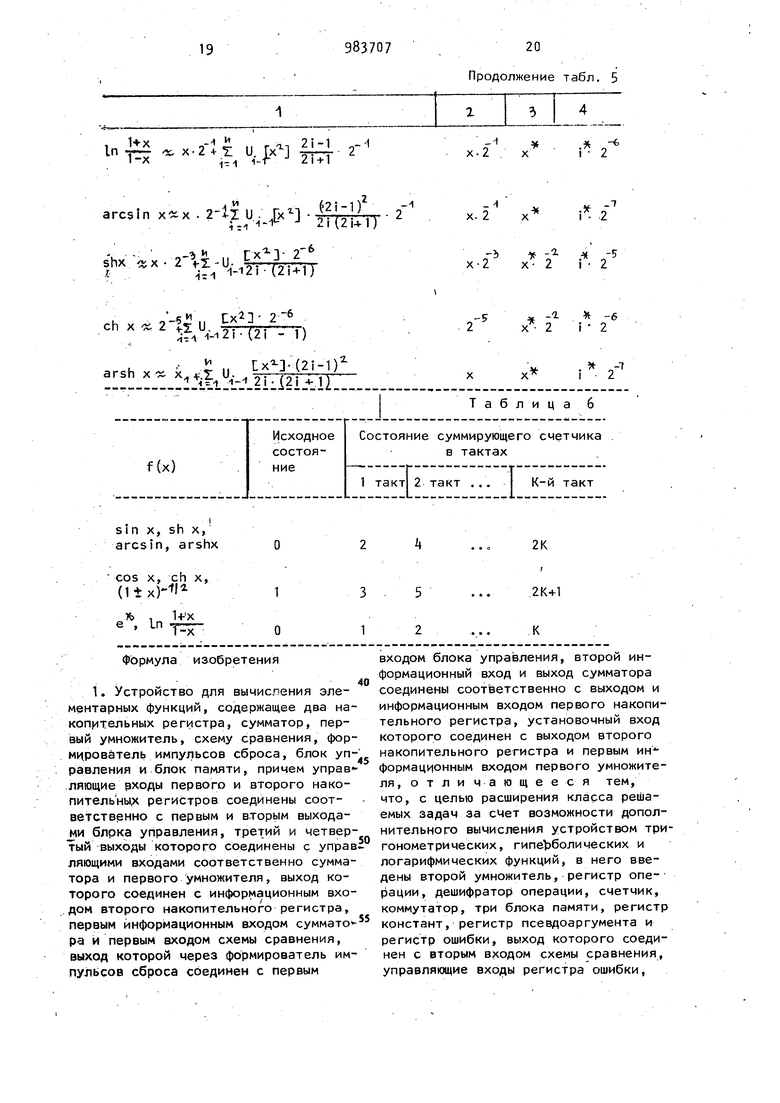

Продолжение табл. 5

-Ь1f - ,:)( -5

х-2 х- 2 i 2

-5 -а -6

г 2 i 2

i . 2-Таблицаб

2K

.2K+1

К -Н - X. 2 2 входом блока управления, второй информационный вход и выход сумматора соединены соответственно с выходом и информационным входом первого накопительного регистра, установочный вход которого соединен с выходом второго накопительного регистра и первым информационным входом первого умножителя, отли чающееся тем, что, с целью расширения класса peiiiaемых задач за счет возможности дополнительного вымисления устройством тригонометрических, гипе эболимеских и логарифмических функций, в него введены второй умножитель, регистр операции, дешифратор операции, счетчик, коммутатор, три блока памяти, регистр констант, регистр псевдоаргумента и регистр ошибки, выход которого соединен с вторым входом схемы сравнения, управляющие входы регистра ошибки, второго умножителя, счетчика, комму,татора, регистра констант и регистра псевдоаргумента соединены соответственно с пятого по десятый выходами блока управления, второй вход которого соединен через дешифратор операции с выходом регистра операци1, выход счетчика соединен с инфор мационным входом коммутатора, выходы с первого по четвертый которого соединены с входами соответственно с первого по четвертый блоков памяти, выходы которых соединены с первым ин формационным входом регистра консттант, второй информационный вход которого соединен с выходом регистра псевдоаргумента и первым информацион ным входом второго умножителя, второ информационный вход которого соедине с выходом регистра констант, выход BTCiporo умножителя соединен с информационным входом регистра псевдоаргу мента, выход которого соединен с установочным входом второго накопитель ного регистра, второй информационный вход первого умножителя соединен с выходом второго умножителя. 2. Устройство по п. 1, о т л и чающееся тем, что блок управ ления содержит генератор импульсов, формирователь синхроимпульсов, три сдвиговых регистра, пять триггеров, десять групп элементов И, три элемента ИЛИ и два элемента И, входы первого и второго элементов ИЛИ и первые входы элементов И с первой по пятую групп соединены с вторым входо блока управления, выход генератора импульсов соединен с входом формирователя синхроимпульсов, выходы с первого по четвертый которого соединены с входами третьего элемента ИЛИ выход которого соединен с синхровходами регистров сдвига, выход переполнения первого регистра сдвига соединен с первыми входами первого и второго элементов И, вторые в)рды ко торых соединены с выходами соответст вующих элементов ИЛИ, выход первого элемента И соединен с информационным входом второго регистра сдвига, выход переполнения которого подключен к информационному входу третьего регистра сдвига и выходу второго элемента И, выходы разрядов с первого по пятый третьего регистра сдвига соединены с первыми входами соответстг венно с первого по пятый триггеров, вторые входы которых подключены к первому входу блока управления,выходы первого и второго разрядов первого регистра сдвига соединены с вторыми входами элементов И соответственiно первой и второй групп, выход первого триггера соединен с вторыми входами элементов И третьей группы, третьи входы которых соединены с четвертым выходом формирователя синх«роимпульсов, выход второго триггера соединен с вторыми входами элементов И четвертой и пятой групп и первыми входами элементов И шестой руппы, вторые входы которых соеди, с первым выходом формирователя синхроимпульсов, третьими входами эле ментов И четвертой и пятой групп и первыми входами элементов И седьмой группы, вторые входы которых соединены с выходом пятого триггера, четвертые входы элементов И пятой группы соединены с вторым выходом формирователя синхроимпульсов, четвертый выход которого соединен с первыми входами элементов И восьмой группы, вторые входы которых соединены с выходом третьего триггера, выход четвертого триггера соединен с первыми входами элементов И девятой и десятой групп, вторые входы которых подключены к третьему выходу формирователя синхроимпульсов, выход первого разряда первого регистра сдвига соединен с первым, вторым, третьим, четвертым, шестым и девятым выходами блока управления, выход третьего разряда первого регистра сдвига соединен с первым выходом блока управления, выходы разрядов с первого по третий второго регистра сдвига соединены соответственно с девятым, шестым и десятым выходами блока управления, выходы элементов И первой группы, соединены с седьмым выходом блока управления, с вторым выходом ко- торого соединены выходы элементов И второй группы, выходы элементов И третьей группы соединены с восьмым выходом блока управления, шестой, выход которого соединен с выходами элементов И четвертой и шестой групп,i, выхЬды элементов И пятой группы соединены с седьмым выходом управления, четвертый, второй, третий и первый выходы которого соединены с выходами элементов и

98370721

соответственно восьмой, девятой, десятой и седьмой групп. Источники информации, 538366 кл. GОб F 7/556, 1976

внимание при экспертизе 5 (прототип) .

принятые во

fi /fOMO Z- Sfd

tmeMfta. 19 Фа.г Вт fjroifu fff /fiff I y,fftT ff y ifSMttyS f-«1 - r l ffjfff/ta л, /4«иу7о JffjfffiiyS

Авторы

Даты

1982-12-23—Публикация

1981-07-17—Подача