Изобретение относится к технической кибернетике и может быть использовано в научных исследованиях и технике, где требуется определять оптимальные периоды между текущими ремонтами изделий, па которых проводятся плановые ремонты двух видов - текущие и капитальные, например, для изделий, эксплуатирующихся на объектах нефтяного производства, для которых вышестоящей организацией (производственным объединением) разрешено корректировать существующие межремонтные периоды при изменении условий эксплуатации, технологии и организации ремонта и т. д.

Целью изобретения является повышение точности устройства.

Для промышленных объектов, в частности для объектов нефтяного производства, характерно использование конструктивно сложных изделий, на которых проводятся плановые ремонты двух видов (текущие и капитальные), а также осуществляются неплановые ремонты, связанные с отказами.

Одним из критериев качества функционирования таких изделий является удельная суммарная продолжительность ремонтов Sp. Математическое выражение такого критерия для изделия, на котором проводятся текущие, капитальный и неплановые ремонты, записывается в виде

S,, (m,/)

тзЛ (ffl,/)+T2+Ti (т--1)

mi

где / - межремонтный пер)иод, /;

m - количество межремонтных периодов между двумя капитальными ремонтами;

t1

Эксплуатирующееся состоящим из элементов элементы, изнашивающ быстро; Ш2 - элементы сравнительно медленно. сов суммарной наработк монтный период, провод ты, полностью обновляю через каждые mt часов, ный цикл, проводятся ты, полностью обновляю 112, при возникновении неплановые ремонть, ос нимально возможном об сивность отказов издел изменяется.

Для указанных выш рий (Г) записывается в

S|.(m,t) 1

тз (x)dx+S ,.2(j-- l)t + x dx}+T2+T,(m. 1)

mt

интенсивность отказов элементов к-го типа, к 1,2;

индекс межремонтного периода внутри ремонтного цикла ,т;

наработка на .межремонтном периоде с индексом /.

т tn Н

.2 b(j-l) .У

(t i a-i)t

т

,Е -1„Р2{( l)t -l,,P2(nit),

Г

гдеРк(/) -функция надежности элементов

к-го типа, выражение (2) приводится к виду

с; /-П --T3 mlnPi(t)+ lnP2(mt)l + Т2+Т|(П1 :з. ni,L)-0

5

5

0

0

Т, Т2, T;i - средние продолжительности одного текущего, капитального и непланового ремонтов соответстенно, г; /(т,() -математическое ожидание числа отказов изделия за время между двумя капитальными ремонтами. Этот критерий, по сравнению с обычно используемыми критериями, такими как коэффициент готовности /(г, коэффициент технического использования Кт и др., обладает большей чувствительностью к изменениям входящих в него величин (так как значение SP близко к нулю и значительно меньше значений Кг, /С™, которые близки к единице).

Дальнейшая формализация критерия (1) осуществляется при следующих допущениях, справедливых для указанных объектов.

Эксплуатирующееся изделие представим состоящим из элементов двух типов: W - элементы, изнашивающиеся сравнительно быстро; Ш2 - элементы, изнашивающиеся сравнительно медленно. Через каждые / часов суммарной наработки, т. е. через межремонтный период, проводятся текущие ремонты, полностью обновляющие элементы шк через каждые mt часов, т. е. через ремонтный цикл, проводятся капитальные ремонты, полностью обновляющие элементы w и 112, при возникновении отказов проводятся неплановые ремонть, осуществляемые в минимально возможном объеме, так что интенсивность отказов изделия существенно не изменяется.

Для указанных выше допущений критерий (Г) записывается в виде

40

С учетом следуюн их преобразований, вытекающих из математических основ теории надежности.

т t

X li{x)dx - -/ г/лЯ|:/1 Г« -

(3)

P2(it)

(4)

(5)

более простому и удобному в вычислительном отношении, чем выражение (2). Для изделий, эксплуатирующихся на объектах нефтяного производства, величина т обычно принимается неизменной при изменении условий эксплуатации изделий, уровня технологии и организации ремонта и т. д, поэтому минимизация критерия Sp (m,/) осуществляется по переменной / при фиксированном и известном т.

Поиск минимума Sp{m,t) по t при т const производится известным методом золотого сечения отрезка А, В, содержащего минимум Sp(m,t).

Алгоритм поиска минимума функции одной переменной Sp{t) методом золотого сечения отрезка А, В приведен ниже:

1)вычислить точки 1 и /2 золотого сечения отрезка А, В по формулам

/, Л + (В-Л)ь (6) /2 Л +(В-Л)(1-,}, (7)

где f I - 0,382;

2)вычислить значения Sp{t) в точках /1 и /2 по формуле (5), т. е. Sp(t) и Sp(/2);

3)вычислить относительную погрешность определения межремонтного периода

,у, . it

(8)

и сравнить ее с заданным значением е; если б( у, то за оптимальный межремонтный период / и минимальное значение Sp принимаются значения /i и Sp (Л); (переход к п. 5); иначе, т. е. если б, е, то переход к п. 4);

tnt

Sp(m,t) + (-L)

mt

Таким образом, сущностью технического решения является схемная реализация алгоритма поиска минимума функции Sp(m,0, задаваемой выражением (10), по t методом золотого сечения интервала А, В, содержащего минимум Sp(m,t) (при известных значениях т, , @, 2, ©2, TI-т.з. А, В).

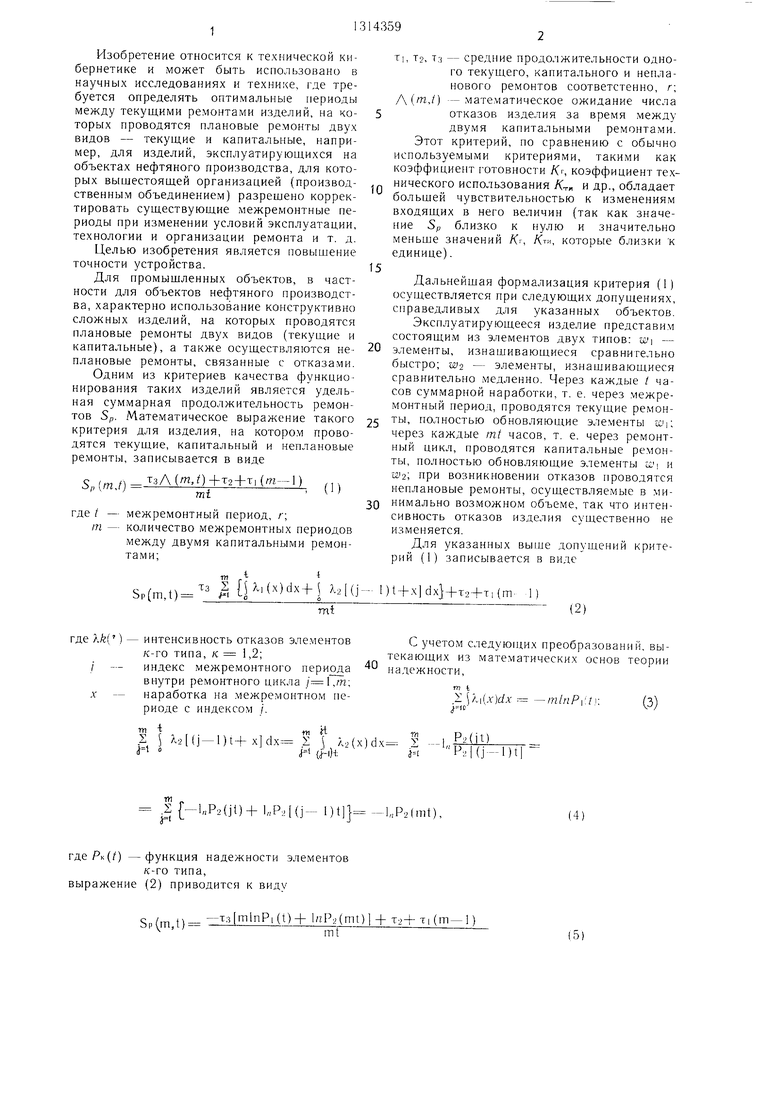

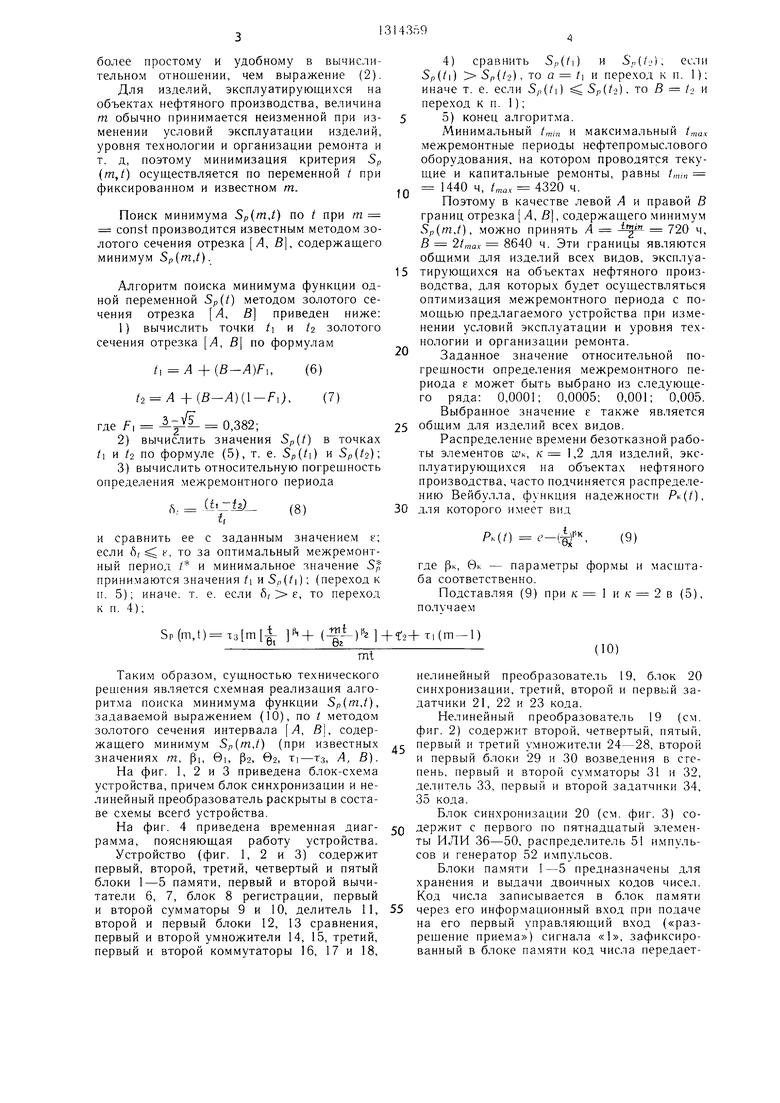

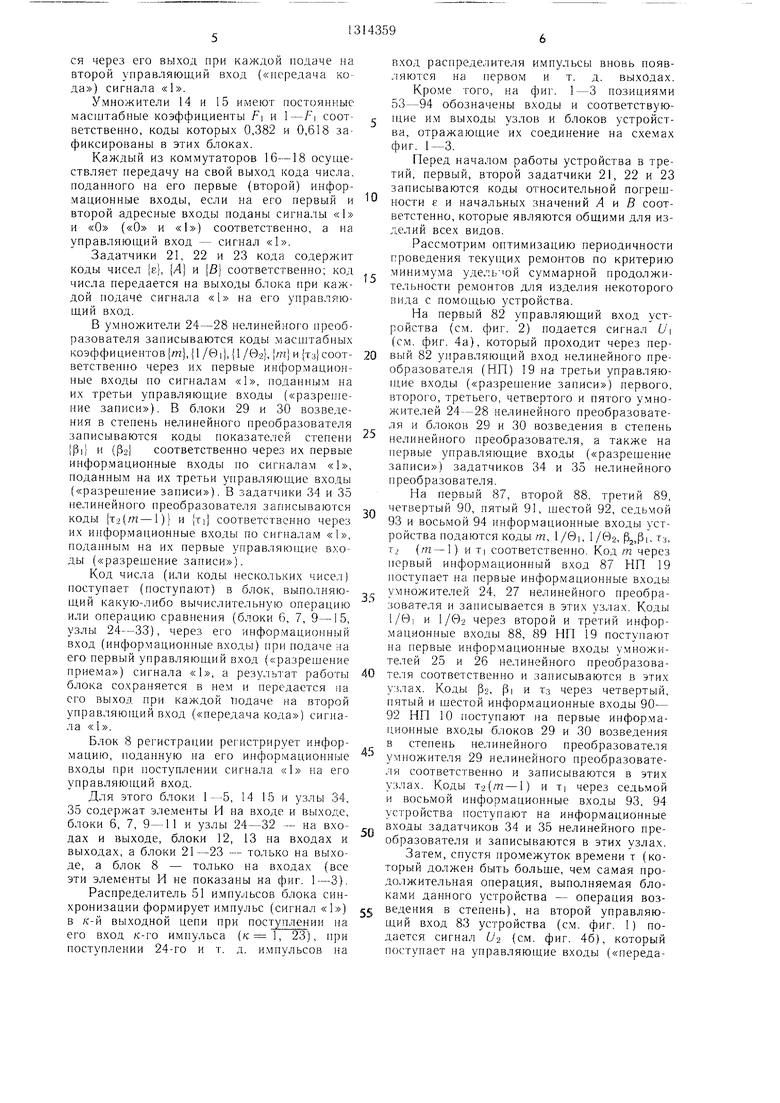

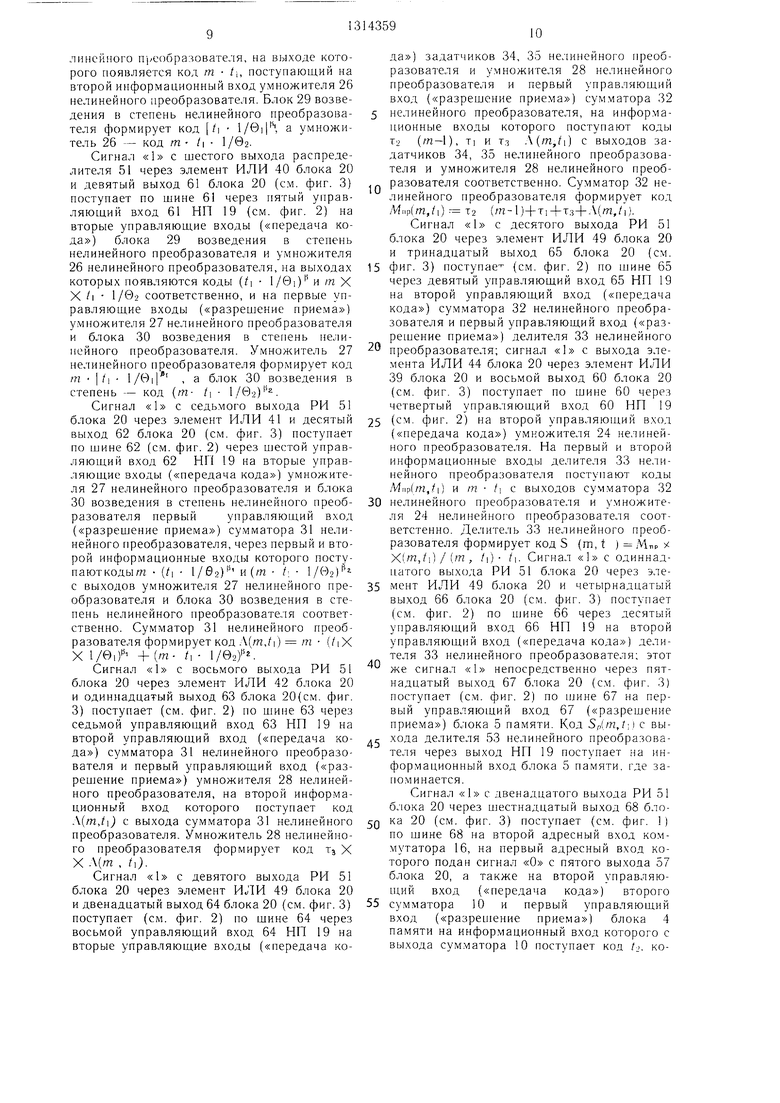

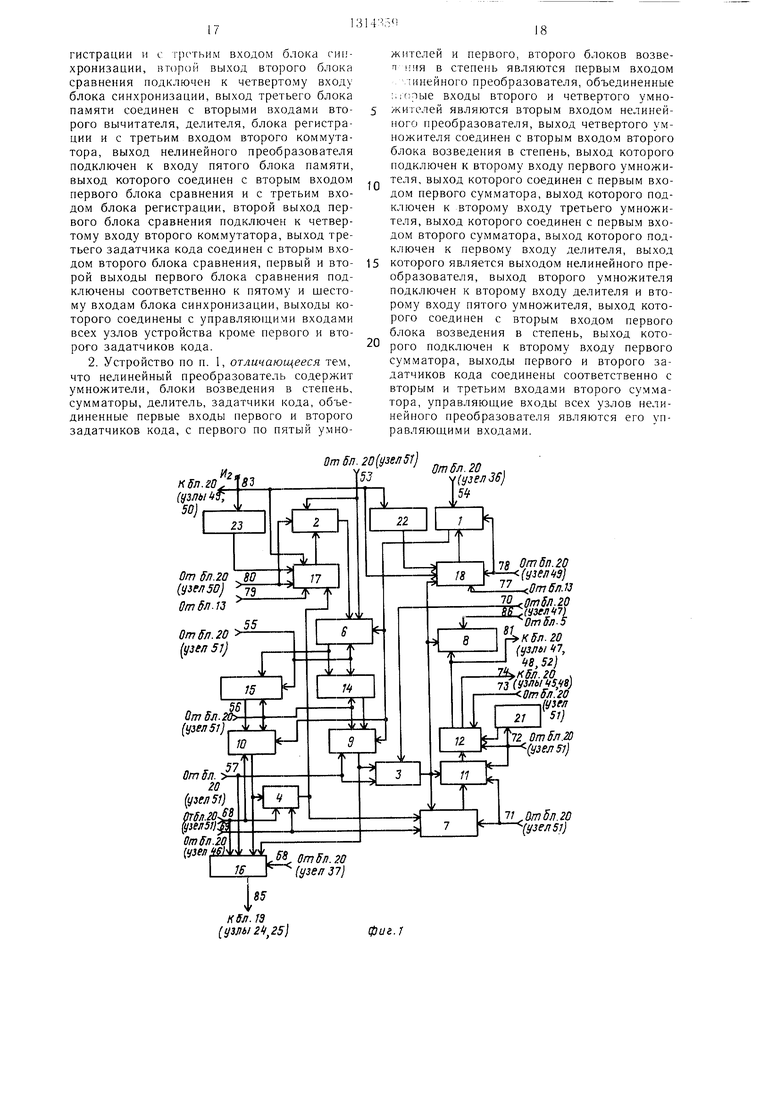

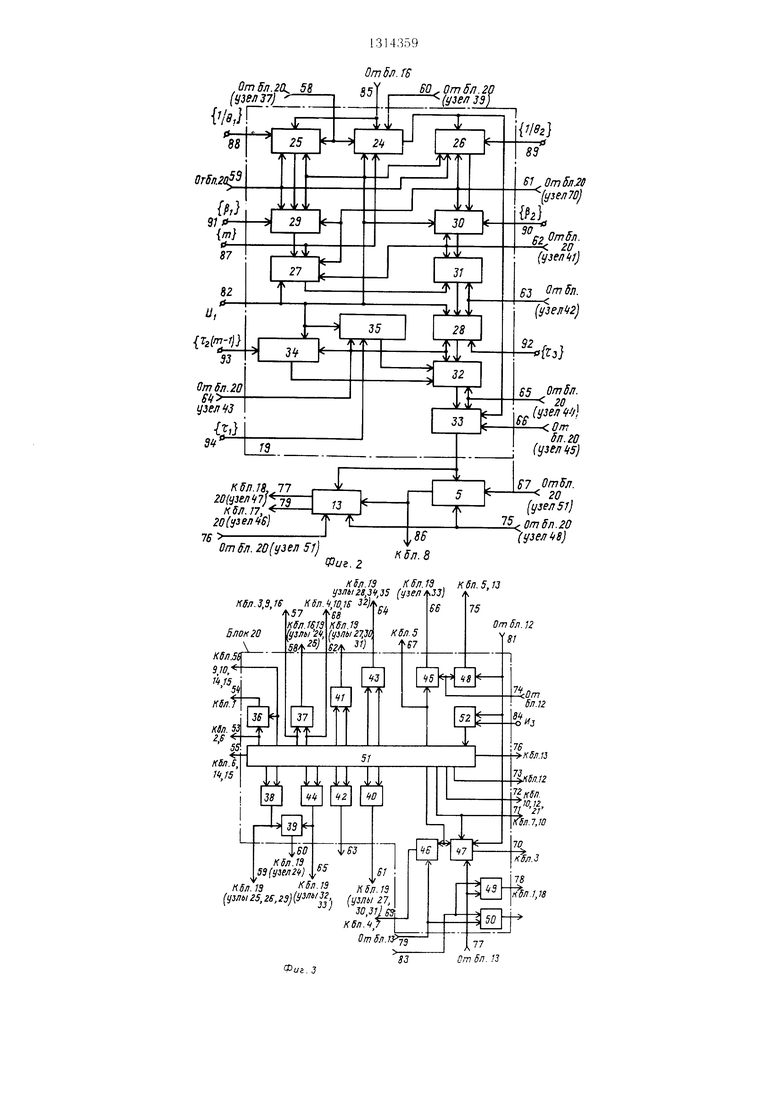

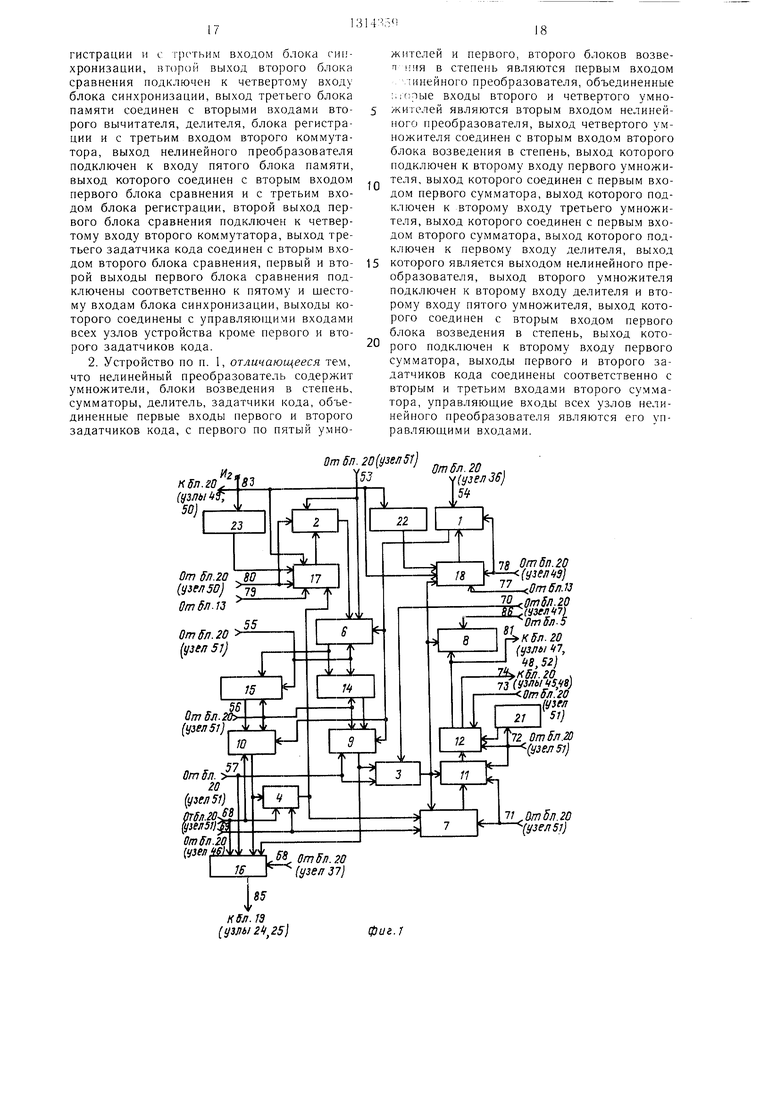

На фиг. 1, 2 и 3 приведена блок-схема устройства, причем блок синхронизации и нелинейный преобразователь раскрыты в составе схемы Bcerd устройства.

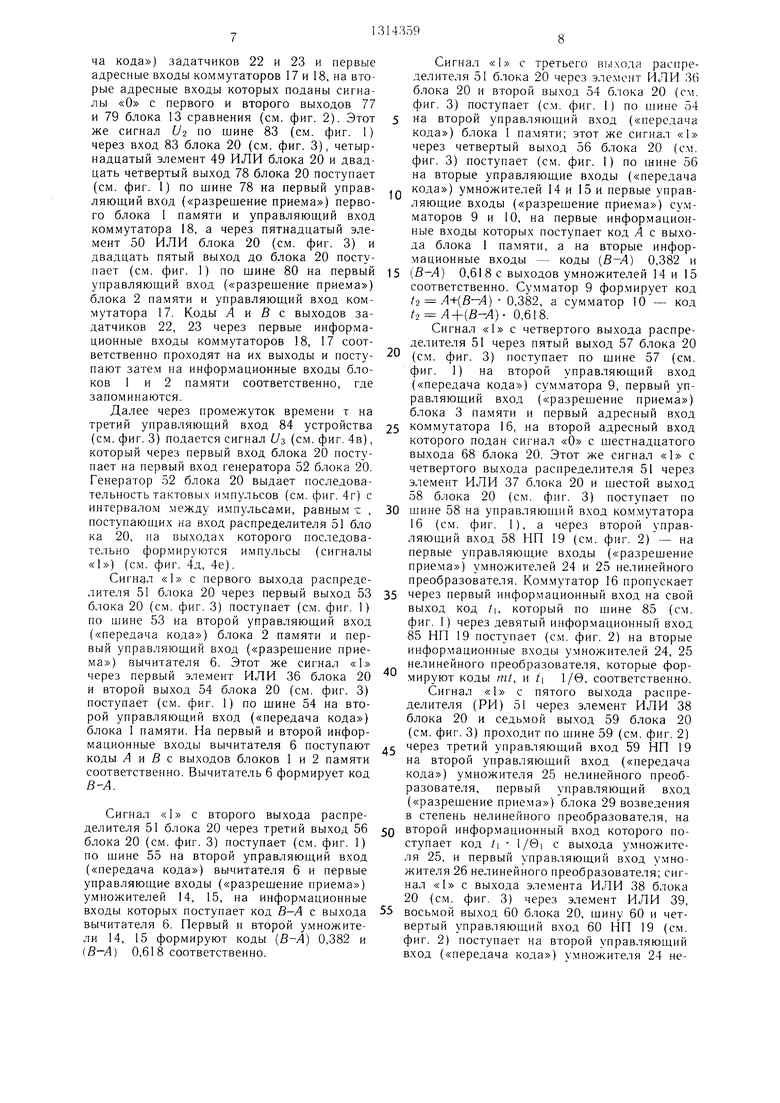

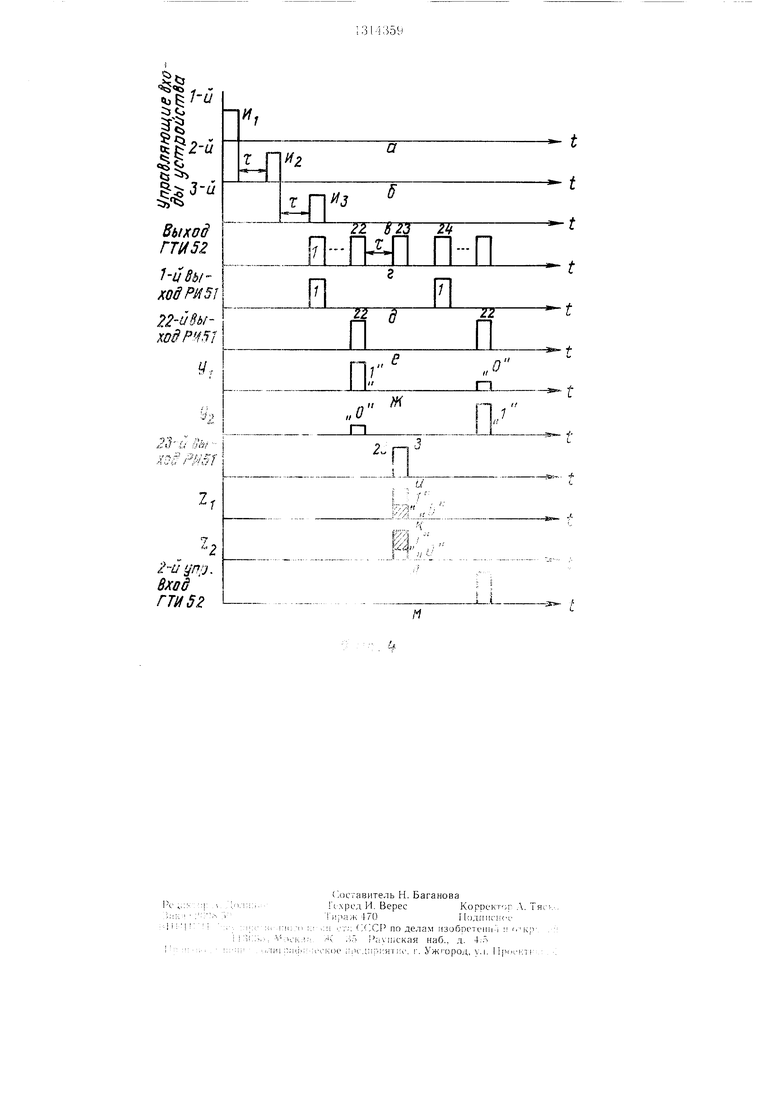

На фиг. 4 приведена временная диаг- рамма, поясняющая работу устройства.

Устройство (фиг. 1, 2 и 3) содержит первый, второй, третий, четвертый и пятый блоки 1-5 памяти, первый и второй вычи- татели 6, 7, блок 8 регистрации, первый и второй сумматоры 9 и 10, делитель 11, второй и первый блоки 12, 13 сравнения, первый и второй умножители 14, 15, третий, первый и второй коммутаторы 16, 17 и 18,

4) сравнить S,,(/i) и 5,,(/:0, если Sp(/i) Sp(/2), то а /: и переход к п. 1); иначе т. е. если 5,,(/i) 5р(/2). то S /: и переход к п. 1); 5) конец алгоритма.

Минимальный /,„,„ и максимальный /„,ал межремонтные периоды нефтепромыслового оборудования, на котором проводятся текущие и капитальные ремонты, равны /„„„

1440 ч, t,na, 4320 ч.

Поэтому в качестве левой А и правой В границ отрезка /4, В, содержащего минимум Sp(m,t}, можно принять А - 720 ч, В It max 8640 Ч. Эти границы являются общими для изделий всех видов, эксплуатирующихся на объектах нефтяного производства, для которых будет осуществляться оптимизация межремонтного периода с помощью предлагаемого устройства при изменении условий эксплуатации и уровня технологии и организации ремонта.

Заданное значение относительной погрешности определения межремонтного периода е может быть выбрано из следующего ряда: 0,0001; 0,0005; 0,001; 0,005. Выбранное значение е также является

общим для изделий всех видов.

Распределение времени безотказной работы элементов Шк, к 1,2 для изделий, эксплуатирующихся на объектах нефтяного производства, часто подчиняется распределению Вейбулла, функция надежности Рк(/),

для которого имеет вид

р(п -(4j

(9)

где (Зк, 0к - параметры формы и масштаба соответственно.

Подставляя (9) при к 1 и к 2 в (5), получаем

(10)

нелинейный преобразователь 19, блок 20 синхронизации, третий, второй и первый за- датчики 21, 22 и 23 кода.

Нелинейный преобразователь 19 (см. фиг. 2) содержит второй, четвертый, пятый, первый и третий умножители 24-28, второй и первый блоки 29 и 30 возведения в степень, первый и второй сумматоры 31 и 32, делитель 33, первый и второй задатчики 34, 35 кода.

Блок синхронизации 20 (см. фиг. 3) содержит с первого по пятнадцатый элементы ИЛИ 36-50, распределитель 51 импульсов и генератор 52 импульсов.

Блоки памяти I-5 предназначены для хранения и выдачи двоичных кодов чисел. Код числа записывается в блок памяти через его информационный вход при подаче на его первый управляющий вход («разрешение приема) сигнала «1, зафиксированный в блоке памяти код числа передается через его выход при каждой подаче па второй управляющий вход («передача ко да) сигпала «1.

Умножители 14 и 15 имеют постоянные маештабные коэффициепты F и 1-Г еоот ветственпо, коды которых 0,382 и 0,618 зафиксированы в этих блоках.

Каждый из коммутаторов 16-18 осуществляет передачу на свой выход кода числа, поданного па его первые (второй) информационные входы, если на его первый и второй адресные входы поданы сигналы «1 и «О («О и «1) соответственно, а на управляющий вход - сигнал «1.

Задатчики 21, 22 и 23 кода содержит коды чисел {Е}, {А} и {В соответственно; код числа передается на выходы блока при каждой подаче сигнала «1 на его управляющий вход.

В умножители 24-28 нелинейного преобразователя записываются коды масштабных коэффициентов {т}, (-) Г), {1/62}, и {тз) соответственно через их первые информационные входы по сигналам «1, поданны.м на их третьи управляющие входы («разрешение записи). В блоки 29 и 30 возведения в степень нелинейного преобразователя записываются коды показателей степени iPiJ и (Pal соответственно через их первые инфор.мационные входы по сигмала.м «1, поданным на их третьи управляющие входы («разрешение записи). В задатчики 34 и 35 нелинейного преобразователя записываются коды {т2(/п-1)} и соответственно через их информационные входы по сигнала. «1, поданным на их первые управляющие входы («разрешение записи).

Код числа (или коды нескольких чисел) поступает (поступают) в блок, выполняющий какую-либо вычислительпую операцию или операцию сравнения (блоки 6, 7, 9-15, узлы 24-33), через его информационный вход (информационные входы) при подаче на его первый управляющий вход («разрешение приема) сигнала «1, а результат работы блока сохраняется в нем и передается па его выход при каждой тюдаче на второй управляющий вход («передача кода) сигнала «1.

Блок 8 регистрации регистрирует информацию, поданную на его информационные входы при поступлении сигнала «1 на его управляю1ций вход.

Для этого блоки 1-5, 14 15 и узлы 34,

35 содержат элементы И на входе и выходе, блоки 6, 7, 9-11 и узлы 24-32 - на входах и выходе, блоки 12, 13 на входах и выходах, а блоки 21-23 - только на выходе, а блок 8 - только на входах (все эти элементы И не показаны на фиг. 1-3).

Распределитель 51 импульсов блока синхронизации формирует и.мпульс (сигнал «1) в к-и выходной цепи при поступлении на его вход к-го импульса (к 1, 23), при поступлении 24-го и т. д. ИМПУЛЬСОВ на

5

.5

вход распределителя импульсы вновь появ- ;1яются на первом и т. д. выходах.

Кроме того, на фиг. 1-3 позициями 53-94 обозначены входы и соответствую- П1ие и.м выходы узлов и блоков устройства, отражающие их соединение на схемах фиг. 1-3.

Перед началом работы устройства в третий, первый, второй задатчики 21, 22 и 23 записываются коды относительной погрещ- ности е и начальных значений А и В соот- ветстенно, которые являются общи.ми для изделий всех видов.

Рассмотрим оптимизацию периодичности проведения текущих ремонтов по критерию минимума удель юй суммарной продолжительности ремонтов для изделия некоторого вида с помощью устройства.

На первый 82 управляющий вход устройства (см. фиг. 2) подается сигнал U (см. фиг. 4а), который проходит через пер- 0 вый 82 управляющий вход нелинейного преобразователя (НП) 19 на третьи управляющие входы («разрещение записи) первого, BTOpoi o, третьего, четвертого и пятого умножителей 24-28 нелинейного преобразователя и блоков 29 и 30 возведения в степень нелинейного преобразователя, а также на первые управляющие входы («разрешение записи) задатчиков 34 и 35 нелинейного преобразователя.

На первый 87, второй 88, третий 89, четвертый 90, пятый 91, шестой 92, седьмой 93 и восьмой 94 информационные входы устройства подаются коды т, 1/в|, 1/02, 2,- , Tj (т-1) и Т| соответственно. Код т через первый информационный вход 87 НП 19 поступает па первые информационные входы умножителей 24. 27 нелинейного преобра- зов-ателя и записывается в этих узлах. Коды 1/Bi и 1/82 через второй и третий информационные входы 88, 89 ПП 19 поступают на первые информационные входы умножителей 25 и 26 нелинейного преобразователя соответственно и записываются в этих узлах. Коды Ра, PI и тз через четвертый, пятый и шестой информационные входы 90- 92 НП 10 поступают на первые информа- 11,ионные входы блоков 29 и 30 возведения в степень нелинейного преобразователя умножителя 29 нелинейного преобразователя соответственно и записываются в этих узлах. Коды т2(/7г-1) и Т| через седьмой и восьмой информационные входы 93, 94 устройства поступают на инфор.мационные входы задатчиков 34 и 35 нелинейного преобразователя и записываются в этих узлах.

Затем, спустя про.межуток вре.мени т (который должен быть больше, чем самая продолжительная операция, выполняемая блоками данного устройства - операция воз- 5 ведения в степень), на второй управляющий вход 83 устройства (см. фиг. 1) подается сигнал Uz (см. фиг. 46), который поступает на управляющие входы («переда0

5

5

0

ча кода) задатчиков 22 и 23 первые адресные входы коммутаторов 17 и 18, на вторые адресные входы которых поданы сигналы «О с первого и второго выходов 77 и 79 блока 13 сравнения (см. фиг. 2). Этот же сигнал Uz по шине 83 (см. фиг. 1) через вход 83 блока 20 (см. фиг. 3), четырнадцатый элемент 49 ИЛИ блока 20 и двадцать четвертый выход 78 блока 20 поступает (см. фиг. 1) по шине 78 на первый управ- ляюший вход («разрешение приема) первого блока 1 памяти и управляющий вход коммутатора 18, а через пятнадцатый элемент 50 ИЛИ блока 20 (см. фиг. 3) и двадцать пятый выход до блока 20 поступает (см. фиг. 1) по шине 80 на первый управляюший вход («разрешение приема) блока 2 памяти и управляюший вход ком- .мутатора 17. Коды А н В с выходов за- датчикоЕ 22, 23 через первые информационные входы коммутаторов 18, 17 соответственно проходят на их выходы и поступают затем на информационные входы блоков 1 и 2 па.мяти соответственно, где запоминаются.

Далее через промежуток времени т на третий уцравляюш.ий вход 84 устройства (см. фиг. 3) подается сигнал L/z (см. фиг. 4в), который через первый вход блока 20 поступает на первый вход генератора 52 блока 20. Генератор 52 блока 20 выдает последовательность тактовых импульсов (см. фиг. 4г) с интервалом между импульсами, равным г , поступаюших на вход распределителя 51 бло ка 20, на выходах которого последовательно формируются импульсы (сигналы « 1) (см. фиг. 4 д, 4е).

Сигнал «1 с первого выхода распределителя 51 блока 20 через первый выход 53 блока 20 (см. фиг. 3) поступает (см. фиг. 1) по шине 53 на второй управляющий вход («передача кода) блока 2 памяти и первый управляюший вход («разрешение приема) вычитателя 6. Этот же сигнал «1 через первый элемент ИЛИ 36 блока 20 и второй выход 54 блока 20 (см. фиг. 3) поступает (см. фиг. 1) по шине 54 на второй управляющий вход («передача кода) блока 1 памяти. На первый и второй информационные входы вычитателя 6 поступают коды Л и S с выходов блоков 1 и 2 памяти соответственно. Вычитатель 6 формирует код В А.

Сигнал «1 с второго выхода распределителя 51 блока 20 через третий выход 56 блока 20 (см. фиг. 3) поступает (см. фиг. 1) по шине 55 па второй управляющий вход («передача кода) вычитателя 6 и первые управляющие входы («разрешение приема) умножителей 14, 15, па информационные входы которых поступает код В-А с выхода вычитателя 6. Первьсй и второй умножители 14, 15 формируют коды () 0,382 и (В-А) 0,61 8 соответственно.

Сигнал «1 с третьего вькхода распределителя 51 блока 20 через элемент ИЛИ 36 блока 20 и второй выход 54 блока 20 (см. фиг. 3) поступает (с.м. фиг. 1) по шине 54 5 на второй управляющий вход («передача кода) блока 1 памяти; этот же сигнал «1 через четвертый выход 56 блока 20 (см. фиг. 3) поступает (см. фиг. 1) по шине 56 на вторые управляющие входы («передача

„ кода) умножителей 14 и 15 и первые управляющие входы («разрешение приема) сумматоров 9 и 10, на первые информационные входы которых поступает код А с выхода блока 1 памяти, а на вторые информационные входы - коды (В-А) 0,382 и

5 (В-А} 0,618с выходов умножителей 14 и 15 соответственно. Сумматор 9 формирует код f2 A+(B-A) 0,382, а сумматор 10 - код /,, Л+(В-Л)- 0,618.

Сигнал «1 с четвертого выхода распределителя 51 через пятый выход 57 блока 20

0 (см. фиг. 3) поступает по шине 57 (см. фиг. 1) на второй управляющий вход («передача кода) сумматора 9, первый управляющий вход («разрешение приема) блока 3 памяти и первый адресный вход

5 коммутатора 16, на второй адресный вход которого подан сигнал «О с шестнадцатого выхода 68 блока 20. Этот же сигнал «1 с четвертого выхода распределителя 51 через элемент ИЛИ 37 блока 20 и шестой выход 58 блока 20 (см. фиг. 3) поступает по

0 щине 58 на управляюший вход коммутатора 16 (см. фиг. 1), а через второй управляюший вход 58 НП 19 (см. фиг. 2) - па первые управляющие входы («разрешение приема) умножителей 24 и 25 нелинейного преобразователя. Коммутатор 16 пропускает

5 через первый информационный вход на свой выход код /I, который по шине 85 (см. фиг. 1) через девятый информационный вход 85 НП 19 поступает (см. фиг. 2) на вторые информационные входы умножителей 24, 25 нелинейного преобразователя, которые формируют коды ml, и /1 1/6, соответственно. Сигнал «1 с пятого выхода распределителя (РИ) 51 через элемент ИЛИ 38 блока 20 и седьмой выход 59 блока 20 (см. фиг. 3) проходит по шине 59 (см. фиг. 2)

через третий управляющий вход 59 НП 19 на второй управляющий вход («передача кода) умножителя 25 нелинейного преобразователя, первый управляющий вход («разрещение приема) блока 29 возведения в степень нелинейного преобразователя, на

0 второй информационный вход которого поступает код /1 1/0 с выхода умножителя 25, и первый управляющий вход умножителя 26 нелинейного преобразовате, 1я; сигнал «1 с выхода элемента ИЛИ 38 блока 20 (см. фиг. 3) через элемент ИЛИ 39,

5 восьмой выход 60 блока 20, щину 60 и четвертый управляющий вход 60 НП 19 (см. фиг. 2) поступает на второй управляющий вход («передача кода) умножителя 24 не0

линейного Преобразователя, на выходе которого ноявляетея код т /ь постунающий на второй информационный вход умножителя 26 нелинейного преобразователя. Блок 29 возведения в етепень нелинейного преобразователя формирует код 1/1 1/в|| а умножитель 26 - код т- /I 1/в2.

Сигнал «1 с шестого выхода распределителя 51 через элемент ИЛИ 40 блока 20 и девятый выход 61 блока 20 (см. фиг. 3) поступает по шине 61 через пятый управляющий вход 61 НП 19 (см. фиг. 2) на вторые управляющие входы («передача кода) блока 29 возведения в степень нелинейного преобразователя и умножителя 26 нелинейного преобразователя, па выходах которых появляются коды (/1 1/61) и /и X X /I 1/в2 соответственно, и на первые управляющие входы («разрещение прие.ма) ум})ожителя 27 нелинейного преобразователя и блока 30 возведения в степень нелинейного преобразователя. Умножитель 27 нелинейного гфеобразователя фор.мирует код т /1 1/в|| , а блок 30 возведения в степень - код (т- t - lIQ-i} -.

Сигнал «1 с седьмого выхода РИ 51 блока 20 через элемент ИЛИ 41 и десятый 62 блока 20 (см. фиг. 3) поступает по шине 62 (см. фиг. 2) через шестой управляющий вход 62 НП 19 на вторые управляющие входы («передача кода) умножителя 27 нелинейного преобразователя и блока 30 возведения в степень нелинейного преобразователя первый управляющий вход («разрещение приема) сумматора 31 нелинейного преобразователя, через первый и второй информационные входы которого посту- паюткодыт (t 1/62) и (m - /: 1/69) с выходов умножителя 27 нелинейного преобразователя и блока 30 возведения в степень нелинейного преобразователя соответственно. Сумматор 31 нелинейного преобразователя формирует код A(m,/ i) ш (/iX X +(m- /I - 1/62)

Сигнал «1 с восьмого выхода РИ 51 блока 20 через элемент ИЛИ 42 блока 20 и одиннадцатый выход 63 блока 20(см. фиг. 3) поступает (см. фиг. 2) по шине 63 через седьмой управляющий вход 63 НП 19 на второй управляющий вход («передача кода) сумматора 31 нелинейного преобразователя и первый управляющий вход («разрешение приема) умножителя 28 нелинейного преобразователя, на второй информационный вход которого поступает код (m,t) с выхода сумматора 31 нелинейного преобразователя. Умножитель 28 нелинейного преобразователя формирует код TJ X X A(m , t).

Сигнал «1 с девятого выхода РИ 51 блока 20 через элемент ИЛИ 49 блока 20 и двенадцатый выход 64 блока 20 (см. фиг. 3) поступает (см. фиг. 2) по щипе 64 через восьмой управляющий вход 64 НП 19 на вторые управляющие входы («передача кода) задатчиков 34, Зо не.чинейного преобразователя и умножителя 28 нелинейного преобразователя и первый управляющий вход («разрещение приема) сумматора 32 нелинейного преобразователя, на информационные входы которого поступают коды Т2 (т-1), Т| и т,з A(m,/i) с выходов задатчиков 34, 35 нелинейного преобразователя и умножителя 28 нелинейного преоб,, разователя соответственно. Сумматор 32 нелинейного преобразователя формирует код /Mnpf/n,/i) Т2 (m-l)+Ti+T3+A(m,/i).

Сигнал «1 с десятого выхода РИ 51 блока 20 через элемент ИЛИ 49 блока 20 и тринадцатый выход 65 блока 20 (см.

5 фиг. 3) поступае- (см. фиг. 2) по тине 65 через девятый управляющий вход 65 НП 19 на второй управляющий вход («передача кода) сум.матора 32 нелинейного преобразователя и первый управляющий вход («разрешение приема) делителя 33 нелинейного

0 преобразователя; сигнал «1 с выхода элемента ИЛИ 44 блока 20 через элемент ИЛИ 39 блока 20 и восьмой выход 60 блока 20 (см. фиг. 3) поступает по шине 60 через четвертый управляющий вход 60 ПП 19

5 (см. фиг. 2) на второй управляюпшй вход («передача кода) умножителя 24 нелинейного преобразователя. На первый и второй информационные входы делителя 33 нелинейного преобразователя поступают коды Mpip(m,/i) и m /1 с выходов сумматора 32

0 нелинейного преобразователя и умножителя 24 нелинейно1-о преобразователя соот- ветстенно. Делитель 33 нелинейного преобразователя формирует код S (т, t ) МТ,Р х ,i)/(m, /Г)- /|. Сигнал «1 с одиннадцатого выхода РИ 51 блока 20 через эле5 мент ИЛИ 49 блока 20 и четырнадцатый выход 66 блока 20 (см. фиг. 3) поступает (см. фиг. 2) по Н1ине 66 через десятый управляющий вход 66 НИ 19 на второй управляющий вход («передача кода) делителя 33 нелинейного преобразователя; этот же сигнал «1 непосредственно через пятнадцатый выход 67 блока 20 (с.м. фиг. 3) поступает (см. фиг. 2) по 1пине 67 на первый управляющий вход 67 («разрешение приема) б;1ока 5 памяти. Код Sp(tn,{ с выг хода делителя 53 нелинейного преобразователя через выход НП 19 поступает на информационный вход блока 5 памяти, где запоминается.

Сигнал «1 с двенадцатого выхода РИ 51 б. юка 20 через шестнадцатый выход 68 блод ка 20 (см. фиг. 3) поступает (см. фиг. 1) по шине 68 на второй адресный вход коммутатора 16, на первый адресный вход которого подан сигнал «О с пятого выхода 57 блока 20, а также на второй управляющий вход («передача кода) второго

5 сумматора 10 и первый управляющий вход («разрещение приема) блока 4 памяти на информационный вход которого с выхода сумматора 10 поступает код /). ко0

торый запоминается в этом блоке памяти, а также проходит на второй информационный вход коммутатора 16. Этот же сигнал «1 через элемент ИЛИ 37 блока 20 и шестой выход 58 блока 20 (см. фиг. 3) посту- нает (см. фиг. 1) по шине 58 на управляющий вход коммутатора 16, а через второй управляющий вход НП 19 (см. фиг. 2) - на первые управляющие входы («разрещение приема) умножителей 24 и 25 нелинейного преобразователя. Коммутатор 16 пропускает через второй инфор.мационный вход на свой выход 85 код /2 (см. фиг. 1), который по шине 85 через девятый информационный вход 85 НП 19 (см. фиг. 1), который по шине 85 через девятый информационный вход 85 НП 19 (см. фиг. 2) поступает на информационные входы умножителей 24, 25 нелинейного преобразователя, которые фор.мируют коды m /2 и /2 l/Oi соответственно.

Сигнал «1 с тринадцатого выхода РИ 51 блока 20 через эле.мент ИЛИ 38 блока 20 и седьмой выход 59 блока 20 (см. фиг. 3) проходит по шине 59 (см. фиг. 2) через третий управляющий вход 59 НП 19 на второй управляющий вход («передача кода) умножителя 25 нелинейного преобразователя, первый управляющий вход («разрешение приема) блока 29 возведения в степень нелинейного преобразователя, на второй информационный вход которого поступает код /2 1/в| с выхода умножителя 25 нелинейного преобразователя и первый управляющий вход умножителя 26 нелинейного преобразователя; сигнал «1 с выхода элемента ИЛИ 38 блока 20 (см. фиг. 3) через элемент ИЛИ 39 блока 20, восьмой выход 60 блока 20 (см. фиг. 3), шину 60 и четвертый управляющий вход 60 НП 19 (с,м. фиг. 2) поступает на второй управляющий вход («передача кода) умножителя 24 нелинейного преобразователя, на которого появляется код т (2, идущий на второй информационный вход умножителя 26 нелинейного преобразователя. Блок 29 возведения в степень нелинейного преобразователя формирует код (/2 I/GI) , а умножитель 26 нелинейного преобразователя - код т- 1-2 /в2.

Сигнал «1 с четырнадцатого выхода РИ 51 блока 20 через элемент ИЛИ 40 блока 20 и девятый выход 61 блока 20 (с.м. фиг. 3) поступает по шине 61 через пятый управляющий вход 61 НП 19 (см. фиг. 2) на вторые управляющие входы («передача кода) блока 29 возведения в степень нелинейного преобразователя и умножителя 26 нелинейного преобразователя, на выходах которых появляются коды (/2 1/в|) и m /2 1/02 соответственно, и на первые управляющие входы («разрещение приема) умножителя 27 нелинейного преобразователя и блока 30 возведения в степень нелинейного преобразователя. Умножитель 27 нелинейного Н(1е()б|1азователя формирует код т (1-2 1/Hi) , а блок 30 возведения в степень - код (in /j l/Bi) Сигнал «1 с пятнадцатого выхода РИ 51 5 блока 20 через элемент ИЛИ 41 блока 20 и десятый выход 62 блока 20 (с.м. фнг. 3) поступает по щине 62 (см. фиг. 2) через Н1естой управляющий вход 62 НП 19 на вторые управляющие входы («передача кода)

умножителя 27 нелинейного преобразователя и блока 30 возведения в степень нелинейного преобразователя и первый управляющий вход («разрещение приема) сумматора 31 нелинейного преобразователя, через первый и второй информационные

5 входы которого поступают коды (/2 X X 1/в|) и (т /2 1/в2) с выходов умножителя 27 нелинейного преобразователя и блока 30 возведения в степень нелинейного преобразователя соответственно. Сумматор 31 нелинейного преобра0 зователя формирует код A(m,/i) глХ Х(/2 1/eif +(т - /2- 1/62)

Сигнал «1 с шестнадцатого выхода РИ 51 блока 20 через элемент ИЛИ 42 блока 20 и одиннадцатый выход 63 блока 20

5 (см. фиг. 3) поступает (см. фиг. 2) по шине 63 через седьмой управляющий вход 63 НП 19 на второй управляющий вход («передача кода) сум.матора 31 нелинейного преобразователя и первый управляющий вход («разрешение приема) умножителя

0 28 нелинейного преобразователя, на второй информационный вход которого поступает код Л(т,/2) с выхода сумматора 31 нелинейного преобразователя. Умножитель 28 нелинейного преобразователя формирует код тз Л(т ,/2).

5 Сигнал «1 с семнадцатого вы.хода РИ 51 блока 20 через элемент ИЛИ 43 блока 20 и двенадцатый выход 64 блока 20 (см. фиг. 3) поступает (см. фиг. 2) по шине 64 через восьмой управляющий вход 64 НП 19 на вторые управляющие входы («передача кода) задатчиков 34 и 35 нелинейного преобразователя и умножителя 28 нелинейного преобразователя и первый управляющий вход («разрещение приема) сумматора 32 нелинейного преобразователя, на инфор5 мационные входы которого поступают коды Т2 - (т - 1), Т и тз (т, /2) с выходов задатчиков 34, 35 нелинейного преобразователя и умножителя 28 нелинейного преобразователя соответстенно. Сумматор 32 нелинейного преобразователя формирует код

0 Mi,p(m, /2) Т2(ш-1)+TI-J-T3 (in, /2). Сигнал «1 с восемнадцатого выхода РИ 51 блока 20 через элемент ИЛИ 44 блока 20 и тринадцатый выход 65 блока 20 (см. фиг. 3) поступает (см. фиг. 2) по тине 65 через девятый управляющий вход 65 НП

5 19 на второй управляющий вход («передача кода) сумматора 32 нелинейного преобразователя и первый управляющий вход («разрешение приема) делителя 33 нели0

нейного преобразователя; сигнал «1 с выхода элемента ИЛИ 44 блока 20 через элемент ИЛИ 39 блока 20 и восьмой выход 60 блока 20 (см. фиг. 3). поступает по шине 60 через четвертый управляющий вход 60 НП 19 (см. фиг. 2) на второй управляющий вход («передача кода) умножителя 24 нелинейного преобразователя. На первый и второй информационные входы делителя 33 нелинейного преобразователя поступают коды Л4пр(т,/2) и m - /2 с выходов сумматора 32 нелинейного преобразователя и умножителя 24 нелинейного преобразователя со- ответстенно. Делитель 33 нелинейного преобразователя формирует код 5,,(ш1/|) Мир X X (тЛч I (т /2). Сигнал «1 с девятнадцатого выхода .РИ 51 блока 20 через элемент ИЛИ 46 блока 20 и семнадцатый выход 69 блока 20 (см. фиг. 3) поступает (см. фиг. 1) по шине 69 па второй управляющий вход («передача кода) блока 4 памяти и первый управляющий вход («разрешение приема) вычитателя 7; этот же сигнал «1 через элемент ИЛИ 47 блока 20 и восемнадцатый выход 70 блока 20 (см. фиг. 3) поступает (см. фиг. 1) по шине 70 на второй управляющий вход («передача кода) блока 3 памяти. На первый и второй информационные входы вычитателя 7 поступают коды /i и /2 с выходов блоков 3 и 4 па.мяти соответственно. Вычи- татель 7 формирует абсолютную величину (без знака) кода Д/ |Л-/2 .

Сигнал «I с двадцатого выхода РИ 51 блока 20 через девятнадцатый выход 71 блока 20 (см. фиг. 3) поступает (см. фиг. 1) по шине 71 на второй управляющий вход («передача кода) вычитателя 7 и первый управляющий вход («разрешение приема) делителя 11; этот же сигнал «1 через элемент ИЛИ 47 блока 20 и восемнадцатый выход 70 элемента 20 (см. фиг. 3) поступает (см. фиг. 1) по шине 70 на второй управляюший вход («передача кода) блока 3 памяти. На первый и второй информационные входы делителя 11 поступают коды / и /1 с выходов вычитателя 7 и блока 3 памяти соответственно. Делитель 1 1 фор.ми- рует код 6t Л///1.

Сигнал «1 с двадцать первого выхода РИ 51 блока 20 через двадцатый выход 72 блока 20 (см. фиг. 3) поступает (см. фиг. 1) по шине 72 на вторые управляющие входы («передача кода) делителя 11 и задатчи- ка 21 и первый управляющий вход («разрешение приема) блока 12 сравнения, на информационные входы которого поступают коды 6i и с выходов делителя 11 и задатчика 21. Блок 12 сравнения осуществляет сравнение кодов б( и е.

Сигнал «1 с двадцать второго выхода РИ 51 блока 20 через двадцать первый выход 73 блока 20 (см. фиг. 3) поступает (см. фиг. 1) по тине 73 на второй управляющий вход («передача кода) блока 12

сравнения, который формирует на своих выходах в зависимости от результата сравнения следующие сигналы: у 1, i/2 О, если 6. ; s; t/i О, , если f е, где

У, У2 - сигналы, формируемые на первом и втором выходах блока 12 сравнения. Рассмотрим сначала случай, когда б. 8, т. е. У I, у2 О (см. фиг. 4ж, 4з). Сигнал «1 с первого выхода 74 блока 12

„ сравнения (см. фиг. 1) по шине 74 через второй вход 74 блока 20 (см. фиг. 3), элемент ИЛИ 45 блока 20, четырнадцатый выход 66 блока 20 (см. фиг. 3) и далее по щине 66 через десятый управляющий вход 66 НН 19 (см. фиг. 2) поступает на второй управляющи вход («передача кода) делителя 33 нелинейного преобразователя; этот же сигнал «Ь с второго входа 74 блока 20 (см. фиг. 3) через элемент ИЛИ . 48 блока 20 и двадцать второй выход 75 блока 20 (см. фиг. 3) проходит (см. фиг. 2) по

шине 75 на второй управляющий вход («передача кода) блока 5 памяти и первый управляющий вход («разрешение приема) блока 13 сравнения. На информационные входы блока 13 сравнения

5 поступают коды S,,(my/i) и S,,(m)/2) с выхода блока 5 памяти непосредственно, а с выхода делителя 33 нелинейного преобразователя - через выход НН 19. Блок 13 сравнения осуществляет сравнение кодов 8,,(пц1 и Sp(mjt:).

0 Сигнал «1 с двадцать третьего выхода РИ 51 блока 20 (см. фиг. 4и) через двадцать третий выход 76 блока 20 (см. фиг. 3) поступает (см. фиг. 2) по пине 76 на второй управляющий вход («передача кода) блока 13 сравнения, который фор5 мирует на своих выходах в зависимости от результата сравнения следующие сигна.чы: Z| 1, Z2 О, если 5р(,„,/|) 5p(m,/ii; Z, 0, Z2 1, если Sp(m,f-i) S,,(m,i-2. где Z, Z-2 - сигналы, формируемые на первом и втором выходах блока 13 сравнения. Если S,,(in,t) : Sp(m,l2), т. е. Z| 1, а Z2 О, (см. фиг. 4к, 4л), то сигнал «1 с первого выхода 77 блока 13 сравнения (см. фиг. 2) по шине 77 через третий вход 77 блока 20 (см. фиг. 3), элемент ИЛИ 47

5 блока 20 и восемнадцатый выход 70 блока 20 поступает (см. фиг. 1) по шине 70 на второй управляющий вход («передача кода) блока 3 памяти; этот же сигнал «Ь с третьего входа 77 блока 20 через элемент ИЛИ 49 блока 20 управления и двадцать

0 четвертый выход 78 блока 20 (см. фиг. 3) поступает (см. фиг. 1) по шине 78 на первый управляющий вход («разрешение приема) блока 1 памяти и управляющий вход коммутатора 18.

Сигнал «1 с первого выхода 77 бло5 ка 13 сравнения (см. фиг. 2) по шине 77 поступает также (см. фиг. 1) на второй адресный вход коммутатора 18, на первый адресный вход которого подан сигнал «О с

второго управляющего входа 83 устройства. С выхода блока 3 памяти код t через второй информационный вход коммутатора 18 и его выход поступает на информационный вход блока 1 памяти, в котором стирается хранившийся там код А и записывается кОд /1, т. е. в качестве новой левой границы интервала поиска минимума функции принимается значение t. Если Sp( f Sp(m,ti}, т. е. Zi О, а Z2 1 (см. фиг. 4к, 4л), то сигнал «1 с второго выхода 79 блока 13 сравнения (см. фиг. 2) через четвертый вход 79 блока 20 (см. фиг. 3), элемент ИЛИ 46 блока 20 и семнадцатый выход 69 блока 20 (см. фиг. 3) поступает (см. фиг. 1) по шине 69 на второй управляющий вход («передача кода) блока 4 памяти; этот же сигнал «1 с четвертого входа 79 блока 20 через элемент ИЛИ 50 блока 20 и двадцать пятый выход ВО блока 20 (см. фиг. 3) поступает (см. фиг. 1) по шине 80 на первый управляющий вход («разрешение приема) блока 2 памяти и управляющий вход коммутатора 17.

Сигнал «1 с второго выхода 79 блока 13 сравнения (см. фиг. 2) по шине 79 поступает также (см. фиг. 1) на второй адресный вход коммутатора 17, на первый адресный вход которого подан сигнал «О с второго управляющего входа 83 устройства. С выхода блока 4 памяти код /2 через второй информационный вход второго коммутатора 17 и его выход поступает на информационный вход блока 2 памяти, в котором стирается хранившийся там код В и записывается код /2, т. е. в качестве новой правой границы интервала поиска минимума функдии Sp{m,i) принимается значение /2. Дальнейшая работа устройства происходит аналогично описанному выше, т. е. вновь на первом, втором и т. д. выходах РИ 51 блока управления формируются сигналы «1, которые управляют работой остальных блоков устройства.

Рассмотрим теперь случай, когда 6. е, т. е. 1/1 0, а (см. фиг. 4ж, 4з). Сигнал «1 с второго выхода блока 12 сравнения (см. фиг. 1) поступает на управляющий вход («разрешение приема) блока 8 регистрации, а по шине 81 (см. фиг. 3) через пятый вход блока 20, элемент ИЛИ 48 &j,OKa 20 и двадцать второй выход 75 блока 20 поступает по шине 75 (см. фиг. 2) на второй управляющий вход («передача кода) блока 5 памяти; этот же сигнал «1 с пятого входа 81 блока 20 (см. фит. 3) через элемент ИЛИ 47 блока 20 и восемнадцатый выход 70 блока 20 поступает (см. фиг. 1) по шине 70 на второй управляющий вход («передача кода) блока 3 памяти. С выхода блока 5 па.мяти (см. фиг. 2) по шине 86 и выхода блока 3 памяти (см. фиг. 1) коды 5p(m,/i) и t соответственно проходят через преобразователи двоичного кода в десятичный

10

5

0

5

0

5

0

5

0

5

(не показанные на схеме устройства) и поступают в виде десятичных кодов S,,(m, /1) и /1 на информационные входы блока 8 регистрации, где регистрируются в качестве оптимальных значений.

По этому же сигналу «1, идущему с пятого входа 81 блока 20 на второй управляющий вход генератора 52 блока 20 (см. фиг. 4м), прекращается генерация тактовых импульсов.

Оптимизация периодичности проведения текущих ремонтов для следующего изделия осуществляется аналогично.

Формула изобретения

1. Устройство для определения оптимального периода ремонта изделия, содержащее первый задатчик кода, выход которого соединен с первым входом первого коммутатора, нелинейный преобразователь, выход которого подключен к первому входу первого блока сравнения, первый выход которого соединен с вторым входом первого коммутатора, первый сумматор, делитель и блок регистрации, отличающееся тем, что, с целью повыщения точности устройства, в него введены задатчики кода, блоки памяти, коммутаторы, вычитатели, умножители, сумматоры, блоки сравнения и блок синхронизации, первый вход нелинейного преобразователя является первым входом устройства, объединенные первые входы блока синхронизации, второго коммутатора, входы первого и второго задатчиков кода и третий вход первого коммутатора являются вторым входом устройства, второй вход блока синхронизации является третьим входом устройства, выход второго задатчика кода соединен с вторым входом второго коммутатора, выход которого подключен к входу первого блока памяти, выход которого соединен с первыми входами первого и второго сумматоров и первого вычитателя, выход которого подключен к первым входам первого и второго умножителей, выходы которых подключены соответстенно к вторым входам первого и второго сумматоров, выходы которых соединены соответственно с первым и вторым входами третьего коммутатора, выход которого подключен к второму входу нелинейного преобразователя, выход первого коммутатора соединен с входом второго блока памяти, выход которого подключен к второму входу первого вычитателя, выходы, первого и второго сумматоров соединены соответственно с входами третьего и четвертого блоков памяти, выход последнего из которых подключен к четвертому входу первого коммутатора и к первому входу второго вычитателя, выход которого соединен с первым входом делителя, выход которого подключен к первому входу второго блока сравнения, первый выход которого соединен с первым входом блока регистрации и с грстьим входом олока синхронизации, второй выход второго блока сравнения подключен к четвертому входу блока синхронизации, выход третьего блока памяти соединен с вторыми входами второго вычитателя, делителя, блока регистрации и с третьим входом второго коммутатора, выход нелинейного преобразователя подключен к входу пятого блока памяти, выход которого соединен с вторым входом первого блока сравнения и с третьим входом блока регистрации, второй выход первого блока сравнения подключен к четвертому входу второго коммутатора, выход третьего задатчика кода соединен с вторым входом второго блока сравнения, цервый и второй выходы первого блока сравнения подключены соответственно к пятому и шестому входам блока синхронизации, выходы которого соединены с управляющими входами всех узлов устройства кроме первого и второго задатчиков кода.

2. Устройство по п. 1, отличающееся тем, что нелинейный преобразователь содержит умножители, блоки возведения в степень, сумматоры, делитель, задатчики кода, объединенные первые входы первого и второго задатчиков кода, с первого по пятый умноОп 5л,20()

К 5л

{(/Ш 50)

рп

/ie

ILfS от tin. 20

I /g Г (узел 37

i«

к Ул. 19 (узлы

0

жителей и первого, второго блоков возве- п в степень являются первым входом шнейного преобразователя, объединенные Sicpbie входы второго и четвертого умножителей являются вторым входом нелинейного преобразователя, выход четвертого умножителя соединен с вторым входом второго блока возведения в степень, выход которого подключен к второму входу первого умножителя, выход которого соединен с первым входом первого сумматора, выход которого подключен к второму входу третьего умножителя, выход которого соединен с первым входом второго сумматора, выход которого подключен к первому входу делителя, выход которого является выходом нелинейного преобразователя, выход второго умножителя подключен к второму входу делителя и второму входу пятого умножителя, выход которого соединен с вторым входом первого блока возведения в степень, выход которого подключен к второму входу первого сумматора, выходы первого и второго задатчиков кода соединены соответственно с вторым и третьим входами второго сумматора, управляющие входы всех узлов нелинейного преобразователя являются его управляющими входами.

0

(Jill UII..IJ

YJ/JMW;

-(ЛтВл.13

(От5л.20

fCi/3e t7l

От5л-5

f8,52)

. го V

j WW .0т5п.20 (уш

51)

и,II 5л.20 (узел51)

.2D (yзsл5)

фиг.1

(.оставитель Н. Ваганова Ч.ро I И. ВересКоррект ;г Л. Тяс

();unicii 4

X1CF по делам ii3o6peieiin i ;: Ч;р I aviiiCKaii иаб., д. 4;Г-.

; .Uipl in iu . г. Ужгород, y.i. |1|ЧЧ ;11

| название | год | авторы | номер документа |

|---|---|---|---|

| ИНТЕРПОЛЯТОР | 1998 |

|

RU2132568C1 |

| ИНТЕРПОЛЯТОР | 1997 |

|

RU2127903C1 |

| СПЛАЙН-ИНТЕРПОЛЯТОР | 1998 |

|

RU2143132C1 |

| СПЛАЙН-ИНТЕРПОЛЯТОР | 1998 |

|

RU2143131C1 |

| Контроллер измерительного преобразователя | 1988 |

|

SU1541632A1 |

| Устройство для считывания графической информации | 1987 |

|

SU1564661A1 |

| Контроллер измерительного преобразователя | 1987 |

|

SU1462357A1 |

| ИНТЕРПОЛЯТОР | 1997 |

|

RU2127902C1 |

| СПЛАЙН-ИНТЕРПОЛЯТОР | 1997 |

|

RU2127901C1 |

| ИНТЕРПОЛЯТОР | 1997 |

|

RU2120137C1 |

И: .;;Гп1о- с; ис относите. к области те.х- И Сск 1/ :-:;; ч р11стики и может быть исполь- n(.jiid;i i li )1л ;1сс:1едованиях и технике. где требуется определять оптимальные периоды между текущими ремонтами изделий, на которых проводятся плановые ремонты двух видов - текущие и капитальные. Устройство обеспечивает высокую точность нахождения оптимального периода ремонта. Устройство содержит блоки памяти, вычита- тели, блок регистрации, сумматоры, делитель, блоки сравнения, умножители, ксп .му- таторы, нелинейный преобр;; орат .: . плок синхронизации и задатчики код::. Гли-дспно Hoiii ix элементов и их свя:5 -; к ччмс uiiun учет в ппоцесое оптимизашп; .1ву imion ремонтов - текущих и капита/пиых. Кроме того, вычислительные операции производятся над кодовыми сигналами. Их высокая разрядность предопределяет дости.жение требуемой точности конечных рез мьтатов. I з.п. ф-лы, 4 ил. со ел со л. со ел со

Авторы

Даты

1987-05-30—Публикация

1986-01-28—Подача