11

Изобретение относится к вычислительной технике и Может быть использовано в системах сопряжения между различными объектами и ЭВМ.

Целью изобретения является повышение коэффициента использования оборудования.

Изобретение обеспечивает оптимизацию вьщеления памяти программам операционной системы при загрузке обрабатывающей программы с диска в ОЗУ по запросу пользователя путем минимизации объема области ОЗУ, выделяемой программам операционной системы, в соответствии с пот ребите- лями конкретной, загружаемой в ОЗУ обрабатывающей программы.

.Увеличение объема памяти, доступной для хранения кода обрабатывающей программы и обрабатываемых ею данных, позволяет производить обработку данных в ОЗУ и обмен с внешней памятью большими порциями. Это позволяет уменьшить число сеансов обмена и, следовательно, потери времени на установки позиционера диска и подвод требуемых участков (секторов) диска к головке, не говоря уже о лишних обращениях к программам операционной системы. Таким образом, увеличение объема доступной обраба- тывающим программам памяти в целом дает возможность существенно повы- сить эффективность работы микроЭВМ.

Принцип решения задачи оптимизации выделения памяти, реализованный с помощью предлагаемого устройства, заключается в следующем. К моменту загрузки обрабатывающей программы в оперативной памяти размещены не все подпрограммы операционной системы (драйверы), непосредственно осуществляющие управление обменом информацией с внешними устройствами, а только драйверы диска и консоли, поскольку эти устройства необходим1з1 для обеспечения работы любой программы (с консоли вв одится запрос на запуск программы, а с диска производится считывание ее кода в ОЗУ). Остальные драйверы содержатся во внеш- ней памяти в специальных файлах - системах поддержки. Каждая система поддержки представляет собой комплект драйверов, обеспечивающий решение некоторого класса задач, использующих соответствующие устройства. В маркерах файлов обрабатывающих программ, содержащихся в оглавлении

59862

диска, наряду с информацией о местоположении кода программы на диске, длиной кода и начальным адресом загрузки программы в ОЗУ находится ин5 формация об используемых данной программой внешних устройствах. Эта информация представляет собой последовательность битов, каждый из которых индицирует использование некото10 рого устройства. Значение 1 бита определяет, что при работе программу потребуется обмен с соответствующим устройством, а. О - что обмен с данным; устройством не потребуется.

f5 В процессе загрузки обрабатывающей программы эта информация считывается из внешней памяти и обрабатьшается предлагаемым устройством наряду с остальными данными, заключенньми в

20 маркере файла обрабатывающей программы, в результате чего устройство производит загрузку в ОЗУ не только кода программы из этого файла, но и минимальной по объему системы держки, включающей драйверы всех используемых при работе данной программы устройств, что обеспечивает наличие в ОЗУ после загрузки программы лишь минимального необходимого

30 объема управляющих программ операционной системы.

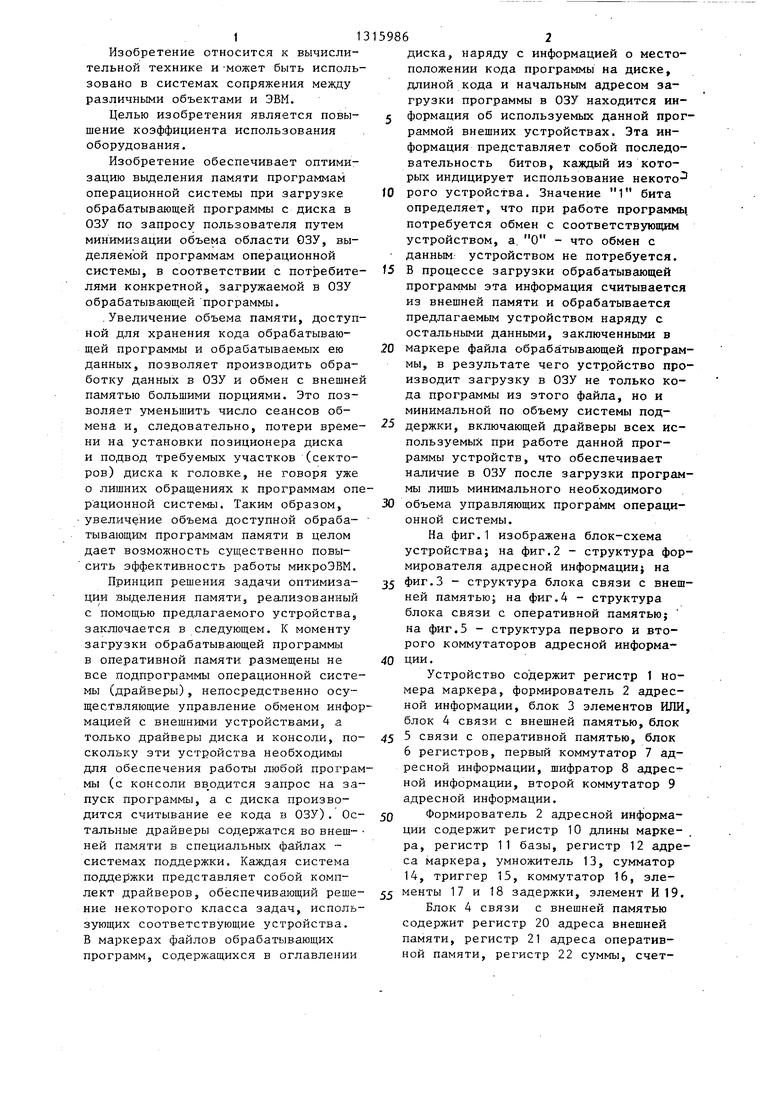

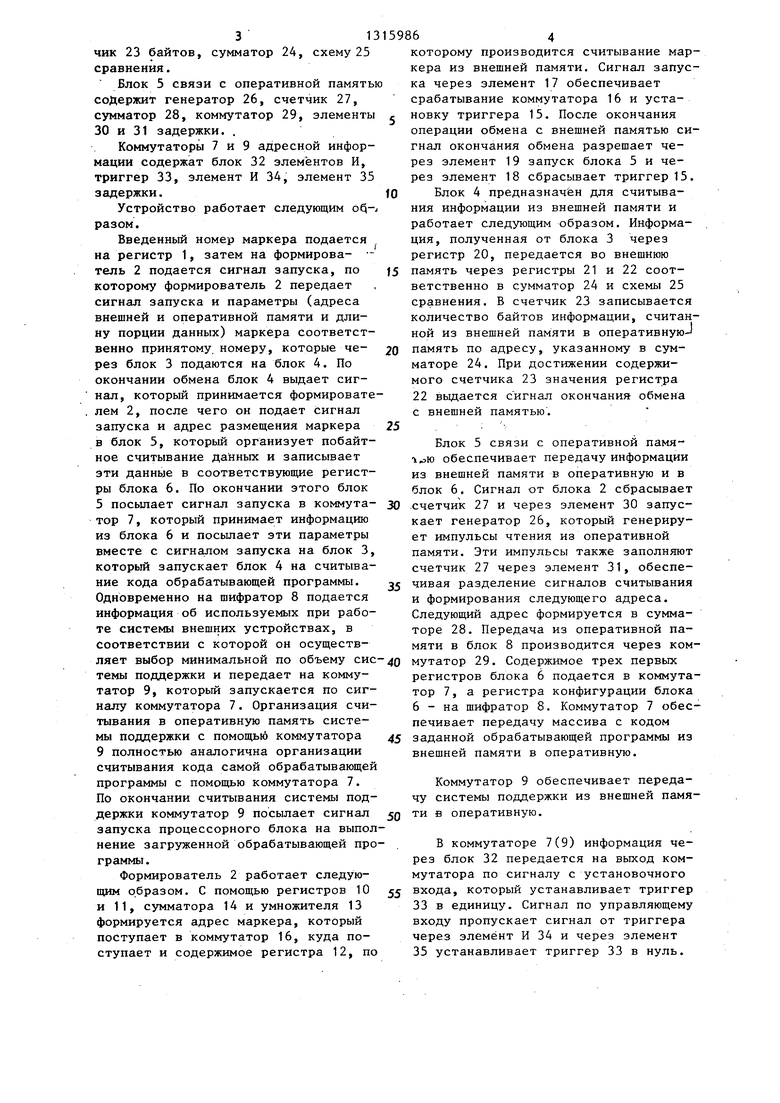

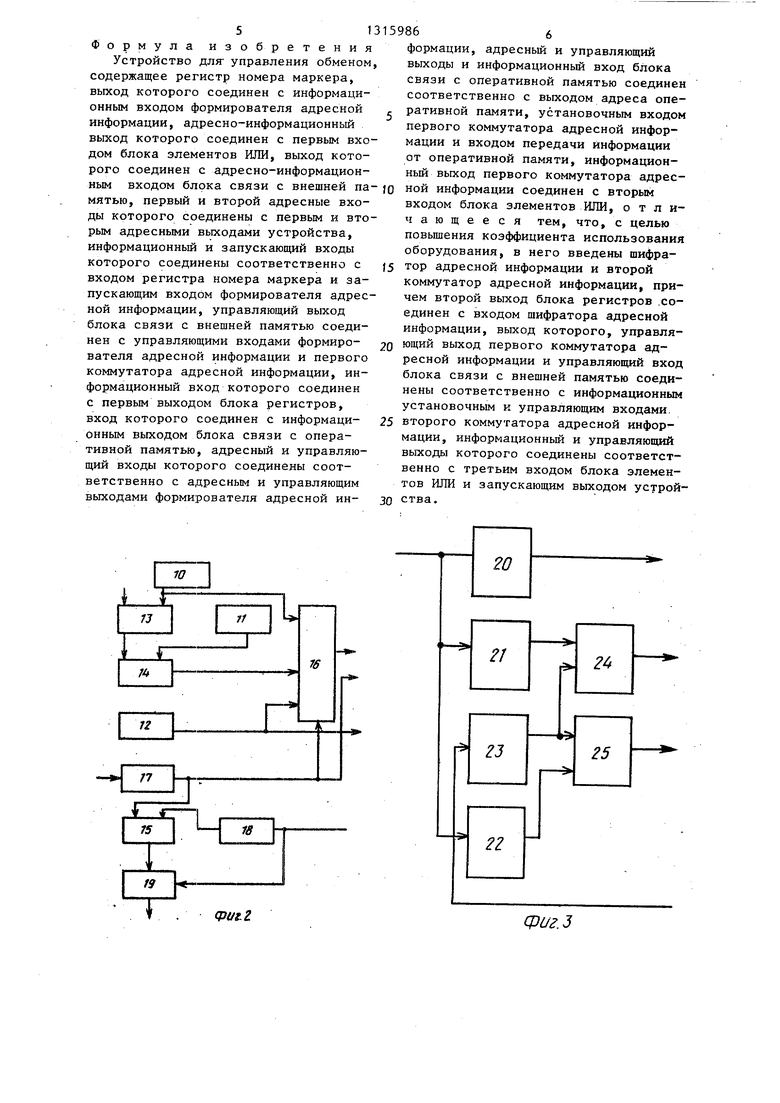

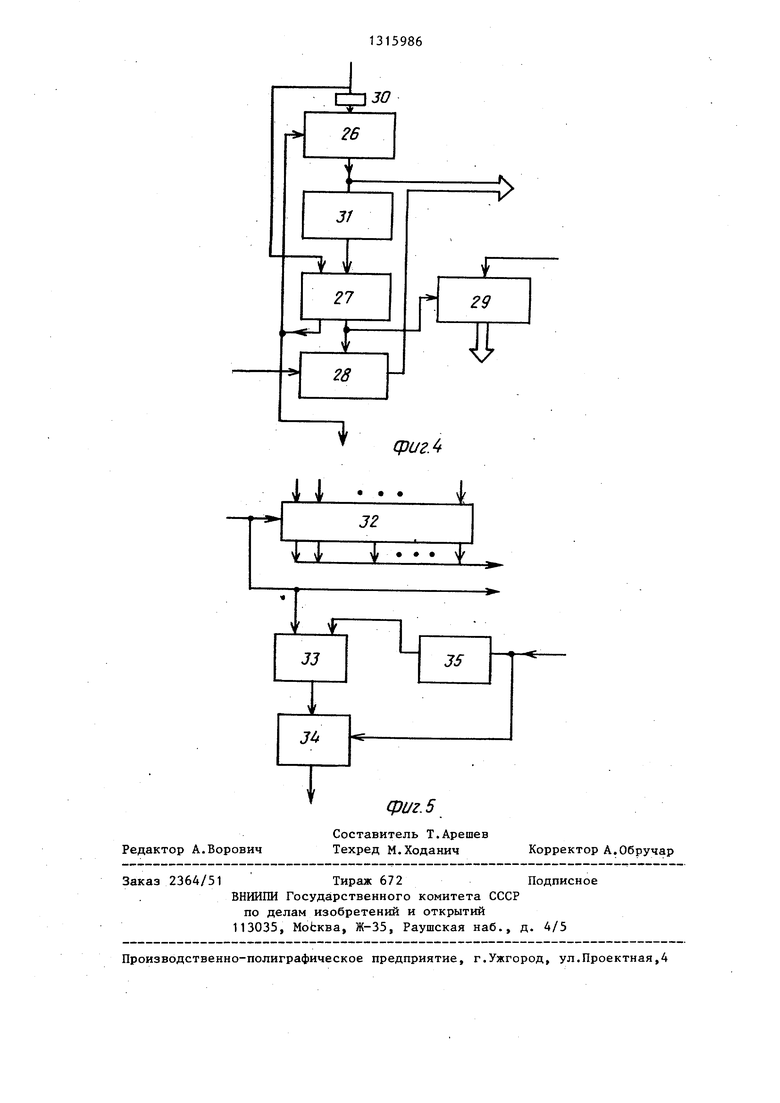

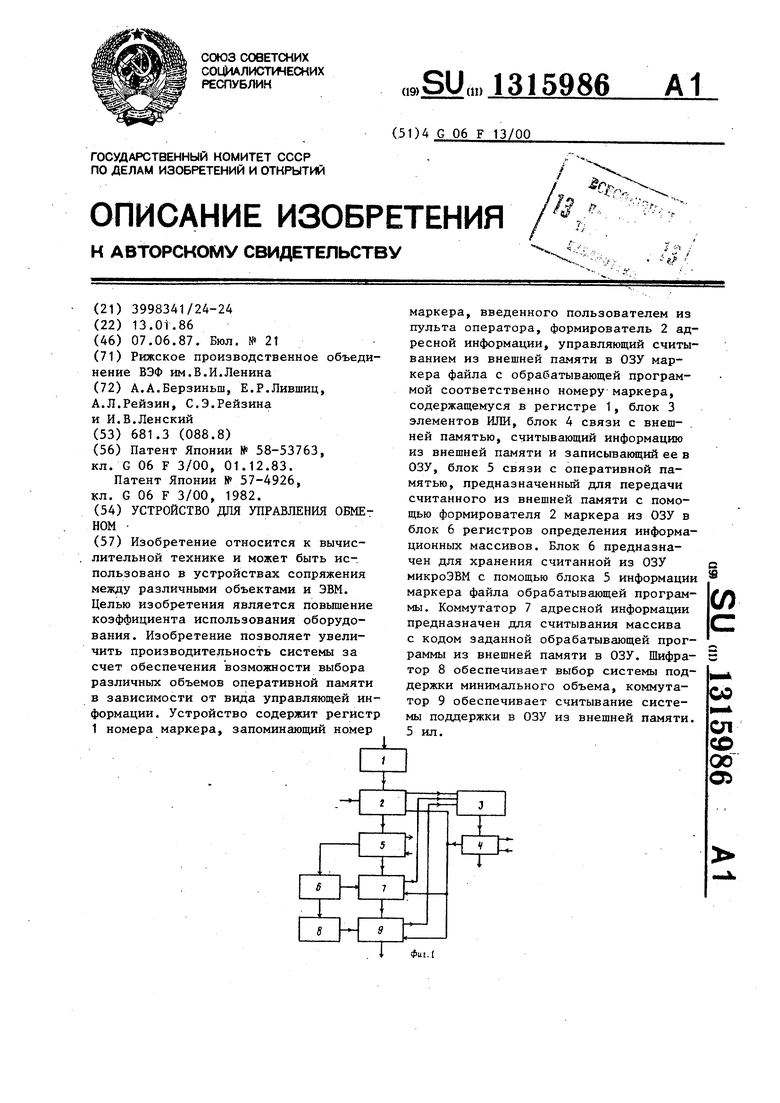

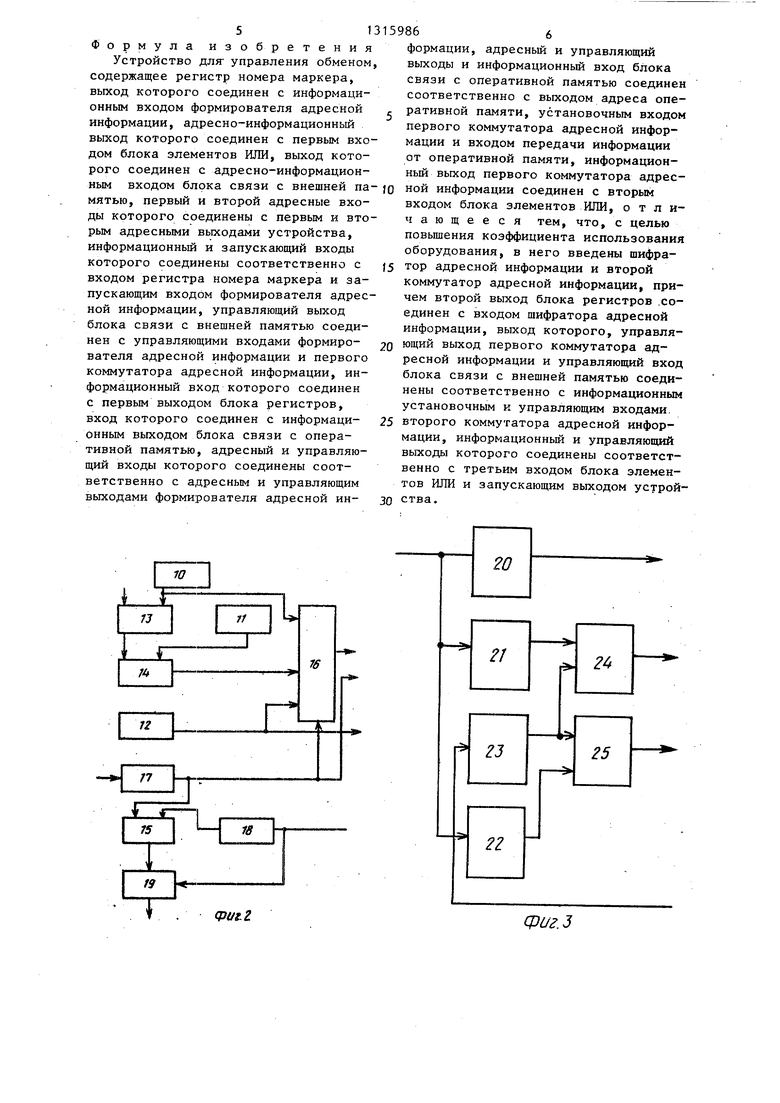

На фиг.1 изображена блок-схема устройства; на фиг.2 - структура формирователя адресной информации; на

:}5 фиг.З - структура блока связи с внешней памятьюJ на фиг.4 - структура блока связи с оперативной памятью; на фиг.З - структура первого и второго коммутаторов адресной информа40 ции.

Устройство содержит регистр 1 номера маркера, формирователь 2 адресной информации, блок 3 элементов ИЛИ, блок 4 связи с внешней памятью, блок

45 5 связи с оперативной памятью, блок 6 регистров, первый коммутатор 7 адресной информации, шифратор 8 адресной информации, второй коммутатор 9 адресной информации.

50 Формирователь 2 адресной информации содержит регистр 10 длины маркера, регистр 11 базы, регистр 12 адреса маркера, умножитель 13, сумматор 14, триггер 15, коммутатор 16, эле55 менты 17 и 18 задержки, элемент И 19.

Блок 4 связи с внешней памятью содержит регистр 20 адреса внешней памяти, регистр 21 адреса оперативной памяти, регистр 22 суммы, счетчик 23 байтов, сумматор 24, схему 25 сравнения.

Блок 5 связи с оперативной память содержит генератор 26, счетчик 27, сумматор 28, коммутатор 29, элементы 30 и 31 задержки. .

Коммутаторы 7 и 9 адресной информации содержат блок 32 элементов И, триггер 33, элемент И 34, элемент 35 задержки.

Устройство работает следующим oQразом.

Введенный номер маркера подается на регистр 1, затем на формирова- - тель 2 подается сигнал запуска, по которому формирователь 2 передает сигнал запуска и параметры (адреса внешней и оперативной памяти и длину порции данных) маркера соответственно принятому, номеру, которые че- рез блок 3 подаются на блок 4. По окончании обмена блок 4 выдает сигнал, который принимается формирователем 2, после чего он подает сигнал запуска и адрес размещения маркера в блок 5, который организует побайтное считывание данных и записывает эти данные в соответствующие регистры блока 6. По окончании этого блок 5 посылает сигнал запуска в коммута- тор 7, который принимает информацию из блока 6 и посьшает эти параметры вместе с сигналом запуска на блок 3, который запускает блок 4 на считывание кода обрабатывающей программы. Одновременно на шифратор 8 подается информация об используемых при работе системы внешних устройствах, в соответствии с которой он осуществляет выбор минимальной по объему сие темы поддержки и передает на коммутатор 9, который запускается по сигналу коммутатора 7. Организация считывания в оперативную память системы поддержки с помощью коммутатора 9 полностью аналогична организации считывания кода самой обрабатывающей программы с помощью коммутатора 7. По окончании считывания системы поддержки коммутатор 9 посылает сигнал запуска процессорного блока на выполнение загруженной обрабатывающей программы.

Формирователь 2 работает следующим образом. С помощью регистров 10 и 11, сумматора 14 и умножителя 13 формируется адрес маркера, который поступает в коммутатор 16, куда поступает и содержимое регистра 12, по

которому производится считывание маркера из внешней памяти. Сигнал запуска через элемент 17 обеспечивает срабатывание коммутатора 16 и установку триггера 15. После окончания операции обмена с внешней памятью сигнал окончания обмена разрешает через элемент 19 запуск блока 5 и через элемент 18 сбрасывает триггер 15.

Блок 4 предназначен для считывания информации из внешней памяти и работает следующим образом. Информация, полученная от блока 3 через регистр 20, передается во внешнюю память через регистры 21 и 22 соответственно в сумматор 24 и схемы 25 сравнения. В счетчик 23 записывается количество байтов информации, считанной из внешней памяти в oпepaтивнyюJ память по адресу, указанному в сумматоре 24. При достижении содержимого счетчика 23 значения регистра 22 выдается с игнал окончания обмена с внешней памятью.

Блок 5 связи с оперативной памя- обеспечивает передачу информации из внешней памяти в оперативную и в блок 6. Сигнал от блока 2 сбрасывает .счетчик 27 и через элемент 30 запускает генератор 26, который генерирует импульсы чтения из оперативной памяти. Эти импульсы также заполняют счетчик 27 через элемент 31, обеспечивая разделение сигналов считывания и формирования следующего адреса. Следующий адрес формируется в сумматоре 28. Передача из оперативной памяти в блок 8 производится через коммутатор 29. Содержимое трех первых регистров блока 6 подается в коммутатор 7, а регистра конфигурации блока 6 - на шифратор 8. Коммутатор 7 обеспечивает передачу массива с кодом заданной обрабатывающей программы из внешней памяти в оперативную.

Коммутатор 9 обеспечивает передачу системы поддержки из внешней памяти в оперативную.

В коммутаторе 7(9) информация через блок 32 передается на выход коммутатора по сигналу с установочного входа, который устанавливает триггер 33 в единицу. Сигнал по управляющему входу пропускает сигнал от триггера через элемент И 34 и через элемент 35 устанавливает триггер 33 в нуль.

51

Формула изобретения Устройство для управления обменом содержащее регистр номера маркера, выход которого соединен с информационным входом формирователя адресной информации, адресно-информационный вькод которого соединен с первым вхо дом блока элементов ИЛИ, выход которого соединен с адресно-информационным входом блока связи с внешней па мятыо, первый и второй адресные входы которого соединены с первым и вто рьм адресными выходами устройства, информационный и запускающий входы которого соединены соответственно с входом регистра номера маркера и запускающим входом формирователя адрес ной информации, управляющий выход блока связи с внешней памятью соединен с управляющими входами формирователя адресной информации и первого коммутатора адресной информации, информационный вход которого соединен с первым выходом блока регистров, вход которого соединен с информационным выходом блока связи с оперативной памятью, адресный и управляющий входы которого соединены соответственно с адресным и управляющим выходами формирователя адресной ин159866

формации, адресный и управляющий

выходы и информационный вход блока связи с оперативной памятью соединен соответственно с выходом адреса опе- ративной памяти, установочным входом первого коммутатора адресной информации и входом передачи информации от оперативной памяти, информационный выход первого коммутатора адрес10 ной информации соединен с вторым

входом блока элементов ИЛИ, отличающееся тем, что, с целью повьшения коэффициента использования оборудования, в него введены шифра- )5 тор адресной информации и второй коммутатор адресной информации, причем второй выход блока регистров .соединен с входом шифратора адресной информации, выход которого, управля- 20 ющий выход первого коммутатора адресной информации и управляющий вход блока связи с внешней памятью соединены соответственно с информационным установочным и управляющим входами. 25 второго коммутатора адресной информации, информационный и управляющий выходы которого соединены соответственно с третьим входом блока элементов ИЛИ и запускающим выходом устрой- 30 ства.

W

фиг.З

(ригА

фиг. 5

Редактор А.Ворович

Составитель Т.Арешев Техред М.Ходанич

Заказ 2364/51 Тираж 672Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, МоЬква, 1-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г.Ужгород, ул.Проектная,4

Корректор А.Обручар

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ ЦИФРОВОЙ МАГНИТНОЙ ЗАПИСИ ИНФОРМАЦИИ НА ВИДЕОМАГНИТОФОНЕ | 1993 |

|

RU2042218C1 |

| Специализированный процессор | 1990 |

|

SU1705834A1 |

| Устройство для обмена информацией между ЭВМ и терминалом | 1984 |

|

SU1416993A1 |

| Устройство для управления обменом информацией накопителя на магнитной ленте с электронно-вычислительной машиной | 1983 |

|

SU1128245A1 |

| Вычислительная система | 1977 |

|

SU692400A1 |

| Управляющая векторная вычислительная система | 1982 |

|

SU1120340A1 |

| Устройство для анализа вызванных потенциалов головного мозга | 1990 |

|

SU1804787A1 |

| Устройство для сопряжения двух магистралей | 1988 |

|

SU1509915A2 |

| АВТОМАТИЗИРОВАННАЯ СИСТЕМА КОНТРОЛЯ ПАРАМЕТРОВ ЭЛЕКТРОННЫХ СХЕМ | 1991 |

|

RU2106677C1 |

| Микропрограммный процессор | 1982 |

|

SU1070557A1 |

Изобретение относится к вычислительной технике и может быть использовано в устройствах сопряжения между различными объектами и ЭВМ. Целью изобретения является повьпиение коэффициента использования оборудования. Изобретение позволяет увеличить производительность системы за счет обеспечения возможности выбора различных объемов оперативной памяти в зависимости от вида управляющей информации. Устройство содержит регистр 1 номера маркера, запоминающий номер маркера, введенного пользователем из пульта оператора, формирователь 2 адресной информации, управляющий считыванием из внешней памяти в ОЗУ маркера файла с обрабатывающей программой соответственно номеру маркера, содержащемуся в регистре 1, блок 3 элементов ИЛИ, блок 4 связи с внешней памятью, считывающий информацию из внешней памяти и записывакнций ее в ОЗУ, блок 5 связи с оперативной памятью, предназначенный для передачи считанного из внешней памяти с помощью формирователя 2 маркера из ОЗУ в блок 6 регистров определения информационных массивов. Блок 6 предназначен для хранения считанной из ОЗУ микроэвм с помощью блока 5 информации маркера файла обрабатывающей программы. Коммутатор 7 адресной информации предназначен для считывания массива с кодом заданной обрабатывающей программы из внешней памяти в ОЗУ. Шифратор 8 обеспечивает выбор системы поддержки минимального объема, коммутатор 9 обеспечивает считывание системы поддержки в ОЗУ из внешней памяти. 5 ил. i (/) со СП ;о (ХГ а Фи.

| Способ окисления боковых цепей ароматических углеводородов и их производных в кислоты и альдегиды | 1921 |

|

SU58A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Способ получения на волокне оливково-зеленой окраски путем образования никелевого лака азокрасителя | 1920 |

|

SU57A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-06-07—Публикация

1986-01-13—Подача