Изобретение относится к вычислительной технике и может быть использовано для построения специализированных вычислительных систем реального масштаба времени.

Цель изобретения - повышение быстродействия и расширение функциональных возможностей путем реализации функционирования в составе вычислительной сети.

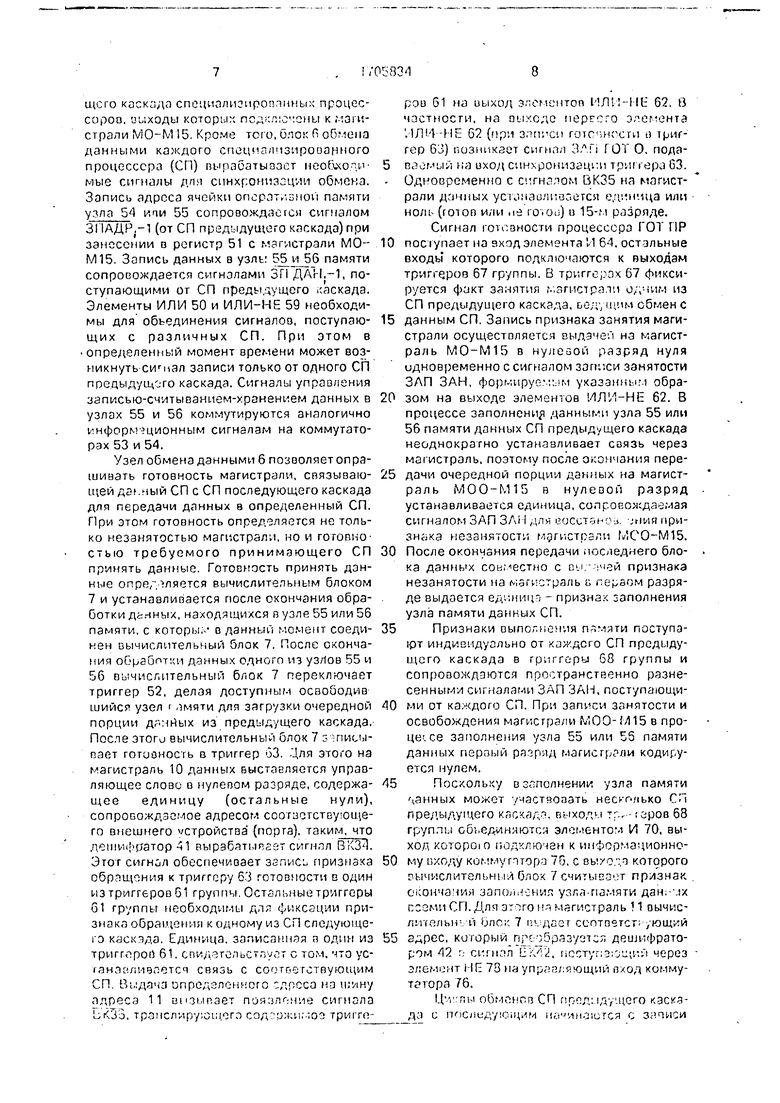

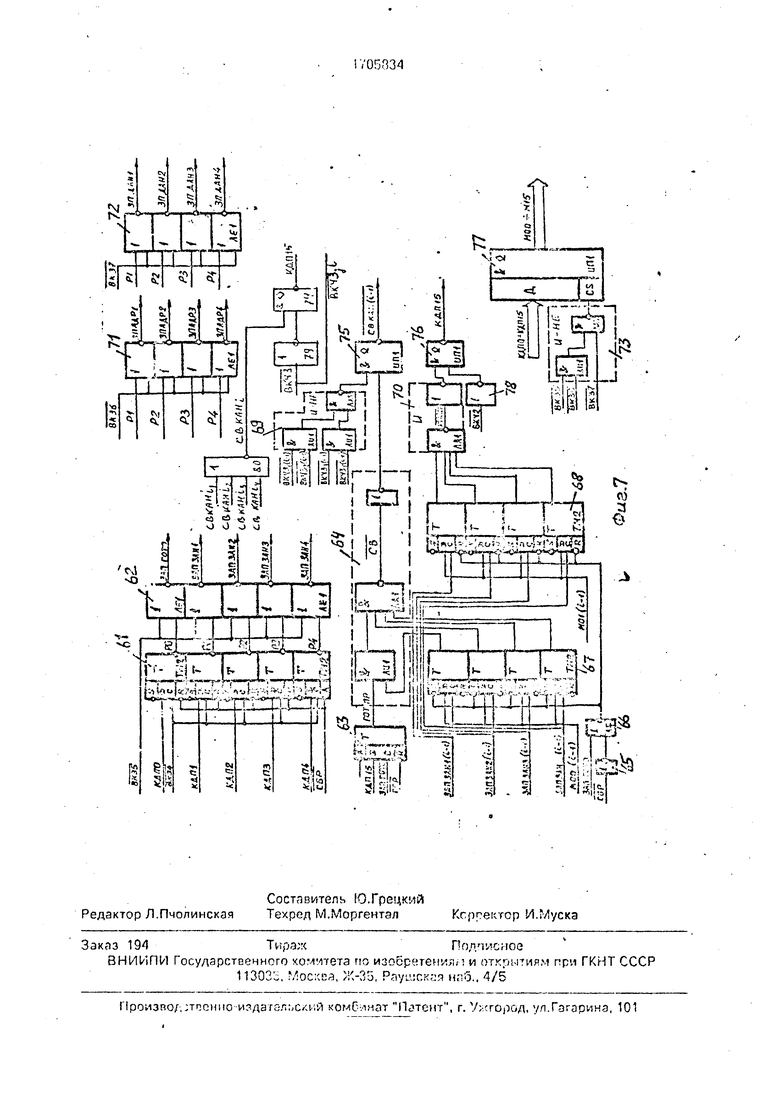

На фиг.1 представлена блок-схема специализированного процессора для случая М

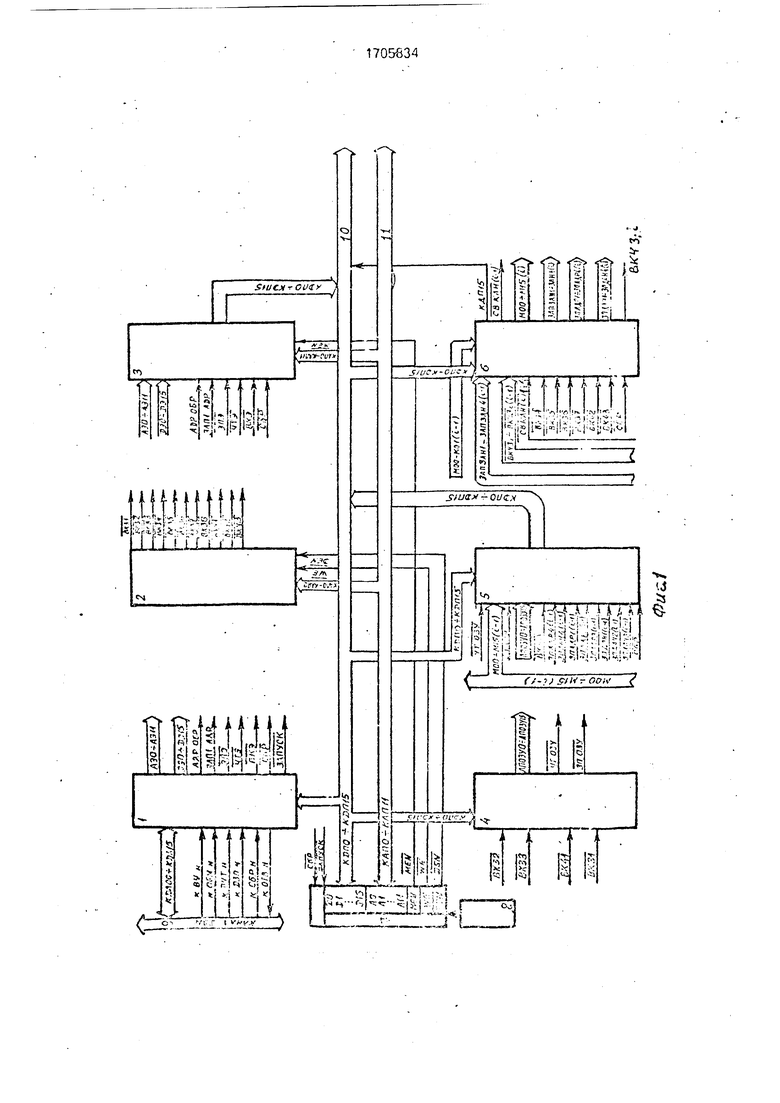

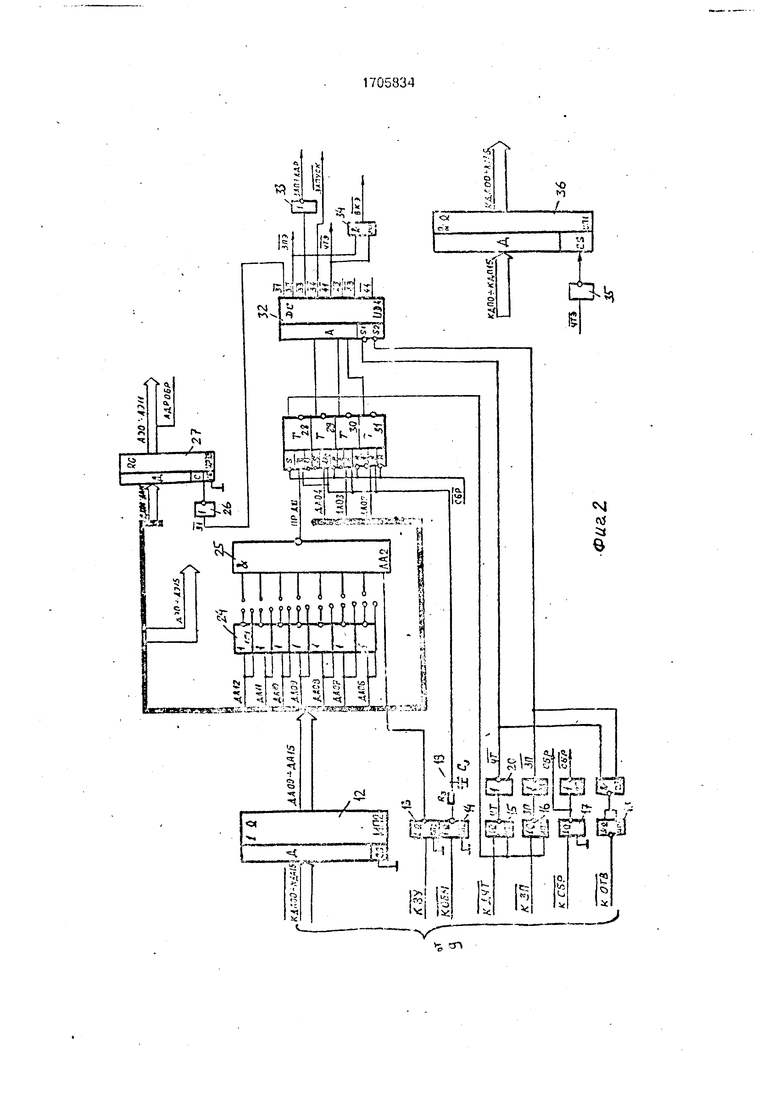

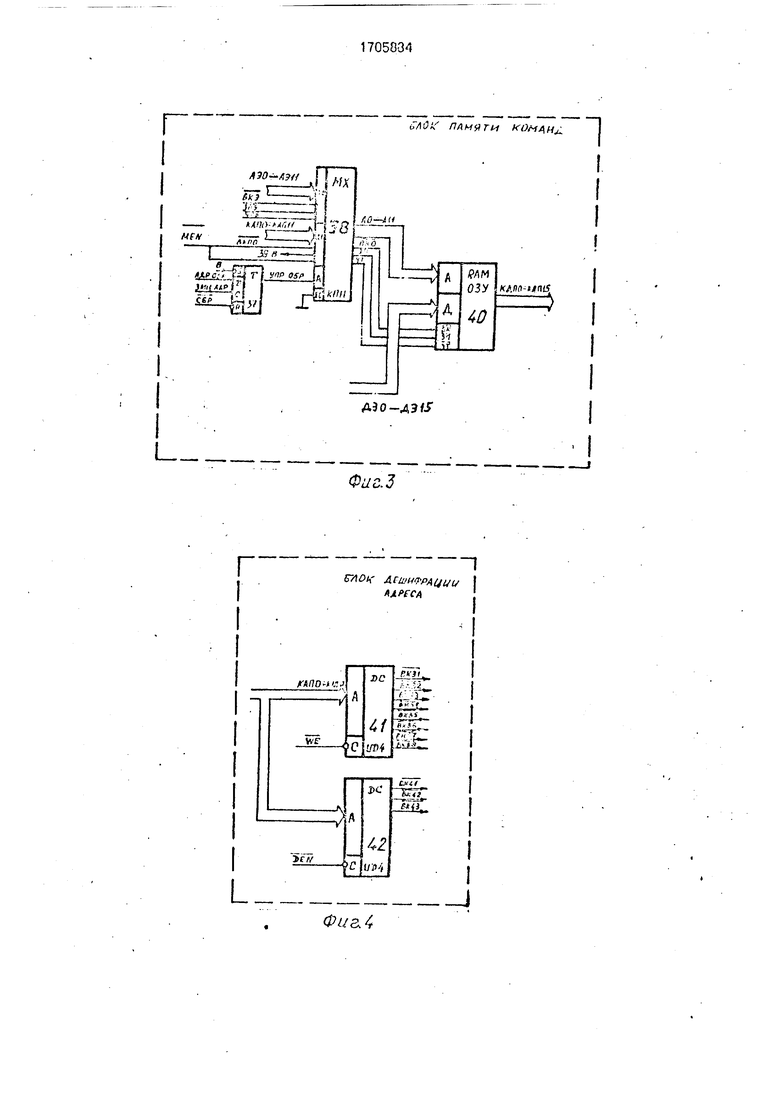

Р 4; на фиг.2 - схема блока интерфейса связи с управляющей ЭВМ, выполненного а стандарте канала МП И; на фиг.З - схема блока памяти команд; на фиг.4 - схема блока дешифрации адреса; нз фиг.5 - схема блока формирования ядреса данных; на фиг.6 - схема блока памяти данных: на Фиг.7 - схема блока oCv.if iio данными (М - количество истс п- мкоп информации, подключенных к охсдн й f-V:, истрал и д :нн;:х ппоц ссорз; Р

- кс.ичест1 о прномячгсой ин: ормоции. подключенных к выходной магистрали ъ процессора).

Специализирозанный процессор содержит блок 1 интерфейса связи с управляющей ЭВМ, блок 2 дешифрации адреса, блокЗ памяти команд, блок 4 формирования адреса данных, блок 5 памяти данных, блок 6 обмена дэнными, вычислительный блок 7, ген .оатор 8 импульсов, магистраль 9 канала С ГШ, магистраль 10 данных процессора и магистраль 11 адреса процессора.

Блок 1 интерфейса образуют коммутаторы 12-18. элемент 19 задержки, элементы НЕ 20-22, элемент 1/1 - НЕ 23, группу элементов НЕ 24, элемент И-НЕ 25, элемент НЕ 26, регистр 27, триггеры 28-31, дешифратор 32, элемент НЕ 33. элемент И 34. элемент НЕ 35 и коммутатор 36.

Блок пзмяти ::оплкд состоит из триггера , кпмму;, ;тора 35. входа 39 логической . ; иж1цы и ус,лп /:0 команд.

00

С

о ел оэ со

4

Блок . ;эи ифряции адреса выполнен на / шифраторах 41 и 42.

Блок сформирования адреса данных оключает о себя элемент НЕ 43, регистр 4, сумматор 45, коммутатор 46, регистр 47, элемент И 48 и формирователь импульса 49.

Блок памяти данных образован элементом ИЛИ 50, регистром 51, триггером 52, коммутаторами 53 и 54, узлами 55 и 56 памяти данных, элементами И 57 и 58, элементом ИЛИ-НЕ 59 и коммутатором 60,

Блок обмена данными содержит группу триггеров 61, группу .элементов ИЛИ-ИЕ 62, триггес 63, элемент И 64, элемент НЕ 65, элемент ИЛИ-НЕ 66, группы 67 и 68 триггеров, элемент И-НЕ 69, элемент И 70, группы элементов ИЛИ-НЕ 71 и 72, элемент И-НЕ 73, коммутаторы 74-77. элементы НЕ 78 и 79 и элемент ИЛИ-НЕ 80.

В качестве вычислительного блока 7 может быть использован микропроцессор ТМ S32010 или аналогичный, в качестве блока 8 помех - любые БИС статических ОЗУ. В зависимости от реализации логики записи и считывания, примененной в БИС ОЗУ, может быть использован вход чтения или записи, подключаемый к входу чтения-записи. Например, если запись осуществляется при низком уровне на входе чтения-записи, то на указанный вход подключается только сигнал ЗП, в противном случае - ЧТ.

Конкретная реализация перечисленных функциональных элементов на уровне принципиальной схемы может быть различной и зависит от конкретных особенностей используемой элементной базы. При конкретной реализации некоторые элементы могут быть конструктивно объединены, кроме того, может возникнуть необходимость вдо- полнитзльном инвертировании или задержке отдельных сигналов, причем как инверторы, так и элементы задержки конструктивно могут входить в состав используемых микросхем или быть выполнены как отдельные элементы.

Специализированный процессор работает следующим образом.

Предварительная установка узлов и блокоп процессора осуществляется сигналом К СБР, поступающим от управляющей ЭВМ.

На первом этапе осуществляется загрузка программ в блок 3 памяти команде управляющей ЭВМ через блок 1 интерфейса. Обмен осуществляется по каналу 9. Для определенности рассмотрим зарилнт интерфейса в стандарте МПИ. Поскольку специализированный процессор предназначен для использования как элемент в .многопроцессорной вычислительной системе, в которой каждый из процессоров должен иметь спой конкрьмный с1, ;р:-С jaгрузки программ с общего канала 9 управляющей ЭВМ, предусмотрена коммутация адреса.

осуществляем.:) гут(;-м установки соответствующих перемычек между выходами группы элементов НЕ 2-1 (лисе их глодлмл) с входами элемента И-НЕ 25. Факт обращения по адресу внешнего устройства (для ЭВМ) подтверждается сигналом КВУ на канале 9. который через соответствующий коммутатор (канальный приемник) поступает на вход элемента И-НЕ 25. Таким образом, нз выходе элемента И-НЕ 25 образуется признак

дешифрации (ПР ДШ) адреса данного специализированного процессора. Запись признака дешифрации ПР ДШ совместно с тремя разрядами ДА02, ДАОЗ и ДА04, обеспечивающими обращение к различным узлам процессора, осуществляется в триггеры 28-31 канальным сигналом К 06М..эадер; жанным на элементе зэдержкч 19.

Дешифрирование адреса узла, к которому осуществляется обращение, обеспечиозетсядешифратором 32. При этом три выхода 31-33 обеспечивают запись дачных и адресов, выход 41 позволяет осуществлять чтение из уг ла памяти команд е уг пс,,.л:чощу о ЭВМ через коммутатор 35 для обеспечения

контроля записываемых программ. Сигнал 34 используется для запуска вычислительного блока.

Занесение программ в блок памяти команд с управляющем ЭВМ осуществляется

в двух циклах вывода данных ЭВМ. В п-о- зсм цикле выводится адрес ячейки памя.и узла памяти команд 40, которой записывается в регистр 27 сигналом 31. С выхода рзгистра 27 адрес ячейки памяти подается

на вход коммутатора 38, на другой -лход которого поступает адрес ячейки памяти с канала адреса вычислительного бло.а 7 (при считывании команд). Управление коммутатором осуществляется сигналом управления обращением УПР 05Р с выхода триггера 37, записываемого иоедваритель- но с ЭВМ по соотоетствующему адресу, определяющему сигнал записи ЗАП1 АДР (инперг.ия сигнала 33). Тэким образом. ЭВМ

определяет режим роботы узла 40 памяти команд значенном сигналл УПР 05Р на выход . триггера 37, подключая :-. узлу 40 лиГэ вычислительный блок 7, гибо ;онал ЭВМ- Р.о «тором цмкло осуществляется аыдачя данных (кода команды) с ЭВМ для записи л ячо й у памяти, пдррс |/отсрл;Г: определен в перлом цикле. Да-,нь з поступают с канала ЭЗМ через коммутатор 12 и проходят нз оходдан ыхузл;з 40 памяти команд. Дачные

Ы 1ЛЮТС;| по з/ .ресу, сгаршая группа ра:рядоз которого определяет а/;рес данною процессора, а младшая группа, записыг.ь-э- мая в триггеры 29-3, обеспечивает форми - рование дешифратором 32 сигнала 32 записи данных ЗПЗ а узел 40 памяти.

Контрольное чтение залисзмныхв узел АО команд осуществляется аналогично с той лишь разницей, что во втором цикле вместо вывода производится ввод, и младшие разряды адреса тяковы, что дешифратором 32 обеспечивается формирование сигнала 41 чтения данных ЧТЗ. который аналогично сигналу ЗПЭ и ВКЭ поступает через коммутатор 38 на входы управления узла АО памяти команд. Необходимо отметить чтр коммутация управляющих сигналов ВКЭ, ЗПЭ, ЧТЭ, MEN осуществляется коммутг о- ром 38 аналогично коммутации адресных сигналов.

Поел.; занесения команд в узел АО триггер 37 переключается о состояние, обеспечивающее подключение узла 40 памяти к вычислительному блоку 7 через коммутатор 38 (процесс записи в триггер 37 приведен вы к ;). Формируется сигнал ЗАПУСК подачей соответствующих младших разрядов в

1 р о р л р м L г г п о «У г a fLinrvro CJMi- - - - - г - - - j- .-,-....... - ,..,

произвели )го числа (которое никуда не записывается), дешифрирование которого формирует сигнал 34. По сигналу ЗАПУСК начинается функционирование вычислительного блока, т.е. чтение команды из узла 40 памяти команд по нулевому адресу и дальнейшее исполнение записанной программы.

Для повышения скорости обработки в. специализированном процессоре предусмотрена алпг.ратная поддержка инкремен- тации адреса с задаваемым шагом инкрементации. Для этого вычислительный блок7фсрм:- пуптнам.згистрали 11 адресов адрес регистра (порта) 44, а на магистраль 10 данных выдается код величины шага инкремен- тации. Дешифратор 41 блока дешифрации адреса 2, формирующий сигналы записи, выдает сигнал ВК32.обеспечивая запись величины шага и регистр 44. После этого аналогично формируется адрес регистра 47 и код начального адреса узлов 55 и 56 памяти данных ка магистралях 11 и 10. Запись на чального а/(ррсз о регистр 47 осуществляется сигналом SK31 с выхода дешифратора 42, задержанным ..и.роаг.теле 49 импульсов. По сигналу ВК31 обеспечивается также переключение коммутатора 46 о Зра- зом, что на его пыхзд, т.е..нз информационней иход регистра 47, коммутируется магистраль /i;-H;;s x РМЧИ-ГЛИТСЛЬКОГО С/.окл 7. на KOTOf.O . ; находятся г этот момент начальный адрес узпоу 55 и 5Ј памяти дапних.

В случае пассивного состояния сигнала ВК31 коммутатор -15 обеспечивает передачу на выход сигналов с выхода сумматора 45, на котором произьодкгся инкрементация 5 лдреса с заданном в регистре 44 шагом. Результат инкрементации фиксируется в регистре 47 при обращении к углу данных в случае обращения на запись данных в узел памяти данных (сигнал ВКЗЗ и при чтении

0 данных (сигнал ВК41) , Формирователь 49 импульсов при этом обеспечивает н- обхо- димую задержку для фиксации с регистре 47 следующего значения адреса после завершения цикла обращена к памяти Таким об5 разом, для записи или считыва. чя данных из памяти вычислительному блоку не требуется самостоятельно формировать адрес, а достаточно только подряд ывать или записывать данные.

0 Блок 5 памяти данных имеет два узла 55 и 56 памяти данных. С каждым из них вычислительный блок 7 поочередно устанавливает связь ч,ерез коммутаторы 53, 54 и 60 путем занесения признака (0 или 1) в триггер

5 52. Запись признака осуществляется выработкой соответствующего адреса порта на rjMuio 11 2ПП2СЯ г Ч /слмте н . м блоксм 7, дешифрацией адреса дешифратсром.41. что приводит к возникновению сигнала ВК38.

0 Сигнал ВК38 поступает одновременно со значением признака на вход синхронизации триггера. 52 и обеспечивает его запись. В случае-, если признак равен 1. коммутатор 53 подключает магистраль 10 данных к вхо5 ду данных узла 55 памяти, а выход регистра 47 (адреса) - к входу адреса узла 55 памяти. Коммутатор 60 подключает пыход узла 55 памяти к магистрали 10 данных вычисли- тельного олока 7 при активном состоянии

0 сигнала ЧТ ОЗУ, который образует .ч непос- редственно из сигнапэ чтения ВК41. При отсутствии сигнала ЧТ ОЗУ выход коммутатора 60 находится з высокоимпедансном состоянии. Инверсный выход триггера 52

5 переключает коммутатор 54 так, что к адресным входам, узла 56 памяти подклг.чается выход регистра 51, г к входу д мных - входная магистраль ооменз данными с предыдущим каскадом специализирован0 них процессоров МО-М15. При изменении значения признака аналогичным образом происходит перекоммутацпя так, что с вычислительным блоком 7 работает узел 56 памяти дзнных, а с входной магистралью

5 МО-М15-узел 55.

Прч такой орггнизацпи вычислительный блок 7 педот обработку данных во вза- имодсйстпи.1: с orsiiM из узлпг. С-5 или 56 гчамят;1,. л другой F, это промя заг. лппется длнными результатов обработки ..редыдущсго каскада специализированных процессоров, оиходы которых подключены к магистрали МО-М 15. Кроме того, блок П обмена данными каждого специализированного процессора (СП) пьфабатыозет нео&холи- мые сигналы для синхронизации обмена. Запись адреса ячейки оперативной памяти узла 54 или 55 сопровождается сигналом ЗПАДР.-1 (от СП предыдущего каскада) при занесении в регистр 51 с магистрали MOM 15. Записи данных в узль: памяти сопровождается сигналами .-1, поступающими от СП предыдущего каскада. Элементы ИЛИ 50 и ИЛИ-НЕ 59 необходимы для объединения сигналов, поступающих с различных СП. При этом в определенный момент времени может возникнуть сигнал записи только от одного СП предыдущего каскада. Сигналы управления записью-считыванием-хранением данных в узлах 55 и 56 коммутируются аналогично информационным сигналам на коммутаторах 53 и 54.

Узел обмена данными 6 позволяетопрз- шивать готовность магистрали, связывающей дакный СП с СП последующего каскада для передачи данных в определенный СП. При этом готовность определяется не только незанятостью магистрали, но и готовностью требуемого принимающего СП принять данные. Готовность принять данные определяется вычислительным блоком 1 и устанавливается после окончания обработки данных, находящихся в узле 55 или 56 памяти, с которые в данный момент соединен вычислительный блок 7. После окончания обработки данных одного из узлов 55 и 56 вычислительный блок 7 переключает триггер 52, делая доступным освободив шийсп узел г лмяти для загрузки очередной порции данных из предыдущего каскада. После этоги вычислительный блок 7 записывает готовность в триггер 63. Для этого на магистраль 10 данных выставляется управляющее слово в нулевом разряде, содержащее единицу (остальные нули), сопровождаемое адресом соответствующего внешнего устройства (порга), таким, что дешифратор 41 вырабатывает сигнал ВКЗЗ. Этот сигнол обеспечивает записи признака обращения к триггеру 63 готовности в один из триггеров 61 группы. Остальные триггеры 61 группы необходимы для фиксации признака обращения к одному из СП следующего каскэдэ. Единица, записанная в один из триггорой 61. свидетельствует с том. что устанавливается связь с соответствующим СП. Выдача определенного сдрсса на шину адреса 11 вызывает поязл.ние сигнала ЬКЗЗ, транслирующего содержимое триггеров 61 на выход элементов ИЛИ-НЕ 62, О частности, на выходе пергсго элемента /ШИ-НЕ 62 (при записи готсчнгсги о триггер 63) возникает сигнал ЗЛП ГОТ О, подапэемый на вход синхронизации триггера 63.

Одновременно с сигналом ВК35 на магистрали данных устомаслпог.ется единица или ноль (готов или ,ie rovou) в 15-м разряде. Сигнал готовности процессора ГОТ ПР

0 поступает на аходэлемента М 64. остальные входы которого подключаются к выходам триггеров 67 группы. В триггерах 67 фиксируется факт занятия магистрали одчим из СП предыдущего каскада, ьедущим обмен с

5 данным СП. Запись признака занятия магистрали осуществляется выдачей на магистраль МО-М15 в нулезой разряд нуля одновременно с сигналом записи занятости ЗАП ЗАН, формируемым указанным обра0 зом на выходе элементов ИЛ11-НЕ 62. В процессе заполнение /данными узла 55 или 56 памяти данных СП предыдущего каскада неоднократно устанавливает связь через магистраль, поэтому после окончания пере5 дачи очередной порции данных на магистраль МОО-М15 в нулевой разряд устанавливается единица, сопровождаемая сигналом ЗАП ЗАМ для еосстзиои. признака незанятости магистрали MCQ-M15.

0 После окончания передачи последнего блока данных совместно с пы,- -чей признака незанятости на магистраль в первом разряде выдается единица - признак заполнения узла памяти данных СП.

5Признаки выполнения памяти поступают индивидуально от каждого СП предыдущего каскада в григгеры 68 группы и сопровождаются пространственно разнесенными сигналами ЗАП ЗАН, поступающи0 ми от каждого СП. При записи занятости и освобождения магистрали WOO-M15 в процессе заполнения узла 55 или 56 памяти данных первый разряд магистрали кодируется нулем.

5Поскольку в заполнении узла памяти данных может участвовать несколько СП предыдущего каскадо, выходы тр- -;аров 68 группы объединяются элементом И 70, выход которое подключен к инфсрмационно0 му входу комму пторз 76, с выходи которого вычислительный блох 7 считывает признак . окончания заполнения узла-памяти дан;-мх псами СП. Для этого нч магистраль 11 вычис- лительнь й блек 7 подаст ссответст /ющий

5 адрес, который прообразуется дешифратором 42 :: сигнал 2К1-2, Г|Сступэ:ощнй через элемент НЕ 78 на управляющий пход коммутатора 76.

Цм гпы обменов СП предыдущего каскада с последующим починаются с записи

признаков окончания запснония в те СП последующего каскада, с которыми оомен нн осущйствл.тсл.

Фо0мирос«ние сигнале:; ЗП АДР и ЗП ДАН, необходимых дня занесения адресов ячеек пгмяти и данных в узлы памяти данных из СП предыдущего каскада, осуществляется с использованием групп элементов ИЛИ-НЕ 71 и 72 аналогично формированию сигналов ЗАП ЗАН элементами 62 группы. Управление обеспечивается триггерами 51 груш.ы, а которые записываются признаки обращение к определенному СП. Стробиро- вание rjymn 71 и 72 осуществляется сигналами ВК36 и ВК37, поступающими с дешифратора 41 при формировании вычислительном блоком 7 соответствующих адресов.

При выдаче информации в СП последующего каскада чтение признака незанятой магистрали осуществляется СП предыдуще- го канала подачей сигнала ВК43, формируемым дешифратором 42 при подаче соответствующего адреса с вычислительного блока 7. Пространственно разделен. -.te сигналы ВК43 от кахдого СП объединяются элементом И-Ht 69, выход которого соединен с управляющим входом коммутатора 75. на информационный вход которого поступает признак незанятости магистрали. С выхода коммутатора 75 признак СВ КАН процессора последующего каскада считывается в СП предыдущего каскада, активный уровень сигнала СВ КАН. вырабатываемого СП. равен логическому нулю. Сигналы СВ КАН, поступающие со всех СП последующего каскада, поступают на входы элемента ИЛИ-НЕ 80 передающего СП. В случае, когда магистраль свободна, на выходе элемента ИЛИ-НЕ 80 появляется сигнал логической единицы, который, так как сиги 1Л ВК43 активен, проходит через коммутатор 74 и анализируется вычислительным блоком.

Выдача 1-:иформации на магистраль МОО-М15 осуществляется вычислительным Злоком 7 через коммутатор 77 при записи адресов (ВК35. записи данных (ВК37) и признаков (ВК35). Поэтому указанные сигналы объединяются на элементе И-НЕ 73, выход которого подключен к управляющему входу коммутатора 77.

Формула изобретения

Специализированный процессор, со- дерхащий вы -исл /тельный блок, генератор импульсов, блок доиифр.-нии адреса, блок памяти .. блек формирования адреса данных и блок памчги данных, причем выход гонср-.in/.ч импульссг. подключен к входу синхроимпульсов вычислительного

блока, информационный вход-выход которого через магистраль данных процессора подключен к информационному ьыходу блока памяти команд, первому информзцион5 ному входу и информационному ьыходу блока памяти данных, адресный пыход вычислительного блока через ма1ч: траль адреса процессора подключен к информационному входу блока дешифра0 ции адреса и первому адресному входу блока памяти команд, выходы синхронизации чтения данных и синхронизации записи данных вычислительного блока подключены соответственно к первому и второ1- / стро5 бирующим входам блока дешифрации адреса, выход синхронизации чтения команд вычислительного блока к входу синхронизации чтения команд блока памяти команд, выходы признаков чтения и запи0 си данных блока формирования адреса данных подключены соответственно к адресному сходу, входам признаков чтения и записи информации блока памяти данных, отличающийся тем, что. с целью

5 повышения быстродействия и расширения функциональных возможностей путем реализации фуНКЦИОНир; Г-.:н.й В СССТЗСС СЫчислительной сети, с него введены блок обмена данных и блок интерфейса связи с

0 управляющей ЭВМ, причем информационный вход-выход, управляющие сходы и выходы интерфейса связи с управляющей ЭВМ через магистраль канала ЭВМ подключены к соответствующим шинам управллю5 щей ЭВМ, выходы адреса данных, признака режима функционирования памяти команд, синхронизации записи признака режима, синхронизации записи, чтения и выборки команд от ЭВМ блока интерфейса связи с

0 управляющей ЭВМ подключены соответственно к второму адресному входу, информационному входу, входу режима функционирования, входу синхронизации записи режима функционирования, входам

5 синхронизации записи, чтения и выборки команд от ЭВМ блока памяти команд, вход начальной установки которого подключен к выходу начальной установки блока интерфейса связи с управляющей ЭВМ и соеди0 нен с входами начальной установки вычислительною блока, блока памяти данных и блока обмена данными, выход запуска блока интерфейса связи с управляющей ЭВМ соединен с входом запуска пычисли5 тельного блока, информационный пхсд-пы- ход которого через магистраль данных процессора подключен к информлционпым входим блокэ iiHsepY ica СРПЗИ с управляющей ЭВМ, блока фэрмнроплнич адреса данных и блока обмена данными, ьыход индикации состояния внешних магисфалсй данных блока обмена данными черэз магистраль данных процессора подключен к одному из разрядов информационного охода-выходз вычислительного блока,еь хи- ды синхронизации записи с первого по восьмой блока дешифрации адреса подключены соответственно к входам записи начального -адреса, записи шага изменения адреса и признака режима записи блока формирования адреса данных, входам записи признаков режима обмена по внешней магистрали, разрешения выдачи признаков занятости магистрали, разрешения выдачи признаков записи адреса, разрешения выдачи признаков записи данных блоха обмена данными, входу записи признака режима функционирования блока памяти данных, зыходы синхронизации чтения с первого по третий блока дешифрации адреса подключены соответственно к входу признака режима чтения блока формирования адреса данных, входам чтения признака состояния входной магистрали и признака состояния выходной магистрали блока обмена данными, адресный выход и второй информационный вход которого подключены к входной магистрали данных процессора, сходы синхронизации внешнего адреса процессора с первого по M-й подключены соответственно к входам с первого по M-й записи внешнего адреса б .ока памяти данных, где М - количестве входных источников информации, входы синхронизации внешних данных процессора с первог. по M-й подключены соответственно к входам с первого по М-й

записи внешних данных блока памяти донных, вчоды записи занятости иход.чсй магистрали процессора с первого по М-й подключены соответственно к входам с первого по M-й записи занятости входной магистрали блока обмена данными, входы опроса состояния входной магистрали с перзого по M-й процессора подключены соответственно к входам с порзого по М-й

опроса состояния входной магистрали блока обмена данными, выход опроса состояния выходной магистрали которого подключен к выходу опроса состояния выходной магистрали процессора, К-й входопроса состояния выходной магистрали и выход индикации состояния входной магистрали блока обмена данными подключены соответственно к К-му входу состояния выходной магистрали и к выходу состояния

входной магистрали процессора, входы признака занятости входной магистрали и признака окончания передачи входных данных блока обмена данными подключены соответственно к двум разрядам входной

магистрали данных процессора, информационный выход, К-й выход записи занятости, выходной магистрали, К-й выход записи внешнего адреса и выход ззпг- си внешних данных блока обмена данными подключены соответственно к выходной магистрали данных, К-му выходу записи занятости выходной магистрали, К-м выходом синхронизации внешнего адреса и внешних данных процессора, К 1...., Р. где Р количество выходных приемников информации.

капо -t-tcanfS

КАПО + КАП ft

10

}

LL

-j

о

g

. со л

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения двух элект-РОННыХ ВычиСлиТЕльНыХ МАшиН | 1979 |

|

SU809147A1 |

| Устройство для сопряжения электронной вычислительной машины с общей шиной | 1983 |

|

SU1144112A1 |

| Устройство для сопряжения двух вычислительных машин | 1986 |

|

SU1405064A1 |

| Мультипроцессорная система | 1983 |

|

SU1156088A1 |

| Устройство сопряжения двух магистралей | 1988 |

|

SU1675894A1 |

| Устройство предварительной выборки команд | 1987 |

|

SU1561073A1 |

| Устройство для сопряжения ЭВМ с общей магистралью | 1990 |

|

SU1728867A1 |

| Устройство для сопряжения магистрали микроЭВМ с магистралью периферийных устройств | 1988 |

|

SU1508220A1 |

| Устройство для сопряжения ЭВМ с магистралью внешних устройств | 1985 |

|

SU1408440A1 |

| Устройство для сопряжения между ЭВМ, оперативной памятью и внешним запоминающим устройством | 1988 |

|

SU1531103A1 |

Изобретение относится к вычислитель- .ной технике и может быть использовано для построения специализированных вычислительных систем реального масштаба времени. Целью изобретения г.зллется повышение быстродействия и расширение функциональных возможностей за счет реализации возможности функционирования в составе вычислительной сети. Специал зи- рованиый процессор содерх : г блок интерфейса связи с управляющей ЭВМ. Р.ПОК дси./фр2Ц ш адреса, блок памяти команд, блок формирования адресных данны, блок памяти данных, блок обмена данными, вычислительный блок, генератор импульсов, магистраль канала ЭВМ, магистрали данных и адресов процессора.7 ил.

0UZ1

э

vjjjrv

/IrtfiVftdH/TJJV ,V(7l/3

I

L

HJ.&HVU JQVJ

1

.J

Ј-2Лф

.f/fF-oetf

т

1Т Щ-

j юс мл

-US

г) Г- I :.---------i

IT-

f Г----------

IF

M i j ttev-Qtv

j

t-CGSOil

АЕР-/Л

т

(Г)

сэ

ID

о

(

SlfiOUV- C/ilCUV

дЪПф

O er

Г J bw€Hi

иЛ i ч t- -

f

-МО

|W

ffVfl

wj

L.

т

LJ

.

dtflOf

UX

OJc

вГСТ

v-У

-f/rTiy

CW/J|3

ЙJ

jf/jji/f Ч

«Чр

ч

ХХ2

r

iVroy

OV

ЛУ

W

9

r

Jp

5/07 -0Ц10/

Т

IАЛОЗУО-4ПЦ-/1$

HOO-rMtS

Т

Гп

1-1 Г1

ь

If

««.

I 4-50

S3

,5

ДР

A/f

Л 00 -

РЛМ

A

fc

XY

57

60

ДОО-Д

л

Л)

NX

кдпо-.дл(.5

Л

ЧГОЗУ

Ј0

(Ш

но

ГЈЕ

.W 0.1 У

AfX

ЛОО-Л (5

РАМ

О

en со

OJ

i.

1

А(

in

КП(«

J}:

Т

SS

i-П

ЗЛАДНПП

Л11 «If |if/1 j

. ZZ23TtЈJ -T

1

Mt

/7

Фи a. 6

О eS ,/ е

О О О v)

гл

о

ta

1

--TCL

di

L-UJj

Г У

С-7 О

I

i$

| Устройство обработки информации | 1986 |

|

SU1363238A1 |

| кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| -, Slgnsi P s-сззсг chips, cd.by Quarmby | |||

| D.J | |||

| Колосниковая решетка с чередующимися неподвижными и движущимися возвратно-поступательно колосниками | 1917 |

|

SU1984A1 |

| Паровозный золотник (байпас) | 1921 |

|

SU153A1 |

| рис | |||

| Кипятильник для воды | 1921 |

|

SU5A1 |

Авторы

Даты

1992-01-15—Публикация

1990-06-15—Подача