11

Изобретение относится к вычислительной технике.

Целью изобретения является расширение функциональных возможностей за счет обеспечения выполнения опе- радий преобразования полутонового изображения.

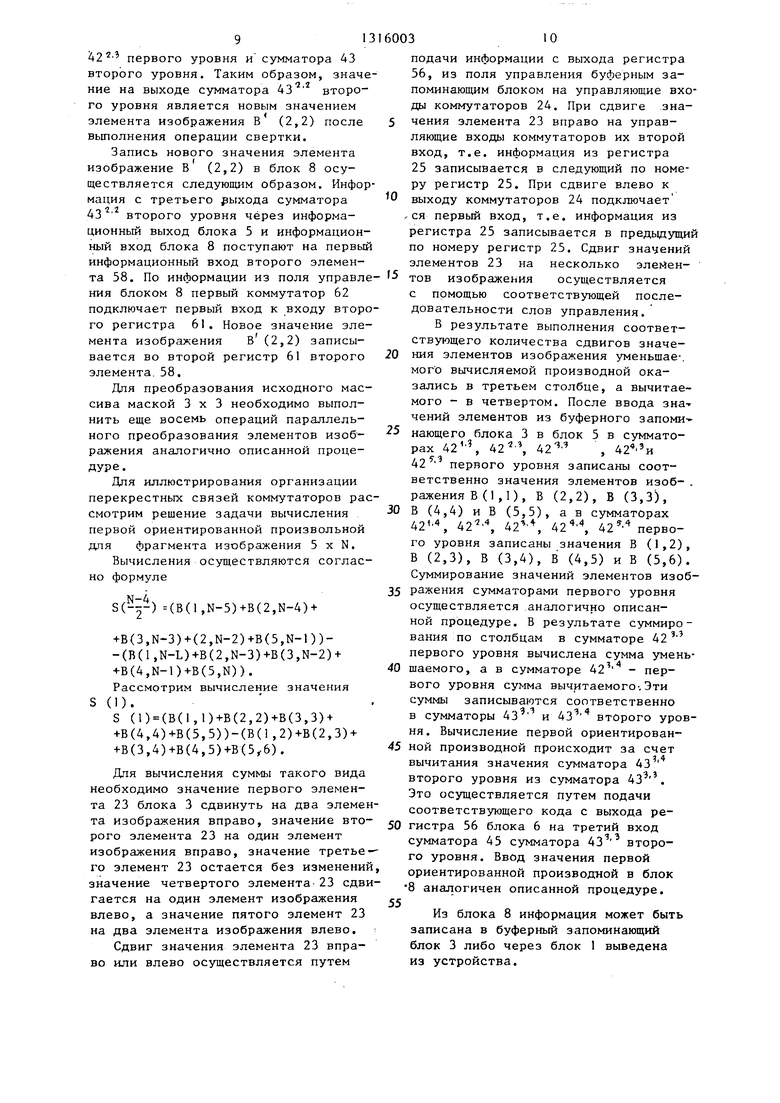

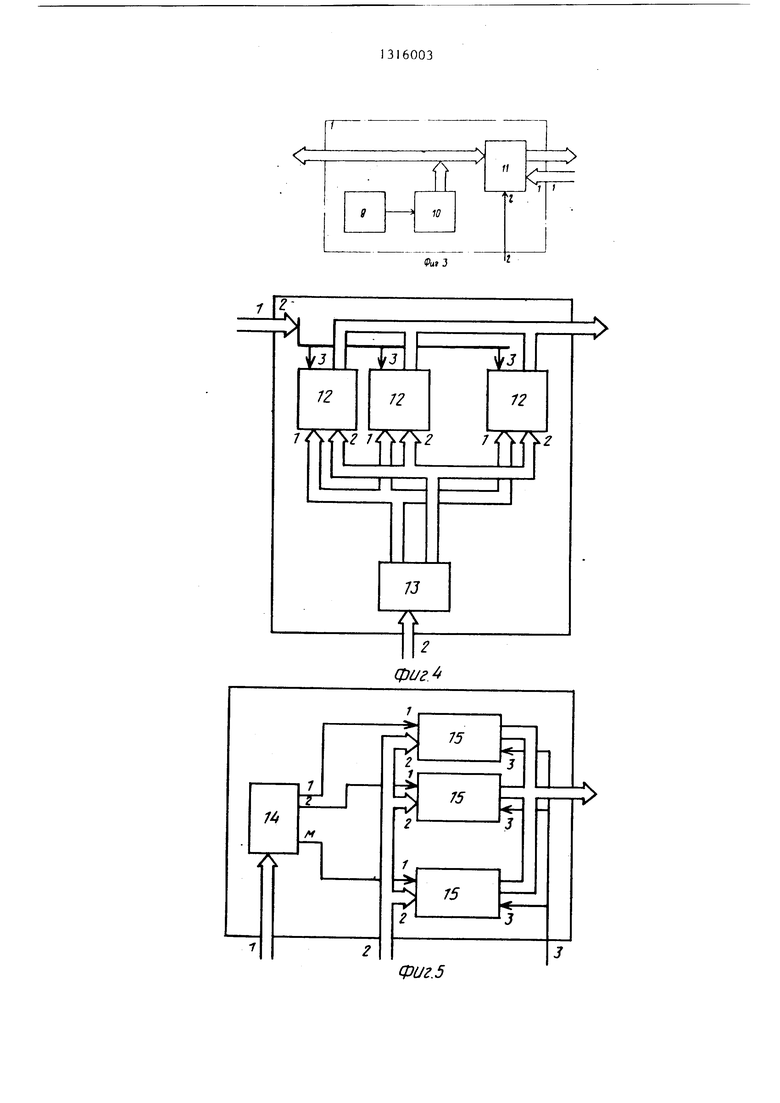

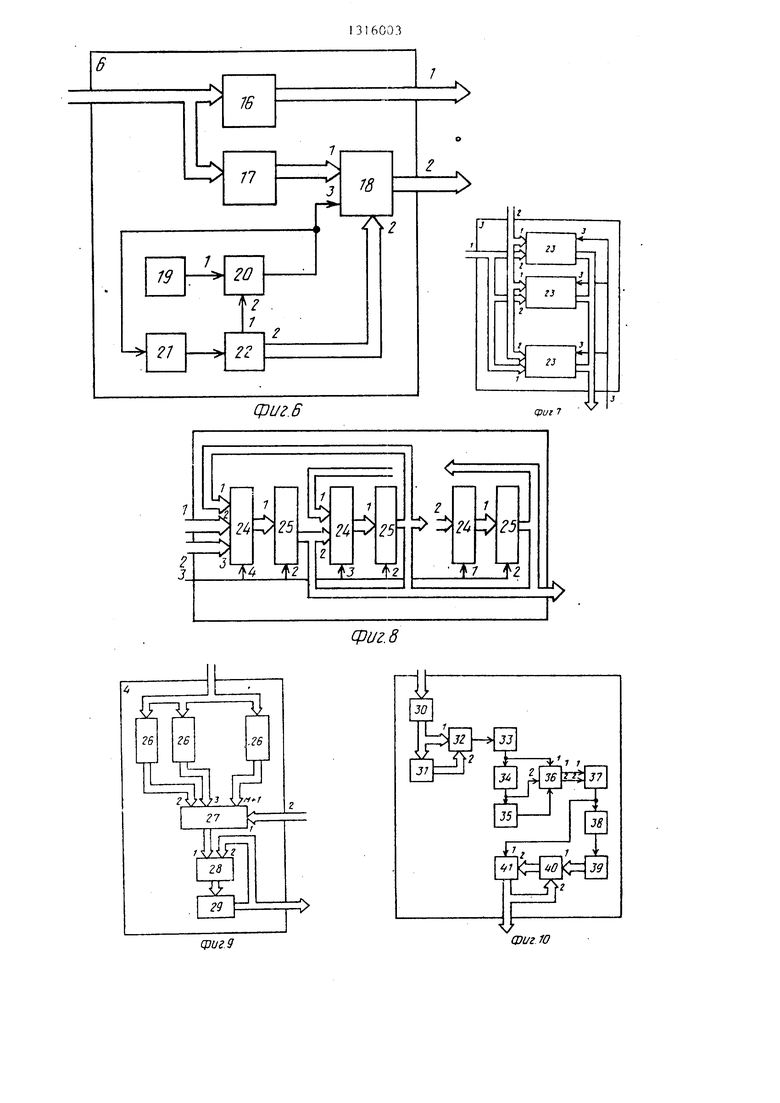

На фиг. 1 представлена схема устройства; на фиг. 2 - схема элемента памяти на строку;,на фиг. 3 - схема блока ввода-вывода; на фиг. 4 - схема блока памяти ввода; на фиг. 5 - схема узла памяти; на фиг. 6 - схема узла управления; на фиг. 7 - схема буферного запоминающего блока; на фиг.8 - схема элементов памяти на строку; на фиг. 9 - схема блока выполнения операций;на фиг. 10 - схема вычислительного узла; на фиг. 11 - схема блока суммирования; на фиг. 12 - схема сумматоров первого и второго уровня; на фиг. 13 - схема блока управления; на фиг. 14 - схема блока памяти программ; на фиг. 15 - схема блока памяти вывода.

Устройство содержит блок 1 ввода- вывода, блок 2 памяти ввода, буферный запоминающий блок 3, блок 4 выполнения операций, блок 5 суммирования, блок 6 управления, блок 7 памяти программ, блок 8 памяти вывода, генератор 9 одиночных импульсов, узел 10 постоянной памяти, узел 11 сопряжения, узлы 12 памяти, узел 13 управления, дишифратор 14,элементы 15 памяти, регистры 16 и 17, коммутатор 18, генератор 19 прямоугольных импульсов, триггер 20, ге нератор 21 прямоугольных импульсов, счетчик 22, элементы 23 памяти на строку, коммутаторы 24, регистры 25, вычислительные узлы 26, коммутатор 27, сумматор 28, регистр 29 выдачи, регистры 30 и 31, схему 32 сравнения, регистры 33 - 35, дешифратор 36, триг гер 37, генератор 38 прямоугольных импульсов, счетчик 39 сумматор 40, регистр 41 сдвига, сумматоры 42 первого уровня, сумматоры 43 второго уровня, коммутатор 44, сумматор 45, регистр 46, генератор 47 тактовых импульсов, коммутатор 48, счетчик 49, коммутатор 50, триггер 51, счетчики 52 и 53, шифратор 54, счетчик 55, регистр 56, элементы 57 памяти, элементы 58 памяти на строку, коммутаторы 59, коммутатор 60 регистры 61, коммутаторы 62.

ге3:

,

25

60032

Рассмотрим работу устройства обработки изображения на примере обработки локального фрагмента размером N X М.Информация о локальном фрагмен5 те представлена в виде исходного массива значений элементов изображения В (1, I), где ...N, ...М.Элемент изображения представляет собой значение оптической плотности в циф 0 ровой форме с дискретизацией на К уровней. Перед вводом в устройство исходного массива в блоке 1 ввода- вывода 1 происходит программирование узла 11 для работы в режиме строби 5 руемого ввода-вывода.

Программирование заключается в загрузке управляющего слова в регистр узла 1I. При включении питания генератора 9 вырабатывает одиночный

0 импульс, который поступает на вход разрешения выборки узла 10. Адресные входы узла 10 памяти заземлены,а в нулевой строке записано значение управляющего слова. Определение направления передачи через узел 11 осуществляется блоком 6 управления путем подачи сигналов управления через управляющий вход блока 1 на входы считывания и записи информации

узла 1 1 .

При вводе исходного массива значений элементов изображения запускается генератор 47 блока 6 управления. Импульсы с выхода генератора

35 47 поступают на вход, который является информационнь№1 входом коммутатора 48. На адресный вход коммута тора 48 поступает код нуля с выхода шифратора 54. На входы шифратора 54,

40 которые являются младшими адресными входами, поступают сигналы с выходов прямого переноса счетчиков 49,53 и 55 и выхода обратный перенос счетчика 52. В каждой строке шифратора 54

45 соответственно комбинации входных

сигналов записан код управления мутатором 48. Импульсы с первого выхода коммутатора 48 поступают на вход счетчика 49, который вырабаты.50 вает адреса ячеек памяти блока 2 при вводе исходного массива. Значение адреса с первого информационного выхода счетчика 49, через коммутатор 50 поступает на информационный вход

.55 узла 13. Управление коммутатором 50 осуществляет триггер 51. Старшие разряды адреса, с помощью которых происходит адресация памяти по строкам, записываются в регистр 15 узла I3

3

управления, n м.члдпшс разряды, для адресации памяти по столбцам, - в регистр 17. Старшие разряды адреса с первого информационного выхода узла 13 управления поступают через первые информационные входы узлов 1 памяти на вход дешифратора 14. Леиш ратор 14 во всех узлах 12 памяти в соответствии со значением старших разрядов адреса выбирает строку памяти, в которую необходимо записать значение элемента изображения, путем подачи управляющего сигнала на вход записи одного из элементов 15. На второй вход элементов памяти 15 поступают младшие разряды адреса с выхода коммутатора 18 узла 13, а на третий вход - соответствующий, разряд элемента изображения. Элемен изображения поступает на первый информационный вход блока 2, каждый разряд при этом подается на соответствующий узел 12. Таким образом на входы всех элементов 15 памяти постпает адрес ячейки памяти и значение разряда элемента изображения, запись которого происходит в элемент 15 памяти, на вход которого поступает управляющий сигнал с дешифратора 14. I

Последовательное соединение генератора 19, триггера 20, генератора 21 и счетчика 22 узла 13 предназначено для регенерации элементов 15 памяти. Регенерация памяти является необходимым условием сохранения информации в динамических запоминающих устройствах и заключается в последовательном обращении к ячейкам памяти одновременно во всех элементах 15 памяти. По переднему фронту импульса периода регенерации триггер 20 устанавливается в единичное состояние, переключая коммутато 18 на передачу младших разрядов адреса с выхода счетчика 22 и запуска генератор 21. С выхода генератора 21 импульсы цикла регенерации поступают на вход счетчика 22, который вырабатывает адреса регенерации ячеек памяти. После регенерации последней ячейки памяти с выхода переноса счетчика 22, триггер 20 сбрасывается в нулевое состояние, переключая коммутатор 18 на передачу младших разрядов адреса с выхода регистра 17 и останавливая генератор 21 импульсов. Операции записи

0 Ч4

и чтения информации из элементов 1 памяти возможны только в промежутках между окончанием регенерации С1аршей ячейки памяти и началом нового периода реге)1ерации,

Таким образом на информационшлй вход блока 2 поступают последовательно значения элементов изображения исходного массива, упорядоченного по

строкам, а на адресный вход - соот- вествующие адреса ячеек памяти, вы- рабатываемые счетчиком 49 блока 6.

Значения элементов изображения исходного массива записываются в

блоке 2 адекватно их пространственному расположению на локальном фрагменте.

После выработки генератором А7

6 N X М импульсов на выходе переноса счетчика 49 появляется сигнал. По этому сигналу триггер 51 устанавливается в единичное состояние, переключая на выход коммутатора 50 счетчика 52 и выбирая в шифраторе 54 строку, где записан код единицы. В соответствии с кодом коммутатор 48 переключает выход генератора 47 на вход счетчика 52, Счетчик 52

вырабатывает адреса ячеек памяти

при записи исходного массива из блока 2 в буферный запоминающий блок 3, запись осуществляется параллельно во все строки. Это организовано путем соединения информационных выходов элемента 15 памяти всех узлов 12 памяти с соответствующими разрядами элемента 23 памяти на строку. Счетчик 52 блока 6 вырабатывает младшие разряды адресов ячеек памяти, начиная со старшей ячейки к младшей. Счетный вход счетчика 52 является входом обратного счета. Младшие разряды адреса ячейки памяти через коммутатор 50 блока 6, регистр 17 и коммутатор 18 узла 13 поступают параллельно на входы элементов 15 памяти всех дузлов 12 памяти. Информация с выхода узлов 12 памяти поступает через информационный вход буферного запомина ще- го блока 3 на информационный вход соответствующего элемента 23 памяти на строку и череэ информационный вход блока 4 на информационные входы соответствующего узла 26. По управляющему входу элементов 23 памяти на строку из регистра 56 блока 6 на управляющий вход ком гутаторов 24

513

поступает код, который подключает к входу регистров 25 элементов 23 памяти на строку второй вход коммута торов 24.

Значения элементов изображения I строки В (1, I), где ...l, после- довательно поступают на информационный вход соответствующего узла 26. Узел 26 вычисляет значение протяженности наиболее чарто встречающегося объекта в данной строке на обрабатываемом локальном фрагменте. В регистр 30 узла 26 записывается вводимое значение элемента изображения, а в регистре 31 хранится значение предыдущего элемента В. Эти два значения сравниваются схемой 32 сравнения и результат запоминается в регистре 33. При вводе следующего значения предьщущее значение из регистра 30 записывается в регистр 31, а информация -из регистра 33 записывается в регистр 34. Ввод значения последующего элемента изображения повторяет процедуру. Если встречается последовательность из четырех значений элементов изображения, когда каждый последующий элемент больше предыдущего, т.е. встречается граница объекта, то на первом выходе дешифратора 36 появится сигнал, который установит триггер 37 в одиночное состояние. Триггер 37 запускает генератор 38, импульсы с выхода которого поступают на вход счетчика 39. Частота генератора 38 соответствует частоте генератора 47 блока 6. Сброс триггера 37 и остановка генератора 38 будет осуществлена по задней границе объекта, когда в последовательности из четырех значений элементов изображения каждый последующий будет меньше предыдущего. В .этом случае дешифратор 36 импульсом с второго выхода триггера 37 запрещает работу генератора 38 и сдвигает значение в регистре 41 влево на один разряд.

Информация о протяженности объекта с выхода счетчика 39 поступает на вход сумматора 40, на второй вход сумматора поступает информация с выхода регистра 41, где хранится информация о среднем значении протяженности предыдущих объектов.

Таким образом после выработки счетчиком 52 блока 6 N значений адресов на выходе перенос счетчика 52 появится сигнал. Шифратор 54 в соответствии с новым значением входов

36

выставит на выходе код двойки, который переключит вход коммутатора 48 на третий выход. Импульсы с выхода генератора 47 будут поступать на

вход счетчика 53. Информация с выхода счетчика 53 поступает через информационный выход блока 6 информационный вход блока 4 на управляющий вход коммутатора 27. Коммутатор 27

последовательно подключает к входу сумматора 28 информационные выходы узлов 26.

Аналогично работе сумматора 40 и регистра 41 узла 26 сумматор 28 и

регистр 29 блока 4 вычисляют значение протяженности наиболее часто встречающегося объекта на обрабаты-. ваемом локальном фрагменте на основе значений протяженности объектов по

строкам. После выработки генератором 47 М импульсов информация из регистра 29 поступает на информационный вход блока 6 управления и записывается в счетчик 55. На выходе счетчика 53 появляется сигнал. По этому сигналу шифратор 54 выставляет код тройки и коммутатор 48 переключает информационный вход на четвертый выход,

Информация, загружаемая из блока 4 в счетчик 55, является начальным адресом программы обработки изображения. В соответствии с адресом с выхода счетчика 55, поступающим через информационный выход блока 6 управления и вход блока.7 памяти программ на входы элементов 57 памяти, с информационных выходов элементов памяти считывается в регистр

56 блока 6 управления слово управления. Слово управления представляет собой пять полей управления: поля управления блоком суммирования, буферным запоминающим блоком, блоком

памяти вывода, блоком ввода-вывода и поля окончания программы обработки.

Рассмотрим задачу подавления шумов в исходном изображении за счет применения низкочастотной пространственной фильтрации, выполняемой маской с положительными элементами. Обработка изобр ажения осуществляется маской вида

Г 1 2 Г

242 1 2 1 Преобразование значений элеменов изображения в регистрах 25 проке713

ходит одио}чи меНПО но псих племеитах 23 памяти ia строку. Иоле буферного запоминающего блока разбивается на квадраты 3 х 3 и преобразование rso всех квадратах ocyщec Tiл ieтcя идентично и параллельно, поэтому расмот- рим процесс преобразования информации в регистрах на основе первого- квадрата. Разрядность ПОЛЯ управления буферным запоминающим блоком в слове управления определяется количеством регистров 25 и коммутаторов 24 в буферном запоминающем блоке 3.

После записи первого управляющего слова в регистр 56 блока 6 информация с выхода поля управления буферным запоминающим блоком поступает на вход второго регистра 25 первого элемента 23 памяти на строку регистров первого, второго и третьего регистров второго элемента 23 и второго регистра 25 третьего элемента 23. Значение этих регистров 25 умножается на два путем сдвига влево на один разряд По следующему сигналу генератора 47 на выходе счетчика 55 блока 6 формируется адрес следутошего управляющего слова, которое записывается в регистр 56. В этом управляющем слове установлен только разряд, который поступает на вход сдвигов второго регистра 25 второго элемента 23, следовательно, в результате двух сдвигов значение этого сдвигового регистра будет умножено на 4.

Таким образом преобразование значения всех регистров 25 ос ществля- лось за два тактовых сиг-нала генератора 47.

Для вычисления значения функции свертки поле сумматоров 42 первого уровня блока 5 разбивается на прямоугольники 2x3. Процесс суммирования происходит идентично и параллельно во всех прямоугольниках.

Вычисление функции свертки для первого квадрата буферного запоминающего блока происходит следующим образом. В регистр 56 загружается очередное слово управления. Сигнал с выход поля управления блоком 5 поступает на пятый вход коммутатора 44 суммато

/„1,1 .„Ii2 ,5

ров первого уровня 42 , 42 , 2 , 42 , 42 и (индексация по строкам и столбцам). На выход коммутатора 44 подключается первый информационный вход и в регистр 46 через сумматор 45 указанных сумматоров первого уровня соответственно записы38

влмтс.ч иачг ния перш го, нторсч о и третьего х-1 истрин 23 riepnoro элемента 23 н neiinoru, нторси о и трст1 сго регистров третьего элемента 23. } ежям работы сумматоров 45 определяется также информацией поля ynpaii. ie- ния блоком 5 регистра 56.

При вводе в регистр 56 следующего слова управления на входы коммутаборов 44 сумм зторов , 42 и

, т (.3

42 первого уровня поступан т коды, переключающие на выход коммутатора

44BTOpoii информационный вход. На второй информационньп вход сумматора 45 сумматоров , , 42 первого уровня поступают значения с выхода соответствующего регистра 25 второго элемента 23 буферного запоминающего блока 3. На первый

вход сумматоров 45 поступает информация с выхода регистра 46 и, следовательно, на выходе сумматоров

45сумматоров первого уровня формируются соответствующие суммы регистров 25.

По следующему слову управления на пятые входы коммутаторов 44 сумматоров первого уровня 42 , 42 и 42 поступают коды, которые переключают на выход KON yTaTOpa 44 третий вход, т.е. на второй вход сумматора 45 поступает информация с соседних по столбцу cybfMaTopoB первого уровня. На выходе сумматоров 45 суммато/ 1 2 42 и

ров первого уровня

42 формируются суммы значений регистров 25 третьего элемента 23 и

/ п . / т .2 ; 1.

сумматоров 42 ,42 , 42 первого уровня. Таким образом находится сум0 ма значений регистров по столбцам.

Очередное слово управления подает на пятый вход коммутаторов 44 сумматоров 43 и 43 второго уровня коды, которые подключают к выходу

5 коммутатора 44 первый информационный вход. В регистры 46 первого и второго сумматоров 43 второго уровня записываются значения с выходов соответствующих сумматоров 42 и 42 пер0 вого уровня. Процедура вычисления значения сумматорами второго уровня аналогична выполнению этой процедуры сум1-1аторами первого уровня. По следующему слову управления на суммато5 ре 43 второго уровня суммируется

,-.1

значение сумматоров 42 и 42 первого уровня, а следующим тактом на сумматоре 43 второго уровня определяется сумма значений сумматора

913

42 первого уровня и сумматора 43 второго уровня. Таким образом, значение на выходе сумматора 43 второго уровня является новым значением элемента изображения В (2,2) после вьтолнения операции свертки.

Запись нового значения элемента изображение В (2,2) в блок 8 осуществляется следующим образом. Информация с третьего ыхода сумматора второго уровня через информационный выход блока 5 и информационный вход блока 8 поступают на первый информационный вход второго элемента 58. По информации из поля управления блоком 8 первый коммутатор 62 подключает первый вход к входу второго регистра 61. Новое значение элемента изображения В (2,2) записывается во второй регистр 61 второго элемента.58.

Для преобразования исходного массива маской 3x3 необходимо выполнить еще восемь операций параллельного преобразования элементов изображения аналогично описанной процедуре.

Для иллюстрирования организации перекрестных связей коммутаторов рассмотрим решение задачи вычисления первой ориентированной произвольной для фрагмента изображения 5 х N.

Вычисления осуществляются согласно формуле

S() (B(l,N-5)+B(2,N-4)+

-t-B(3,N-3)+(2,N-2)-i-B(5,N-l))-(B(l,N-L)+B(2,N-3)+B(3,N-2)(4,N-l)-bB(5,N)).

Рассмотрим вычисление значения

S (1).

S (1)(В(1,1)+В(2,2)В(3,3)

+В(4,4)+В(5,5))-(В(1,2)+В(2,3)+

+В(3,4)+В(4,5)+В(5,6).

Для вычисления суммы такого вида необходимо значение первого элемента 23 блока 3 сдвинуть на два элемента изображения вправо, значение второго элемента 23 на один элемент изображения вправо, значение третье го элемент 23 остается без изменений значение четвертого элемента 23 сдви гается на один элемент изображения влево, а значение пятого элемент 23 на два элемента изображения влево.

Сдвиг значения элемента 23 вправо или влево осуществляется путем

60031 О

подачи информации с выхода регистра 56, из поля управления буферным запоминающим блоком на управляющие входы коммутаторов 24. При сдвиге зна5 чения элемента 23 вправо на управляющие входы коммутаторов их второй вход, т.е. информация из регистра 25 записывается в следующий по номеру регистр 25. При сдвиге влево к

0 выходу коммутаторов 24 подключает .ся первый вход, т.е. информация из регистра 25 записывается в предыдущий по номеру регистр 25. Сдвиг значений элементов 23 на несколько элемен- 5 тов изображения осуществляется с помощью соответствующей последовательности слов управления.

В результате выполнения соответствующего количества сдвигов значе20 ния элементов изображения уменьщае-, мог о вычисляемой производной оказались в третьем столбце, а вычитаемого - в четвертом. После ввода зна-- чений элементов из буферного запоми- 5 нающего блока 3 в блок 5 в сумматорах 42 % 42 42 , 42 и первого уровня записаны соответственно значения элементов изоб- . ражения В(1,1), В (2,2), В (3,3),

30 В (4,4) и В (5,5), а в сумматорах 42 42 42 Л перво- го уровня записаны значения В (1,2), В (2,3), В (3,4), В (4,5) и В (5,6). Суммирование значений элементов изоб35 ражения сумматорами первого уровня осуществляется аналогично описанной процедуре. В результате суммиро- вания по столбцам в сумматоре первого уровня вычислена сумма умень40 шаемого, а в сумматоре 42 - первого уровня сумма вычитаемого-. Эти суммы записываются соответственно в сумматоры и 43 второго уровня. Вычисление первой ориентирован45 ной производной происходит за счет вычитания значения сумматора 43 второго уровня из сумматора . Это осуществляется путем подачи соответствующего кода с выхода ре50 гистра 56 блока 6 на третий вход сумматора 45 сумматора 43 второго уровня. Ввод значения первой ориентированной производной в блок 8 аналогичен описанной процедуре.

Из блока 8 информация может быть записана в буферный запоминающий блок 3 либо через блок 1 выведена из устройства.

I 113

Информация с выхода регистров 61 элементов 58 поступает на вход соответствующего коммутатора 59. Первый выход коммутаторов 59 соединен с вторым входом соответствующего элемента 23 буферного запоминающего блока 3, второй выход - с соответствующим входом коммутатора 60.

При записи информации из блока 8 в буферный запоминающий блок 3 на входы коммутаторов 62 элементов 58 с третьего выхода регистра 56 блока 6 из поля управления блоком 8 поступает информация, которая подключает к выходу коммутаторов 62 второй вход. В элементах 23 на выход первого коммутатора 24 подключаетс третий вход, а на выход остальных коммутаторов 24 второй вход. Записывая в регистр 56 последовательность из управляющих слов, информация в элементах 58 будет сдвигаться вправо. По каждому управляющему слову значение регис.тра 61 будет записано в следующий по номеру регистр 61 по сигналу, поступающему с выхода регисра 56 из поля управления блока 8. На вторые информационные входы элементов 23 блока 3 поступает последовательность значений элементов изображ женил. Запись информации в блок 3 аналогична описанной процедуре.

При выводе результатов обработки из устройства коммутатор 60, управляемый по первому входу, подключает последовательно к выходу входы, начиная со второго. Коммутаторы 59 подключают первый вход к второму выходу. Управление коммутаторами 59-И 60 осуществляется информацией из поля управления блоком памяти вывода. Сдвигая информацию последовательно в элементах 58, новые значения элементов изображения со второго выхода блока 8 поступают на вход блока 1.

На вход узла 11 из поля управления блоком 1 ввода-вывода регистра 56 поступает информация, которая nt- реводит узел 11 в режим чтения.

После окончания вывода информация из блока 8 в последнем управляющем слове в поле управления окончанием программы записан признак окончания обработки локального фрагмента Эта информация с выхода регистра 56 поступает на вход шифратора 54 блока 6.Шифратор 54 вырабатывает код,который отключает вход коммутатора 48 от четвер

10

15

0

00312

того выхода, и счетчик 55 перестает вырабатывать адреса ячеек памяти блока 7 памяти программ. Формула изобретения

5 1. Устройство для обработки изоб- ражений, содержащее блок памяти ввода, буферный запоминаюпуш блок, блок памяти вывода, блок управления и блок ввода-вывода, первые информа- . цонные вход и выход которого являются соответственно входом и выходом устройства, а управляющий вход - подключен к первому управляющему выходу блока управления, о т л и - чающееся тем, что, с целью .расширения функциональных возможностей за счет выполнения операций преобразования полутонового изображения, в него введены блок памяти программ, блок суммирования и блок выполнения операций, включающий вы - числительные узлы, коммутатор, сумматор и регистр выдачи, информационный вход которого соединен с выходом сумматора, вход первого слагаемого которого подключен к выходу коммутатора, выход регистра выдачи соединен с входом второго слагаемого сумматора и входом начального адреса

программ блока управления, выходы

I

вь1числительных узлов подключены

к информационным входам коммутатора, второй информационный выход блока ввода-вывода подключен к инфор- мационному входу блока памяти ввода, адресный вход которого соединен с выходом адреса данных блока управления, выход блока памяти ввода соединен с входами вычислительных узлов и с первым информационным входом буферного запоминающего блока, выход которого подключен к информационному входу блока суммирования, выход которого подключен к информационному входу блока памяти вывода, первый и второй выходы которого соединены соответственно с вторыми информационными входами буферного запоминающего блока и блока ввода-вывода, выход блока

5

30

40

45

50

55

памяти программ соединен с входом команд блока управления, управляющие входы блока суммирования, буферного запоминающего блока, блока па- пяти вывода и коммутатора соединены соответственно с вторым, третьим, четвертым, пятым управляющими выходами блока управления, выход текущего адреса команды которого под131

ключей к адресному входу блока памяти программ,

2. Устройство по п.1, о т л и - чающееся тем, что каждый вычислительный узел содержит регистры, схему сравнения, дешифратор триггер, сумматор, регистр сдвига, счетчик и генератор прямоугольных импульсов, выход которого подключен к счетному входу счетчика, а вход соединен с выходом триггера, информационный вход первого регистра является входом вычислительного узла, выход первого регистра подключен к информационному входу второго регистра и к первому входу сравнения, второй вход которой подключен к выходу второго регистра выход схемы сравнения соединен с информационным входом третьего регистра, выход которого подключен к информационному входу четвертого регистра, выход которого подключен к информационному входу пятого регистра, выходы третьего, четвертого и пятого регистров подключены соответственно к входам дешифратора, первый и второй выходы которого соедин Hbi соответственное входами установки и сброса триггера, выход которого подключен к управляющему входу регистра сдвига, выход счетчика соединен с входом первого слагаемого сумматора, выход которого соединен с информационным входом регистра сдвига, выход которого подключен к входу второго слгаемого сумматора и к выходу узла.

314

3. Устройство по п. I, о т л и - ч а ю щ е е с я тем, что блок управления содержит счетчики, коммутаторы, триггер, шифратор, регистр и генератор тактовых импульсов, выход

которого подключен к информационному входу первого коммутатора, адресный вход которого соединен с выходом шифратора, выходы первого коммутатора

соединены соответственно с счетными входами первого, второго, третьего и четвертого счетчиков, выходы разрядов первого и второго счетчиков соединены соответственно с первым и вторым информационными входами второго коммутатора, выход которого является выходом адреса данных блока, выход переноса первого счетчика подключен к первому входу шифратора и к входу установки триггера, выход переноса второго счетчика соединен с вторым входом шифратора и с входом; сброса триггера, выход которого соединен с управляющим входом коммутатора, выход переноса третьего счетчика соединен с третьим входом шифратора, выходы разрядов третьего счетчика являются пятым управляющим .выходом блока, информационный вход четвертого счетчика является входом начального адреса программ блока, выходы разрядов четвертого счетчика являются выходом текущего адреса команды блока, выходы разрядов регистра подключены соответственно к второму,.третьему, четвертому и первому управляющим выходам блока и к четвертому входу шифратора, вход регистра является

входом команд блока.

.2

ФигЗ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для преобразования телевизионного стандарта | 1986 |

|

SU1343562A1 |

| Устройство буферизации команд процессора | 1983 |

|

SU1092506A1 |

| Буферное запоминающее устройство с произвольной выборкой двумерного фрагмента | 1986 |

|

SU1444784A1 |

| Конвейерное буферное запоминающее устройство для систем обработки изображений | 1989 |

|

SU1751769A1 |

| Устройство для ввода информации | 1988 |

|

SU1580340A1 |

| Устройство центрального управления процессора | 1983 |

|

SU1136177A1 |

| Устройство для воспроизведения псевдообъемного изображения | 1984 |

|

SU1233302A1 |

| Устройство для преобразования малокадрового телевизионного стандарта | 1985 |

|

SU1256245A1 |

| Цветная телевизионная камера | 1984 |

|

SU1233301A1 |

| Устройство для считывания цветной графической информации | 1989 |

|

SU1695339A1 |

Изобретение относится к вычислительной технике. Целью изобретения является расширение функциональных возможностей за счет обеспечения выполнения операций преобразования полутонового изображения. Устройство содержит блок 1 ввода, блок 2 памяти ввода, буферный запоминающий блок 3, блок 4 выполнения операций, блок 5 суммирования, блок 6 управления, блок 7 программ, блок 8 памяти вывода. В устройстве осуществляется низкочастотная пространственная фильтрация посредством маски 3x3 элемента с положительными элементами. 2 3.п. ф-лы, 15 ил. с € (Л ю Э5 о о со сриг.1

Фиг.5

фиг.8

сригЗ

фиг Ю

J

Фиг. //

Фиг 12

сриг. /J

R/.w

ери г./5

| Пароводогрейное устройство | 1961 |

|

SU149516A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Duff M.I.В | |||

| Geometrical analysis of i mage.part | |||

| - In: Digital Image Processing and Analysis/Eds, Simon I.e | |||

| and Rosenfeld A | |||

| Leyden, Fhe Netherlands | |||

| Noordhoff, 1977, p | |||

| Приспособление для записи звуковых явлений на светочувствительной поверхности | 1919 |

|

SU101A1 |

Авторы

Даты

1987-06-07—Публикация

1986-01-08—Подача