13435622

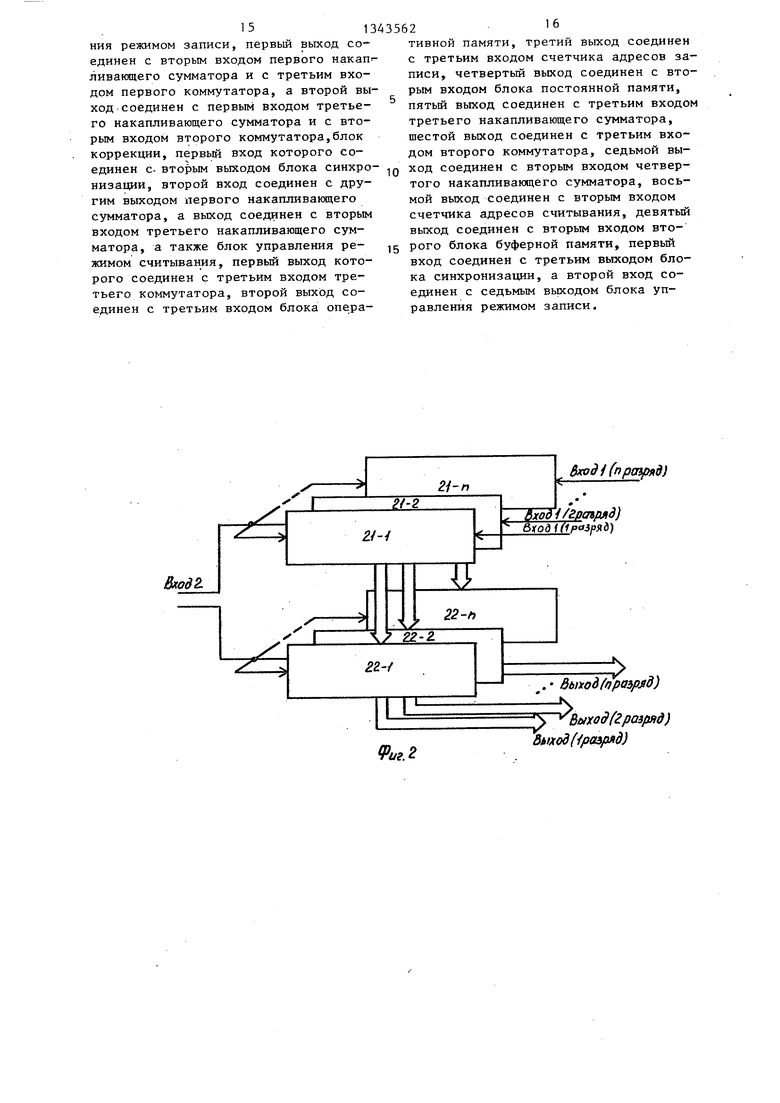

Изобретение относится к технике раллельные регистры 21-1-21-п, паралтелевидения и может быть использова-лельные регистры 22-1-22-п.

Но при построении устройств преобра-Блок 3 оперативной памяти (фиг.З)

эования и отображения многофрагмент-содержит блоки 23-1-23-п оперативных

ных движущихся изображений в мало-запоминающих устройств,

кадровых телевизионных системах, Блок 23-i оперативных запоминающих

Цель изобретения - расширение фун- устройств (фиг.4) содержит оперативкциональных возможностей путем обе-ные запоминающие устройства 24-1-24-k,

спечения отображения многофрагмент-io Первый 7 и второй 9 накапливающие

ных движущихся изображений в .режимесумматоры (фиг.З) содержат сумматор

панорамирования с регулируемьми ско-25 и параллельный ре)гистр 26.

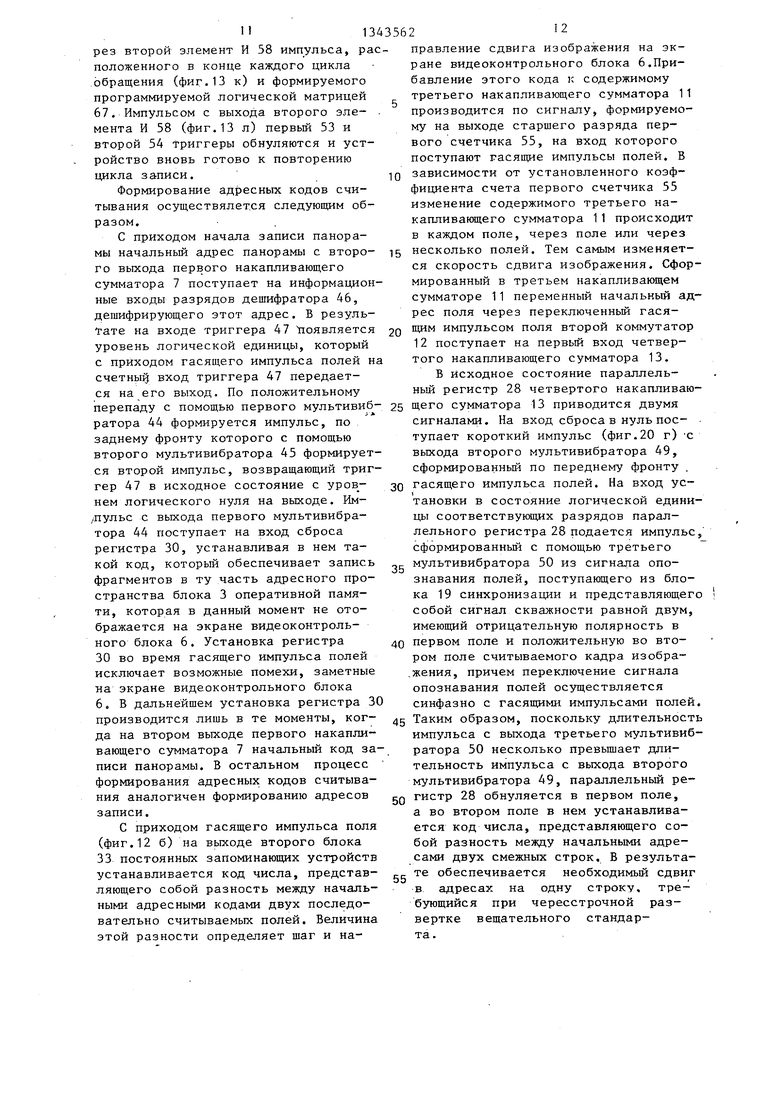

ростью и направлением сдвига.Четвертый накапливающий сумматор

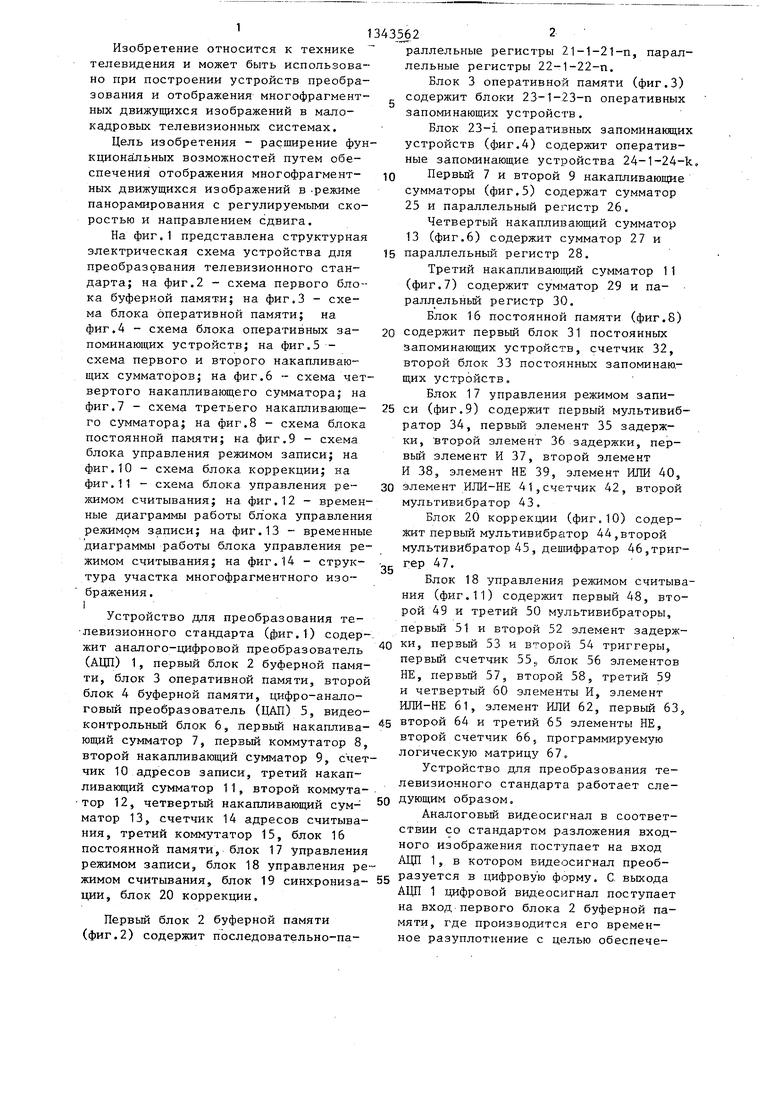

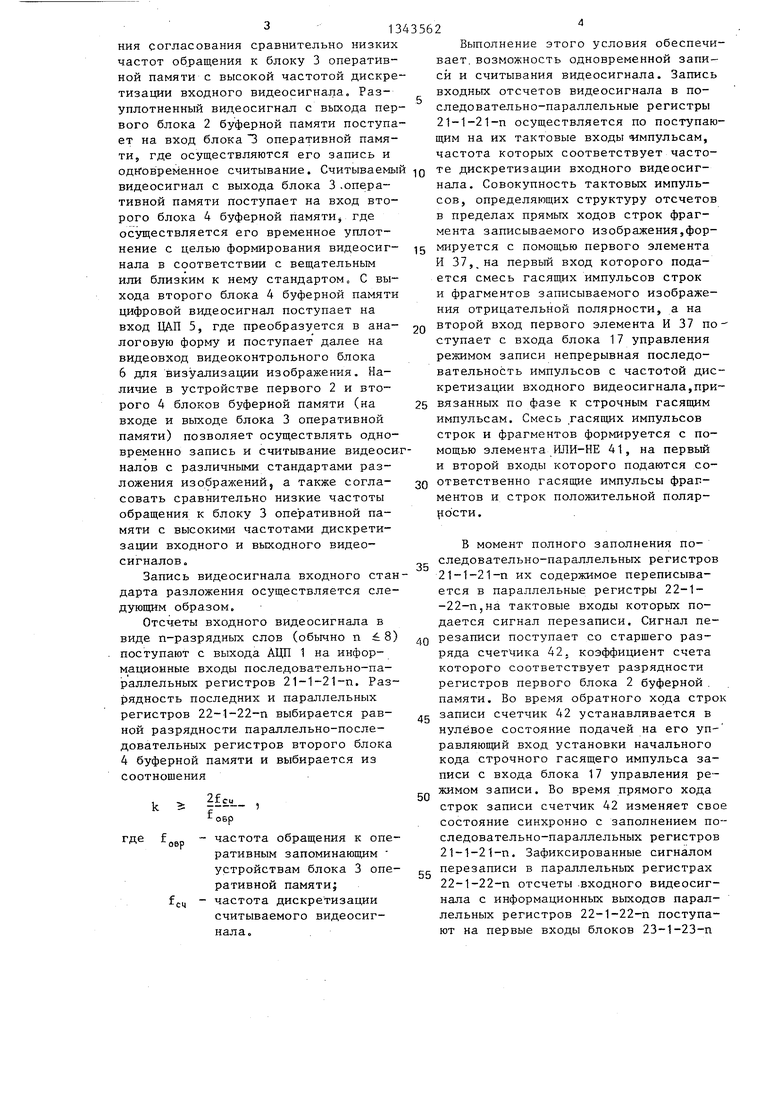

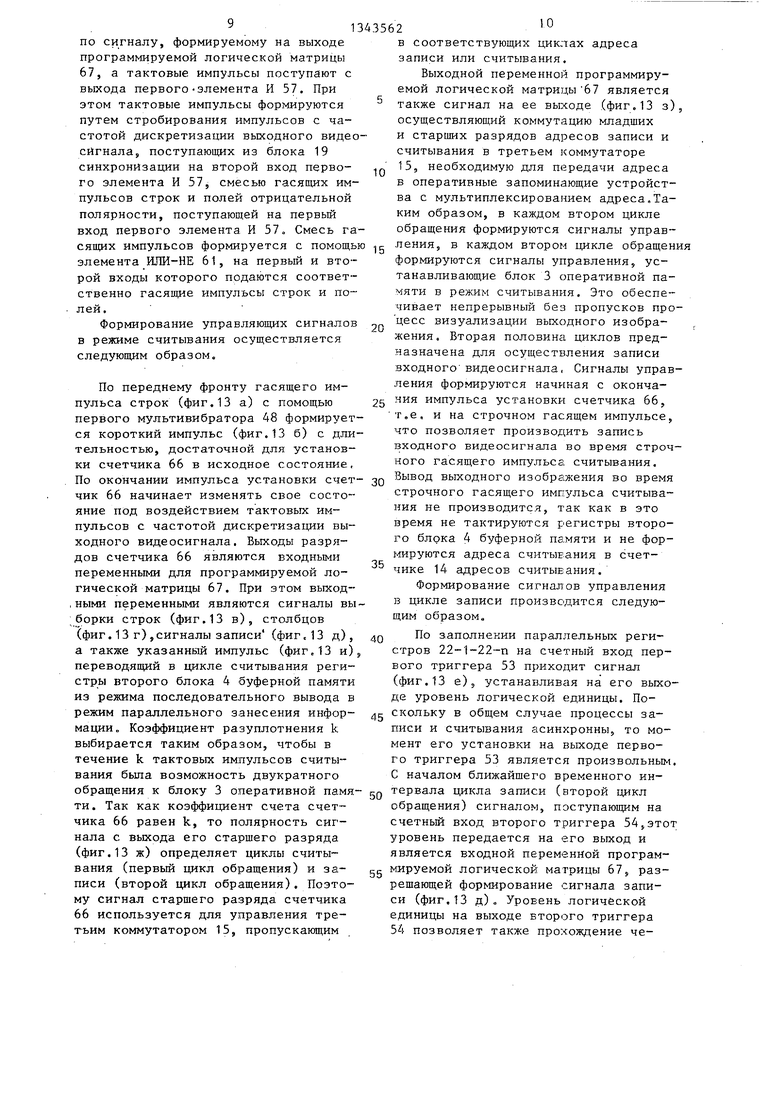

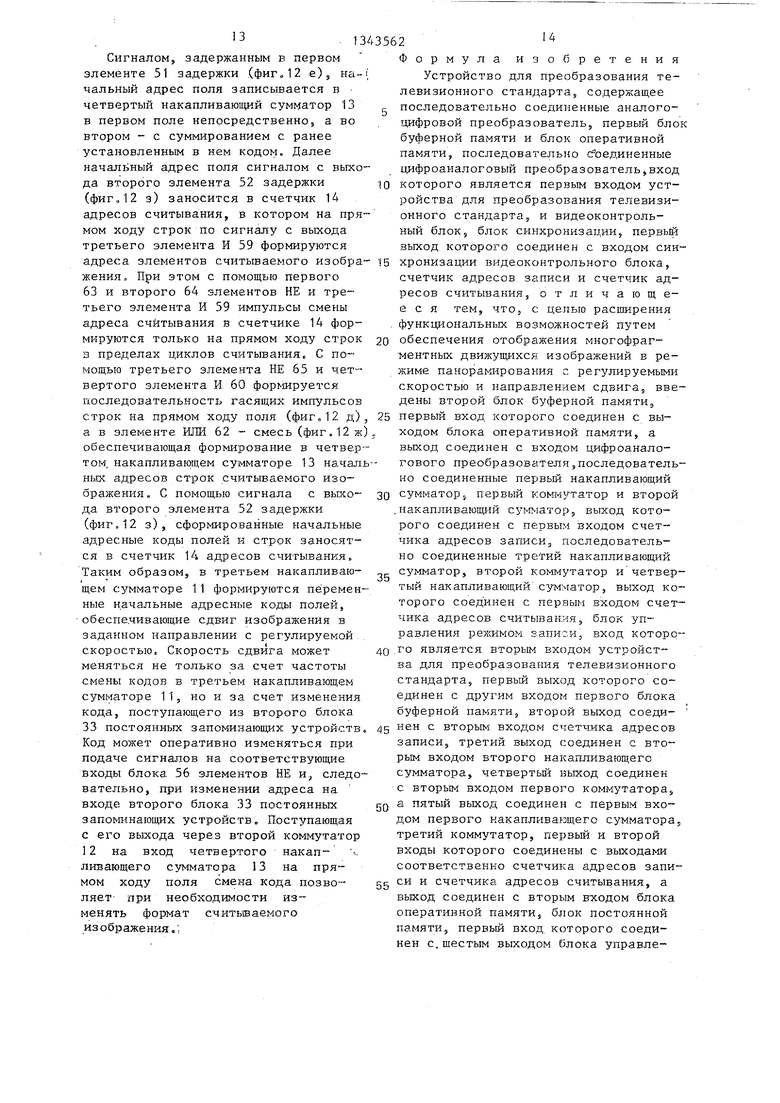

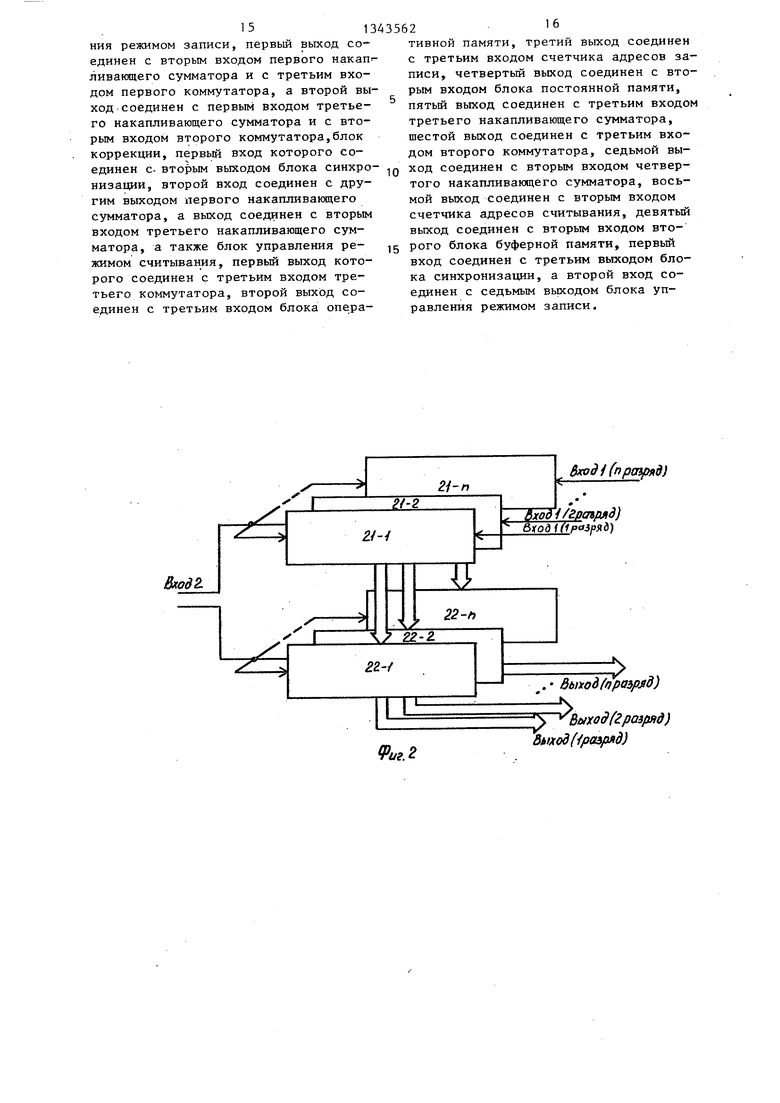

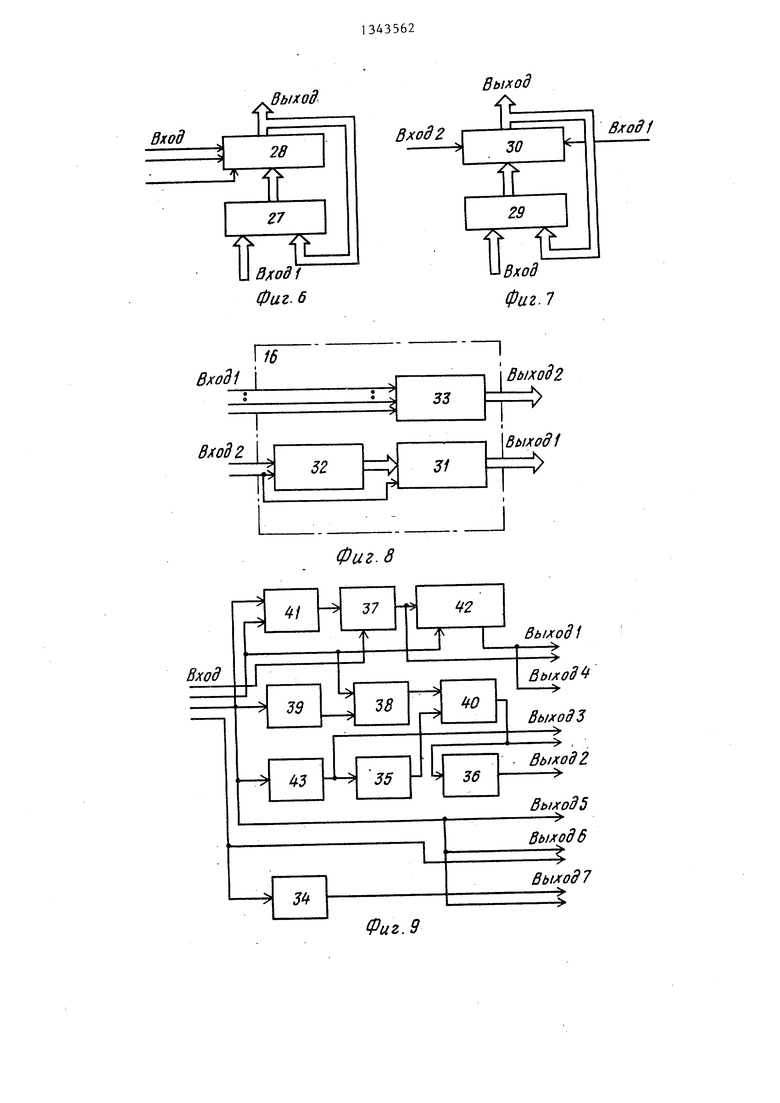

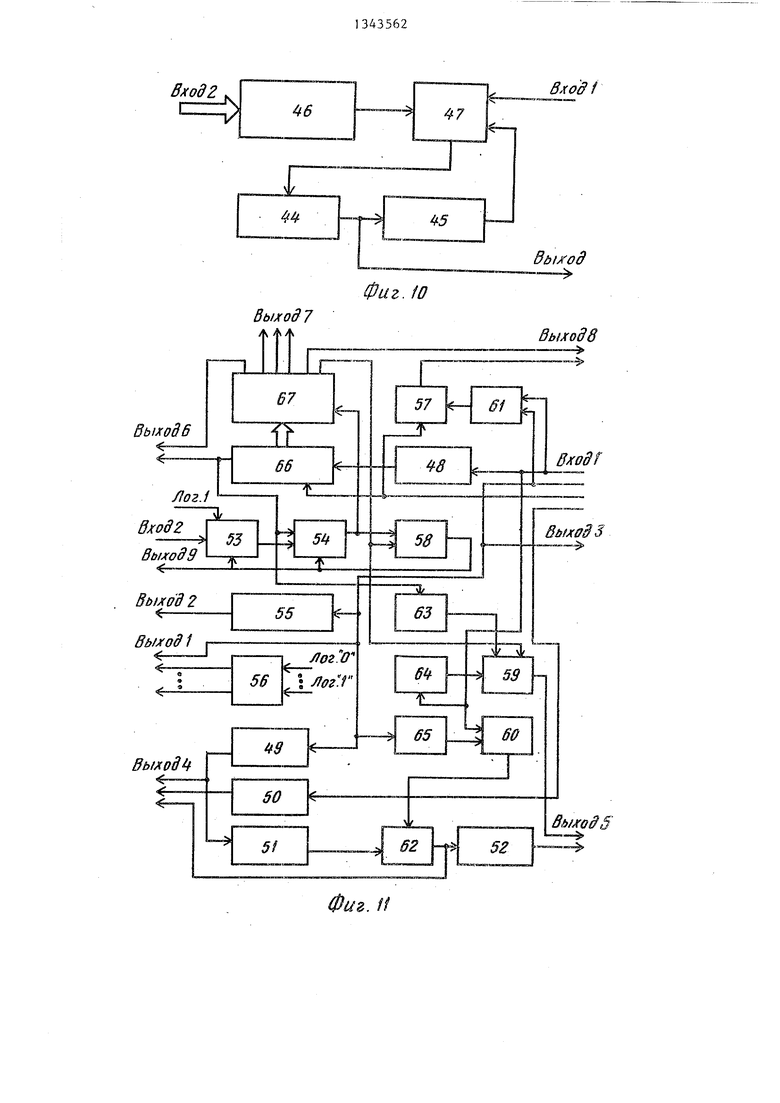

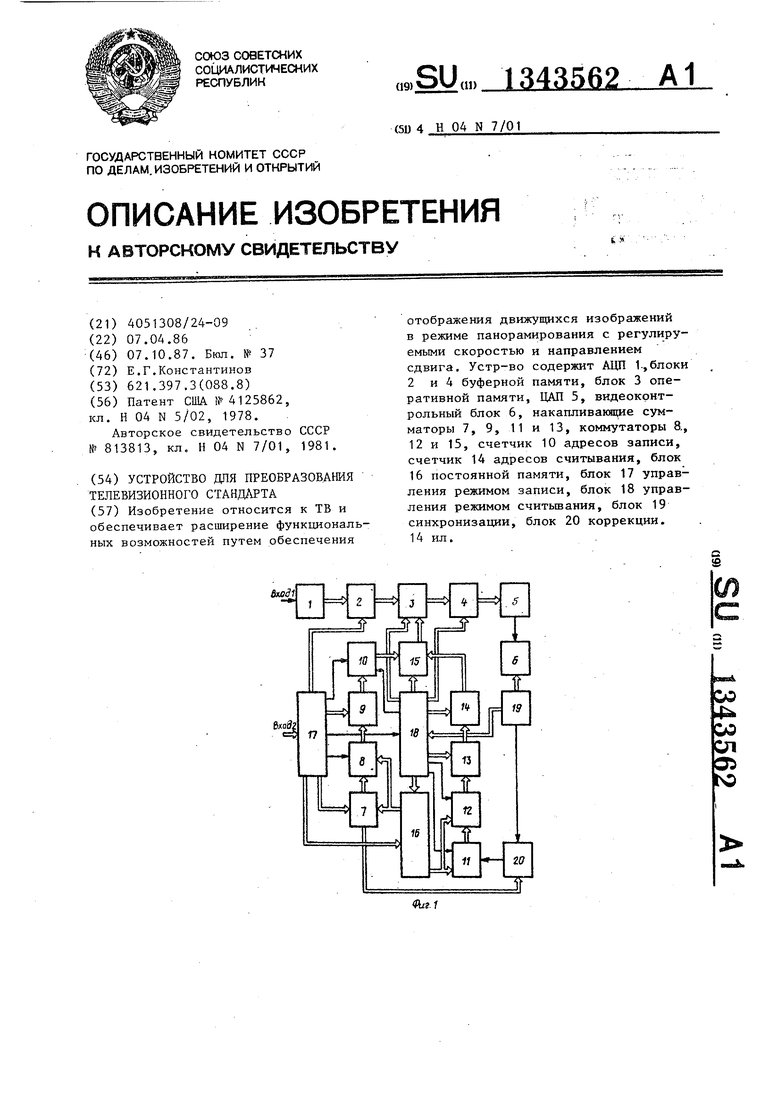

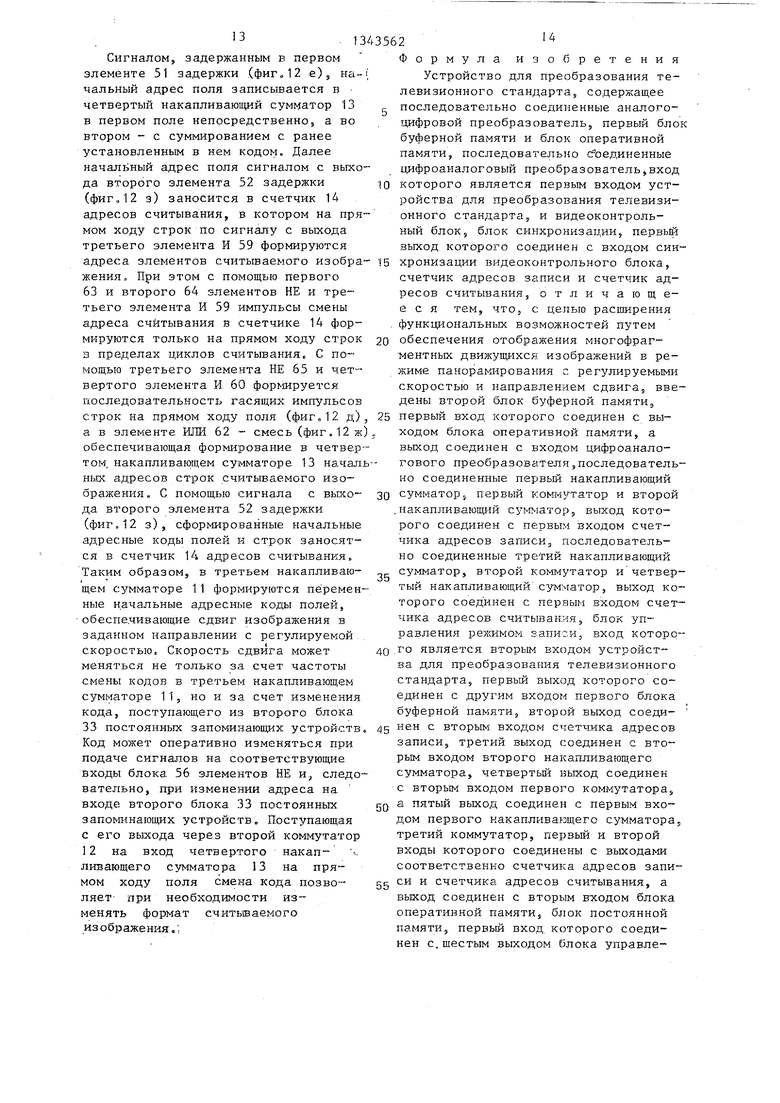

На фиг.1 представлена структурная13 (фиг.6) содержит сумматор 27 и электрическая схема устройства для15 параллельный регистр 28. преобразования телевизионного стан-Третий накапливаю1 1ий сумматор 1 1 дарта; на фиг.2 - схема первого бло--(фиг.7) содержит сумматор 29 и пака буферной памяти; на фиг.З - схе-раллельный регистр 30. ма блока оперативной памяти; наБлок 16 постоянной памяти (фиг.8) фиг.4 - схема блока оперативных за-20 содержит первый блок 31 постоянных поминающих устройств; на фиг.5 -запоминающих устройств, счетчик 32, схема первого и второго накапливаю-второй блок 33 постоянных запоминающих сумматоров; на фиг.6 схема чет- щих устройств.

вертого накапливающего сумматора; наБлок 17 управления режимом запифиг.7 - схема третьего накапливающе-25 си (фиг.9) содержит первый мультивибго сумматора; на фиг.8 - схема блокаратор 34, первый элемент 35 задержпостоянной памяти; на фиг.9 - схемаки, второй элемент 36 задержки, перблока управления режимом записи; навьй элемент И 37, второй элемент

фиг.10 - схема блока коррекции; наИ 38, элемент НЕ 39, элемент ИЛИ 40,

фиг.11 - схема блока управления ре-ЗО элемент ИЛИ-НЕ 41,счетчик 42, второй

жимом считывания; на фиг.12 - времен-мультивибратор 43.

ные диаграммы работы блока управленияБлок 20 коррекции (фиг.10) содеррежимом записи; на фиг.13 - временныежит первый мультивибратор 44,второй

диаграммы работы блока управления ре-мультивибратор 45, дешифратор 46,тригжимом считывания; на фиг.14 - струк-. гер 47.

тура участка многофрагментного изо-Блок 18 управления режимом считывабражения. .ния (фиг. 11) содержит первый 48, вто .. 49 и третий 50 мультивибраторы.

Устройство для преобразования те-.. m

левизионного стандарта (фиг.1) содер- второй 52 элемент задерж- жит аналого-цифровой преобразователь 0 и второй 54 триггеры, (АЦП) 1, первый блок 2 буферной памя- Р счетчик э5, блок :э6 элементов ти, блок 3 оперативной памяти, второй °P° 58, третий 59 блок 4 буферной памяти, цифро-анапо- четвертый 60 элементы И, элемент говый преобразователь (, видео- ™И-НЕ 61, элемент ИЛИ 62, первьй 63, контрольный блок 6, первый накаплива- °Р° 64 и третий 65 элементы НЕ, ющий сумматор 7, первьш коммутатор 8, второй счетчик 66, программируемую второй накапливающий сумматор 9, счет- логическую матрицу 67. чик 10 адресов записи, третий накап- Устройство для преобразования те- ливающий сумматор 11, второй коммута-- ви ионного стандарта работает елетор 12, четвертый накапливающий сум- ДУЮЩим о разом.

матор 13, счетчик 14 адресов считыва- Аналоговьй видеосигнал в соответ- ния, третий коммутатор 15, блок 16 ™ ° стандартом разложения вход- постоянной памяти, блок 17 управления изображения поступает на вход режимом записи, блок 18 управления ре- АЦП 1, в котором видеосигнал преоб- жимом считывания, блок 19 синхрониза- 55 Разуется в цифровую форму. С выхода ции, блок 20 KoppeKuiiH. цифровой видеосигнал поступает

на вход первого блока 2 буферной паПервьй блок 2 буферной памяти мяти, где производится его времен- (фиг.2) содержит последовательно-па- ное разуплотнение с целью обеспече 134

ния согласования сравнительно низких частот обращения к блоку 3 оперативной памяти с высокой частотой дискретизации входного видеосигнала. Разуплотненный видеосигнал с выхода первого блока 2 буферной памяти поступает на вход блока 3 оперативной памяти, где осуществляются его запись и

15

20

25

одКовреМенное считывание. Считываемый IQ те дискретизации входного видеосиг- видеосигнал с выхода блока 3 .опера- нала. Совокупность тактовых импуль- тивной памяти поступает на вход второго блока 4 буферной памяти, где осуществляется его временное уплотнение с целью формирования видеосигнала в соответствии с вещательным или близким к нему стандартом. С выхода второго блока 4 буферной памяти цифровой видеосигнал поступает на вход ЦАП 5, где преобразуется в аналоговую форму и поступает далее на видеовход видеоконтрольного блока 6 для визуализации изображения. Наличие в устройстве первого 2 и второго 4 блоков буферной памяти (на входе и выходе блока 3 оперативной памяти) позволяет осуществлять одновременно запись и считывание видеосигналов с различными стандартами разложения изображений, а также согласовать сравнительно низкие частоты обращения к блоку 3 оперативной памяти с высокими частотами дискретизации входного и выходного видеосигналов.

Запись видеосигнала входного стандарта разложения осуществляется следующим образом.

Отсчеты входного видеосигнала в виде п-разрядных слов (обычно п 8) поступают с выхода АЦП 1 на информационные входы последовательно-па- траллельных регистров 21-1-21-п. Разрядность последних и параллельных регистров 22-1-22-п выбирается равной разрядности параллельно-последовательных регистров второго блока 4 буферной памяти и выбирается из соотношения

30

35

40

45

в пределах прямых ходов строк фрагмента записываемого изображения,формируется с помощью первого элемента И 37,.на первый вход которого подается смесь гасящих импульсов строк и фрагментов записываемого изображения отрицательной полярности, а на второй вход первого элемента И 37 по ступает с входа блока 17 управления режимом записи непрерывная последовательность импульсов с частотой дис кретизации входного видеосигнала,при вязанных по фазе к строчным гасящим импульсам. Смесь гасящих импульсов строк и фрагментов формируется с помощью элемента ИЛИ-НЕ 41, на первый и второй входы которого подаются соответственно гасяпще импульсы фрагментов и строк положительной поляр- ро сти.

В момент полного заполнения последовательно-параллельных регистров 21-1-21-п их содержимое переписывается в параллельные регистры 22-1- -22-п,на тактовые входы которых подается сигнал перезаписи. Сигнал перезаписи поступает со старшего разряда счетчика 42. коэффициент счета которого соответствует разрядности регистров первого блока 2 буферной . памяти. Во время обратного хода стро записи счетчик 42 устанавливается в нулевое состояние подачей на его управляющий вход установки начального кода строчного гасящего импульса записи с входа блока 17 управления режимом записи. Во время прямого хода строк записи счетчик 42 изменяет сво состояние синхронно с заполнением по следовательно-параллельных регистров 21-1-21-п. Зафиксированные сигналом перезаписи в параллельных регистрах 22-1-22-п отсчеты .входного видеосигнала с информационных выходов параллельных регистров 22-1-22-п поступают на первые входы блоков 23-1-23-п

де

овр

2f.- ,

ОБр

-частота обращения к оперативным запоминающим устройствам блока 3 оперативной памяти;

-частота дискретизации считываемого видеосигнала.

Выполнение этого условия обеспечивает, возможность одновременной записи и считывания видеосигнала. Запись входных отсчетов видеосигнала в последовательно-параллельные регистры 21-1-21-п осуществляется по поступающим на их тактовые входы -импульсам, частота которых соответствует часто5

0

5

Q те дискретизации входного видеосиг- нала. Совокупность тактовых импуль-

0

5

0

5

0

5

в пределах прямых ходов строк фрагмента записываемого изображения,формируется с помощью первого элемента И 37,.на первый вход которого подается смесь гасящих импульсов строк и фрагментов записываемого изображения отрицательной полярности, а на второй вход первого элемента И 37 по- ступает с входа блока 17 управления режимом записи непрерывная последовательность импульсов с частотой дискретизации входного видеосигнала,привязанных по фазе к строчным гасящим импульсам. Смесь гасящих импульсов строк и фрагментов формируется с помощью элемента ИЛИ-НЕ 41, на первый и второй входы которого подаются соответственно гасяпще импульсы фрагментов и строк положительной поляр- ро сти.

В момент полного заполнения последовательно-параллельных регистров 21-1-21-п их содержимое переписывается в параллельные регистры 22-1- -22-п,на тактовые входы которых подается сигнал перезаписи. Сигнал перезаписи поступает со старшего разряда счетчика 42. коэффициент счета которого соответствует разрядности регистров первого блока 2 буферной . памяти. Во время обратного хода строк записи счетчик 42 устанавливается в нулевое состояние подачей на его уп равляющий вход установки начального кода строчного гасящего импульса записи с входа блока 17 управления режимом записи. Во время прямого хода строк записи счетчик 42 изменяет свое состояние синхронно с заполнением последовательно-параллельных регистров 21-1-21-п. Зафиксированные сигналом перезаписи в параллельных регистрах 22-1-22-п отсчеты .входного видеосигнала с информационных выходов параллельных регистров 22-1-22-п поступают на первые входы блоков 23-1-23-п

513

оперативных запоминающих устройств таким образом, что каждый из п разрядов входных отсчетов поступает в один . из п блоков 23-1-23-п. Таким образом каждый из бит, поступивших на вход блоков 23-1-23-п оперативных запоминающих устройств5 оказывается на входе одного из оперативных запоминающих устройств и удерживается там до окончания цикла записи по адресу записи, поступив1иему на их адресные входы через третий коммутатор 15 с информационных выходов разрдов счетчика 10 адресов записи.

Сигналом начала цикла записи служит с;игнал перезаписи, поступивший со старшего разряда счетчика 42 на счетный вход триггера 53, что приводит к формированию в соответствующем временном интервале сигналов выборки строкg столбцов и сигнала записи, .поступающих с выходов программируемо логической матрицы 67 на управляющие входы оперативных запоминающих устройств 24-1-24-k. По этим сигналам все слова данных записываются в .оперативные запоминаюпще устройства 24-1-24-k блоков 23-1-23-п оперативных запоминающих устройств. Аналогичные циклы записи осуществ.ляются всякий раз по заполнении последовательно-параллельных регистров 21-1-21-п и перезаписи их содержимого в параллельные регистры 22-1- -22-п по сигналу со старшего разряда счетчика 42.

Формирование адресных кодов записи, по которым производится запись отсчетов входного видеосигнала, осуществляется следующим образом.

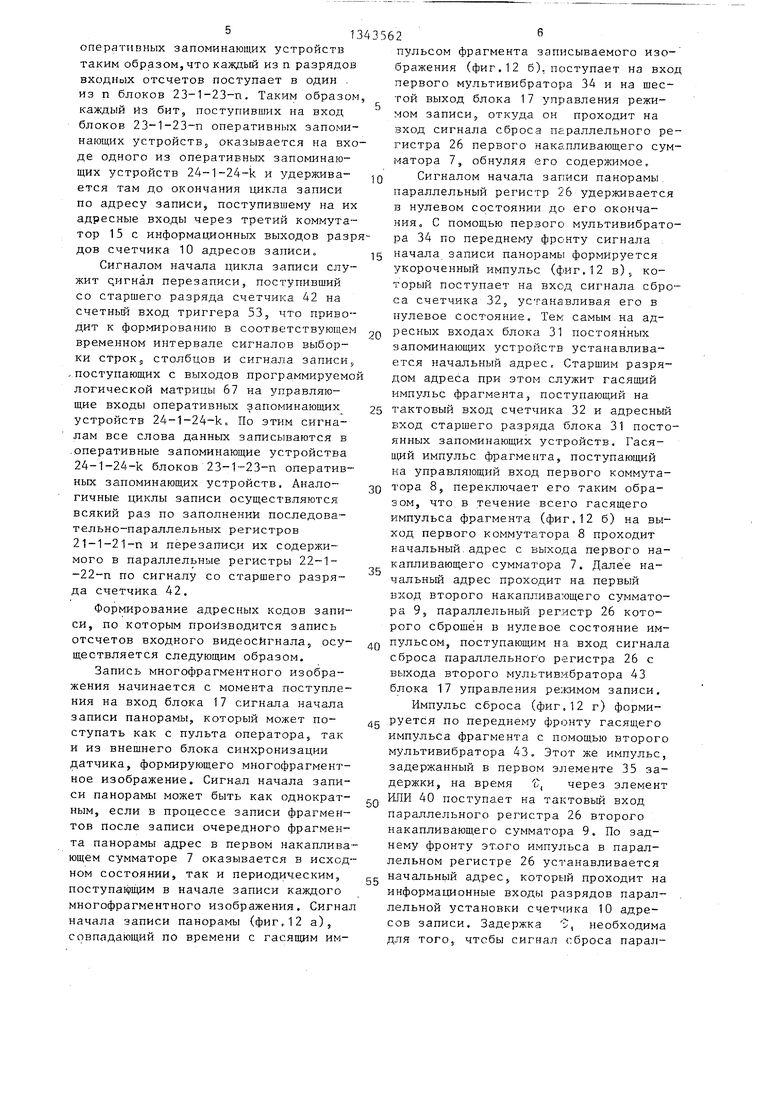

Запись многофрагментного изображения начинается с момента поступления на вход блока 17 сигнала начала записи панорамы, который может поступать как с пульта оператора, так и из внещнего блока синхронизации датчика, формирующего многофрагментное изображение. Сигнал начала записи панорамы может быть как однократным, если в процессе записи фрагментов после записи очередного фрагмента панорамы адрес в первом накапливающем сумматоре 7 оказывается в исходном состоянии, так и периодическим, поступа1фщим в начале записи каждого многофрагментного изображения. Сигнал начала записи панорамы (фиг,12 а), совпадающий по времени с гасящим им562

пульсом фрагмента записываемого изображения (фиг,12 б), поступает на вход первого мультивибратора 34 и на шестой выход блока 17 управления режимом записи, откуда он проходит на вход сигнала сброса параллельного регистра 26 первого накапливающего сумматора 7, обнуляя его содержимое,

Q Сигналом начала записи панорамы, параллельный регистр 26 удерживается в нулевом состоянии до его окончания. С помощью первого мультивибратора 34 по переднему фронту сигнала

5 начала записи панорамы формируется укороченный импульс (фиг.12 в), который поступает на вход сигнала сброса счетчика 32, устанавливая его в нулевое состояние. Тек самым на адQ ресных входах блока 31 постоянных запоминающих устройств устанавливается начальный адрес. Старшим разрядом адреса при этом служит гасяощй импульс фрагмента, поступающий на

5 тактовый вход счетчика 32 и адресный вход старшего разряда блока 31 постоянных запоминающих устройств. Гасящий импульс фрагмента, поступающий на управляющий вход первого коммута0 тора 8, переключает его таким образом, что в течение всего гасящего импульса фрагмента (фиг.12 б) на выход первого коммутатора 8 проходит начальный.адрес с выхода первого накапливающего сумматора 7. Далее на- чальньй адрес проходит на первый вход второго накапливающего сумматора 9, параллельный регистр 26 которого сброшен в нулевое состояние имQ пульсом, поступающим на вход сигнала сброса параллельного регистра 26 с выхода второго мультивибратора 43 блока 17 управления ре;кимом записи. Импульс сброса (фиг,12 г) форми5 руется по переднему фронту гасящего импульса фрагмента с помощью второго мультивибратора 43. Этот же импульс, задержанный в первом элементе 35 задержки, на время (х, через элемент

Q И.ПИ 40 поступает на тактовый вход параллельного регистра 26 второго накапливающего суммато.ра 9, По заднему фронту этого импульса в параллельном регистре 26 устанавливается

g начальный адрес, который проходит на информационные входы разрядов параллельной установки счетчика 10 адресов записи. Задержка , необходима для того, чтобы сигнал сброса парал5

7

лельного регистра 26 снять раньше, чем поступит задний фронт импульса установки в параллельный регистр 26 начального адреса. Задержанный далее во втором элементе 36 задержки на же сигнал устанавливает наадрес в счетчик 10 адресов

необходима для

чальныи

записи. Задержка

компенсации задержки начального адреса кода -во втором накапливающем сумматоре 9, Таким образом,начальный адресный код первого фрагмента панорамы (фиг.14) устанавливается в счетчике 10 адресов записи.Далее на прямом ходу строки сигналом, поступающим на тактовый вход счетчика 10 адресов записи., его содержимое увеличивается кажд.ый раз на единицу формируя тем самым адреса элементов записываемого изображения вдоль строки.

По окончании гасящего импульса фрагмента по его заднему фронту увеличивается на единицу состояние счетчика 32, формируя новый адрес для блока 31 постоянных запоминающих устройств. На старшем адресном разряде последнего по окончании гасящего импульса фрагмента меняется полярность сигнала и на его выходе формируется код числа, представляющего собой разность между начальными адресами двух соседних строк фрагмента изображения. Это код через переключившийся по окончанию гасящего импульса фрагмента изображения первый коммутатор 8 поступает на первый вход второго накапливающего сумматора 9 и удерживается там в течение прямого хода фрагмента записываемого изображения по задним фронтам гасящих импульсов строк (фиг.12 д), замешанных в элементе ИЛИ 40 с импульсами (фиг.12 е), содержимое второго накапливающего сумматора 9 увеличивается сигналом с выхода элемента ИЛИ 40 (фиг,12 ж) -на величину, равную выбранной разности между начальными адресными кодами строк. Таким образом, во втором накапливающем сумматоре 9 на прямом ходу фрагмента формируются начальные адресные коды строк записываемого фрагмента изображения (фиг,14), которые передаются в счетчик 10 адресов записи сигналом с выхода второго элемента 36 задержки (фиг.12 з).

С приходом следующего гасящего импульса фрагмента изображения процесс

т10

20

25

343562 передачи начального адресного кода

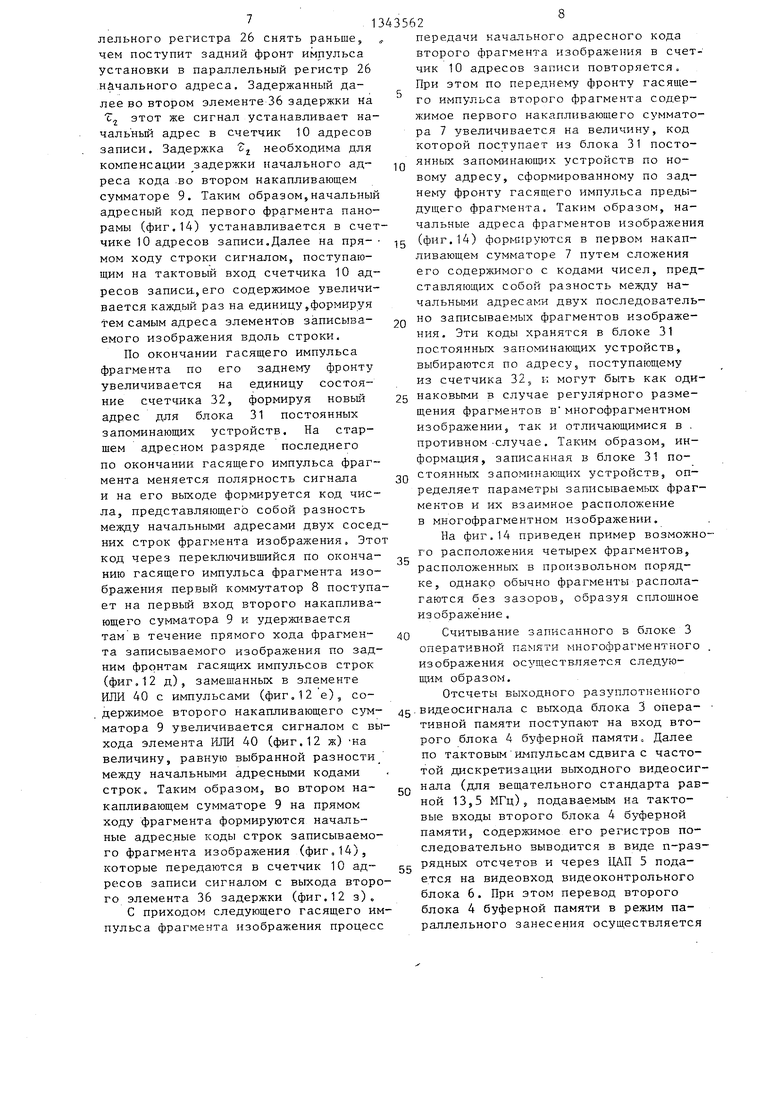

второго фрагмента изображения в счетчик 10 адресов записи повторяется. При этом по переднему фронту гасящего импульса второго фрагмента содержимое первого накапливаюп1его сумматора 7 увеличивается на величину, код которой поступает из блока 31 постоянных запоминающих устройств по новому адресу, сформированному по зад- Hehry фронту гасящего импульса предыдущего фрагмента. Таким образом, начальные адреса фрагментов изображения 15 (фиг.14) формируются в первом накапливающем сумматоре 7 путем сложения его содержимого с кодами чисел, представляющих собой разность между на- чальньми адресами двух последовательно записываемых фрагментов изображения. Эти коды хранятся в блоке 31 постоянных запоминающих устройств, выбираются по адресу, поступающему из счетчика 32, и могут быть как одинаковыми в случае регулярного размещения фрагментов в многофрагментном изображении, так и отличающимися в , противном-случае. Таким образом, информация, записанная в блоке 31 постоянных запоминающих устройств, определяет параметры записываемых фрагментов и их взаимное расположение в многофрагментном изображении.

На фиг.14 приведен пример возможного расположения четырех фрагментов, расположенных в произвольном порядке, однако обычно фрагменты располагаются без зазоров, образуя сплошное изображе ние,

Считывание записанного в блоке 3 оперативной памяти многофрагментного . изображения осз ществ-пяется следую- образом.

Отсчеты выходного разуплотненного видеосигнала с выхода блока 3 опера- тивной памяти поступают на вход второго блока 4 буферной памяти с Далее по тактовым импульсам сдвига с частотой дискретизации выходного видеосигнала (для вещательного стандарта равной 13,5 МГц)5 подаваемым на тактовые входы второго блока 4 буферной памяти, содержимое его регистров последовательно выводится в виде п-раз- рядных отсчетов и через ЦА.П 5 подается на видеовход видеоконтрольного блока 6. При этом перевод второго блока 4 буферной памяти в режим параллельного занесения осуществляется

30

35

40

45

50

55

по сигналу, формируемому на выходе программируемой логической матрицы 67, а тактовые импульсы поступают с выхода первого-элемента И 57. При этом тактовые импульсы формируются путем стробирования импульсов с частотой дискретизации выходного видеосигнала, поступающих из блока 19 синхронизации на второй вход первого элемента И 57, смесью гасящих импульсов строк и полей отрицательной полярности, поступающей на первый вход первого элемента И 57 Смесь га10

в соответствующих циклах адреса записи или считывания.

Выходной переменной программируемой логической матрицы 67 является также сигнал на ее выходе (фиг.13 з), осуществляющий коммутацию младших и старших разрядов адресов записи и считывания в третьем коммутаторе 15, необходимую для передачи адреса в оперативные запоминающие устройства с мультиплексированием адреса.Таким образом, в каждом втором цикле обращения формируются сигналы управсящих импульсов формируется с помощью д ления, в каждом втором цикле обращения

элемента ИЛИ-НЕ 61, на первый и второй входы которого подаются соответственно гасящие импульсы строк и по- . лей.

Формирование управляющих сигналов в режиме считывания осуществляется следуюпщм образом.

По переднему фронту гасящего импульса строк (фиг,13 а) с помощью первого мультивибратора 48 формируется короткий импульс (фиг.13 б) с длительностью, достаточной для установки счетчика 66 в исходное состояние, По окончании импульса установки счетчик 66 начинает изменять свое состояние под воздействием тактовых импульсов с частотой дискретизации выходного видеосигнала. Выходы разрядов счетчика 66 являются входными переменными для программируемой логической матрицы 67. При этом выход- ,ными переменными являются сигналы вы- ;борки строк (фиг.13 в), столбцов (фиг. 13 г),сигналы записи (фиг, 13 д) , а также указанный импульс (фиг.13 и), переводящий в цикле считывания регистры второго блока 4 буферной памяти из режима последовательного вывода в режим параллельного занесения информации. Коэффициент разуплотнения k выбирается таким образом, чтобы в течение k тактовых импульсов считывания была возможность двукратного обращения к блоку 3 оперативной памяти. Так как коэффициент счета счетчика 66 равен k, то полярность сигнала с выхода его старшего разряда (фиг.13 ж) определяет циклы считывания (первый цикл обращения) и записи (второй цикл обращения), Поэтому сигнал старшего разряда счетчика 66 используется для управления третьим коммутатором 15, пропускающим

20

25

30

35

формируются сигналы управления, устанавливающие блок 3 оперативной памяти в режим считывания. Это обеспечивает непрерывный без пропусков процесс визуализации выходного изображения. Вторая половина циклов предназначена для осуществления записи ВХОДНОГО видеосигнала, Сигналы управления формируются начиная с окончания импульса установки счетчика 66, т.е. и на строчном гасящем импульсе, что позволяет производить запись входного видеосигнала во время строчного гасящего импульса считывания. Вывод выходного изображения во время строчного гасящего импульса считывания не производится, так как в это время не тактируются регистры второго блока 4 буферной па.мяти и не формируются адреса считывания в счетчике 14 адресов считывания.

Формирование сигналов управления в цикле записи производится следующим образом.

По з.аполнении параллельных регистров 22-1-22-п на счетный вход первого триггера 53 приходит сигнал (фиг.13 е)5 устанавливая на его выходе уровень логической единицы. По45 скольку в общем слз чае процессы записи и считывания асинхронны, то момент его установки на выходе первого триггера 53 является произвольным. С началом ближайшего временного интервала цикла записи (второй цикл обращения) сигналом, поступающим на счетньй вход второго триггера 54,этот уровень передается на его выход и является входной переменной програмgg мируемой логической матрицы 67, разрешающей формирование сигнала записи (фиг.13 д)„ Уровень логической единицы на выходе второго триггера 54 позволяет также прохождение че40

50

в соответствующих циклах адреса записи или считывания.

Выходной переменной программируемой логической матрицы 67 является также сигнал на ее выходе (фиг.13 з), осуществляющий коммутацию младших и старших разрядов адресов записи и считывания в третьем коммутаторе 15, необходимую для передачи адреса в оперативные запоминающие устройства с мультиплексированием адреса.Таким образом, в каждом втором цикле обращения формируются сигналы управд ления, в каждом втором цикле обращения

0

5

0

5

формируются сигналы управления, устанавливающие блок 3 оперативной памяти в режим считывания. Это обеспечивает непрерывный без пропусков процесс визуализации выходного изображения. Вторая половина циклов предназначена для осуществления записи ВХОДНОГО видеосигнала, Сигналы управления формируются начиная с окончания импульса установки счетчика 66, т.е. и на строчном гасящем импульсе, что позволяет производить запись входного видеосигнала во время строчного гасящего импульса считывания. Вывод выходного изображения во время строчного гасящего импульса считывания не производится, так как в это время не тактируются регистры второго блока 4 буферной па.мяти и не формируются адреса считывания в счетчике 14 адресов считывания.

Формирование сигналов управления в цикле записи производится следующим образом.

По з.аполнении параллельных регистров 22-1-22-п на счетный вход первого триггера 53 приходит сигнал (фиг.13 е)5 устанавливая на его выходе уровень логической единицы. По5 скольку в общем слз чае процессы записи и считывания асинхронны, то момент его установки на выходе первого триггера 53 является произвольным. С началом ближайшего временного интервала цикла записи (второй цикл обращения) сигналом, поступающим на счетньй вход второго триггера 54,этот уровень передается на его выход и является входной переменной програмg мируемой логической матрицы 67, разрешающей формирование сигнала записи (фиг.13 д)„ Уровень логической единицы на выходе второго триггера 54 позволяет также прохождение че0

0

ч134356212

импульса, рас- правление сдвига изображения на эк10

15

20

рез второй элемент И 58 положенного в конце каждого цикла обращения (фиг.13 к) и формируемого программируемой логической матрицей 67. Импульсом с выхода второго эле- . мента И 58 (фиг.13 л) первый 53 и второй 54 триггеры обнуляются и устройство вновь готово к повторению цикла записи.

Формирование адресных кодов считывания осуществялется следующим образом.

С приходом начала записи панорамы начальный адрес панорамы с второго выхода первого накапливающего сумматора 7 поступает на информационные входы разрядов дешифратора 46, дешифрирующего этот адрес. В результате на входе триггера 47 появляется уровень логической единицы, который с приходом гасящего импульса полей на счетныц вход триггера 47 передается на его выход. По положительному перепаду с помощью первого мультивиб- 25 ратора 44 формируется импульс, по заднему фронту которого с помощью второго мультивибратора 45 формируется второй импульс, возвращающий триггер 47 в исходное состояние с уровнем логического нуля на выходе. Им- /пульс с выхода первого мультивибратора 44 поступает на вход сброса регистра 30, устанавливая в нем такой код, который обеспечивает запись фрагментов в ту часть адресного пространства блока 3 оперативной памяти, которая в данный момент не отображается на экране видеоконтрольного блока 6. Установка регистра 30 во время гасящего импульса полей исключает возможные помехи, заметные на экране видеоконтрольного блока 6. В дальнейшем установка регистра 30 производится лишь в те моменты, KOI- да на втором выходе первого накапливающего сумматора 7 начальный код записи панорамы. В остальном процесс формирования адресных кодов считывания аналогичен формированию адресов записи.

С приходом гасящего импульса поля (фиг,12 б) на выходе второго блока 33 постоянных запоминающих устройств устанавливается код числа, представляющего собой разность между начальными адресными кодами двух последовательно считываемых полей. Величина этой разности определяет шаг и на30

ране видеоконтрольного блока 6,Прибавление этого кода к содержимому третьего накапливающего сумматора 11 производится по сигналу, формируемому на выходе старшего разряда первого счетчика 55, на вход которого поступают гасящие импульсы полей. В зависимости от установленного коэффициента счета первого счетчика 55 изменение содержимого третьего накапливающего сумматора 11 происходит в каждом поле, через поле или через несколько полей. Тем самым изменяется скорость сдвига изображения. Сфор мированный в третьем накапливающем сумматоре 11 переменный начальный ад рес поля через переключенный гасящим импульсом поля второй коммутатор 12 поступает на первый вход четвертого накапливающего сумматора 13.

В исходное состояние параллельный регистр 28 четвертого накапливаю щего сумматора 13 приводится двумя сигналами. На вход сброса в нуль поступает короткий импульс (фиг.20 г) С выхода второго мультивибратора 49, сформированный по переднему фронту

гасящего импульса полей. На вход ус- 1

тановки в состояние логической едини цы соответствующих разрядов параллельного регистра 28 подается импульс сформированньй с помощью третьего мультивибратора 50 из сигнала опознавания полей, поступающего из блока 19 синхронизации и представляющег собой сигнал скважности равной двум, имеющий отрицательную полярность в первом поле и положительную во втором поле считываемого кадра изобра- .жения, причем переключение сигнала опознавания полей осуществляется синфазно с гасящими импульсами полей 45 Таким образом, поскольку длительност импульса с выхода третьего мультивиб ратора 50 несколько превышает длительность импульса с выхода второго мультивибратора 49, параллельный регистр 28 обнуляется в первом поле, а во втором поле в нем устанавливается код числа, представляющего собой разность между начальными адресами двух смежных строк, В результате обеспечивается необходимьм сдвиг в адресах на одну строку, требующийся при чересстрочной развертке вещательного стандарта..

35

40

50

55

0

5

0

5

0

ране видеоконтрольного блока 6,Прибавление этого кода к содержимому третьего накапливающего сумматора 11 производится по сигналу, формируемому на выходе старшего разряда первого счетчика 55, на вход которого поступают гасящие импульсы полей. В зависимости от установленного коэффициента счета первого счетчика 55 изменение содержимого третьего накапливающего сумматора 11 происходит в каждом поле, через поле или через несколько полей. Тем самым изменяется скорость сдвига изображения. Сформированный в третьем накапливающем сумматоре 11 переменный начальный адрес поля через переключенный гасящим импульсом поля второй коммутатор 12 поступает на первый вход четвертого накапливающего сумматора 13.

В исходное состояние параллельный регистр 28 четвертого накапливающего сумматора 13 приводится двумя сигналами. На вход сброса в нуль поступает короткий импульс (фиг.20 г) С выхода второго мультивибратора 49, сформированный по переднему фронту

гасящего импульса полей. На вход ус- 1

тановки в состояние логической единицы соответствующих разрядов параллельного регистра 28 подается импульс, сформированньй с помощью третьего мультивибратора 50 из сигнала опознавания полей, поступающего из блока 19 синхронизации и представляющего собой сигнал скважности равной двум, имеющий отрицательную полярность в первом поле и положительную во втором поле считываемого кадра изобра- .жения, причем переключение сигнала опознавания полей осуществляется синфазно с гасящими импульсами полей, 5 Таким образом, поскольку длительность импульса с выхода третьего мультивибратора 50 несколько превышает длительность импульса с выхода второго мультивибратора 49, параллельный регистр 28 обнуляется в первом поле, а во втором поле в нем устанавливается код числа, представляющего собой разность между начальными адресами двух смежных строк, В результате обеспечивается необходимьм сдвиг в адресах на одну строку, требующийся при чересстрочной развертке вещательного стандарта..

5

0

0

5

13 Сигналом, задержанным в первом

13

элементе 51 задержки (фиг.12 е), начальный адрес поля записывается в четвертый накапливающий сумматор 13 в первом поле непосредственно, а во втором - с суммированием с ранее установленным в нем кодом. Далее начальный адрес поля сигналом с выхода второго элемента 52 задержки (фиг„12 з) заносится в счетчик 14 адресов считывания, в котором на прямом ходу строк по сигналу с выхода третьего элемента И 59 формируются адреса элементов считываемого изображения. При этом с помощью первого 63 и второго 64 элементов НЕ и третьего элемента И 59 импульсы смены адреса считывания в счетчике 14 формируются только на прямом ходу строк 3 пределах циклов считывания С помощью третьего элемента НЕ 65 и четвертого элемента И 60 формируется последовательность гасящих импульсов строк на прямом ходу поля (фиг,12 д) а в элементе ИЛИ 62 смесь (фиг. 12 ж обеспечивающая формирование в четвертом, накапливающем сумматоре 13 начал ных адресов строк считываемого изображения „ С помощью сигнала с выхода второго элемента 52 задержки (фиг,12 з), сформированные начальные адресные коды полей и строк заносятся в счетчик 14 адресов считывания. Таким образом, в третьем накапливающем сумматоре 11 формируются переменные начальные адресные коды полей, обеспечивающие сдвиг изображения в зада1- ном направлении с регулируемой скоростью. Скорость сдвига может меняться не только за счет частоты смены кодов в третьем накапливающем сумматоре 11, но и за счет изменения кода, поступающего из второго блока 33 постоянных запоминающих устройств Код может оперативно изменяться при подаче сигналов на соответствующие входы блока 56 элементов НЕ и., следовательно, при изменении адреса на входе второго блока 33 постоянных зaпo шнaющиx устройств. Поступающая с его выхода через второй коммутатор 12 на вход четвертого накапливающего сумматора 13 на прямом ходу поля смена кода позволяет при необходимости изменять формат считьшаемого изображения,;

343562

Ф о

14

Ш

15

20

i ояакв), 25 ж), рь--ен, я в. ор

рмула изобретения Устройство для преобразования телевизионного стандарта, содержащее последовательно соединенные аналого- цифровой преобразователь, первый блок буферной памяти и блок оперативной памяти, последовательно с±1единенные цифроаналоговый преобразователь,вход которого является первым входом устройства для преобразования телевизионного стандарта, и видеоконтрольный блок, блок синхронизации, первый выход которого соединен с входом синхронизации видеоконтрольного блока, счетчик адресов записи и счетчик адресов считывания, отличающееся тем, что, с целью расширения функциональных возможностей путем обеспечения отображения многофрагментных движущихся изображений в режиме панорамирования с регулируемыми скоростью и направлением сдвига, введены второй блок буферной памяти, первый вход которого соединен с выходом блока оперативной памяти, а выход соединен с входом цифроанало- гового преобразователя,последовательно соединенные первый накапливающий сумматор 5 первый коммутатор и второй накапливающий сумматор, выход которого соединен с первым входом счетчика адресов записи, последовательно соединеннЕ)1е третий накапливающий сумматор, второй коммутатор и четвертый накапливающий сумматор, выход которого соединен с первым входом счетчика адресов считывания, блок управления режимом записи, вход которого является вторым входом устройства для преобразования телевизионного стандарта, первый выход которого соединен с другим входом первого блока буферной памяти, второй выход соеди- 45 нен с вторым входом с -гетчика адресов записи, третий выход соединен с вторым входом второго накапливающего сумматора, четвертый выход соединен с вторым входом первого коммутатора, а пятый выход соединен с первым входом первого накапливающего сумматора, третий коммутатор, первьй и второй входы которого соединены с выходами соответственно счетчика адресов записи и счетчика адресов считывания, а выход соединен с вторым входом блока оперативной памятИ; блок постоянной памяти, первый вход, которого соединен с. шестым выходом блока управле30

35

40

50

55

15

ния режимом записи, первый выход соединен с вторым входом первого накапливающего сумматора и с третьим входом первого коммутатора, а второй выход соединен с первым входом третьего накапливающего сумматора и с вторым входом второго коммутатора,блок коррекции, первый вход которого соединен с- вторым выходом блока синхро- Q ход соединен с вторым входом четвернизации, второй вход соединен с другим выходом первого накапливающего сумматора, а выход соединен с вторым входом третьего накапливающего сумматора, а также блок управления режимом считывания, первый выход которого соединен с третьим входом третьего коммутатора, второй выход соединен с третьим входом блока оператого накапливающего сумматора, восьмой выход соединен с вторым входом счетчика адресов считывания, девятый выход соединен с вторым входом вто- 5 рого блока буферной памяти, первый вход соединен с третьим выходом блока синхронизации, а второй вход соединен с седьмым вькодом блока управления режимом записи.

.

.

16

третий

тивнои памяти, третий выход соединен с третьим входом счетчика адресов записи, четвертый выход соединен с вторым входом блока постоянной памяти, пятый выход соединен с третьим входом третьего накапливающего сумматора, шестой выход соединен с третьим входом второго коммутатора, седьмой вытого накапливающего сумматора, восьмой выход соединен с вторым входом счетчика адресов считывания, девятый выход соединен с вторым входом вто- рого блока буферной памяти, первый вход соединен с третьим выходом блока синхронизации, а второй вход соединен с седьмым вькодом блока управления режимом записи.

21-п

Вход i fn разряд)

f 2

/-/

f 6xod1(2ptnfa3)

5код1(1разряд)

и

22-h

7 22-2.

:

. Bbiwdfnpabp d)

Bыxo fгразряд)

Skixodf pcoflAd)

Вход/ff) разряд)

I

0xo3ff3fla3osg)

Bxadi (1рС131мШ

Вход2

выжод (3pa$fi d)

Выуод (разряд)

ВыУйдНров/злд)

BjfodS

дхоёг

Suxod (

ff/od2

Г

Bxodi

Bbixodi

Jb

Zd

11

ва1ход2

ь

1

Фиг. 8

Фиг.В

Вход г к

45

Выход 7

Фаг. //

7

Фиг.Ш

--

Выходе

-™

Пербый qjpQZMeHm

третий фрагмент fernffeprnbJu

Редактор И.Шулла

Составитель Э.Борисов

Техред М.ДиЦык Корректор М.Демчик

Заказ 4837/57 Тираж 638Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб,, д.4/5

Производственно-полиграфическое предприятие, г.Ужгород, ул.Проектная,4

второй сррагпёнт

Фиг 11

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для преобразования малокадрового телевизионного стандарта | 1985 |

|

SU1256245A1 |

| Устройство компенсации сигнала дефектов киноленты | 1987 |

|

SU1494247A1 |

| Устройство компенсации сигнала царапин кинопленки | 1986 |

|

SU1392635A1 |

| Преобразователь телевизионного стандарта | 1980 |

|

SU1238267A1 |

| Устройство компенсации сигнала царапин кинопленки | 1988 |

|

SU1536521A2 |

| ДИСПЛЕЙ | 1990 |

|

RU2015536C1 |

| Преобразователь телевизионных стандартов | 1987 |

|

SU1506591A1 |

| УСТРОЙСТВО ИЗМЕРЕНИЯ ПАРАМЕТРОВ ТЕЛЕВИЗИОННЫХ ОПТИЧЕСКИХ СИСТЕМ | 1991 |

|

RU2010448C1 |

| Устройство для отображения радиолокационной информации на экране электронно-лучевой трубки | 1989 |

|

SU1691880A1 |

| Устройство для отображения информации на экране цветного видеоконтрольного блока | 1988 |

|

SU1529280A1 |

Изобретение относится к ТВ и обеспечивает расширение функциональных возможностей путем обеспечения отображения движущихся изображений в режиме панорамирования с регулируемыми скоростью и направлением сдвига. Устр-во содержит АЦП 1.,блоки 2 и 4 буферной памяти, блок 3 оперативной памяти, ЦАП 5, видеокрнт- рольный блок 6, накапливагацие сумматоры 7, 9, 11 и 13, коммутаторы 8,, 12 и 15, счетчик 10 адресов записи, счетчик 14 адресов считывания, блок 16 постоянной памяти, блок 17 управления режимом записи, блок 18 управления режимом считьшания, блок 19 синхронизации, блок 20 коррекции. 14 ил. с ел

| Патент США №4125862, кл | |||

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Устройство для преобразования теле-ВизиОННОгО СТАНдАРТА | 1979 |

|

SU813813A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1987-10-07—Публикация

1986-04-07—Подача