113

Изобретение относится к вычислительной технике и может быть использовано в высокоточных системах автоматического регулирования скорости или положения исполнительных, механизмов с упругой кинематической связью и фазовыми датчиками положения.

Цель изобретения - повышение надежности устройства за счет упрощения его схемы.

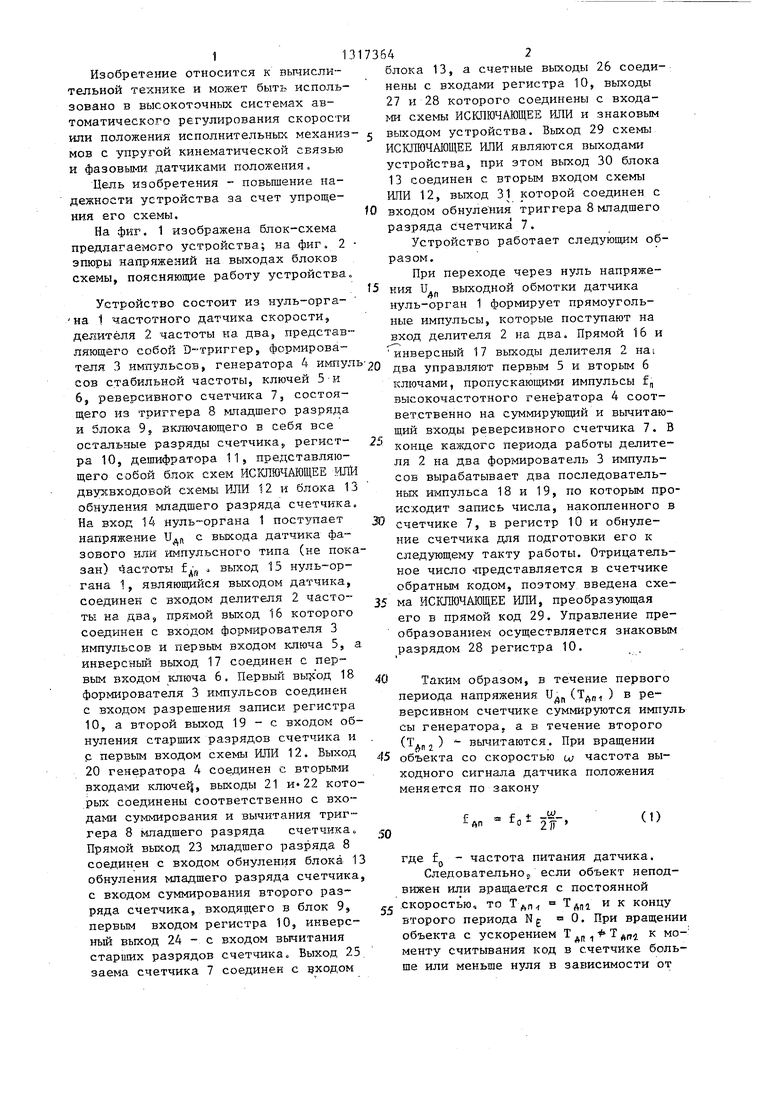

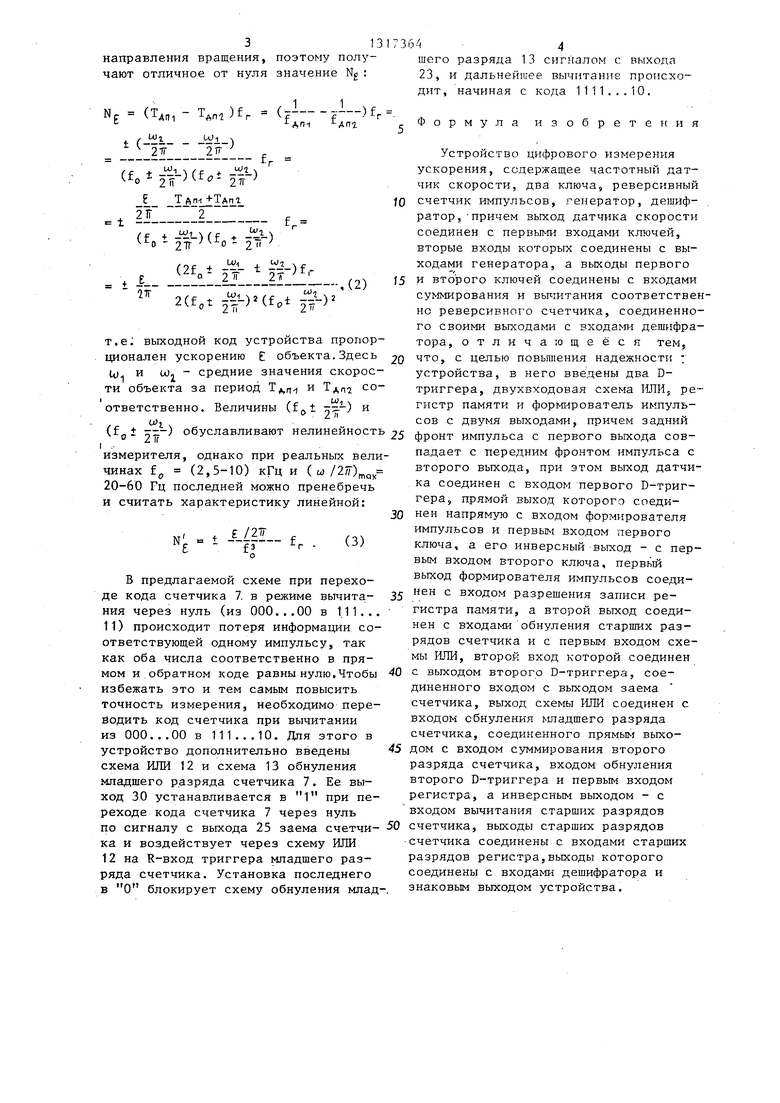

На фиг. 1 изображена блок-схема предлагаемого устройства; на фиг. 2 эгаоры напряжений на выходах блоков схемы, поясняющие работу устройства

Устройство состоит из нуль-орга- на 1 частотного датчика скорости, делителя 2 частоты на два, представляющего собой В-триггер} формирователя 3 импульсов, генератора k импуль сов стабильной частоты, ключей 5-и 6, реверсивного счетчика 7, состоящего из триггера 8 младшего разряда и блока 9. включающего в себя все остальные разряды счетчика регистра 10, дешифратора 11, представляющего собой блок схем ИСКШО ШОЩЕЕ ВДИ двухвкодовой схемы ИЛИ 12 и блока 13 обнуления младшего разряда счетчика. На вход 14 нуль-органа 1 поступает напряжение , с выхода датчика фазового или импульсного типа (не показан) астоты . выход 15 нуль-органа 1, являющийся выходом датчика, соединен с входом делителя 2 частоты на два, прямой вькод 16 которого соединен с входом формирователя 3 импульсов и первым входом ключа 5, а инверсньш выход, 17 соединен с первым входом ключа 6, Первый вьцсод 18 формирователя 3 импульсов соединен с входом разрешения записи регистра 10, а второй выход 19 - с входом обнуления старших разрядов счетчика и с первым входом схемы ИЛИ 12. Выход 20 генератора 4 соединен с вторыми входами ключей}, выходы 21 и«22 которых соединены соответственно с входами суммирования и вычитания триггера 8 младшего разряда счетчика Прямой выход 23 младшего разряда 8 соединен с входом обнуления блока 13 обнуления младшего разряда счетчика, с входом суммирования второго разряда счетчика, входящего в блок 9, первым входом регистра 10, инверс- ньй выход 24 - с входом вычитания старишх разрядов счетчика. Выход 25, заема счетчика 7 соединен с входом

42

блока 13, а счетные выходы 26 соеди-; нены с входами регистра 10, выходы 27 и 28 которого соединены с входами схемы ИСКЛЮЧАЮЩЕЕ ИЛИ и знаковым

выходом устройства. Выход 29 схемы ИСЮТЮЧАЮЩЕЕ ИЛИ являются выходами устройства, при этом выход 30 блока 13 соединен с вторым входом схемы ИЛИ 12, выход 31 которой соединен с

входом обнуления триггера 8 младшего разряда счетчика 7.

Устройство работает следующим образом.

При переходе через нуль напряже

5

0

5

кия U.J, выходной обмотки датчика

нуль-орган 1 формирует прямоугольные импульсы, которые поступают на вход делителя 2 на два. Прямой 16 и инверсный 17 выходы делителя 2 Hai два управляют первым 5 и вторым 6 ключами, пропускающими импульсы „ высокочастотного генератора 4 соответственно на суммирующий и вычитающий входы реверсивного счетчика 7. В конце каждого периода работы делителя 2 на два формирователь 3 импульсов вырабатывает два последовательных импульса 18 и 19, по которым происходит запись числа, накопленного в

счетчике 7, в регистр 10 и обнуление счетчика для подготовки его к следующему такту работы. Отрицательное число Представляется в счетчике обратным кодом, поэтому введена схе35 ма ИСКЛЮЧАЮЩЕЕ ИЛИ, преобразующая его в прямой код 29. Управление преобразованием осуществляется знаковым разрядом 28 регистра 10.

О Таким образом, в течение первого периода напряжения U(Тдп, ) в реверсивном счетчике суммируются импуль сы генератора, а в течение второго () - вычитаются. При вращении

45 объекта со скоростью ц; частота выходного сигнала датчика положения меняется по закону

f

АП

f -е 21Г

(1)

где fjj - частота питания датчика.

СледоватепьнО} если обьект неподвижен или вращается с постоянной .скоростью, то Т,П1 Тд„1 и к концу второго периода Ng 0. При вращении объекта с ускорением Т д„ чь т к мо- менту считывания код в счетчике больше или меньше нуля в зависимости от

313

направления вращения, поэтому получают отличное от нуля значение Ng :

NC (Тдщ Тдп1

)f, (-l--,-l-)f.

- ff

дпг

UJi

2ТГ

Ji l--) 2tr

)(fc ) L 1 Л1±1А11

r

(f + 4i -)(f + -1.) 0 - 2 П ° 2

LUi

w

T.e; выходной код устройства пропорционален ускорению t объекта.Здесь U), и to,, - средние значения скорости объекта за период и Тд соответственно. Величины (f|5± о) и

Wi

(fg i о-) обуславливают нелинейность

измерителя, однако при реальных величинах f (2,5-10) кГц и (а)/2«-)„д 20-60 Гц последней можно пренебречь и считать характеристику линейной:

N

S.L11

Ч

(3)

в предлагаемой схеме при переходе кода счетчика 7, в режиме вычитания через нуль (из 000. . .00 в 1,11.. 11) происходит потеря информации соответствующей одному импульсу, так как оба числа соответственно в прямом и обратном коде равны нулю,Чтобы избежать это и тем самым повысить точность измерения, необходимо переводить код счетчика при вычитании из 000...00 в 111...10. Для этого в устройство дополнительно введены схема ИЛИ 12 и схема 13 обнуления младшего разряда счетчика 7. Ее выход 30 устанавливается в 1 при переходе кода счетчика 7 через нуль по сигналу с выхода 25 заема счетчика и воздействует через схему ИЛИ 12 на R-вход триггера младшего разряда счетчика. Установка последнего в О блокирует схему обнуления млад36 4

шего разряда 13 сигналом с выхода 23, и дальнейшее вычитание происходит, начиная с кода 1111..,10.

J. Формула изобретения

Устройство цифрового измерения ускорения, содержащее частотный датчик скорости, два ключа, реверсивный 10 счетчик импульсов, генератор, дешифратор, причем выход датчика скорости соединен с первыми входами ключей, вторые входы которых соединены с выходами генератора, а выходы первого J5 и второго ключей соединены с входами суммирования и вычитания соответственно реверсивного счетчика, соединенного своими выходами с входами дешифратора, отличающееся тем, 0 что, с целью повьпиения надежности устройства, в него введены два D- триггера, двухвходовая схема ИЛИ, регистр памяти и формирователь импульсов с двумя выходами, причем задний 5 фронт импульса с первого выхода совпадает с передним фронтом импульса с второго выхода, при этом выход датчика соединен с входом первого D-триг- гера, прямой выход которого соеди- 0 нен напрямую с входом формирователя импульсов и первым входом первого ключа, а его инверсный выход - с пер- BbtM входом второго ключа, первьш выход формирователя импульсов соеди- нен с входом разрешения записи регистра памяти, а второй выход соединен с входами обнуления старших разрядов счетчика и с первым входом схемы I-Uffl, второй вход которой соединен 0 с. выходом второго В-триггера, соединенного входом с выходом заема счетчика, выход схемы ИЛИ соединен с входом обнуления младшего разряда счетчика, соединенного прямым выхо- 5 дом с входом суммирования второго разряда счетчика, входом обнуления второго D-триггера и первым входом регистра, а инверсным выходом - с входом вычитания старших разрядов 0 счетчика, выходы старших разрядов - счетчика соединены с входами старших разрядов регистра,выходы которого соединены с входами дешифратора и знаковым выходом устройства.

%

фиг

Составитель В.Пимеров Редактор А.Ревин Техред М.Ходанич Корректор Г.Решетник.

Заказ 2417/40 Тираж 776 Подписное ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб,, д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

| название | год | авторы | номер документа |

|---|---|---|---|

| ДЕЛИТЕЛЬ НА НЕЙРОНАХ | 2003 |

|

RU2249846C1 |

| АРИФМЕТИЧЕСКИЙ ВЫЧИСЛИТЕЛЬ | 2004 |

|

RU2292580C2 |

| СУММАТОР-ВЫЧИТАТЕЛЬ СТАРШИМИ РАЗРЯДАМИ ВПЕРЕД НА НЕЙРОНАХ | 2002 |

|

RU2205444C1 |

| Устройство для коррекции шкалы времени | 1986 |

|

SU1365039A2 |

| Цифровой веберметр | 1986 |

|

SU1368832A1 |

| Функциональный преобразователь | 1981 |

|

SU960836A1 |

| Цифровой фазометр | 1983 |

|

SU1128187A1 |

| Аналого-цифровой преобразователь с промежуточным преобразованием напряжения в частоту импульсов | 1985 |

|

SU1305856A1 |

| ПАРАЛЛЕЛЬНЫЙ СУММАТОР-ВЫЧИТАТЕЛЬ НА НЕЙРОНАХ СО СКВОЗНЫМ ПЕРЕНОСОМ | 2012 |

|

RU2523942C2 |

| Устройство для коррекции шкалы времени | 1990 |

|

SU1709268A1 |

Изобретение относится к вычислительной технике и может быть использовано в высокоточных системах автоматического регулирования скорости или положения исполнительных механизмов с упругой кинематической связью и фазовыми датчиками положения. Цель изобретения - повышение надежности устройства за счет упрощения его схемы. В конце каждого периода работы делителя частоты 2 на два формирователь 3 импульсов вьфабатывает два последовательных импульса, по которым происходит запись числа, накопленного в счетчике 7, в регистр 10 и обнуление счетчика 7 для подготовки его к следующему такту работы. Отрицательное число представляется в счетчике 7 обратным кодом и схема ИСКЛЮЧАЮЩЕЕ ИЛИ 11 преобразует его в прямой код. Управление преобразова нием осуществляют знаковым разрядом i СО со со 05 4 фикТ

| Бургин Б.Ш., Хорошавин В.П | |||

| Использование дополнительных обратных связей для модельного управления двухмассовой электромеханической системой | |||

| - В кн.: Электрооборудование автоматизированных установок | |||

| Проектирование аналого-цифровых систем на интегральных схемах /Под ред | |||

| Б.В.Шамря | |||

| М.: Машиностроение, 1976, с | |||

| Кулисный парораспределительный механизм | 1920 |

|

SU177A1 |

| 0 |

|

SU162993A1 | |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Цифровой измеритель ускорения вала | 1978 |

|

SU685987A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Видоизменение прибора для получения стереоскопических впечатлений от двух изображений различного масштаба | 1919 |

|

SU54A1 |

Авторы

Даты

1987-06-15—Публикация

1984-12-19—Подача