1 .1

Изобретение относится к радиотехнике и может быть использовано для фильтрации импульсных сигналов с преобразованием в цифровой код.

Цель изобретения сокращение времени переходных процессов„

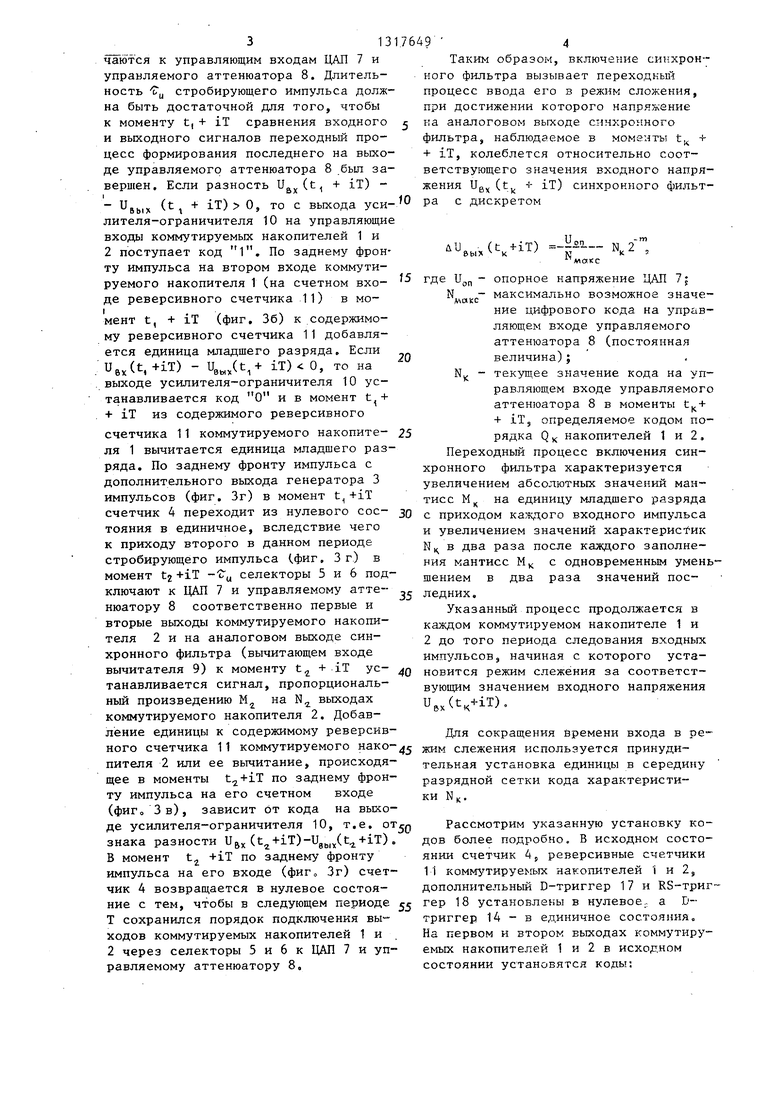

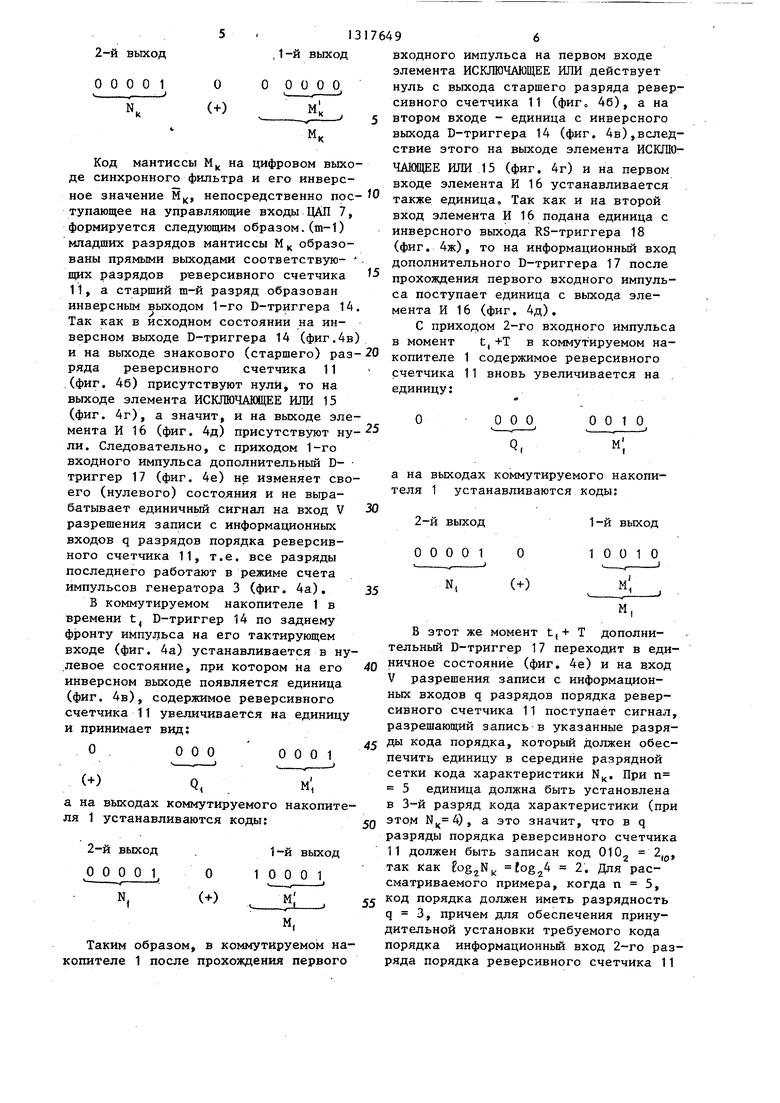

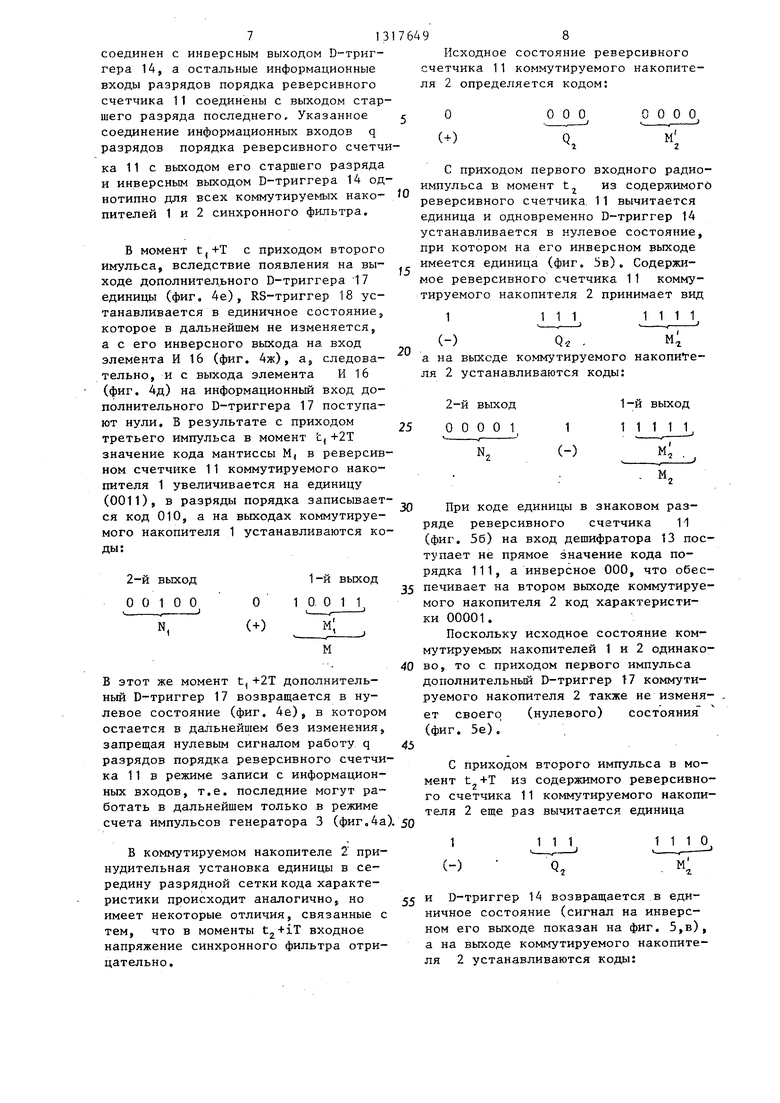

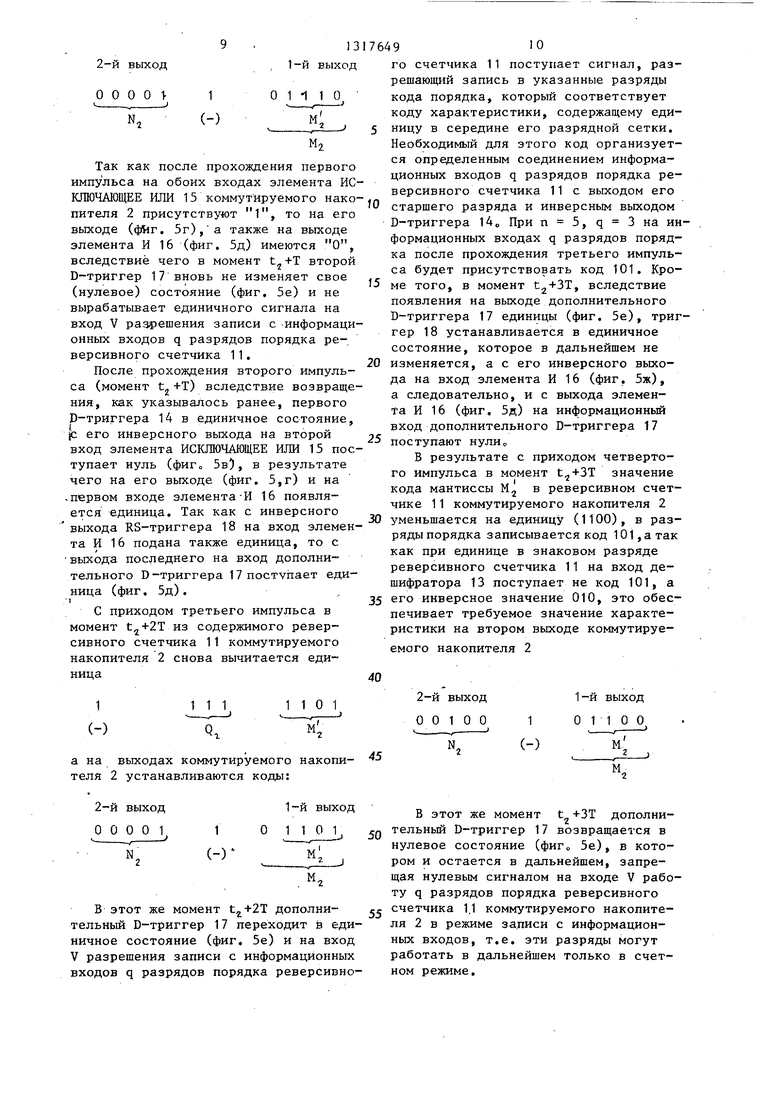

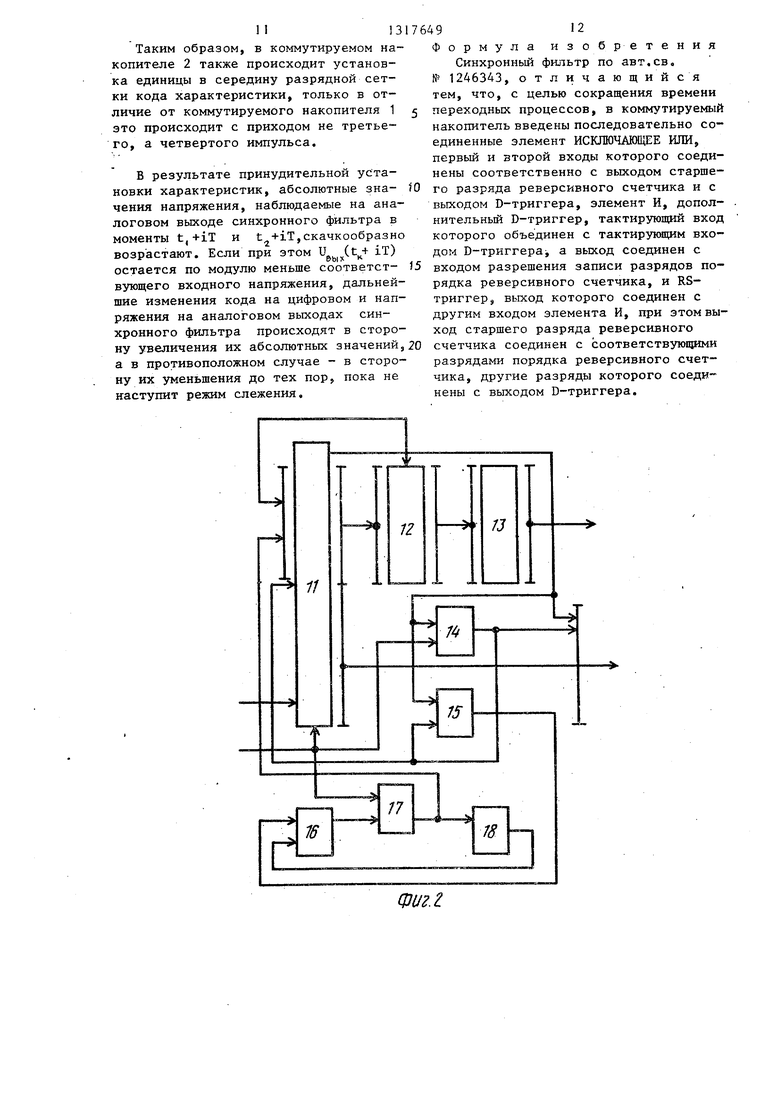

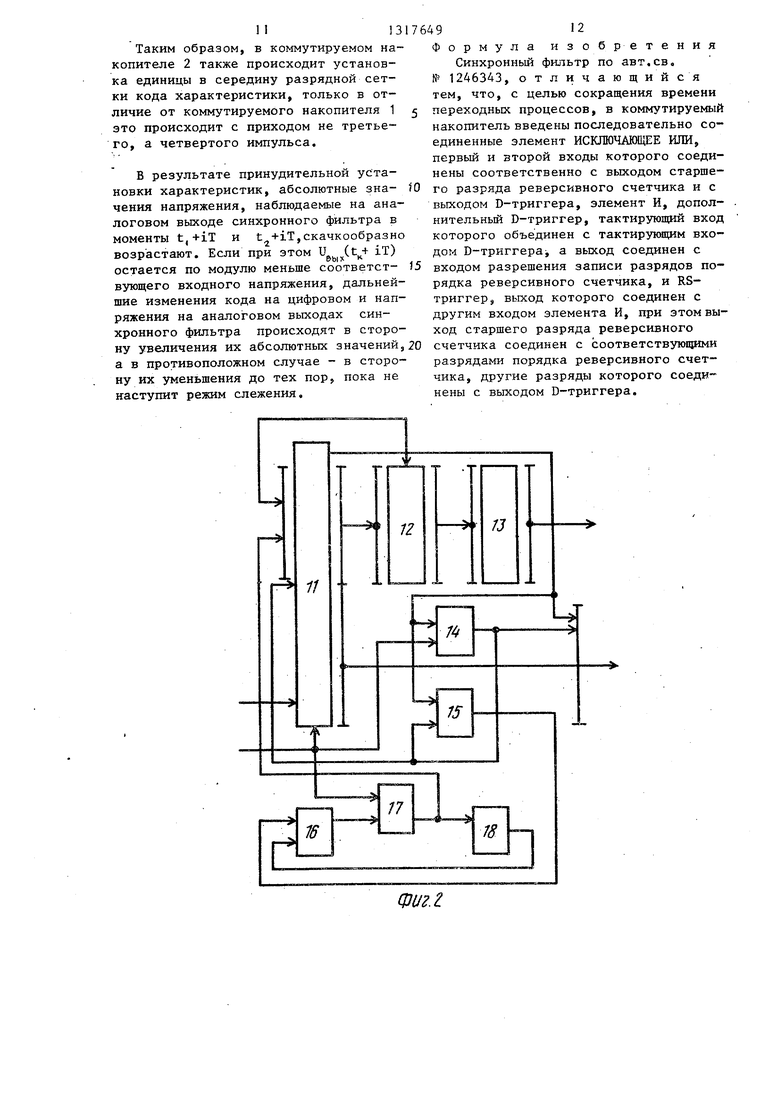

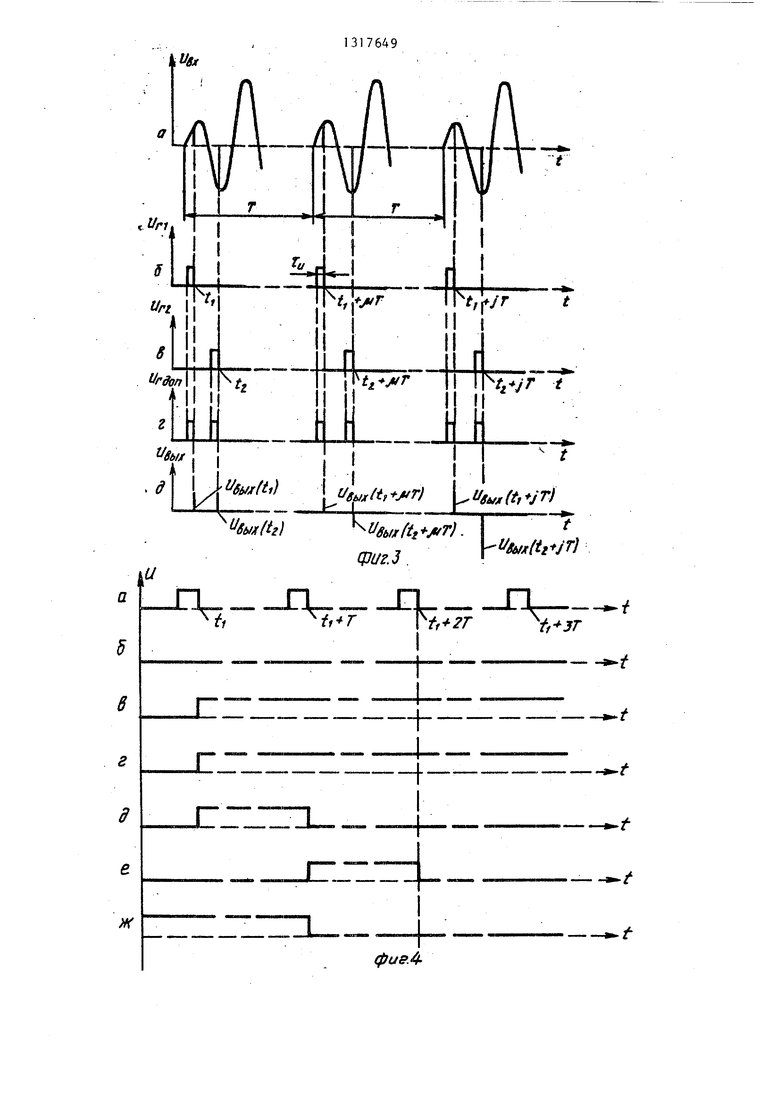

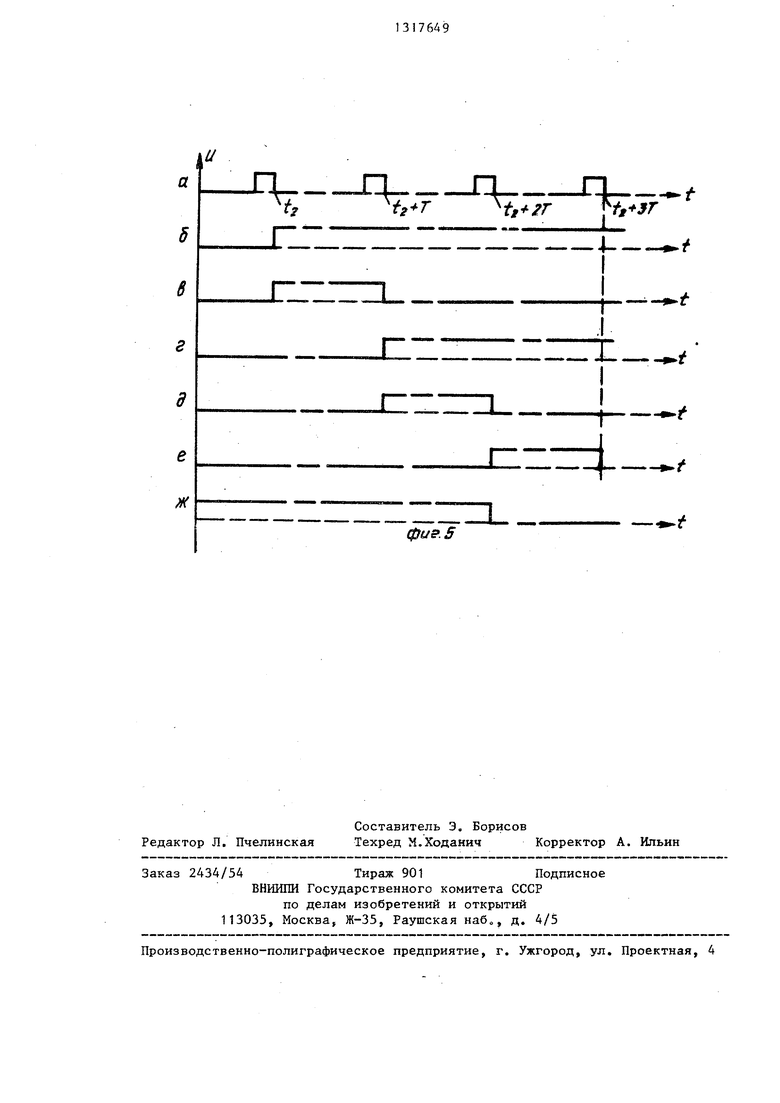

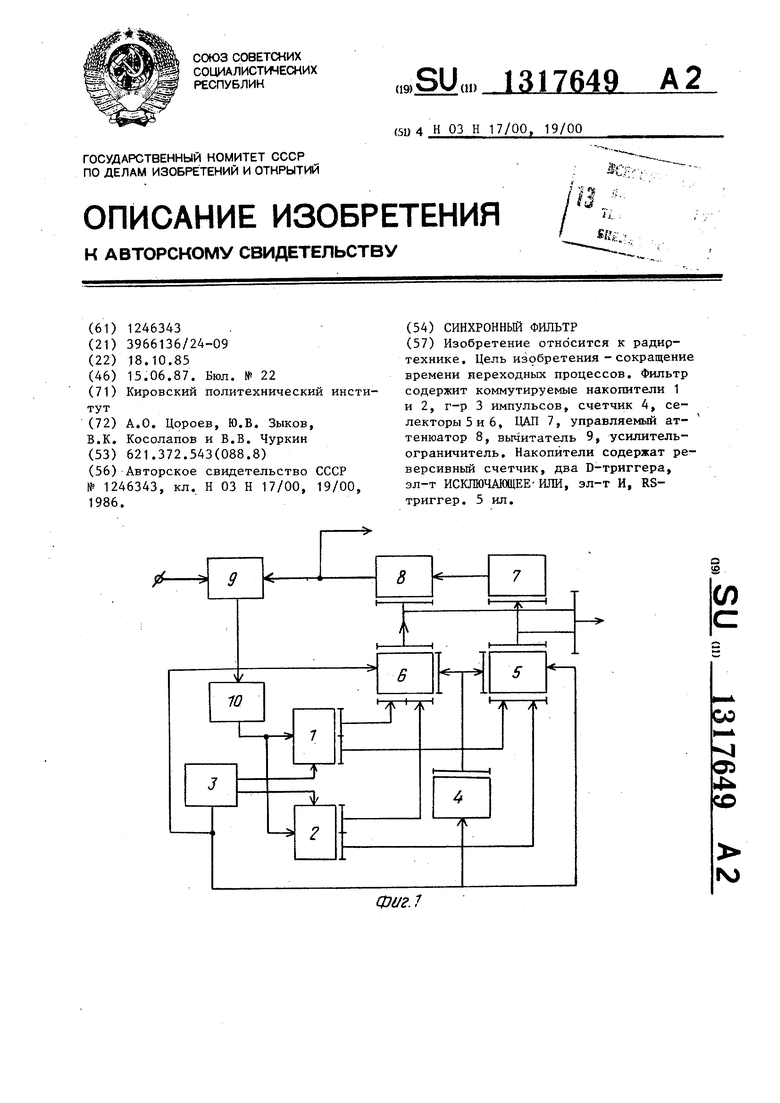

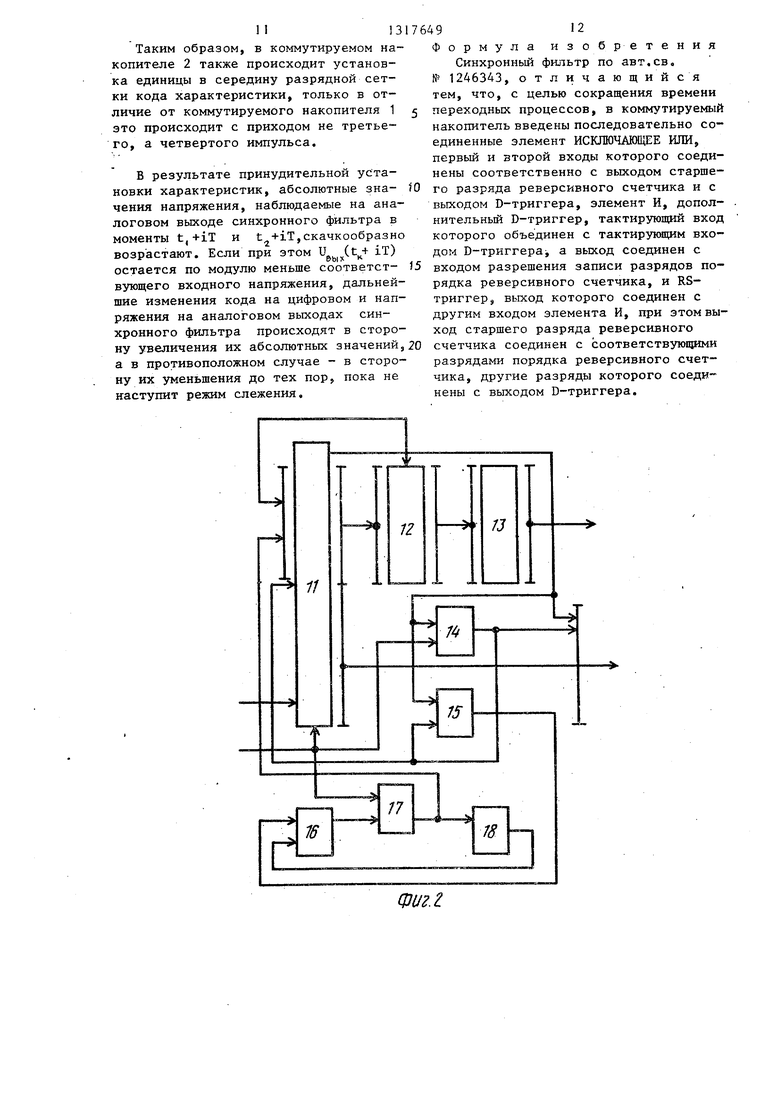

На фиг, 1 приведена структурная электрическая схема синхронного фильтра фиг, 2 структурная электрическая схема коммутируемого накопителя | на фиг. 3 - временные диаграг шы, поясняющие работу синхронного фильтра § на фиг.о 4 и 5 - временные диаграммы, поясняющие работу коммутируемых накопителей в начале переходного процесса включения синхронного фильтра о.

Синхронный фильтр содержит комму- тируёг-ше накопители 1 и 2, генератор 3 импульсов, счетчик 4, первый 5 и второй 6 селекторы, цифроаналоговый преобразо1затель (ЦАП) 7, управляемый аттенюатор 8, вычитатель 9 и усилитель-ограничитель Юо

Коммутируемый накопитель образуют реверсивный счетчик 11, комбинационный логический блок 12 дешифратор. 13, D-триггер 14, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ ISj элемент И 16, дополнительный D-триггер 17 и RS-триггер 18„

Синхронный фильтр работает следующим образоМо

Входной сигнал синхронного фильтра (фиг„За) представляет собой когерентную последовательность импульсов следующих с периодом То Сршхронньш фильтр вьщеляет L (по числу коммутируемых накопителей) значений входного импульса (на фиг о 3 L 2, соответственно количество комг- гутирз -емых накопителей также равно двум). Вьщеление значений входного сигнала во всех точках происходит параллельно

I

Каждый из KOMMyTHpyejyfbix накопителей 1 и 2 имеет два выхода Первый выход образуется из (т-1) младших разрядов реверсивного счетчика 11, выхода С триггера 14 и старщего разряда, реверсивного счетчика 11 , Первые выходы коммутируе1 1ых накопителей 1 и 2 представляют собой га- разрядную мантиссу М и знак цифрового эквивалента входного сигнала, рассматриваемого в моменты iT (i - число периодов, прошедших после включения синхронного фильтра) Остальные q разрядов реверсивного счетчика 11„ преобразованные при по9 2

мощи комбинационного логического блока 12 и дешифратора 13 в характеристику Nj5, образуют вторые выходы коммутируемых накопителей 1 и 2,

Первый селектор 5 обеспечивает поочередное подключение первых выходов коммутируемых накопителей 1 и 2 к управляющим входам ЦАП 7, а второй селектор 6 поочередно подключает вторые выходы коммутируемых накопителей 1 и 2 к управляющим входам управляемого аттенюатора 8, Порядок подключения определяется кодом на выходе счетчика 4, а моменты подключения и отключения задаются сигналами (фиг, Зг) с дополнительного выхода генератора 3. При наличии двух ком- мyтиpye ьrx накопите: ей счетчик 4 представлен одним двоичным разрядом.

Напряжение на выходе управляемого аттенюатора 8 (на алаговом выходе синхронного фильтра), определяется выражениями:

U,

II /, 1 г макс )

Мк+г- н,прии,,оз

N

MuN,.

макс

,

из которых следует, что напряжение на аналоговом выходе синхронного

фильтра в моменты t + iT пропорционально произведению кодов М и N на управляющих входах соответственно ЦАП 7 и управляемого аттенюатоР

Принцип работы синхронного фильтра основан на компенсации вьщеляемых значений входного напряжения Ugjj(t,+ + iT) напряжением ( iT) , действующим на вычитающем входе вычита- теля 9, Компенсация наступает по истечении j периодов Т после включения синхронного фильтра, когда U (t,, +

obl

+ iT) достигает (фиг. Зд) соответст- вующих значений Ugj((tj + iT) , т.е. i становится равным j. С приходом каждого входного импульса в каждый из двух моментов выделения значений входного напряжения к управляющим входам ЦАП 7 и управляемого аттенюатора 8 подключаются выходы соответствующего коммутируемого накопителя 1 или 2. Допустим, если с выхода счетчика 4 на управляющие входы селекто- ров 5 и 6 поступает код нуля, с приходом тактирующего импульса (фиг.Зг) первый и второй выходы коммутируемого накопителя 1 соответственно через первый 5 и второй 6 селекторы подклю3131.7649

к управляющим входам ЦАП 7 и емого аттенюатора 8. Длительнпр пр ка + ве же

ность Су стробирующего импульса должна быть достаточной для того, чтобы к моменту t, + iT сравнения входного и выходного сигналов переходный процесс формирования последнего на выходе управляемого аттенюатора 8 был завершен. Если разность , + iT) Таким образом, включение сиггхрон- ного фильтра вызывает переходкьш процесс ввода его в режим сложения, при достижении которого напряжение ка аналоговом выходе синхронного фильтра, наблюдаемое в моменты t, + + iT, колеблется относительно соответствующего значения входного напряжения Ug (t )- iT) синхронного фильт- с дискретом

Jeb.iT) макс

N,2

- (t + iT) О, то с выхода уси- Р лителя-ограничителя 10 на управляющие входы коммутируемых накопителей 1 и 2 поступает код 1, По заднему фронту импульса на втором входе коммутируемого накопителя 1 (на счетном вхо- где U опорное напряжение ЦАП 7|

максимально возможное значение цифрового кода на управляющем входе управляемого аттенюатора 8 (постоянная величина);

текущее значение кода на управляющем входе управляемого

де реверсивного счетчика 11) в момент t, + iT (фиг, Зб) к содержимому реверсивного счетчика 11 добавляется единица младшего разряда. Если

N

и

ex(t,+iT) - Ue,( iT)0, то на выходе усилителя-ограничителя 10 и в момент t.+

20

лакс

N. танавливается код

м

аттенюатора 8 в моменты t. +

м

аттенюатора 8 в моменты t. +

гч

+ iTj определяемое кодом порядка Q накопителей 1 и 2, Переходный процесс включения синхронного фильтра характеризуется увеличением абсолютных значений мантисс М1 на единицу младшего разряда с приходом каждого входного импульса и увеличением значений характеристик N, в два раза после каждого заполнения мантисс М шением в два

с одновременным умень раза значений пос+ iT из содержимого реверсивного

счетчика 11 коммутируемого накопите- 25 ля 1 вычитается единица младшего разряда. По заднему фронту импульса с дополнительного выхода генератора 3 импульсов (фиг. Зг) в момент t,+iT счетчик 4 переходит из нулевого сое- зо тояния в единичное, вследствие чего к приходу второго в данном периоде стробирующего импульса (.фиг, 3 г) в момент t2 +iT - сГц селекторы 5 и 6 подключают к ЦАП 7 и управляемому атте- ледних.

нюатору 8 соответственно первые и Указанный процесс продолжается в вторые выходы коммутируемого накопи- каждом коммутируемом накопителе 1 и теля 2 и на анапоговом выходе син- 2 до того периода следования входньпс хронного фильтра (вычитающем входе импульсов, начиная с которого уста- вычитателя 9) к моменту t + iT ус- Q новится режим слежения за соответст- танавливается сигнал, пропорциональный произведению М на N,j выходах коммутируемого накопителя 2, Добавление единицы к содержимому реверсивного счетчика 11 коммутируемого нако- им слежения используется принуди- пителя 2 или ее вычитание, происходящее в моменты Ц+iT по заднему фронту импульса на его счетном входе (фиГо Зв), зависит от кода на выходе усилителя-ограничителя 10, т.е. знака разности (t2+iT)-Ug|,|() . В момент tj, +iT по заднему фронту импульса на его входе (фиг Зг) счетчик 4 возвращается в нулевое состояние с тем, чтобы в следующем периоде гер 18 установлены в нулевое,, а D- Т сохранился порядок подключения вы- триггер 14 - в единичное состояния, Ходов коммутируемых накопителей 1 и . На первом и втором выходах коммутиру- 2 через селекторы 5 и 6 к ЦАП 7 и уп- емых накопителей 1 и 2 в исходном равляемому аттенюатору 8.состоянии установятся коды:

вующим значением входного напряжения кU,,(t,H.iT)

Для сокращения времени входа в ретельная установка единицы в середину разрядной сетки кода характеристики N.

Рассмотрим указанную установку кодов более подробно, В исходном состоянии счетчик 4, реверсивные счетчики 11 коммутируемых накопителей 1 и 2, дополнительный D-триггер 17 и RS-триг

Таким образом, включение сиггхрон- ного фильтра вызывает переходкьш процесс ввода его в режим сложения, при достижении которого напряжение ка аналоговом выходе синхронного фильтра, наблюдаемое в моменты t, + + iT, колеблется относительно соответствующего значения входного напряжения Ug (t )- iT) синхронного фильт- с дискретом

Р где U опорное напряжение ЦАП 7|

Jeb.iT) макс

N,2

U опорное напряжение

U N

лакс

20

N.

аттенюатора 8 в моменты t. +

гч

+ iTj определяемое кодом порядка Q накопителей 1 и 2, Переходный процесс включения синхронного фильтра характеризуется увеличением абсолютных значений мантисс М1 на единицу младшего разряда с приходом каждого входного импульса и увеличением значений характеристик N, в два раза после каждого заполне25зо ледних.

с одновременным умень- раза значений пос

Указанный процесс продолжается в каждом коммутируемом накопителе 1 и 2 до того периода следования входньпс импульсов, начиная с которого уста- новится режим слежения за соответст- им слежения используется принуди- гер 18 установлены в нулевое,, а D- триггер 14 - в единичное состояния, На первом и втором выходах коммутиру- емых накопителей 1 и 2 в исходном состоянии установятся коды:

вующим значением входного напряжения кU,,(t,H.iT)

Указанный процесс продолжается в дом коммутируемом накопителе 1 и о того периода следования входньпс ульсов, начиная с которого уста- ится режим слежения за соответст- слежения используется принуди- 18 установлены в нулевое,, а D- ггер 14 - в единичное состояния, первом и втором выходах коммутиру- х накопителей 1 и 2 в исходном тоянии установятся коды:

Для сокращения времени входа в ре Указанный процесс продолжается в каждом коммутируемом накопителе 1 и 2 до того периода следования входньпс импульсов, начиная с которого уста- новится режим слежения за соответст- им слежения используется принуди- гер 18 установлены в нулевое,, а D- триггер 14 - в единичное состояния, На первом и втором выходах коммутиру- емых накопителей 1 и 2 в исходном состоянии установятся коды:

тельная установка единицы в середину разрядной сетки кода характеристики N.

Рассмотрим указанную установку кодов более подробно, В исходном состоянии счетчик 4, реверсивные счетчики 11 коммутируемых накопителей 1 и 2, дополнительный D-триггер 17 и RS-триг13

,1-и выход

о00000

-JiLм.

Код мантиссы М на цифровом выходе синхронного фильтра и его инверсное значение М, непосредственно поступающее на управляющие входы ЦАП 7, формируется следующим образом.(т-1) младших разрядов мантиссы М образованы прямыми выходами соответствую- щих разрядов реверсивного счетчика 11, а старший т-й разряд образован инверсным выходом 1-го D-триггера 14 Так как в исходном состоянии на инверсном выходе D-триггера 14 (фиг.4в) и на выходе знакового (старшего) разряда реверсивного счетчика 11 .(фиг. 4б) присутствуют нули, то на выходе элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 15 (фиг. 4г), а значит, и на выходе элемента И 16 (фиг. 4д) присутствуют нули. Следовательно, с приходом 1-го входного импульса дополнительный D- триггер 17 (фиг. 4е) не изменяет своего (нулевого) состояния и не вырабатывает единичный сигнал на вход V разрешения записи с информационных входов q разрядов порядка реверсивного счетчика 11, т.е. все разряды последнего работают в режиме счета импульсов генератора 3 (фиг, 4а).

В коммутируемом накопителе 1 в времени t D-триггер 14 по заднему фронту импульса на его тактирующем входе (фиг. 4а) устанавливается в нулевое состояние, при котором на его инверсном выходе появляется единица (фиг. 4в), содержимое реверсивного счетчика 11 увеличивается на единицу и принимает вид:

О

О 00

0001

(+)

Qi .M;

а на выходах коммутируемого накопителя 1 устанавливаются коды:

1-й выход о 1 О 001

м.

Таким образом, в коммутируемом накопителе 1 после прохождения первого

76496

входного импульса на первом входе элемента ИСКЛЮЧАЮЩЕЕ ИЛИ действует нуль с выхода старшего разряда реверсивного счетчика 11 (фиг 46), а на 5 втором входе - единица с инверсного выхода D-триггера 14 (фиг. 4в),вследствие этого на выходе элемента ИСКГПОЧАЩЕЕ ИЛИ 15 (фиг. 4г) и на первом входе элемента И 16 устанавливается также единица. Так как и на второй вход элемента И 16 подана единица с инверсного выхода RS-триггера 18 (фиг. 4ж), то на информационный вход дополнительного D-триггера 17 после прохождения первого входного импульса поступает единица с выхода элемента И 16 (фиг. 4д),

С приходом 2-го входного импульса в момент t, +Т в коммутируемом на- копителе 1 содержимое реверсивного счетчика 11 вновь увеличивается на . единицу:

5

25

О

0010

а на выходах коммутируемого накопителя 1 устанавливаются коды:

30

2-й выход

1-й выход

00001

0010

N,

(+)

5м.

в этот же момент t,+ Т дополнительный Б-триггер 17 переходит в единичное состояние (фиг. 4е) и на вход V разрешения записи с информационных входов q разрядов порядка реверсивного счетчика 11 поступает сигнал, разрешающий запись-в указанные разряды кода порядка, который должен обеспечить единицу в середине разрядной сетки кода характеристики N. При п 5 единица должна быть установлена в 3-й разряд кода характеристики (при

этом ), а это значит, что в q

разряды порядка реверсивного счетчика 11 должен быть записан код OlOg 2,, так как og,jN| 2. Для рассматриваемого примера, когда п 5,

код порядка должен иметь разрядность q 3, причем для обеспечения принудительной установки требуемого кода порядка информационный вход 2-го разряда порядка реверсивного счетчика 11

соединен с инверсным выходом D-триг- гера 14, а остальные информационные входы разрядов порядка реверсивного счетчика 11 соединены с выходом старшего разряда последнего. Указанное соединение информационных входов q разрядов порядка реверсивного счетчика 1 1 с выходом его старшего разряда и инверсным выходом D-триггера 14 однотипно для всех коммутируемых нако- пителей 1 и 2 синхронного фильтра.

В момент t,+T с приходом второго имульса, вследствие появления на выходе дополнительного D-триггера 17 единицы (фиг, 4е), RS-триггер 18 устанавливается в единичное состояние, которое в дальнейшем не изменяется, а с его инверсного выхода на, вход элемента И 16 (фиг. 4ж), а, следовательно, и с выхода элемента И 16 (фиг. 4д) на информационный вход дополнительного D-триггера 17 поступают нули, В результате с приходом третьего импульса в момент t +2Т значение кода мантиссы М, в реверсивном счетчике 11 коммутируемого накопителя 1 увеличивается на единицу (0011), в разряды порядка записьшает- ся код 010, а на выходах коммутируемого накопителя 1 устанавливаются коды:

2-й выход

00100

,

N,

М

В этот же момент t, +2Т дополнительный D-триггер 17 возвращается в нулевое состояние (фиг, 4е), в котором остается в дальнейшем без изменения, запрещая нулевым сигналом работу q разрядов порядка реверсивного счетчика 1 1 в режиме записи с информационных входов, т,е, последние могут работать в дальнейшем только в режиме счета импульсов генератора 3 (фиг,4а

В коммутируемом накопителе 2 принудительная установка единицы в середину разрядной сетки кода характеристики происходит аналогично, но имеет некоторые отличия, связанные с тем, что в моменты входное напряжение синхронного фильтра отрицательно.

Исходное состояние реверсивного счетчика 11 коммутируемого накопителя 2 определяется кодом:

О (+)

О 00 0

М

с приходом первого входного радиоимпульса в момент t из содержимогб реверсивного счетчика 11 вычитается единица и одновременно D-триггер 14 устанавливается в нулевое состояние, при котором на его инверсном выходе имеется единица (фиг, 5в). Содержимое реверсивного счетчика 11 коммутируемого накопителя 2 принимает вид

1111 1111

(-)

М

Qi . г а на выходе коммутируемого накопителя 2 устанавливаются коды:

2-й выход 0000 1,

N.

1 (-)

1-й выход

11111

- М

При коде единицы в знаковом разряде реверсивного счетчика 11 (фиг, 56) на вход дешифратора 13 поступает не прямое значение кода порядка 111, а инверсное 000, что обеспечивает на втором выходе коммутируемого накопителя 2 код характеристики 00001,

Поскольку исходное состояние коммутируемых накопителей 1 и 2 одинаково, то с приходом первого импульса дополнительный D-триггер 17 коммутируемого накопителя 2 также не изменяет своего (нулевого) состояния (фиг. 5е),

С приходом второго импульса в моиз содержимого реверсивного счетчика 11 коммутируемого накопителя 2 еще раз вычитается единица

мент t,,+T

1

дТ

1110

М

и D-триггер 14 возвращается в единичное состояние (сигнал на инверсном его выходе показан на фиг, 5,в), а на выходе коммутируемого накопителя 2 устанавливаются коды:

9 .13

, 1-й выход

1 01110

J

M;

м.

Так как после прохождения первого импульса на обоих входах элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 15 коммутируемого накопителя 2 присутствуют 1, то на его выходе (фиг, 5г), а также на выходе элемента И 16 (фиг, 5д) имеются О, вследствие чего в момент t,, +Т второй D-триггер 17 вновь не изменяет свое (нулевое) состояние (фиг, 5е) и не вырабатывает единичного сигнала на вход V разрешения записи с информационных входов q разрядов порядка реверсивного счетчика 11,

После прохождения второго импульса (момент t,, +Т) вследствие возвращения, как указывалось ранее, первого Р-триггера 14 в единичное состояние, JC его инверсного выхода на второй вход элемента ИСКЛЮЧАЩЕЕ ИЛИ 15 поступает нуль (фиго 5в), в результате чего на его выходе (фиг, 5,г) и на

-первом входе элемента-И 16 появляется единица. Так как с инверсного выхода RS-триггера 18 на вход элемента И 16 подана также единица, то с

выхода последнего на вход дополнительного D-триггера 17 поступает единица (фиг, 5д) ,

1

С приходом третьего импульса в момент t2+2T из содержимого реверсивного счетчика 11 коммутируемого накопителя 2 снова вычитается единица

910

го счетчика 11 поступает сигнал, разрешающий запись в указанные разряды кода порядка, который соответствует коду характеристики, содержащему еди- ницу в середине его разрядной сетки. Необходимый для этого код организуется определенным соединением информационных входов q разрядов порядка реверсивного счетчика 11 с выходом его старшего разряда и инверсным выходом D-триггера 14о При , информационных входах q разрядов порядка после прохождения третьего импульса будет присутствовать код 101, Кро- ме того, в момент , вследствие появления на выходе дополнительного D-триггера 17 единицы (фиг, 5е), триггер 18 устанавливается в единичное состояние, которое в дальнейшем не

да на вход элемента И 16 (фиг. 5ж), а следовательно, и с выхода элемента И 1 6 (фиг, 5д) на информационньш вход дополнительного D-триггера 17 поступают нули о

В результате с приходом четвертого импульса в момент

ц+зт

значение

кода мантиссы М в реверсивном счетчике 11 коммутируемого накопителя 2

уменьшается на единицу (1100), в разряды порядка записывается код 101, а так как при единице в знаковом разряде реверсивного счетчика 11 на вход дешифратора 13 поступает не код 101, а

его инверсное значение 010, это обеспечивает требуемое значение характеристики на втором выходе коммутируеемого накопителя 2

1 (-)

1101

мГ

а на выходах коммутируемого накопи теля 2 устанавливаются коды:

45

2-й выход 001001

1

N,(-)

1-й выход о 11 00

JL.

м

выход 001

N

1

(-Г

1-й выход о 1101

м:

.-J J

м.

в этот же момент дополнительный D-триггер 17 переходит в единичное состояние (фиг, 5е) и на вход V разрешения записи с информационных входов q разрядов порядка реверсивно

В этот же момент t +ЗТ дополнительный D-триггер 17 возвращается в нулевое состояние (фиго 5е), в котором и остается в дальнейшем, запрещая, нулевым сигналом на входе V работу q разрядов порядка реверсивного счетчика 1.1 коммутируемого накопителя 2 в режиме записи с информационных входов, т.е. эти разряды могут работать в дальнейшем только в счетном режиме.

1 113

Таким образом, в коммутируемом накопителе 2 также происходит установка единицы в середину разрядной сетки кода характеристики, только в отличие от коммутируемого накопителя 1 это происходит с приходом не третьего, а четвертого импульса.

В результате принудительной установки характеристик, абсолютные значения напряжения, наблюдаемые на аналоговом выходе синхронного фильтра в моменты t,+1Т и ,скачкообразно возрастают. Если при этом остается по модулю меньше соответствующего входного напряжения, дальнейшие изменения кода на цифровом и напряжения на аналоговом выходах синхронного фильтра происходят в сторону увеличения их абсолютных значений, а в противоположном случае - в сторону их уменьшения до тех пор, пока не наступит режим слежения.

912

Формула изобретения

Синхронный фильтр по авт.ев, № 1246343, отличающийся тем, что, с целью сокращения времени

переходных процессов, в коммутируемый накопитель введены последовательно соединенные элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, первый и второй входы которого соединены соответственно с выходом старшего разряда реверсивного счетчика и с выходом D-триггера, элемент И, дополнительный D-триггер, тактирующий вход которого объединен с тактирующим входом D-триггераi а выход соединен с

входом разрешения записи разрядов порядка реверсивного счетчика, и RS- триггер, выход которого соединен с другим входом элемента И, при этом выход старшего разряда реверсивного

счетчика соединен с соответствующими разрядами порядка реверсивного счетчика, другие разряды которого соеди™ нены с выходом D-триггера.

Фиг.1

Vn

Vrt I

4r/r

IJrdon

I

%лг

д

I

i

| L/ //V7 /

t

д///4;

- | L/ //V7 /

t

Sbf/ftg - r). I

07. J.

ут;

| название | год | авторы | номер документа |

|---|---|---|---|

| Синхронный фильтр | 1984 |

|

SU1246343A1 |

| Синхронный фильтр | 1983 |

|

SU1131028A1 |

| Устройство для кодирования звуковых сигналов с инерционным компандированием | 1985 |

|

SU1356233A1 |

| Устройство для измерения средней мощности огибающей узкополосного процесса | 1986 |

|

SU1325373A1 |

| Следящий аналого-цифровой преобразова-ТЕль | 1979 |

|

SU828401A1 |

| Формирователь синусоидальных сигналов | 1986 |

|

SU1429281A1 |

| Устройство для контроля аналого-цифрового преобразователя | 1986 |

|

SU1585897A1 |

| Устройство измерения временных интервалов | 1984 |

|

SU1144062A1 |

| СЛЕДЯЩИЙ АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 1989 |

|

RU2028731C1 |

| УСТРОЙСТВО ФОРМИРОВАНИЯ СЛОЖНЫХ СИГНАЛОВ | 1988 |

|

SU1841042A1 |

Изобретение относится к радир- технике. Цель изобретения -сокращение времени переходных процессов. Фильтр содержит коммутируемые накопители 1 и 2, г-р 3 импульсов, счетчик 4, селекторы 5 и 6, ЦАП 7, управляемый аттенюатор 8, вычитатель 9, усилитель- ограничитель. Накопители содержат реверсивный счетчик, два D-триггера, эл-т ИСКЛЮЧАЮЩЕЕ-ИЛИ, эл-т И, RS- триггер. 5 ил. N) фиг. 7

| Синхронный фильтр | 1984 |

|

SU1246343A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1987-06-15—Публикация

1985-10-18—Подача