4; to о to

00

Устройство относится к радиотех- йике и может быть использовано в уст- |)ойствах технической диагностики для формирования синусоидальных сигналов.

Целью изобретения является повыше- |1ие точности формирования выходных сигналов.

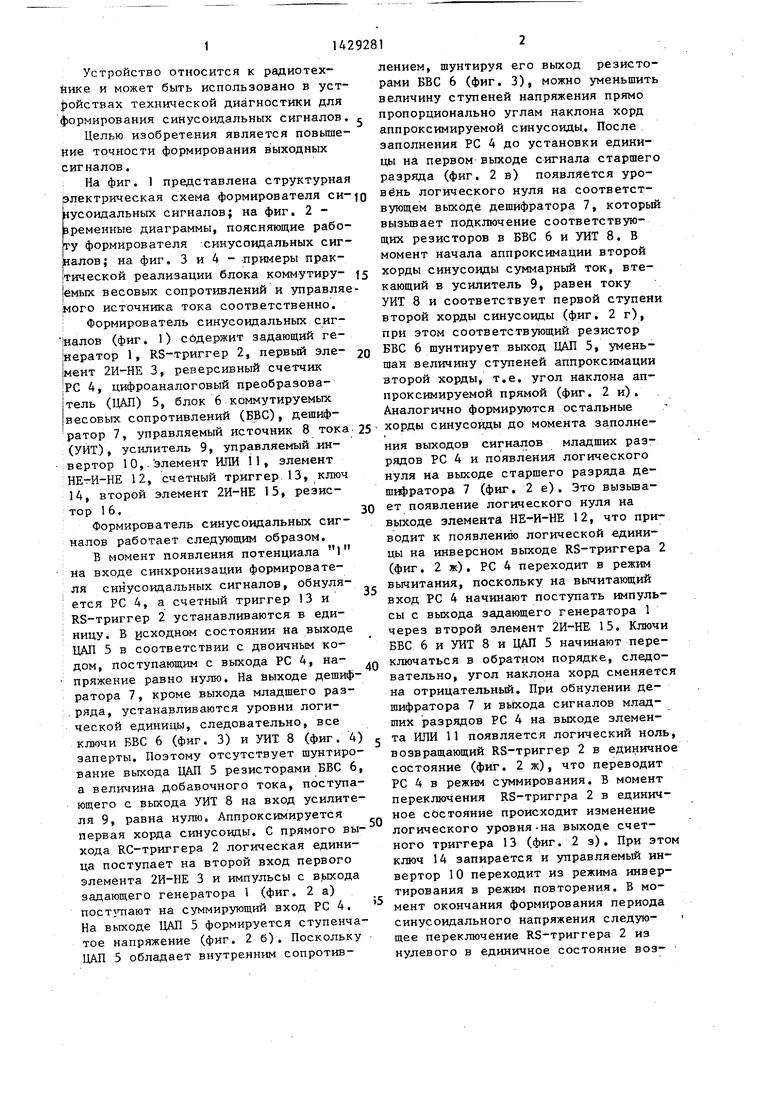

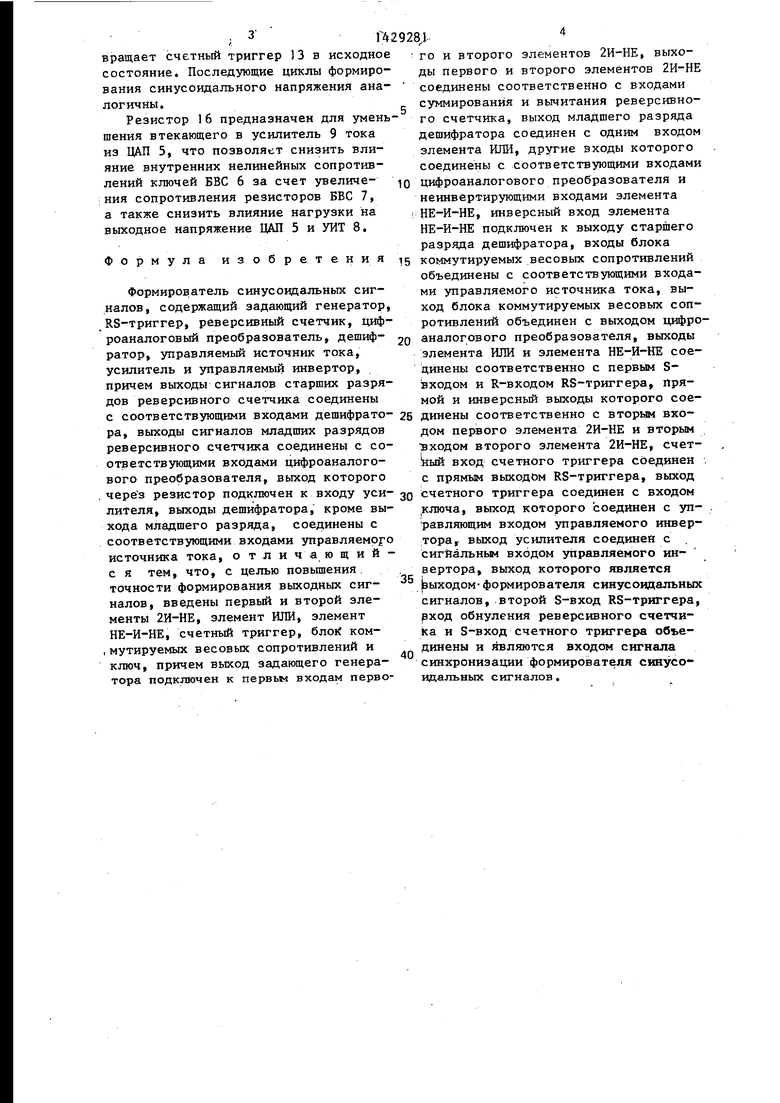

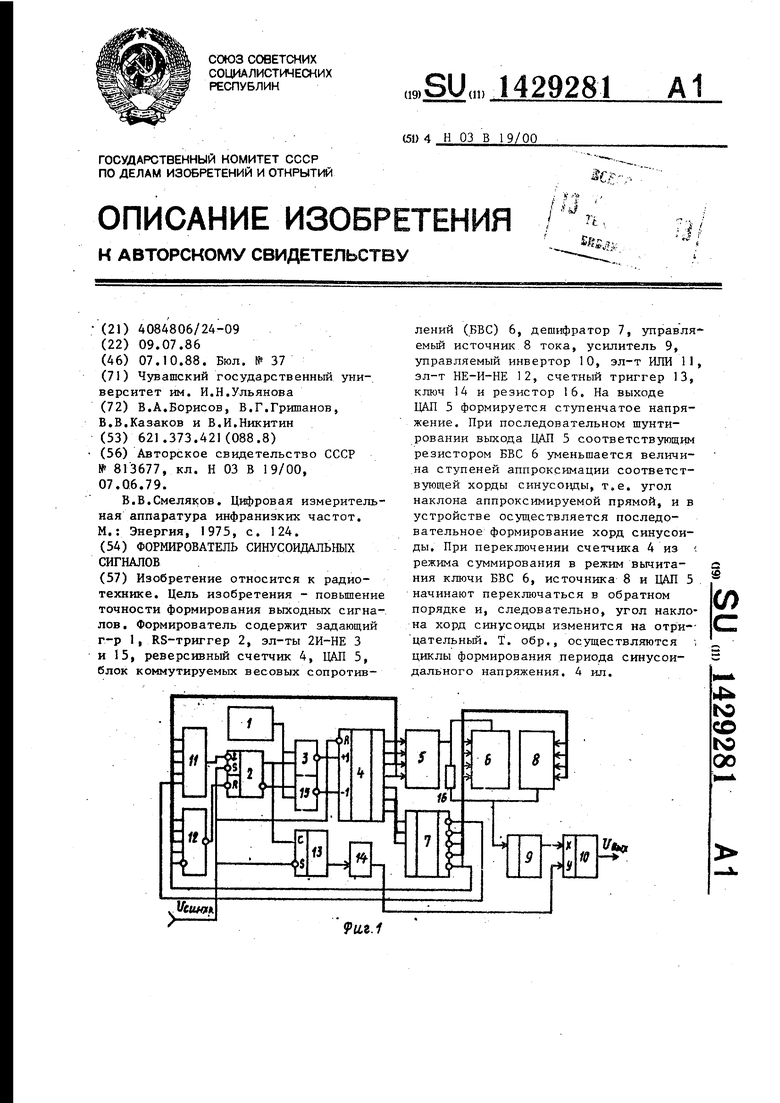

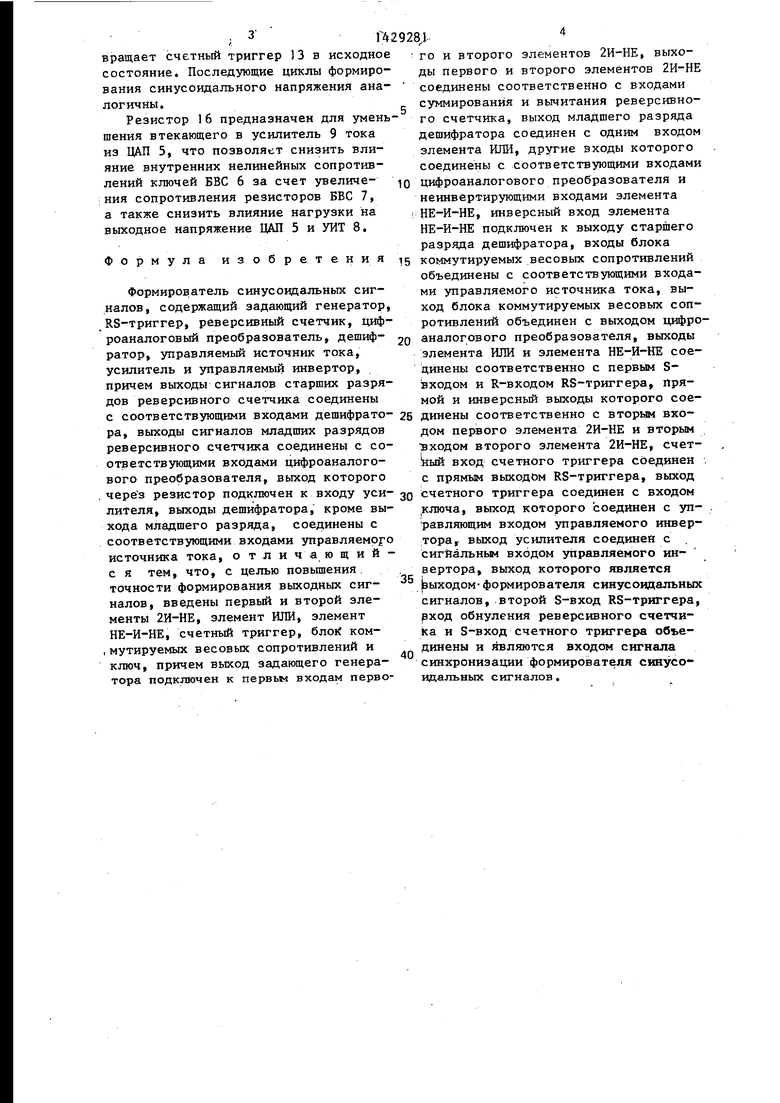

: На фиг. 1 представлена структурная рлектрическая схема формирователя синусоидальных сигналов; на фиг. 2 временные диаграммы, поясняющие работу формирователя синусоидальных сигналов ; на фиг. 3 и 4 - примеры прак- |тической реализации блока коммутиру- |емьгх весовых сопротивлений и управляе JMoro источника тока соответственно. ; Формирователь синусоидальных сиг- налов (фиг. 1) сйдержит задающий генератор 1, RS-триггер 2, первый элемент 2И-НЕ 3, реверсивный счетчик ;РС 4, цифроаналоговый преобразова- тель (ЦДЛ) 5, блок 6 коммутируемых весовых сопротивлений (ВВС), дешиф- ратор 7, управляемый источник 8 тока (УИТ), ycIiлитeль 9, управляемый инвертор 10,. элемент ИЛИ П, элемент НЕг-И-НЕ 12, счетный триггер 13 ключ 14, второй элемент 2И-НЕ 15, резистор 16.

Формирователь синусоидальных сигналов работает следующим образом.

В момент появления потенциала 1 на входе синхронизации формирователя синусоидальных сигналов, обнуляется PC 4, а счетный триггер 13 и RS-триггер 2 устанавливаются в единицу. В {ИСХОДНОМ состоянии на выходе ЦАП 5 в соответствии с двоичным кодом, поступающим с выхода PC 4, напряжение равно нулю. На выходе дешифратора 7, кроме выхода младшего раз- .ряда, устанавливаются уровни логической единицы, следовательно, все ключи ВВС 6 (фиг. 3) и УИТ 8 (фиг. 4) заперты. Поэтому отсутствует шунтирование выхода ЦАП 5 резисторами ВВС 6, а величина добавочного тока, поступающего с выхода УИТ 8 на вход усилителя 9, равна нулю. Аппроксимируется первая хорда синусоиды. С прямого выхода ЕС-триггера 2 логическая единица поступает на второй вход первого элемента 2И-НЕ 3 и импульсы с вькода задающего генератора 1 (фиг. 2 а) пост ттают на суммирующий вход PC 4. На выходе ЦАП 5 формируется ступенчатое напряжение (фиг. 2 б). Поскольку иДП 5 обладает внутренним сопротив

0

5

0

5

0

0

55

лением, шунтируя его выход резисторами ВВС 6 (фиг. 3), можно уменьшить величину ступеней напряжения прямо пропорционально углам наклона хорд аппроксимируемой синусоиды. После заполнения PC 4 до установки единицы на первом выходе сигнала старшего разряда (фиг. 2 в) появляется уровень логического нуля на соответствующем выходе дешифратора 7, который вызывает подключение соответствующих резисторов в ВВС 6 и УИТ 8. В момент начала аппроксимации второй хорды синусоиды суммарный ток, втекающий в усилитель 9, равен току УИТ 8 и соответствует первой ступени второй хорды синусоиды (фиг. 2 г), при этом соответствующий резистор ВВС 6 шунтирует выход ЦАП 5, уменьшая величину ступеней аппроксимации второй хорды, т.е. угол наклона аппроксимируемой прямой (фиг. 2 и). Аналогично формируются остальные хорды синусоиды до момента заполнения выходов сигналов младших разрядов PC 4 и появления логического нуля на выходе старшего разряда де- Ш14 ратора 7 (фиг. 2 е). Это вызьша- ет появление логического нуля на выходе элемента НЕ-И-НЕ 12, что приводит к появленио логической единицы на инверсном выходе RS-триггера 2 (фиг. 2 ж). PC 4 переходит в режим вычитания, поскольку на вьтчитающий вход PC 4 начинают поступать импульсы с выхода задающего генератора 1 через второй элемент 2И-НЕ 15. Ключи ВВС 6 и УИТ 8 и ЦАП 5 начинают переключаться в обратном порядке, следовательно, угол наклона хорд сменяется на отрицательный. При обнулении дешифратора 7 и вьтхода сигналов младших разрядов PC 4 на выходе элемента ИЛИ 11 появляется логический ноль, возвращающий RS-триггер 2 в единичное состояние (фиг. 2 ж), что переводит PC 4 в режим суммирования. В момент переключения RS-триггра 2 в единичное состояние происходит изменение логического уровня-на выходе счетного триггера 13 (фиг. 2 з). При этом ключ 14 запирается и управляемый инвертор 10 переходит из режима инвертирования в режим повторения. Б момент окончания формирования периода синусоидального напряжения следую- щее переключение RS-триггера 2 из нулевого в единичное состояние возвращает счетный триггер 13 в исходное состояние. Последующие циклы формирования синусоидального напряжения аналогичны.

Резистор 16 предназначен для уменьшения втекающего в усилитель 9 тока из ЦАП 5, что позволяет снизить влияние внутренних нелинейных сопротивлений ключей ВВС 6 за счет увеличения сопротивления резисторов ВВС 7, а также снизить влияние нагрузки на выходное напряжение ЦАП 5 и УИТ 8.

Формула изобретения

15 коммутируемых весовых сопротивлений объединены с соответствующими входами управляемого источника тока, выход блока коммутируемых весовых сопротивлений объединен с выходом цифро

20 аналогового преобразователя, выходы элемента ИЛИ и элемента НЕ-И-НЕ соединены соответственно с первым S- входом и R-входом RS-триггера, прямой и инверсный выходы которого соеФормирователь синусовдальных сигналов, содержащий задающий генератор, RS-триггер, реверсивный счетчик, циф- роаналоговый преобразователь, дешифратор, управляемый источник тока, усилитель и управляемый инвертор, причем выходы сигналов старших разрядов реверсивного счетчика соединены с соответствующими входами дешифрато- 26 динены соответственно с вторым вхо- ра, выходы сигналов младших разрядовдом первого элемента 2И-НЕ и вторым

реверсивного счетчика соединены с со- входом второго элемента 2И-НЕ, счет- ответе твующими входами цифроаналого- ный вход счетного триггера соединен вого преобразователя, выход которого с прямым выходом RS-триггера, выход . чере з резистор подключен к входу уси- зо счетного триггера соединен с входом лителя, выходы дешифратора, кроме вы- ключа, выход которого соединен с уп- хода младшего разряда, соединены с соответствующими входами управляемого источника тока, отличающий равляющим входом управляемого инвертора , выход усилителя соединен с сигИальньм входом управляемого инвертора, выход которого является выходом-формирователя синусоцдальных сигналов, второй S-вход RS-триггера, рход обнуления реверсивного счетчи- ka и S-вход счетного триггера объединены и являются входом сигнала синхронизации формирователя синусоидальных сигналов.

с я тем, что, с целью повьш1ения точности формирования выходных сигналов, введены первый и второй элементы 2И-НЕ, элемент ШШ, элемент НЕ-И-НЕ, счетный триггер, блок ком- , мутируемых весовых сопротивлений и ключ, причем выход задающего генератора подключен к первьм входам первого и второго элементов 2И-НЕ, выходы первого и второго элементов 2И-НЕ соединены соответственно с входами суммирования и вычитания реверсивного счетчика, выход младшего разряда дешифратора соединен с одним входом элемента ИЛИ, другие входы которого соединены с соответствующими входами

0 цифроаналогового преобразователя и

неинвертирующими входами элемента НЕ-И-НЕ, инверсный вход элемента НЕ-И-НЕ подключен к выходу старшего разряда дешифратора, входы блока

5 коммутируемых весовых сопротивлений объединены с соответствующими входами управляемого источника тока, выход блока коммутируемых весовых сопротивлений объединен с выходом цифро0 аналогового преобразователя, выходы элемента ИЛИ и элемента НЕ-И-НЕ соединены соответственно с первым S- входом и R-входом RS-триггера, прямой и инверсный выходы которого сое6 динены соответственно с вторым вхо- дом первого элемента 2И-НЕ и вторым

входом второго элемента 2И-НЕ, счет- ный вход счетного триггера соединен с прямым выходом RS-триггера, выход о счетного триггера соединен с входом ключа, выход которого соединен с уп-

равляющим входом управляемого инвертора , выход усилителя соединен с сигИальньм входом управляемого инвертора, выход которого является выходом-формирователя синусоцдальных сигналов, второй S-вход RS-триггера, рход обнуления реверсивного счетчи- ka и S-вход счетного триггера объединены и являются входом сигнала синхронизации формирователя синусоидальных сигналов.

0

TnjiEU/jiimijimuiimJDJi

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для исследования магнитных свойств материалов | 1987 |

|

SU1518809A1 |

| Синтезатор частот | 1985 |

|

SU1358092A1 |

| Устройство формирования многоступен-чАТОгО КВАзиСиНуСОидАльНОгО ТРЕХфАз-НОгО НАпРяжЕНия | 1979 |

|

SU817902A1 |

| Устройство формирования много-СТупЕНчАТОгО КВАзиСиНуСОидАльНОгОТРЕХфАзНОгО НАпРяжЕНия | 1978 |

|

SU809437A1 |

| Устройство для формирования @ -фазного квазисинусоидального напряжения с нечетным числом фаз | 1984 |

|

SU1220071A1 |

| Устройство для управления встречно-параллельно включенными тиристорами | 1979 |

|

SU884144A1 |

| Цифровой измеритель составляющих комплексных сопротивлений | 1987 |

|

SU1456907A1 |

| Фазометр | 1990 |

|

SU1797076A1 |

| Двухчастотный генератор для лечения заболеваний методом Немека | 1990 |

|

SU1823129A1 |

| Устройство автоматической подстройки линейного закона частотной модуляции | 1984 |

|

SU1218463A1 |

Изобретение относится к радиотехнике. Цель изобретения - повышение точности формирования выходных сигналов. Формирователь содержит задающий г-р 1, RS-триггер 2, эл-ты 2И-НЕ 3 и 15, реверсивный счетчик 4, ДАЛ 5, блок коммутируемых весовых сопротивлений (ВВС) 6, дешифратор 7, управля- емьш источник 8 тока, усилитель 9, управляемый инвертор 10, эл-т ИЛИ П, эл-т НЕ-И-НЕ 12, счетный триггер 13, ключ 14 и резистор 16. На выходе ЦАП 5 формируется ступенчатое напряжение. При последовательном шунтировании выхода ЦАП 5 соответствующим резистором ВВС 6 уменьшается величина ступеней аппроксимации соответствующей хорды синусоиды, т.е. угол наклона аппроксимируемой прямой, и в устройстве осуществляется последовательное формирование хорд синусоиды. При переключении счетчика 4 из ( режима суммирования в режим вычитания ключи ВВС 6, источника 8 и ЦАП 5 . начинают переключаться в обратном порядке и, следовательно, угол наклона хорд синусоиды изменится на отри- дательный. Т. обр., осуществляются циклы формирования периода синусоидального напряжения. 4 ил. Si (Л

uz.t

8ш

Выл

| Цифровой синтезатор частот | 1979 |

|

SU813677A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| В.В.Смеляков | |||

| Цифровая измерительная аппаратура инфранизких частот | |||

| М.: Энергия, 1975, с | |||

| Аппарат для радиометрической съемки | 1922 |

|

SU124A1 |

Авторы

Даты

1988-10-07—Публикация

1986-07-09—Подача