Изобретение относится к радиотехнике и может быть использовано для передачи цифровой информации.

Цель изобретения - повышение помехоустойчивости.

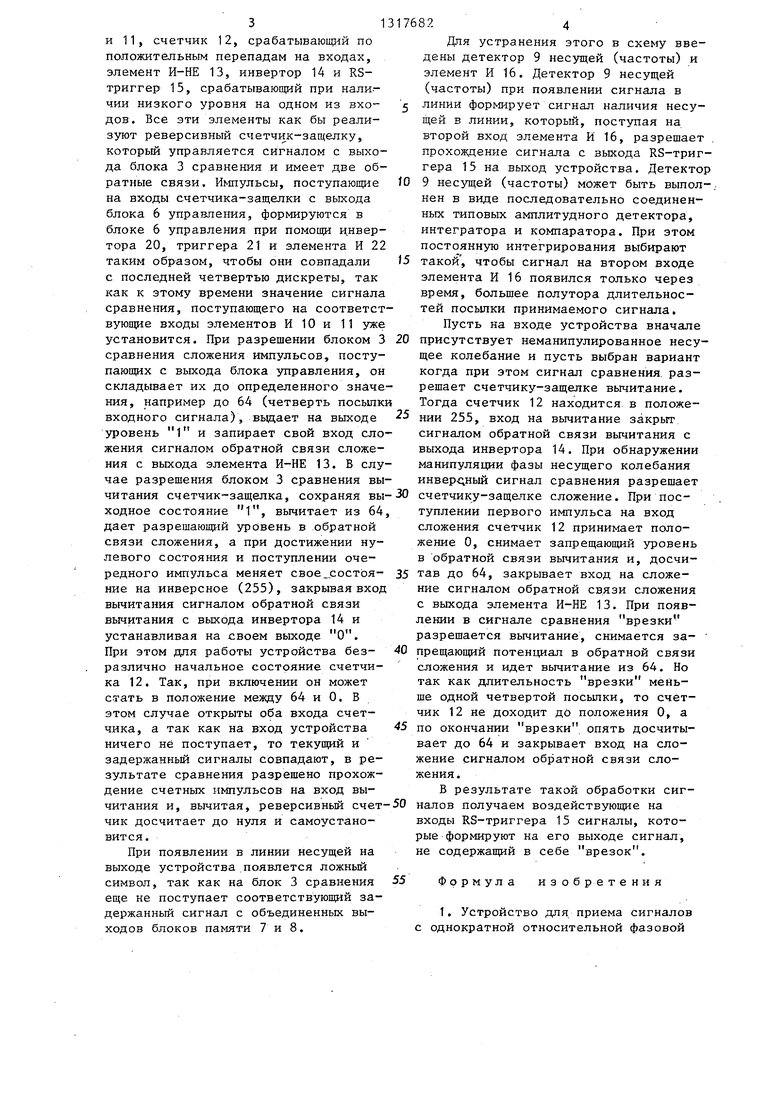

На фиго1 изображена структурная электрическая схема предлагаемого устройства; на фиг.2 - структурная электрическая схема блока -управления Устройство содержит блок 1 согласования, D-триггер 2, блок 3 сравнения, первый инвертор 4, ге нератор 5 тактовых импульсов, блок 6 управления, блоки 7 и 8 памяти, детектор 9 несущей, первьй и второй элементы И 10 и 11, счетчик 12, элемент И-НЕ 13 второй инвертор 14, RS-триггер 15 и третий элемент И 16.

Блок 3 состоит из инверторов 17 и 18 и элемента 2И-ИЛИ-НЕ 19.

Блок 6 управления состоит из инвертора 20, первого триггера 21, элемента И 22, второго триггера 23 и счетчиков 24 и 25.

Устройство работает следующим образом.

Входной сигнал подают на блок 1 согласования с линией и преобразуют в прямоугольные импульсы.

Рассмотрим случай когда частота несущего колебания принимаемого сигнала равна скорости передачи посыло а манипуляция фазы производится в момент начала периода несущего колебания .

Особенностью сигнала является наличие врезок, вызванных присутствующими в линии помехами. Эти врезки могут появляться в любой момент времени на фронтах или в середин импульсов и приводят при демодуляци сигнала к ошибкам.

Устройство для приема сигналов с однократной относительной фазовой манипуляцией осуществляет цифровую обработку сигнала. Управление работой устройства происходит с помощью блока 6 управления, на вход которог поступают тактовые импульсы от генератора 5. .Частоту следования этих импульсов выбирают много большей чатоты несущего колебания принятого сигнала, а именно frrn нм например fr.rn 512 ,ц , Эти импульсы, пройдя через инвертор 20 и триггер 21 блока 6 управления, поступают, будучи поделенными на RBB, на счетный ВХОД D-триггера 2, на ин

5

0

5

формационньм вход которого подают сигнал с выхода блока 1 согласования с линией. D-триггер 2 производит привязку входного сигнала к положительным фронтам импульсов, поступающих на его счетный вход.

С выхода 1)триггера привязанный к тактовой частоте сигнал поступает на один из входов блока 3 сравнения, на другой вход которого подают сигнал с объединенных выходов блоков памяти 7 и 8„ На вход блоков памяти. 7 и 8 поступают сигналы с выхода D-триггера 2„ Блоки памяти 7 и 8 осуществляют задержку сигнала на время, равное длительности посьшки принимаемого сигнала,, Дпя этого блоки памяти 7 и 8 работают поочередно: один - на запоминание, другой - на считывание. Переключение релсима работы произво дится через время, равное длительности посылки принимаемого сигнала, и определяется работой триггера 23 блока 6 управления и счетчиками 24 и 25, включенны ш: последовательно и работающими циклично. Счетчики 24 и 25 задают также ячеек блоков памяти 7 и 8. Согласно принятой тактовой xiacTOTe счетчики 24 и 25 выполнены четьгоехразрядными, что соответствует делению посьшки входного сигнала на 256 дискрет. Счетные импульсы на вход счетчика 24, -срабатывающего по отрицательному фронту входных импульсов,, 5 и на вход разрещения выборки блоков памяти 7 и 8 поступают с инверсного выхода триггера 2 i. Б результате адреса меняются синхронно с привязкой входного сигнала, а именно под О положительны фронт тактовых импульсов, поступающих на. счетный вход, D-триггера 2, тогда как запись и считывание производятся в блоках памяти 7 и 8 под отрицательный фронт этих 5 же импульсов., т.е. в середине дискре - ты, когда значения адреса и сигнала на входе уже установились.

Таким образом блок 3 сравнения производит сравнение сигнала сиыхо- 50 да D-триггера 2 и задержанного сигнала с объединенного выхода блоков памяти 7 и 8. Блок 3. с1эавнения реализует функцию равнозначности, т.е. при совпадении сигналов на входе на вы- 55 ходе появляется 1,

Предлагаемое устройство позволяет нейтрализовать воздействие помех. Дпя этого используются элементы И 10

0

JO

и 11, счетчик 12, срабатывающий по положительным перепадам на входах, элемент И-НЕ 13, инвертор 14 и RS- триггер 15, срабатывающий при наличии низкого уровня на одном из входов . Все эти элементы как бы реализуют реверсивный счетчик-защелку, которьй управляется сигналом с выхода блока 3 сравнения и имеет две обратные связи. Импупъсы, поступающие на входы счетчика-защелки с выхода блока 6 управления, формируются в блоке 6 управления при помощи и,нвер- тора 20, триггера 21 и элемента И 22 таким образом, чтобы они совпадали с последней четвертью дискреты, так как к этому времени значение сигнала сравнения, поступающего на соответствующие входы элементов И 10 и 11 уже установится. При разрешении блоком 3 20 сравнения сложения импульсов, поступающих с выхода блока з равления, он складывает их до определенного значения, например до 64 (четверть посыпки входного сигнала), вьдает на выходе уровень 1 и запирает свой вход сложения сигналом обратной связи сложения с выхода элемента И-НЕ 13. В случае разрешения блоком 3 сравнения выДля устранения этого в схему вве дены детектор 9 несущей (частоты) и элемент И 16. Детектор 9 несущей (частоты) при появлении сигнала в линии формирует сигнал наличия несу щей в линии, которыЛ, поступая на второй вход элемента И 16, разрешае прохоявдение сигнала с выхода RS-три гера 15 на выход устройства. Детект 9 несущей (частоты) может быть выпол нен в виде последовательно соединен ных типовых амплитудного детектора, интегратора и компаратора. При этом постоянную интегрирования выбирают такой, чтобы сигнал на втором входе элемента И 16 появился только через время, большее полутора длительностей посьики принимаемого сигнала.

Пусть на входе устройства вначале присутствует неманипулированное несу щее колебание и пусть выбран вариант когда при этом сигнал сравнения, разрешает счетчику-защелке вычитание. Тогда счетчик 12 находится в положении 255, вход на вычитание закрыт сигналом обратной связи вычитания с выхода инвертора 14. При обнаружении манипуляции фазы несущего колебания инвер ;ный сигнал сравнения разрешает

15

читания счетчик-защелка, сохраняя вы-30 счетчику-защапке сложение. При посходное состояние 1, вычитает из 64, дает разрешающий уровень в обратной связи сложения, а при достижении нулевого состояния и поступлении очередного импульса меняет свое „состоя- 35 ние на инверсное (255), закрывая вход вычитания сигналом обратной связи вычитания с выхода инвертора 14 и устанавливая на своем выходе О. При этом дпя работы устройства без- 40 различно начальное состояние счетчика 12. Так, при включении он может стать в положение между 64 и 0. В этом случае открыты оба входа счетчика, а так как на вход устройства 45 ничего не поступает, то текущий и задержанный сигналы совпадают, в результате сравнения разрешено прохождение счетных импульсов на вход вытуплении первого импульса на вход сложения счетчик 12 принимает положение О, снимает запрещающий уровень в обратной связи вычитания и, досчитав до 64, закрывает вход на сложение сигналом обратной связи сложения с выхода элемента И-НЕ 13. При появлении в сигнале сравнения врезки разрешается вычитание, снимается запрещающий потенциал в обратной связи сложения и идет вычитание из 64. Но так как длительность врезки меньше одной четвертой посылки, то счетчик 12 не доходит до положения О, а по окончании врезки опять досчитывает до 64 и закрывает вход на сложение сигналом обратной связи сложения.

В результате такой обработки сигчитания и, вычитая, реверсивньм счет-50 налов получаем воздействующие на

чик досчитает до нуля и самоустановится.

При появлении в линии несущей на выходе устройства появлется ложньш символ, так как на блок 3 сравнения еще не поступает соответствуюш й задержанный сигнал с объединенных выходов блоков памяти 7 и 8.

JO

203176824

Для устранения этого в схему введены детектор 9 несущей (частоты) и элемент И 16. Детектор 9 несущей (частоты) при появлении сигнала в линии формирует сигнал наличия несущей в линии, которыЛ, поступая на второй вход элемента И 16, разрешает прохоявдение сигнала с выхода RS-триг- гера 15 на выход устройства. Детектор 9 несущей (частоты) может быть выпол-, нен в виде последовательно соединенных типовых амплитудного детектора, интегратора и компаратора. При этом постоянную интегрирования выбирают такой, чтобы сигнал на втором входе элемента И 16 появился только через время, большее полутора длительностей посьики принимаемого сигнала.

Пусть на входе устройства вначале присутствует неманипулированное несущее колебание и пусть выбран вариант когда при этом сигнал сравнения, разрешает счетчику-защелке вычитание. Тогда счетчик 12 находится в положении 255, вход на вычитание закрыт сигналом обратной связи вычитания с выхода инвертора 14. При обнаружении манипуляции фазы несущего колебания инвер ;ный сигнал сравнения разрешает

15

туплении первого импульса на вход сложения счетчик 12 принимает положение О, снимает запрещающий уровень в обратной связи вычитания и, досчитав до 64, закрывает вход на сложение сигналом обратной связи сложения с выхода элемента И-НЕ 13. При появлении в сигнале сравнения врезки разрешается вычитание, снимается запрещающий потенциал в обратной связи сложения и идет вычитание из 64. Но так как длительность врезки меньше одной четвертой посылки, то счетчик 12 не доходит до положения О, а по окончании врезки опять досчитывает до 64 и закрывает вход на сложение сигналом обратной связи сложения.

В результате такой обработки сигвходы RS-триггера 15 сигналы, которые формируют на его выходе сигнал, не содержащий в себе врезок.

Формула изобретения

1. Устройство для приема сигналов с однократной относительной фазовой

W

манипуляцией, содержащее блок согласования, генератор тактовых импульсов, блок управления, блок сравнения, первьй инвертор, два элемента И, второй инвертор, выход которого соединен 5 с R-входом RS-триггера, отличающееся тем, что, с целью повышения помехоустойчивости, в него введены детектор несущей., D-триггер, два блока памяти, счетчик, элемент И-НЕ и третий элемент И, причем выход блока согласования сое динен с D-входом D-триггера, С-вход которого соединены с первым выходом блока управления, вход которого соединен с выходом генератора тактовых импульсов, второй выход блока управления соединен с первым входом первого блока памяти, третий выход блока управления соединен с первым входом вто- 20 рого блока памяти, четвертьм и пятый выходы блока управления соединены соответственно с объединенными вторыми и объединенными третьими входами пер15

ментов И соединены с соответствующими входами счетчика, первый выход которого соединен с первым входом элемента И-НЕ, второй вход которого соединен с выходом второго инверто™ ра, вход которого соединен с вторым выходом счетчика.

2.Устройство по П.1, отличающееся тем, что блок срав- .нения состоит из двух инверторов и элемента 2И-И11И-НЕ, причем вход первого инвертора соединен с первым входом элемента 2И-ИЛИ-НЕ и является первым входом блока сравнения, выход первого инвертора соединен с вторым входом элемента 2И-ИЛИ-НЕ, вход второго инвертора объединен с треть им входом элемента 2И-ИЛИ-НЕ и является вторым входом блока сравнения, выход второго инвертора соединен с четвертым входом элемента 2И-ИЛИ-НЕ, выход которого является выходом блока сравнения,

3.Устройство по П.1, о т л и вого и второго блоков памяти, четвер- 5 чающееся тем, что блок управтые входы которых соединены с выхо-. дом D-триггера, подключенным к первому входу блока сравнения, второй вход которого соединен с выходами первого и второго блоков памяти, выход блока сравнения через первый инвертор соединен с первым входом первого элемента И, второй вход которого соединен с выходом элемента И-НЕ, подключенным к S-входу RS-триггера, выход которого соединен с первым входом третьего элемента И, второй вход которого соединен с выходом детектора несущей, вход которого соединен с

входом блока согласования, выход вто- 40 вующий вход первого счетчика соединен

рого инвертора соединен с первым входом второго элемента И, второй вход которого соединен с выходом блока сравнения, третьи входы первого и второго элементов И объединены и со- единены с шестым;выходом блока управления, выходы первого и второго эле

5 0

5

ментов И соединены с соответствующими входами счетчика, первый выход которого соединен с первым входом элемента И-НЕ, второй вход которого соединен с выходом второго инверто™ ра, вход которого соединен с вторым выходом счетчика.

2.Устройство по П.1, отличающееся тем, что блок срав- .нения состоит из двух инверторов и элемента 2И-И11И-НЕ, причем вход первого инвертора соединен с первым входом элемента 2И-ИЛИ-НЕ и является первым входом блока сравнения, выход первого инвертора соединен с вторым входом элемента 2И-ИЛИ-НЕ, вход второго инвертора объединен с треть им входом элемента 2И-ИЛИ-НЕ и является вторым входом блока сравнения, выход второго инвертора соединен с четвертым входом элемента 2И-ИЛИ-НЕ, выход которого является выходом блока сравнения,

3.Устройство по П.1, о т л и 5 чающееся тем, что блок управления состоит из инвертора, элемента И, двух триггеров и двух счетчиков, причем вход инвертора объединен с первым входом элемента И и является

30 входом блока з равления, выход инвертора соединен с входом первого триггера, прямой вькод которого является первым выходом блока управления, инверсньй выход первого тригге35 ра соединен с вторым входом элемента И, входом первого счетчика и является четвертым выходом блока управления, вькоды счетчиков являются пятым выходом блока управления, соответстс входом второго счетчика, соответст- в ующий выход которого соединен с входом второго триггера, прямой и инверсный выходы которого являются соответственно вторым и третьим выходами блока управления, шестым выходо которого является выход элемента И.

О

23

О

25

20

21

22

Составитель Н.Лазарева Редактор А.Лежнина Техред В.Кадар. . Корректор Г.Решетник

Заказ 2437/56 Тираж 638Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г.Ужгород, ул.Проектная, 4

J

t k

Juti

8

А8рес

Ю

П

фие.2

| название | год | авторы | номер документа |

|---|---|---|---|

| Стенд для испытания энергоустановок электромобилей | 1985 |

|

SU1255890A1 |

| Электропривод постоянного тока | 1990 |

|

SU1741247A1 |

| Устройство для измерения угла закручивания вращающегося вала | 1991 |

|

SU1795312A1 |

| УСТРОЙСТВО ДЛЯ СЧЕТА ЦЕЛЫХ ФАЗОВЫХ ЦИКЛОВ | 1991 |

|

RU2022279C1 |

| Устройство для измерения параметров вращения ротора в переходных режимах | 1983 |

|

SU1352369A1 |

| Устройство контроля витковых замыканий в обмотке ротора электрической машины | 1992 |

|

SU1831744A3 |

| Устройство для выделения кадровых синхроимпульсов | 1984 |

|

SU1197143A1 |

| Цифровой фазометр мгновенных значений | 1985 |

|

SU1270718A1 |

| Цифровой измеритель центра тяжести видеосигналов | 1990 |

|

SU1723559A1 |

| Самонастраивающееся устройство управления | 1983 |

|

SU1130830A1 |

Изобретение может использоваться для передачи цифровой информации. Цель изобретения - повьшение помехоустойчивости . Устройство содержит блок 1 согласования, D-триггер 2, блок 3 сравнения, инверторы 4, 14, 17, 18, г-р 5 тактовых импульсов, .блок 6 управления, блоки 7 и 8 памяти, детектор 9 несущей, эл-ты И 10, 11, 16, счетчик 12, зл-т И-НЕ 13, RS-триггер 15, эл-т 2 И-ИЛИ-НЕ 19. Для нейтрализации помех используются эл-ты И 10 и 11, счетчик 12, срабатывающий по положительным перепадам на входах, эл-т И-НЕ 13, инвертор 14 и RS-триггер, срабатывающий при наличии низкого уровня на одном из входов . Эти эл-ты как бы реализуют ре- вер сив ньй счетчик-защелку, к-рый управляется сигналом с блока 3 и имеет две обратные связи. В п.2 ф-лы дается устр-во блока 3. В п.З ф-лы дается устр-во блока 6. 2 з.п. ф-лы. 2 ил. i (Л 00 9д

| Устройство для демодуляции фазоманипулированного сигнала | 1981 |

|

SU1054923A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1987-06-15—Публикация

1985-10-02—Подача