10

f5

20

t1318921

Изобретение относится к области радиотехники и может быть использовано в измерителях коэффициента стоя - чей волны в СВЧ-технике, а также схемах спектрометров и спектрофотометров.

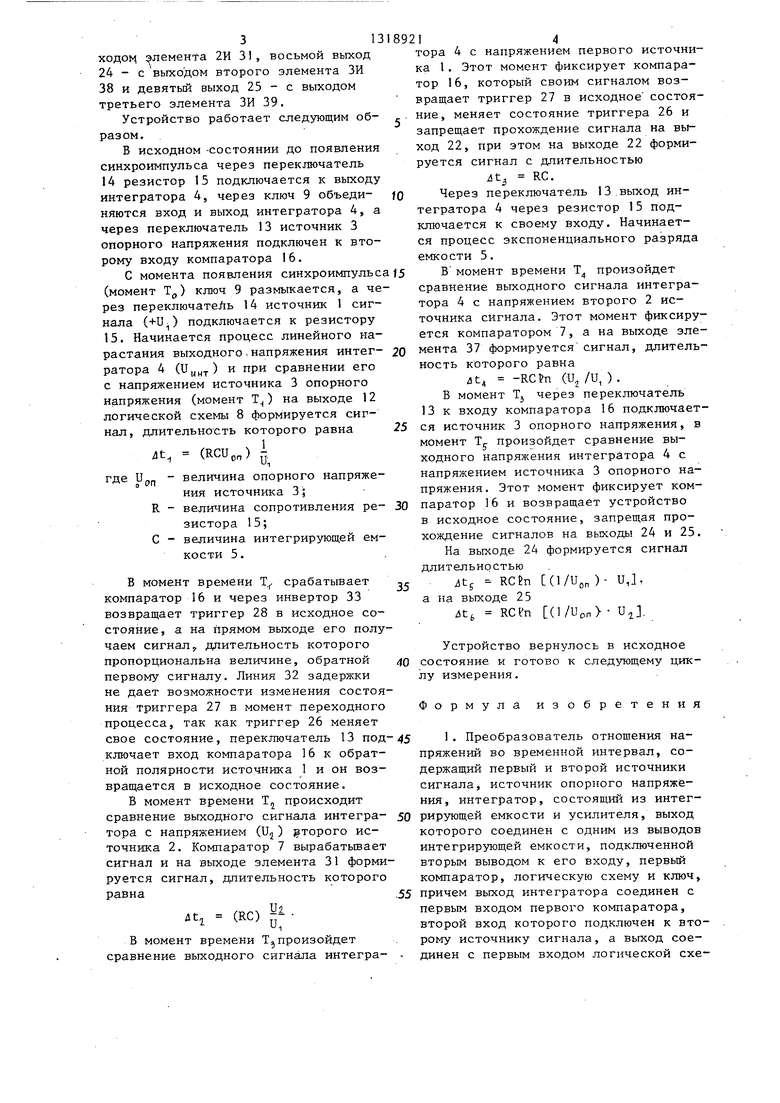

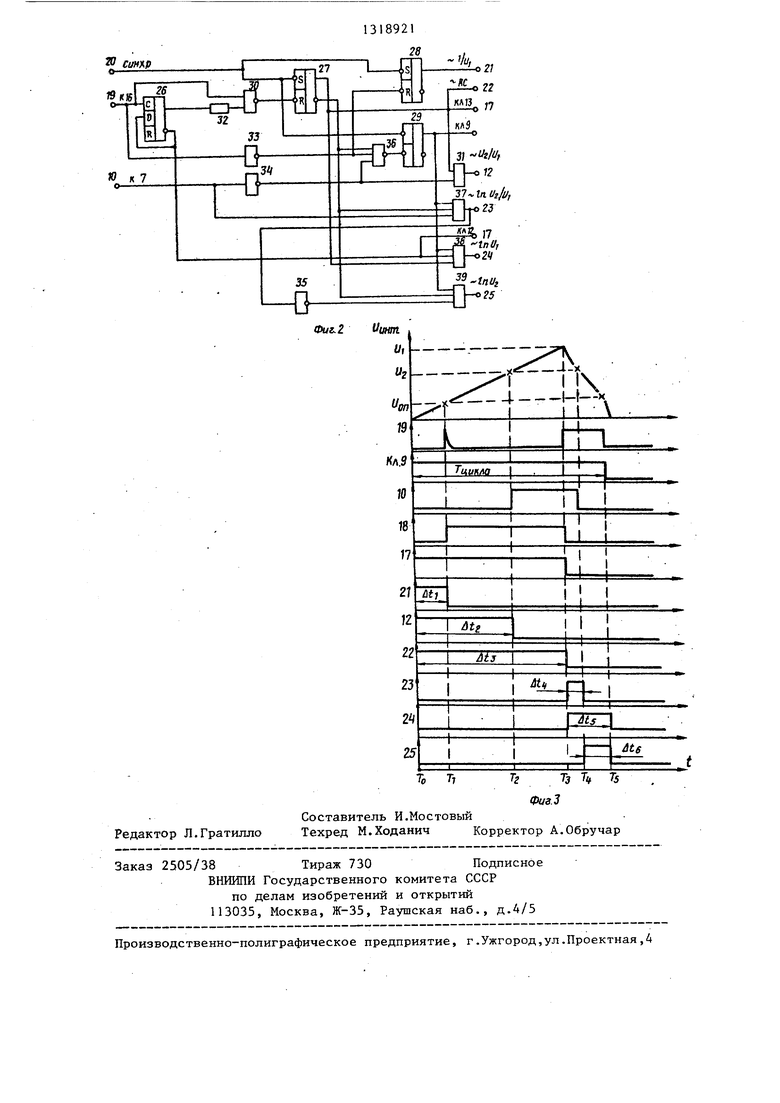

Целью изобретения является расширение функциональных возможностей за счет одновременного измерения отношения напряжений, величины, обратной одному из напряжений, логарифма отношения напряжений, постоянной времени измерительной цепи и логарифмов каждого из входных напряжений. На фиг.1 приведена структурная схема устройства; на фиг.2 - вариант реализации логической схемы; на фиг.З - временная диаграмма работы устройства (Т J моменты времени срабатывания компараторов. Т,, - момент времени появления синхроимпульса) .

Устройство содержит первый 1 и второй 2 источники , источник 3 опорного напряжения, интегратор 4, состоящий из интегрирующей емкости 5 и усилителя 6, выход которого соединен с первым выводом интегрирующей емкости 5, подключенной вторым выводом к его входу, первый компаратор 7, логическую схему 8 и ключ 9, причем выход интегратора 4 соединен с пер- вым входом первого компаратора 7, второй вход которого подключен к вто- j рому 2 источнику сигнала, а его выход подключен к первому 10 входу логической схемы 8, первый 11 выход которой подключен к управляющему входу ключа 9,. а второй выход является первым J2 выходом устройства. Устройство содержит также первый 13 и второй 14 переключатели, резистор 15, второй компаратор 16, причем первый вход первого переключателя 13 подключен к

40

в в в

х

30

25 т м ч пр ин св и пе то ед пе ры вт ко ты 45 ро эл со ЗИ ра 50 вы во со до то

клемме минус первого 1 источника сигнала, клеммой плюс подключенного к первому входу второго переключателя 14, второй вход которого подключен к выходу интегратора 4, первому входу второго компаратора 16 и входу ключа 9, выход которого соединен с входом интегратора 4 и через резистор 15 с выходом второго переключателя 14, управляющий вход которо- 55 третьего элемента ЗИ 39, R-вход втого соединен с третьим 17 выходом логической схемы 8, четвертый 18 выход которой соединен с управляющим входом первого переключателя 13, второй

рого триггера 27 соединен с выходом элемента 2И-НЕ 30; пятый выход 21 соединен с прямым выходом третьего триггера 28, второй выход 12 - с вы

вход которого соединен с источником 3 опорного напряжения, а выход - с вторым входом второго компаратора 16, выход которого подключен к второму

19входу логической схемы 8, третий

20вход которой соединен с шиной синхронизации, а с пятого по девятый 21-25 выходы ее являются выходами устройства.

5

0

0

0

Логическая схема 8 состоит из первого 26, второго 27, третьего 28 И четвертого 29 триггеров, элемента 2И-НЕ 30, элемента 2И 31, линии 32 задержки, первого 33, второго 34 и третьего 35 инверторов, элемента ЗИ-НЕ 36 и первого 37, второго 38 и третьего 39 элементов ЗИ, причем третий вход 20 соединен с S-входами второго 27, третьего 28 и четвертого 29 триггеров, второй вход 19 соединен с входом первого инвертора 33, выход которого соединен с вторым вхо-- дом элемента ЗИ-НЕ 36 и R-входом 5 третьего триггера 28, G-входом первого триггера 26 и первым входом элемента 2И-НЕ 30, второй вход которрго, через линию 32 задержки соединен с прямым выходом первого триггера 2Ь, инверсный выход которого соединен со своим D-входом, четвертым выходом 18 и вторым входом второго элемента ЗИ 38, первый вход которого соединен с первым входом первого 37 и третьего 39 элементов ЗИ, первым выходом 11 (на ключ 9) и прямьи выходом четвертого 29 триггера, R-вход которого соединен с выходом элемента ЗИ-НЕ 36, первьш вход которого соединен с вторыми входами первого 37 и третьего 39 элементов ЗИ и инверсным выходом второго триггера 27, прямой выход которого соединен с третьим 17 и шестым 22 выходами, третьим входом вто- 5 рого 38 элемента ЗИ и первым входом элемента 2И 31, второй вход которого соединен с третьим входом элемента ЗИ-НЕ 36 и выходом второго инвертора 34, вход которого соединен с пер- 0 вым входом 10 и третьим входом первого элемента ЗИ 37, выход которого соединен с седьмым выходом 23 и входом третьего инвертора 35, выход которого соединен с третьим входом

рого триггера 27 соединен с выходом элемента 2И-НЕ 30; пятый выход 21 соединен с прямым выходом третьего триггера 28, второй выход 12 - с выХОДОЦ элемента 2И 3), восьмой выход 24 - с выходом второго элемента ЗИ 38 и девятый выход 25 - с выходом третьего элемента ЗИ 39.

Устройство работает следующим об- разом.

В исходном -состоянии до появления синхроимпульса через переключатель 14 резистор 15 подключается к выходу интегратора 4, через ключ 9 объеди- няются вход и выход интегратора 4, а через переключатель 13 источник 3 опорного напряжения подключен к второму входу компаратора 16.

С момента появления синхроимпульс (момент Тд) ключ 9 размыкается, а через переключатель 14 источник 1 сигнала (+и) подключается к резистору 15. Начинается процесс линейного нарастания выходного.напряжения интег- ратора 4 (U) и при сравнении его с напряжением источника 3 опорного напряжения (момент Т) на выходе 12 логической схемы 8 формируется сигнал, длительность которого равна

At, (КСи,„) Iгде и

оп

Ui

величина опорного напряжения источника 3;

R - величина сопротивления ре- зистора 15;

С - величина интегрирующей емкости 5.

В момент времени Т. срабатывает компаратор 16 и через инвертор 33 возвращает триггер 28 в исходное состояние, а на прямом выходе его получаем сигнал у длительность которого пропорциональна величине, обратной первому сигналу. Линия 32 задержки не дает возможности изменения состояния триггера 27 в момент переходного процесса, так как триггер 26 меняет свое состояние, переключатель 13 под ключает вход компаратора 16 к обратной полярности источника 1 и он возвращается в исходное состояние.

В момент времени Т происходит сравнение выходного сигнала интегра- тора с напряжением (Uj) gToporo источника 2. Компаратор 7 вырабатывает сигнал и на выходе злемента 31 формируется сигнал, длительность которого равна

At (RC) J{- - 1

В момент времени Т,произойдет сравнение выходного сигнала интегра- тора 4 с напряжением первого источника 1. Этот момент фиксирует компаратор 16, который своим сигналом возвращает триггер 27 в исходное состояние, меняет состояние триггера 26 и запрещает прохождение сигнала на выход 22, при этом на выходе 22 формируется сигнал с длительностью At RC.

Через переключатель 13 выход интегратора 4 через резистор 15 подключается к своему входу. Начинается процесс экспоненциального разряда емкости 5.

В момент времени Т произойдет сравнение выходного сигнала интегратора 4 с напряжением второго 2 источника сигнала. Этот момент фиксируется компаратором 7, а на выходе элемента 37 формируется сигнал, длительность которого равна

dt -RCb (U /и,).

В момент Tj через переключатель 13 к входу компаратора 16 подключается источник 3 опорного напряжения, в момент TJ произойдет сравнение выходного напряжения интегратора 4 с напряжением источника 3 опорного напряжения. Этот момент фиксирует компаратор 16 и возвращает устройство в исходное состояние, запрещая прохождение сигналов на выходы 24 и 25.

На выходе 24 формируется сигнал длительностью

4tj RCEn (1/и,„ )- и,, на выходе 25

utf, RCVn (l/Uon .

Устройство вернулось в исходное состояние и готово к следующему циклу измерения.

Формула изобретения

1. Преобразователь отношения напряжений во временной интервал, содержащий первый и второй источники сигнала, источник опорного напряжения, интегратор, состоящий из интегрирующей емкости и усилителя, выход которого соединен с одним из выводов интегрирующей емкости, подключенной вторым выводом к его входу, первый компаратор, логическую схему и ключ, причем выход интегратора соединен с первым входом первого компаратора, второй вход которого подключен к второму источнику сигнала, а выход соединен с первым входом логической схе513

мы, первый выход которой подключен к управляющему входу ключа, а второй выход является первым выходом преобразователя, отличающийся тем, что, с целью расширения функциональных возможностей за счет одновременного измерения отношения напряжений, величины, обратной одному из напряжений, логарифма отношения напряжений, постоянной времени измерительной цепи и логарифмов обоих входных напряжений, в него введены первый и второй переключатели, резистор, второй компаратор, причем первый вход iepBoro переключателя подключен к клемме минус первого источника сиг- нала,подключенного клеммой плюс к первому входу второго переключателя, второй вход которого подключен к выходу, интегратора, первому входу второго компаратора и входу ключа, выход которого соединен с входом интегратора и через резистор с выходом второго переключателя, управляющий вход которого соединен с третьим выходом логической схемы, четвертый выход которой соединен с управляющим входом первого переключателя, второй вход которого соединен с источником опорного напряжения, а выход - с вторым входом второго компаратора, выход которого подключен к второму входу логической схемы, третий вход которой соединен с шиной синхронизации, а с пятого по девятый выходы ее явля ются с второго по шестой выходами преобразователя соответственно.

2. Преобразователь по п.1, о т - личагощийся тем, что логическая схема состоит из первого, второго, третьего и четвертого триггеров элемента 2И-НЕ, элемента 2И, линии задержки, первого, второго и третьего инверторов, элемента ЗИ-НЕ и первого, второго и третьего элементов

16

ЗИ, причем третий вход логической схемы соединен с S-входами второго, третьего и четвертого триггеров, второй вход соединен с входом первого

инвертора, выход которого соединен с вторым входом элемента ЗИ-НЕ и R-BXO- дом третьего триггера, С-входом первого триггера и первым входом элемента 2И-НЕ, второй вход которого

через линию задержки соединен с прямым выходом первого триггера, инверсный выход которого соединен со своим D-входом, четвертым выходом логической схемы и вторым входом второго

элемента ЗИ, первый вход которого соединен с первыми входами первого и третьего элементов ЗИ, первым выходом логической схемы и прямым выходом четвертого триггера, R-вход которого соединен с выходом элемента ЗИ-НЕ, первый вход которого соединен с вторыми входами первого.и третьего элементов ЗИ и инверсным выходом второго триггера, прямой выход которого

соединен с третьим и шестым выходами логической схемы, третьим входом второго элемента ЗИ и первым входом зле- мента 2И, второй вход которого соединен с третьим входом элемента

ЗИ-НЕ и выходом второго инвертора, вход которого соединен с первым входом логической схемы и третьим вхо дом первого элемента ЗИ, выход которого соединен с седьмым выходом ло- гической схемы и входом третьего инвертора, выход которого соединен с третьим входом третьего элемента ЗЙ, R-вход второго триггера соединен с выходом элемента 2И-НЕ, пятый выход

огической схемь: соединен с прямым

выходом третьего триггера, второй ыход - с выходом элемента 2И, восьой выход - с выходом второго элеента ЗИ и девятый выход - с выходом

третьего элемента ЗИ.

Фиг.2 УШИ Ui

Редактор Л.Гратилло

То Т, Гг Tj Т 75

Фаг.

Составитель И.Мостовый Техред М.Ходанич Корректор А.Обручар

Заказ 2505/38 Тираж 730Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д.4/5

Производственно-полиграфическое предприятие, г.Ужгород,ул.Проектная,А

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для моделирования вентильного преобразователя | 1981 |

|

SU968829A1 |

| Устройство измерения отклонения сопротивления от заданного значения | 1990 |

|

SU1737360A1 |

| Преобразователь экстремумов периодического сигнала в постоянное напряжение | 1989 |

|

SU1674002A1 |

| Преобразователь логарифма отношения напряжений во временной интервал | 1987 |

|

SU1559299A1 |

| Измеритель отношения двух сигналов | 1986 |

|

SU1465791A1 |

| Устройство для определения содержания связующего в стеклопластиках | 1984 |

|

SU1265538A1 |

| Стенд для диагностирования технического состояния транспортных средств | 1990 |

|

SU1744563A1 |

| Устройство для формирования частотно-манипулированных сигналов | 1983 |

|

SU1172058A1 |

| Преобразователь экстремумов периодического сигнала в постоянное напряжение "Галс-7 | 1987 |

|

SU1442926A1 |

| Цифровой измеритель температуры | 1990 |

|

SU1765719A1 |

Изобретение относится к радиотехнике и может быть использовано в измерителях коэффициента стоячей волны в СВЧ-технике. Цель изобретения - расширение функциональных возможностей преобразователя. Для этого в него введены переключатели 13, 14, резистор 15, компаратор 16. Преобразователь также содержит источники I и 2 сигнала, источник 3 опорного напряжения, интегратор 4, состоящий из интегрирующей емкости 5 и усилителя 6, компаратор 7, логическую схему 8, ключ 9, входы 10, 19 логической схемы и ее выходы 11, 12, 17, 18, 20 - 25. Цель достигается за счет измерения следующих параметров входного сигнала в течение одного цикла измерения: отношения напряжений, величины, обратной второму входному сигналу, постоянной времени измерительной цепи, логарифма отношения входных напряжений, логарифма каждого вход- . ного напряжения. 1 з.и. ф-лы, 3 ил. I (Л I2i Z/izzi 236 2«i 4 i г Г t. 5 s выходы устройства Фи&1

| Измеритель отношения напряжений | 1983 |

|

SU1150565A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Жилинскас Р.-П.П | |||

| Измерители отно- .шения и их применение в радиоизмерительной технике | |||

| М.: Советское радио, 1975, с | |||

| Раздвижной паровозный золотник со скользящими по его скалке поршнями и упорными для них шайбами | 1922 |

|

SU147A1 |

Авторы

Даты

1987-06-23—Публикация

1985-06-20—Подача