Изобретение относится к транспортному машиностроению и может быть использовано при оценке технического состояния двигателя и трансмиссии транспортного средства.

Известен стенд, с помощью которого определяются максимальная мощность на колесах в режиме стабилизации скорости и мощность потерь в трансмиссии при выбеге, при этом мощность двигателя равна сумме этих мощностей.

Недостатком данного стенда является низкая точность измерения мощности потерь в трансмиссии из-за низкой точности определения момента инерции вращающихся масс.

Известен стенд, позволяющий с достаточной точностью определять суммарную мощность потерь в трансмиссии и стенде в режиме выбега в два этапа.

Недостатком указанного стенда является сложность определения мощности двигателя, заключающаяся в том, что необходимо вначале определить максимальную тяговую мощность на колесах в режиме стабилизации скорости, затем потери в трансмиссии и в стенде и далее эти величины просуммировать.

Наиболее близким к предлагаемому по технической сущности является стенд, позволяющий с достаточной точностью определять мощность двигателя и потери в трансмиссии и стенде в три этапа: двух этапах разгона и этапе выбега, содержащий .опорные ролики, регулируемый тормоз, кинематически соединенный с опорными роликами, датчик частоты вращения опорных роликов с нормирующим преобразователем, датчик крутящего момента регулируемого тормоза с нормирующим преобразователем, регистрирующий прибор скбрости и дифференциатор, блок уставок, три компаратора, сигнализирующее устройство, систему автоматического регулирования, где между усилителем рассогласования и блоком управления силовыми элементами установлен переключатель, логический блок вычислительное устройство, регистрирующий прибор мощности, при этом логический блок содержит инвертор, три элемента 2 И, два элемента 2 И-НЕ, резистор и кнопку Сброс.

Кнопкой Сброс сбрасывается предыдущее замеренное значение мощности двигателя и схема переводится в исходное состояние.

Разгон транспортного средства начинается с постоянной нагрузкой М0. Постоянство нагрузки в трансмисии обеспечивается замкнутой системой автоматического регулирования, в которой сравнивается сигнал, поступающий с блока уставок, и сигнал обратной связи, поступающий с выхода нормирующего преобразователя датчика

крутящего момента. Разность сигналов усиливается усилителем рассогласования и через открытый переключатель и блок управления силовыми элементами поступает на управляющий элемент регулируемого

тормоза.

По достижении значения частоты вращения срабатывания первого компаратора в трех блоках памяти вычислительного устройства фиксируются значения дополнительной нагрузки М0, скорости ускорения Јi. В этот же момент переключатель системы автоматического регулирования размыкается и с управляющего элемента регулируемого тормоза снимается

сигнал, нагрузка, создаваемая тормозом, снимается. Дальнейший разгон осуществляется без дополнительной нагрузки М0. По окончании переходного процесса снятия нагрузки по достижении значения частоты

вращения срабатывания второго компаратора в четвертом блоке памяти вычислительного устройства фиксируется значение ускорения Ј2. По достижении значения частоты вращения срабатывания третьего компаратора включается сигнализирующее устройство Отключить двигатель и транспортное средство переводится в режим свободного выбега. При снижении частоты вращения -в момент отпускания первого

компаратора в пятом блоке памяти вычислительного устройства фиксируется значение замедления Јз.

Вычислительное устройство, используя значения М0, со, Јi, Ј2 и Јз , вычисляет значение мощности двигателя по формуле

N Мо(Ј1+Ј3)

Недостатком известного стенда является то, что этап разгона начинается с постоянной дополнительной нагрузкой М0. После сброса нагрузки в момент срабатывания первого компаратора начинается переходный процесс установления значения нового, большего ускорения разгона без

нагрузки,.что занимает определенное время, и чем больше это время, тем ниже точность измерения мощности. того, в, процессе измерения непрерывно изменяются показания на регистрирующих прибоpax, что вызывает неудобство считывания информации,

Цель изобретения - повышение точности диагностирования транспортного сред-.

ства, стабильности работы и удобства считывания информации.

Поставленная цель достигается тем, что в стенд, содержащий установленные на основании опорные ролики, регулируемый тормоз, кинематически соединенный с опорными роликами, датчик частоты вращения опорных роликов с нормирующим преобразователем, датчик крутящего момента регулируемого тормоза с нормирующим преобразователем, регистрирующий прибор скорости, дифферециатор, блок уставок, первый, второй и третий компараторы, систему автоматического регулирования, имеющую усилитель рассогласования, переключатель, первый вход которого соединен с выходом усилителя рассогласования, блок управления силовыми элементами, вход которого соединен с выходом переключателя, сигнализирующее устройство, логический блок, вычислительное устройство, регистрирующий прибор мощности, при этом логический блок содержит два элемента 2И-НЕ, два элемента 2Й, резистор, нормально открытый контакт, инвертор, введены два элемента ЗИ.

В предлагаемом стенде хотя логический блок и состоит из известных элементов 2И, ЗИ.2И-НЕ и инвертора, однако в указанной связи с остальными элементами схемы позволяет осуществить процесс разгона в два этапа в следующее последовательности. Вначале идет этап разгона без дополнительной нагрузки, а затем этап с дополнительной эталонной нагрузкой М0. Изменение порядка приложения нагрузки в предлагаемом стенде по сравнению с прототипом позволяет уменьшить время переходного процесса к установившемуся режиму второго этапа.

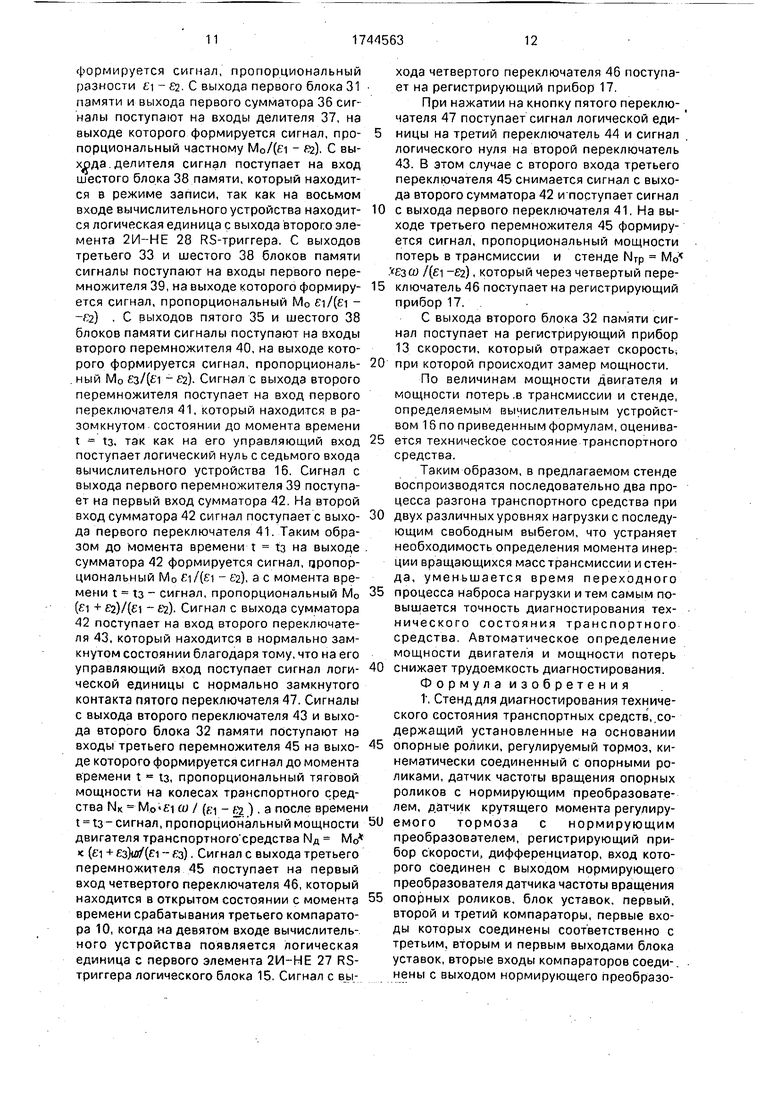

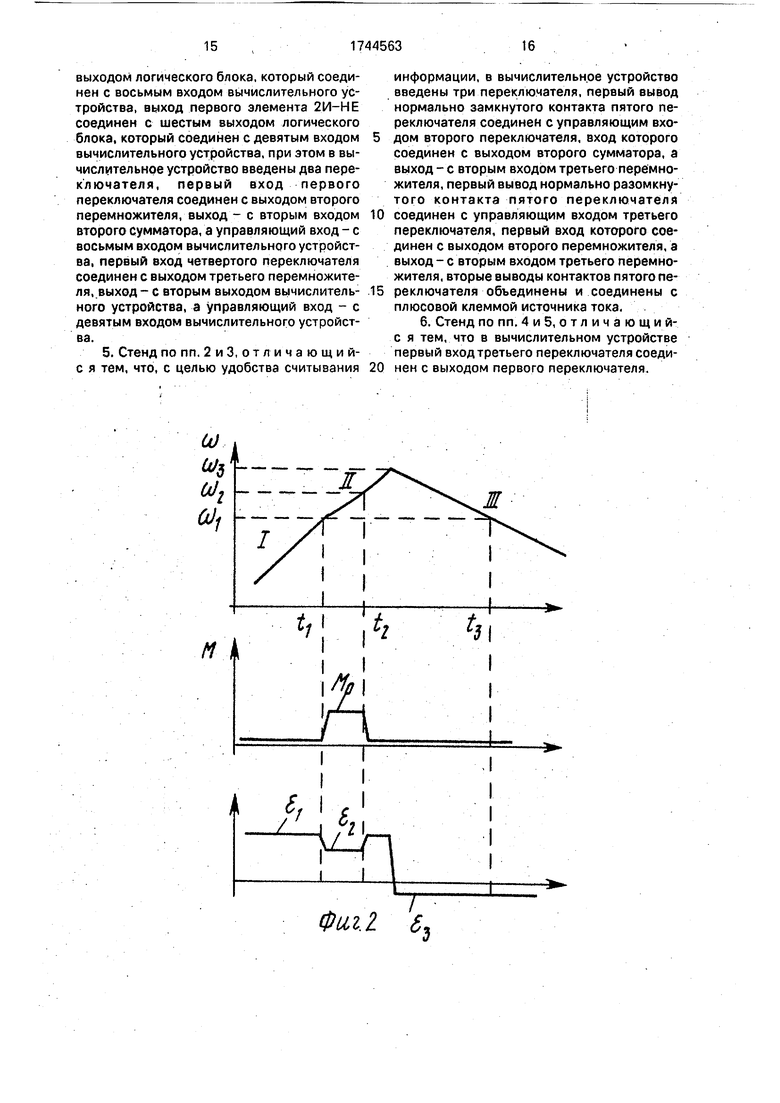

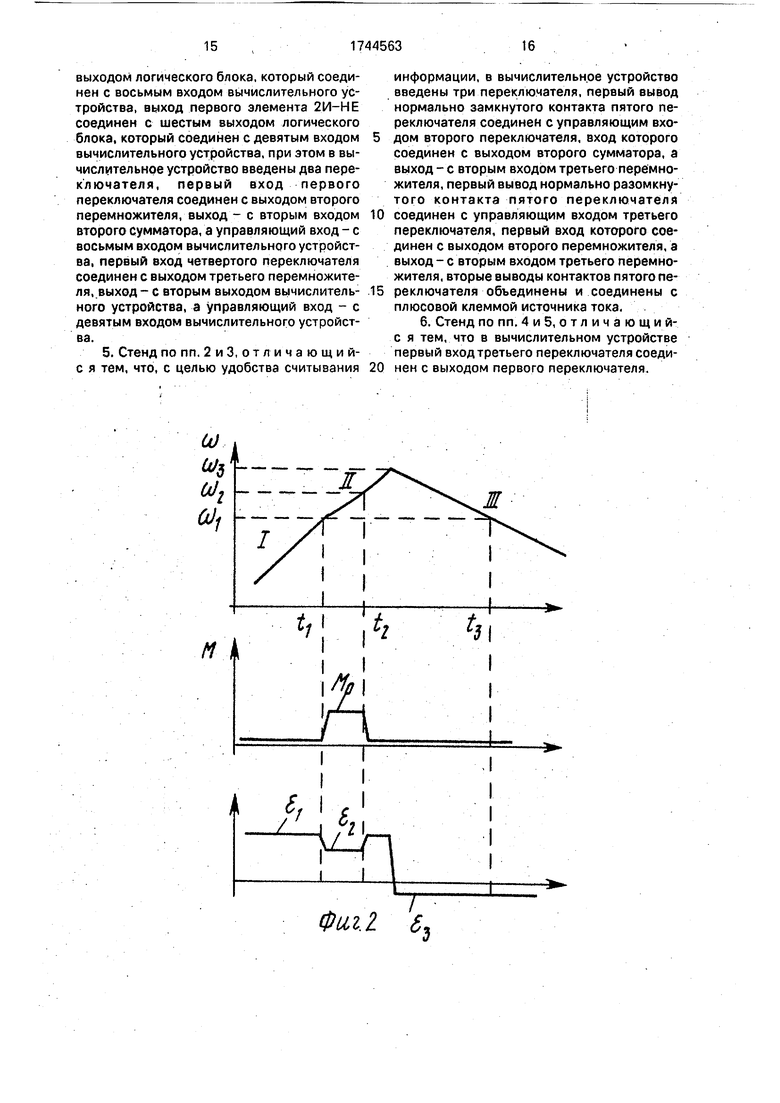

На фиг, 1 изображена структурная схе-. ма предлагаемого стенда; на фиг. 2 - график изменения частоты вращения СУ ведущих колес, нагрузки М на ведущих колесах и углового ускорения е ведущих колес от времени.

Стенд содержит установленные на основании ведущие 1 и поддерживающие 2 опорные ролики, регулируемый тормоз 3, кинематически соединенный с ведущими опорными роликами 1, датчик 4 частоты вращения опорных роликов с нормирующим преобразователем 5, датчик 6 крутящего момента регулируемого тормоза с нормирующим преобразователем 7, первый 8, второй 9 и третий 10 компараторы, блок 11 уставок, систему 12 автоматического регулирования, регистрирующий прибор 13 скорости, дифференциатор 14, логический блок

15, вычислительное устройство 16. регистрирующий прибо 17 мощности и сигнализирующее устройство 21.

Система 12 автоматического регулиро- 5 вания содержит усилитель 18 рассогласования, переключатель 19 и блок 20 управления силовыми элементами.

Логический блок 15 содержит первый элемент ЗИ 22, инвертор 23. второй эле- 0 ментЗИ 24, первый 25 и второй26 элементы 2И, RS-триггер на первом 27 и втором 28 элементах 2И-НЕ, резистор 29 и нормально открытый контакт (кнопку) 30 Сброс.

Вычислительное устройство содержит 5 первый 31, второй 32, третий 33, четвертый 34 и пятый 35 блоки памяти, первый сумматор 36, делитель 37, шестой блок 38 памяти, первый 39 и второй 40 перемножители, первый переключатель 41, второй сумматор 42, 0 второй 43 и третий 44 переключатели, третий перемножитель 45, четвертый переключатель 46 и пятый переключатель 47.

Блок 11 уставок представляет собой четыре резисторных делителя напряжения и 5 формирует напряжения, соответствующие

ШЗ, Ш2- И МоКомпараторы 8, 9 и 10 выполнены на базе интегральных микросхем и имеют на выходе сигнал, равный логической единице

0 при частоте вращения опорных роликов, меньшей соответствующей уставки.

Сигнализирующее устройство 21 представляет собой управляемый мультивибратор, на выходе которого включено световое

5 табло Отключить двигатель.

Переключатели 19,41, 44,45 и 47 выполнены на базе двунаправленных бесконтакт- ных переключателей в интегральном исполнении. Переключатель 49 представля0 ет собой кнопку, имеющую нормально закрытый и нормально открытый контакты.

Блоки памяти выполнены на схемах выборки-хранения, сумматоры - на операционных усилителях, делитель и перемно5 жители - на базе интегральной микросхемы аналогового перемножителя,

Выход нормирующего преобразователя 5 соединен с входом дифференциатора 14, вторыми входами первого 8, второго 9 и

0 третьего 10 компараторов и вторым входом вычислительного устройства 16. Выход дифференциатора 14 соединен с первым входом вычислительного устройства 16. Первый вход первого компаратора 8 соеди5 нен с третьим входом блока 11 уставок, первый вход второго компаратора 9 - с вторым выходом блока 11 уставок, первый вход третьего компаратора 10 - с первым выходом блока 11 уставок. Выход первого компа- ратора 8 соединен с первым входом

логического блока 15, выход второго компаратора 9 - с вторым входом логического блока 15, выход третьего компаратора 10 - с третьим входом логического блока 15 и входом сигнализирующего устройства 21. Выход нормирующего преобразователя 7 соединен с одним из входов усилителя 18 рассогласования и третьим входом вычислительного устройства 16. Четвертый выход блока 11 уставок соединен с другим входом усилителя 18 рассогласования, выход которого соединен с вторым входом переключателя 19. Управляющий вход переключателя 19 соединен с вторым выходом логического блока 15, а выход - с входом блока 20 управления силовыми элементами, выход которого соединен с входом управляющего элемента регулируемоготормозаЗ. Первый- шестой выходы логического блока 15 соединены соответственно с четвертым-девятым входами вычислительного устройства 16. Первый выход вычислительного устройства 16 соединен с регистрирующим прибором 13 скорости, а второй - с регистрирующим прибором 17 мощности.

В составе логического блока 15 его второй вход соединен с первым входом первого элемента ЗИ 22, выход которого соединен с вторым выходом логического блока 15. Первый вход логического блока 15 соединен с входом инвертора 23 и вторыми входами элементов 2И 25 и 26. Выход инвертора 23 соединен с вторыми входами элементов ЗИ 22 и 24. Третий вход логического блока 15 соединен с первым входом элемента 2И-НЕ 27 и первым входом второго элемента ЗИ 24. Третий вход элемента ЗИ 22 соединен с первым входом первого элемента 2И 25, вторым входом первого элемента 2И-НЕ 27, выходом второго элемента 2И-НЕ 28 и пятым выходом логического блока 15. Третий вход второго элемента ЗИ 24 соединен с первым входом второго элемента 2И 26, первым входом второго элемента 2И-НЕ 28, выходом первого элемента 2И-НЕ 27 и шестым выходом логического блока 15. Выход второго элемента ЗИ 24 соединен с третьим выходом логического блока 15. Выход первого элемента 2И 25 соединен с первым выходом логического блока 15. Выход второго элемента 2И 26 соединен с четвертым выходом логического блока 15. Второй вход второго элемента 2И-НЕ 28 через резистор 29 соединен с плюсовой клеммой источника тока. Нормально разомкнутый контакт (кнопка 30 Сброс) подключен к резистору 29 и минусовой клемме источника тока.

В составе вычислительного устройства 16 вход первого блока 31 памяти соединен с третьим входом вычислительного устройства 16, вход второго блока 32 памяти - с вторым входом вычислительного устройства 16, входы третьего 33, четвертого 34 и пятого 35 блоков памяти объединены и соединены с первым входом вычислительного устройства 16. Управляющие цепи второго 32 и третьего 33 блоков памяти соединены с четвертым входом вычислительного устройства 16. Управляющие цепи первого 31 и

четвертого 34 блоков памяти соединены с пятый входом вычислительного устройства 16. Управляющая цепь пятого блока 35 памяти соединена с шестым входом вычислительного устройства 16. Выход третьего

блока 33 памяти соединен с одним из входов первого сумматора 3-6 и первым входом первого перемножителя 39. Выход четвертого блока 34 памяти соединен с другим входом первого сумматора 36 . Выход первого блока 31 памяти соединен с одним из выходов делителя 37 Выход первого сумматора 36 соединен с другим входом делителя 37, выход которого соединен с входом шестого блока 38 памяти, выход которого соединен

с вторым входом перемножителя 39 и первым входом второго перемножителя 40. Управляющая цепь шестого блока 38 памяти соединена с восьмым входом вычислительного устройства 16 Выход пятого блока памяти соединен с вторым входом второго перемножителя 40. Выход первого перемножителя 39 соединен с первым входом второго сумматора 42, второй вход которого соединен с выходом первого переключателя

41, первый вход которого соединен с выходом второго перемножителя 40. Управляющая цепь первого переключателя 41 соединена с седьмым входом вычислительного устройства. Выход второго сумматора

соединен с первым входом второго переключателя 43, выход которого соединен с вторым входом перемножителя 45 и выходом третьего переключателя 44, вход которого соединен с выходом первого

переключателя 41. Управляющая цепь второго переключателя 43 соединена с одним выводом нормально замкнутого контакта пятого переключателя 47. Управляющая цепь третьего переключателя 44 соединена

с одним выводом нормально размокнутого контакта пятого переключателя 47. другие выводы контактов которого объединены и соединены с плюсовой клеммой источника тока. Выход второго блока 32 памяти соединен с первым входом третьего перемножителя 45 и первым выходом вычислительного блока 16. Выход третьего перемножителя 45 соединен с входом четвертого переключателя 46, выход которого соединен с вторым

выходом вычислительного устройства 16,

девятый вход которого соединен с управляющим входом четвертого переключателя 46.

Для определения мощности двигателя и потерь мощности в трансмиссии транспортное средство устанавливают ведущими колесами на опорные ролики 1 и 2, нажимают кнопку 30 Сброс, разгоняют транспортное средство до частоты вращения сиз, контролируемой датчиком 4 частоты вращения. Включается сигнализирующее устройство 21, которое подает световой сигнал Отключить двигатель, отключают двигатель транспортного средства от входного вала трансмиссии. При этом вращение трансмиссии происходит в режиме свободного выбега.

При нажатии кнопки 30 Сброс устанавливают RS-триггер на элементах 2 И-НЕ 27 и 28 в нулевое состояние, т.е. на первом выходе RS-триггера (выходе первого элемента 2И-НЕ 27) устанавливается логический нуль. Разгон транспортного средства начинается без нагрузки (участок I на фиг. 2). В процессе разгона на выходе дифференциатора 14 формируется сигнал, пропорциональный ускорению Ј ведущих колес транспортного средства, который поступает на входы третьего 33, четвертого 34 и пятого 35 блоков памяти вычислительного устройства.

Одновременно на входы второго 32 и первого 31 блоков памяти поступают сигналы соответственно с выхода нормирующего преобразователя 5 датчика 4 частоты вращения и с выхода нормирующего преобразователя 7 датчика 6 крутящего момента. Второй 32 и третий 33 блоки памяти находятся в режиме записи, так как на четвертый вход вычислительного устройства 16 поступает сигнал логической единицы с выхода второго элемента 2И 25, на выходы которого поступают сигналы логической единицы соответственно первого компаратора 8 и RS- триггера (с выхода второго элемента 2И-НЕ 28).

В процессе разгона в момент времени t ti при достижении значения частоты вращения ш- срабатывает первый компаратор 8 и на выходе первого элемента 2И 25 появляется сигнал логического нуля, что переводит второй 32 и третий 33 блоки памяти в режим хранения. На их выходах будут сигналы соответственно йл и Ј1 соответствующие моменту срабатывания первого компаратора 8. В этот же момент первый 31 и четвертый 34 блоки памяти переходят в режим записи, так как на пятый вход вычислительного устройства 16 поступает сигнал логической единицы с выхода первого элемента ЗИ 22, на входы которого поступают сигналы логической единицы соответственно второго компаратора 9, инвертора 23 (так как после срабатывания первого компаратора 8 на его выходе будет логический нуль) и RS-триггера (с выхода второго элемента 2И- НЕ 28). Сигнал логической единицы с второго выхода логического блока 15 поступает на управляющий вход переключателя 19, который соединяет выход усилителя 18 рассогласования с входом блока 20 управления силовыми элементами, что приводит к включению регулируемого тормоза 3. С момента времени t ц разгон транспортного средства осуществляется с дополнительной нагрузкой при включенном регулируемом тормозе 3 (участок II на фиг. 2).

При достижении частоты вращения о 0)2 в момент времени t t2 срабатывает

второй компаратор 9 и на выходе первого элемента ЗИ 22 появляется сигнал логического нуля, что переводит первый 31 и четвертый 34 блоки памяти в режим хранения. На выходе этих блоков памяти соответственно будут сигналы, соответствующие М0

И Ј2.

При достижении частоты вращения о) с«з срабатывает третий компаратор 10, что приводит к изменению состояния RS-триггера, появлению сигнала логической единицы на выходе второго элемента ЗИ 24, который переводит пятый блок памяти 35 в режим записи. В этот же момент на пятом выходе логического блока 15 появляется логический нуль, а на шестом - логическая единица и включается сигнализирующее устройство 21, по сигналу Отключить двигатель которого отключают двигатель транспортного средства от входного вала

трансмиссии. Транспортное средство переходит в режим свободного выбега (участок III, фиг. 2). При достижении частоты вращения а) в момент времени тз первый компаратор 8 возвращается в исходное состояние, на входе второго элемента ЗИ 24 появляется сигнал логического нуля, который переводит пятый блок 35 памяти в режим хранения. На выходе этого блока памяти появляется сигнал, соответствующий ез. В этот же момент на четвертом выходе логического блока 15 появляется сигнал логической единицы с выхода второго элемента 2И 26, так как на обоих входах его присутствуют логические единицы с выхода первого компаратора 8 и выхода элемента 2И-НЕ 27 RS-триггера.

С выходов третьего 33 и четвертого 34 блоков памяти сигналы поступают на входы первого сумматора 36, на выходе которого

формируется сигнал, пропорциональный разности Јi - Ј2. С выхода первого блока 31 памяти и выхода первого сумматора 36 сигналы поступают на входы делителя 37, на выходе которого формируется сигнал, про- порциональный частному М0/(Јч - Ј2). С выхода делителя сигнал поступает на вход шестого блока 38 памяти, который находится в режиме записи, так как на восьмом входе вычислительного устройства находит- ся логическая единица с выхода второго элемента 2И-НЕ 28 RS-триггера. С выходов третьего 33 и шестого 38 блоков памяти сигналы поступают на входы первого перемножителя 39, на выходе которого формиру- ется сигнал, пропорциональный М0 Ј1/(Ј1 - -Ј2) . С выходов пятого 35 и шестого 38 блоков памяти сигналы поступают на входы второго перемножителя 40, на выходе которого формируется сигнал, пропорциональ- ный М0 Ј3/(Јi Ј2). Сигнал с выхода второго перемножителя поступает на вход первого переключателя 41, который находится в разомкнутом состоянии до момента времени тз, так как на его управляющий вход поступает логический нуль с седьмого входа вычислительного устройства 16. Сигнал с выхода первого перемножителя 39 поступает на первый вход сумматора 42. На второй вход сумматора 42 сигнал поступает с выхо- да первого переключателя 41. Таким образом до момента времени t тз на выходе сумматора 42 формируется сигнал, пропорциональный М0 Ј1/(Ј1 - Ј2), а с момента времени t t3 сигнал, пропорциональный М0 (Ј1 + Јз)/(Ј1 Ј2). Сигнал с выхода сумматора 42 поступает на вход второго переключателя 43, который находится в нормально замкнутом состоянии благодаря тому, что на его управляющий вход поступает сигнал логи- ческой единицы с нормально замкнутого контакта пятого переключателя 47. Сигналы с выхода второго переключателя 43 и выхода второго блока 32 памяти поступают на входы третьего перемножителя 45 на выхо- де которого формируется сигнал до момента времени t 13, пропорциональный тяговой мощности на колесах транспортного средства NK М0 Ј1 ш / (Ј1 - Ј2 ) , а после времен t t3 сигнал, пропорциональный мощности двигателя транспортного средства Мд М0 к (Јi + Јs)w/(Јi - Ј3). Сигнал с выхода третьего перемножителя 45 поступает на первый вход четвертого переключателя 46, который

находится в открытом состоянии с момента времени срабатывания третьего компаратора 10, когда на девятом входе вычислительного устройства появляется логическая единица с первого элемента 2И-НЕ 27 RS- триггера логического блока 15. Сигнал с вы0 5 0 5 0 5 0 5 U

5

хода четвертого переключателя 46 поступает на регистрирующий прибор 17.

При нажатии на кнопку пятого переклю-1 чателя 47 поступает сигнал логической единицы на третий переключатель 44 и сигнал логического нуля на второй переключатель 43. В этом случае с второго входа третьего переключателя 45 снимается сигнал с выхода второго сумматора 42 и поступает сигнал с выхода первого переключателя 41. На выходе третьего перемножителя 45 формируется сигнал, пропорциональный мощности потерь в трансмиссии и стенде NTp Mo VЈ3O) /(Ј1 -Ј2), который через четвертый переключатель 46 поступает на регистрирующий прибор 17.

С выхода второго блока 32 памяти сигнал поступает на регистрирующий прибор 13 скорости, который отражает скорость, при которой происходит замер мощности.

По величинам мощности двигателя и мощности потерь .в трансмиссии и стенде, определяемым вычислительным устройством 16 по приведенным формулам, оценивается техничес кое состояние транспортного средства.

Таким образом, в предлагаемом стенде воспроизводятся последовательно два процесса разгона транспортного средства при двух различных уровнях нагрузки с последующим свободным выбегом, что устраняет необходимость определения момента инерции вращающихся масс трансмиссии и стенда, уменьшается время переходного процесса наброса нагрузки и тем самым повышается точность диагностирования технического состояния транспортного средства. Автоматическое определение мощности двигателя и мощности потерь снижает трудоемкость диагностирования.

Формула изобретения

Т, Стенд для диагностирования технического состояния транспортных средств,.содержащий установленные на основании опорные ролики, регулируемый тормоз, кинематически соединенный с опорными роликами, датчик частоты вращения опорных роликов с нормирующим преобразователем, датчик крутящего момента регулируемого тормоза с нормирующим преобразователем, регистрирующий прибор скорости, дифференциатор, вход которого соединен с выходом нормирующего преобразователя датчика частоты вращения опорных роликов, блок уставок, первый, второй и третий компараторы, первые входы которых соединены соответственно с третьим, вторым и первым выходами блока уставок, вторые входы компараторов соеди-. нены с выходом нормирующего преобразователя датчика частоты вращения опорных роликов, систему автоматического регулирования, имеющую усилитель рассогласования, один вход которого соединен с выходом нормирующего преобразователя датчика крутящего момента регулируемого тормоза, второй вход - с четвертым выходом блока уставок, переключатель, первый вход которого соединен с выходом усилителя рассогласования, блок управления силовыми элементами, вход которого соединен с выходом переключателя, а выход - с входом управляющего элемента регулируемого тормоза, сигнализирующее устройство, вход которого соединен с выходом третьего компаратора, логический блок, первый, второй и третий входы которого соединены соответственно с выходами первого, второго и третьего компараторов, вычислительное устройство, первый вход которого соединен с выходом дифференциатора, второй вход- с выходом нормирующего преобразователя датчика частоты вращения опорных роликов, третий вход-с выходом нормирующего преобразователя датчика крутящего момента регулируемого тормоза, четвертый, пятый, шестой и седьмой входы - соответственно с первым, вторым, третьим и четвертым выходами логического блока, регистрирующий прибор, вход которого соединен с вторым выходом вычислительного устройства, при этом логический блок содержит первый элемент 2И-НЕ, первый вход которого соединен с третьим входом логического блока, второй элемент 2И-НЕ, первый вход которого соединен с выходом первого элемента 2И-НЕ, выход - с вторым входом первого элемента 2И-НЕ, резистор, подключенный к второму входу второго элемента 2И-НЕ и плюсовой клемме источника тока, и нормально открытый контакт, подключенный к второму входу второго элемента 2И-НЕ и минусовой клемме источника тока, инвертор, элемент 2И, о т л и ч-а ю- щ и и с я тем, что, с целью повышения точности диагностирования, логический блок снабжен двумя элементами ЗИ, первый вход первого элемента ЗИ соединен с вторым входом логического блока, второй вход - с выходом инвертора, вход которого соединен с первым входом логического блока, третий вход - с выходом второго элемента 2И-НЕ и первым входом элемента 2И, первый вход второго элемента ЗИ соединен с третьим входом логического блока, второй вход - с выходом инвертора, третий вход - с выходом первого элемента 2И-НЕ, второй вход элемента 2И соединен с первым входом логического блока, выходы элемента 2И, первого элемента ЗИ, второго элемента

ЗИ и второго элемента 2И-НЕ соединены соответственно с первым, вторым, третьим и четвертым выходами логического блока, первый выход вычислительного устройства соединен с регистрирующим прибором скорости.

2.Стенд по п. 1,отличающийся тем, что вычислительное устройство содержит пять блоков памяти, вход первого блока

0 памяти соединен с третьим входом вычислительного устройства, вход второго блока памяти соединен с вторым входом вычислительного устройства, входы третьего, четвертого и пятого блоков памяти обье5 динены и соединены с первым входом вычислительного устройства, управляющие входы второго и третьего блоков памяти соединены с четвертым входом вычислительного устройства, управляющий вход пятого

0 блока памяти соединен с шестым входом вычислительного устройства, два сумматора, входы первого сумматора соединены с выходами третьего и четвертого блоков памяти, делитель, входы которого соединены

5 с выходом первого блока памяти и выходом первого сумматора, три перемножителя, первый вход первого перемножителя соединен с выходом третьего блока памяти, второй вход - с выходом делителя, первый вход

0 второго перемножителя соединен с выходом делителя, второй вход - с выходом пятого блока памяти, первый вход второго сумматора соединен с выходом первого перемножителя, второй вход-с вторым выхо5 дом второго перемножителя, первый вход третьего перемножителя соединен с выходом второго блока памяти, второй вход - с выходом второго сумматора, а выход - с вторым выходом вычислительного устройст0 ва, выход второго блока памяти соединен с первым выходом вычислительного устройства.

3.Стенд по п. 2, отличающийся тем, что, с целью повышения стабильности

5 работы вычислительного устройства, в него введен шестой блок памяти, первый вход которого соединен с выходом делителя, выход - с вторым входом первого перемножителя и первым входом второго

0 перемножителя, а управляющий вход соединен с седьмым входом вычислительного устройства, который соединен с четвертым входом логического блока, который соединен с выходом второго элемента 2И-НЕ.

5 4. Стенд по пп. 2 и 3, о т л и ч а ю щ и й- с я тем. что, с целью удобства считывания информации, в него введены второй элемент 2И, входы которого соединены с выходом первого элемента 2И-НЕ и первым входом логического блока, а выход - с пятым

выходом логического блока, который соединен с восьмым входом вычислительного устройства, выход первого элемента 2И-НЕ соединен с шестым выходом логического блока, который соединен с девятым входом вычислительного устройства, при этом в вычислительное устройство введены два пере- ключателя, первый вход первого переключателя соединен с выходом второго перемножителя, выход - с вторым входом второго сумматора, а управляющий вход - с восьмым входом вычислительного устройства, первый вход четвертого переключателя соединен с выходом третьего перемножителя, выход - с вторым выходом вычислитель- ного устройства, а управляющий вход - с девятым входом вычислительного устройства.

5. Стенд по пп. 2 и 3, о т л и ч а ю щ и йс я тем, что, с целью удобства считывания

информации, в вычислительное устройство введены три переключателя, первый вывод нормально замкнутого контакта пятого переключателя соединен с управляющим входом второго переключателя, вход которого соединен с выходом второго сумматора, а выход - с вторым входом третьего перемножителя, первый вывод нормально разомкнутого контакта пятого переключателя соединен с управляющим входом третьего переключателя, первый вход которого соединен с выходом второго перемножителя, а выход - с вторым входом третьего перемножителя, вторые выводы контактов пятого переключателя объединены и соединены с плюсовой клеммой источника тока.

6. Стенд по пп. 4 и 5, о т л и ч а ю щ и й- с я тем, что в вычислительном устройстве первый вход третьего переключателя соединен с выходом первого переключателя.

| название | год | авторы | номер документа |

|---|---|---|---|

| Стенд для диагностирования технического состояния транспортных средств | 1988 |

|

SU1543280A1 |

| Способ определения технического состояния транспортного средства | 1989 |

|

SU1688150A1 |

| Устройство контроля каналов связи | 1988 |

|

SU1578820A1 |

| Устройство для моделирования вентильного преобразователя | 1981 |

|

SU968829A1 |

| Цифровой измеритель центра тяжести видеосигналов | 1990 |

|

SU1723559A1 |

| Устройство для контроля параметров электронных схем | 1982 |

|

SU1112324A1 |

| УСТРОЙСТВО ПОДАВЛЕНИЯ ПОМЕХ ДЛЯ ПРИЕМНИКОВ ШИРОКОПОЛОСНЫХ СИГНАЛОВ | 2003 |

|

RU2253183C1 |

| Устройство для измерения частоты гармонического сигнала | 1987 |

|

SU1525607A1 |

| Стенд для диагностирования технического состояния трансмиссии транспортных средств | 1985 |

|

SU1237939A1 |

| Устройство для измерения интенсивности линии в оптическом спектре | 1987 |

|

SU1509625A1 |

Изобретение относится к транспортному машиностроению и может быть использовано при оценке технического состояния транспортного средства. Цель изобретения - повышение точности диагностирования транспортного средства. Стенд содержит опорные ролики 2, датчик 5 частоты вращения роликов, регулируемый гор- моз, кинематически соединенный с роликами, датчик 6 момента регулируемого тормоза, систему 12 автоматического регулирования, логический блок 15 и вычислительное устройство 16. 5 з.п.ф-лы, 2 ил. J.i

Ж

| Стенд для диагностирования технического состояния транспортных средств | 1988 |

|

SU1543280A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1992-06-30—Публикация

1990-07-30—Подача