Изобретение относится- к вычислительной технике и может быть использовано при отладке программ, а также отработке и настройке специализированных внешних устройств управляющих вычислитбльнь:х комплексов.

Целью изобретения является расширение диагностических возможностей устройства.

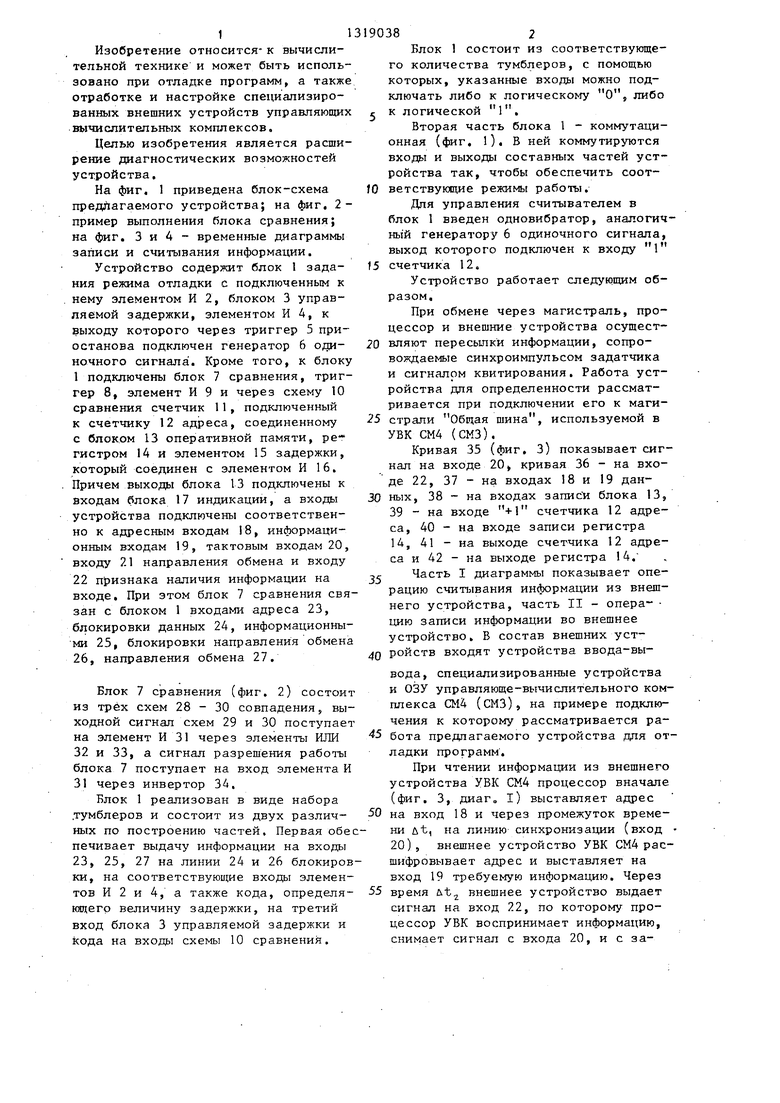

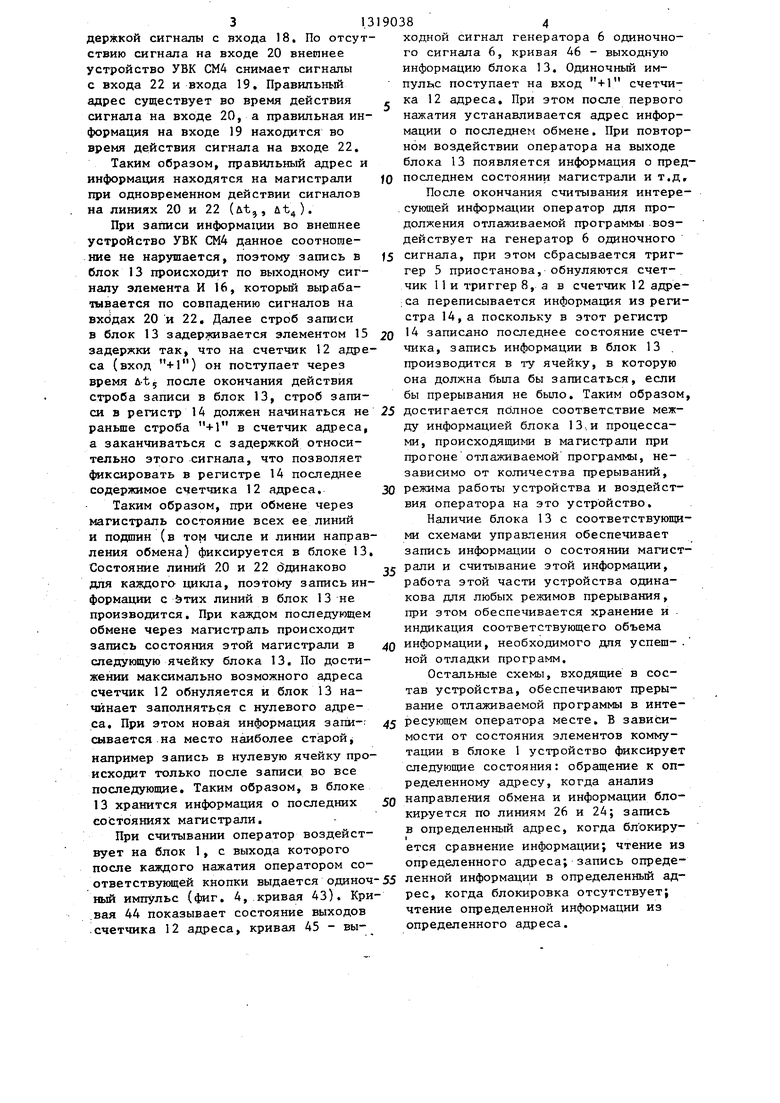

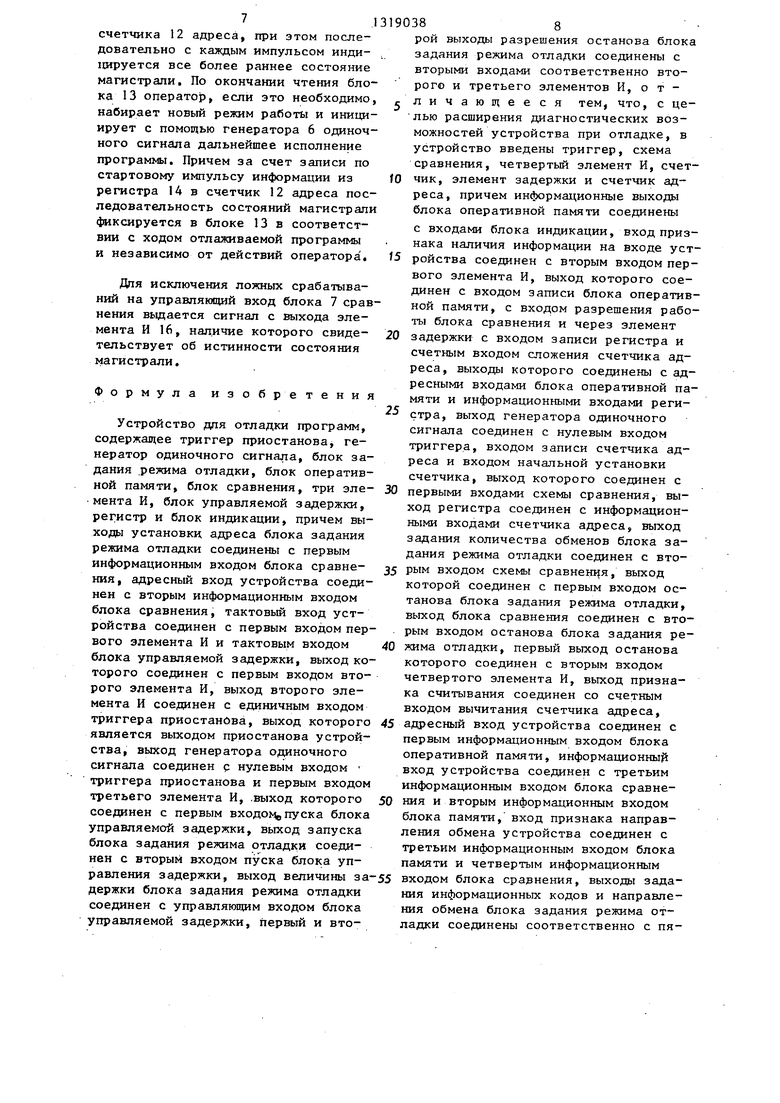

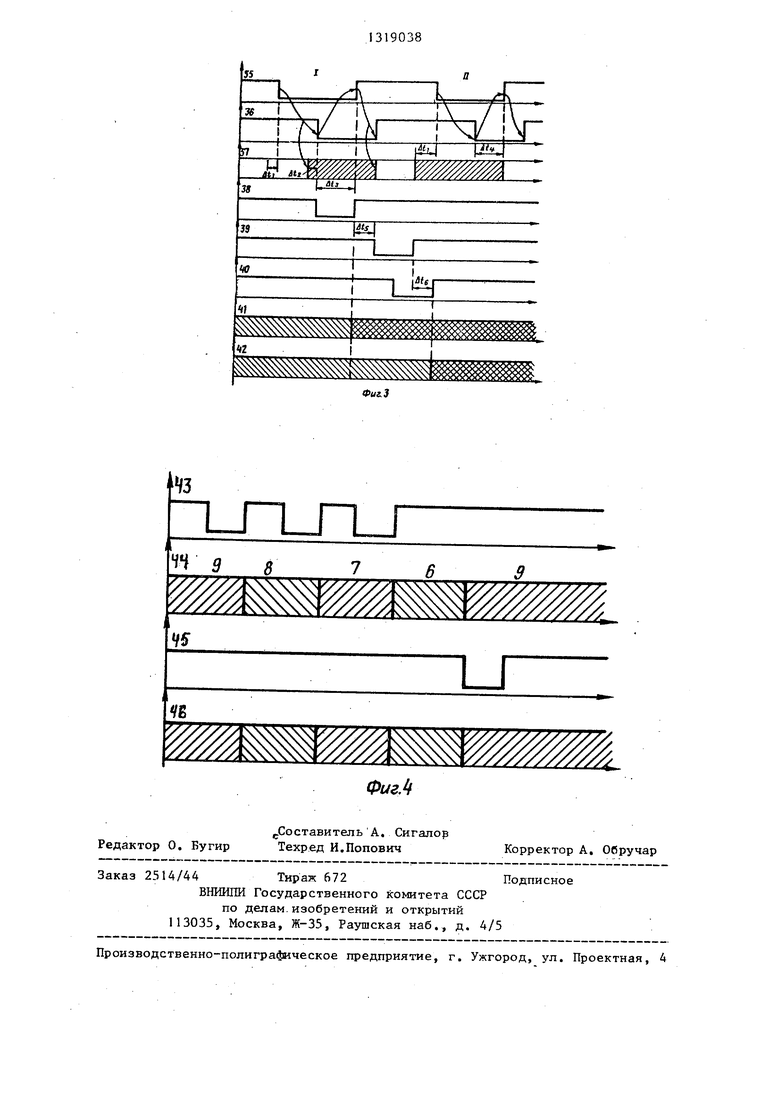

На фиг. 1 приведена блок-схема предлагаемого устройства; на фиг, 2- пример выполнения блока сравнения; на фиг. 3 и 4 - временные диаграммы записи и считывания информации.

Устройство содержит блок 1 задания режима отладки с подключенным к нему элементом И 2, блоком 3 управляемой задержки, элементом И 4, к выходу которого через триггер 5 при- останова подключен генератор 6 одиночного сигнала;. Кроме того, к блоку 1 подключены блок 7 сравнения, триггер 8, элемент И 9 и через схему 10 сравнения счетчик 11, подключенный к счетчику 12 адреса, соединенному с блоком 13 оперативной памяти, регистром 14 и элементом 15 задержки, который соединен с элементом И 16, Причем выходы блока 13 подключены к входам блока 17 индикации, а входы устройства подключены соответственно к адресным входам 8, информационным входам 19, тактовым входам 20, входу 21 направления обмена и входу 22 признака наличия информации на входе. При этом блок 7 сравнения связан с блоком 1 входами адреса 23, блокировки данных 24, информационны- ми 25, блокировки направления обмена 26, направления обмена 27,

Блок 7 сравнения (фиг, 2) состоит из трёх схем 28 - 30 совпадения, выходной сигнал схем 29 и 30 поступает на элемент И 31 через элементы ИЛИ 32 и 33, а сигнал разрешения работа блока 7 поступает на вход элемента И 31 через инвертор 34.

Блок 1 реализован в виде набора тумблеров и состоит из двух различных по построению частей. Первая обесечивает выдачу информации на входы 23, 25, 27 на линии 24 и 26 блокирови, на соответствующие входы элементов И 2 и 4, а также кода, определя- дего величину задержки, на третий ход блока 3 управляемой задержки и ода на входы схемы 10 сравнения.

Блок 1 состоит из соответствующего количества тумблеров, с помощью которых, указанные входы можно подключать либо к логическому О, либо

к логической 1,

Вторая часть блока 1 - коммутационная (фиг. 1). В ней коммутируются входа и выходы составных частей устройства так, чтобы обеспечить соответствующие режимы работы.

Для управления считывателем в блок 1 введен одновибратор, аналогич- ны й генератору 6 одиночного сигнала, выход которого подключен к входу 1

счетчика 12.

Устройство работает следующим образом.

При обмене через магистраль, процессор и внешние устройства осуществляют пересыпки информации, сопровождаемые синхроимпульсом задатчика и сигналом квитирования. Работа устройства для определенности рассматривается при подключении его к магистрали Общая шина, используемой в УВК СМ4 (СМЗ).

Кривая 35 (фиг. 3) показывает сигнал на входе 20 кривая 36 - на входе 22, 37 - на входах 18 и 19 данных, 38 - на входах запис и блока 13, 39 - на входе +1 счетчика 12 адреса, 40 - на входе записи регистра 14, 41 - на выходе счетчика 12 адреса и 42 - на выходе регистра 14,

Часть I диаграммы показывает операцию считывания информации из внешнего устройства, часть II - опера цию записи информации во внешнее устройство, В состав внешних устройств входят устройства ввода-вывода, специализированные устройства и ОЗУ управляюще-вычислительного комплекса СМ4 (СМЗ), на примере подключения к которому рассматривается работа предлагаемого устройства для отладки программ .

При чтении информации из внешнего устройства УВК СМ4 процессор вначале (фиг, 3, диаг,, I) выставляет адрес

на вход 18 и через промежуток времени д1, на линию синхронизации (вход 20), внешнее устройство УВК СМ4 расшифровывает адоес и выставляет на вход 19 требуемую информацию. Через

время At. внешнее устройство выдает сигнал на вход 22, по которому процессор УВК воспринимает информацию, снимает сигнал с входа 20, и с за

31.

держкой сигналы с входа 18. По отсутствию сигнала на входе 20 внешнее устройство УВК СМ4 снимает сигналы с входа 22 и входа 19. Правильный адрес существует во время действия сигнала на входе 20, а правильная информация на входе 19 находится во время действия сигнала на входе 22.

Таким образом, правильный адрес и информация находятся на магистрали при одновременном действии сигналов на линиях 20 и 22 (ut,, ut).

При записи информахши во внешнее устройство УВК СМ4 данное соотношение не нарушается, поэтому запись в блок 13 происходит по выходному сигналу элемента И 16, которьй вырабатывается по совпадению сигналов на входах 20 и 22, Далее строб записи в блок 13 задерживается элементом 15 задержки так, что на счетчик 12 адреса (вход +1) он поступает через время u-ty после окончания действия строба записи в блок 13, строб записи в регистр 14 должен начинаться не раньше строба +1 в счетчик адреса, а заканчиваться с задержкой относительно этого сигнала, что позволяет фиксировать в регистре 14 последнее содержимое счетчика 12 адреса.

Таким образом, при обмене через магистраль состояние всех ее линий и подшин (в том числе и линии направления обмена) фиксируется в блоке 13 Состояние линий 20 и 22 ддинаково для каждого цикла, поэтому запись информации с &ТИХ линий в блок 13 не производится. При каждом последующем обмене через магистраль происходит запись состояния этой магистрали в следующую ячейку блока 13. По достижении максимально возможного адреса счетчик 12 обнуляется и блок 13 начинает заполняться с нулевого адреса. При этом новая информация запи-; сывается на место наиболее старойj например запись в нулевую ячейку происходит только после записи во все последующие. Таким образом, в блоке 13 хранится информация о последних состояниях магистрали.

При считывании оператор воздействует на блок 1, с выхода которого после каждого нажатия оператором со- ответствукицей кнопки выдается одиночный импульс (фиг. 4, кривая 43). Кри .вая 44 показывает состояние выходов счетчика 12 адреса, кривая 45 - вы384

ходной сигнал генератора 6 одиночного сигнала 6, кривая 46 - выходную информацию блока 13. Одиночный импульс поступает на вход +1 счетчика 12 адреса. При этом после первого нажатия устанавливается адрес информации о последнем обмене. При повторном воздействии оператора на выходе блока 13 появляется информация о предпоследнем состоянии магистрали и т.д. После окончания считывания интере- сующей информации оператор для продолжения отлаживаемой программы воздействует на генератор 6 одиночного

сигнала, при этом сбрасывается триггер 5 приостанова, обнуляются счетчик 11 и триггер 8, а в счетчик 12 адре- ; са переписывается информация из регистра 14, а поскольку в этот регистр

14 записано последнее состояние счетчика, запись информации в блок 13 производится в ту ячейку, в которую она должна была бы записаться, если бы прерывания не было. Таким образом,

достигается полное соответствие между информацией блока 13,и процессами, пpoиcxoдяшJiми в магистрали при прогоне отлаживаемой программы, независимо от количества прерываний,

режима работы устройства и воздействия оператора на это устройство.

Наличие блока 13 с соответствуюшл- ми схемами управления обеспечивает запись информации о состоянии магистрали и считывание этой информации, работа этой части устройства одинакова для любых режимов прерывания, при этом обеспечивается хранение и . индикация соответствующего объема

информации, необходимого для успеш-. ной отладки программ.

Остальные схемы, входящие в состав устройства, обеспечивают прерывание отлаживаемой программы в интересующем оператора месте. В зависимости от состояния элементов коммутации в блоке 1 устройство фиксирует следующие состояния: обращение к определенному адресу, когда анализ

направления обмена и информации блокируется по линиям 26 и 24; запись в определенный адрес, когда бл окиру- ется сравнение информации; чтение из определенного адреса; запись определенной информации в определенный адрес, когда блокировка отсутствует; чтение определенной информации из определенного адреса.

Состояние коммутационных элемен- тсв а, Ъ, с блока 1 задает режимы останова: а - 1, Ъ, с - безразлично - останов по выходному сигналу блока 7 сравнения (первый режим); а - 2, Ъ - 1, с - останов по прохождению заданного количества циклов обмена через магистраль после выдачи сигнала блоком 7 (второй режим); а - 2, Ъ - 2, с - 2- останов по определенному количеству вьпсодных импульсов блока 7 (третий резким) ;а-2, Ъ-1,с-2 Ьстанов по количеству команд после пуска (четвертый режим).

В первом режиме останова выход блока 7 непосредственно подключен к входу блока 3 управляемой задержки и останов производится по любому из фиксируемых этим блоком состояний, т.е. существует пять подрежимов.

Во втором режиме выход блока 7 подключен к Б-входу триггера 8, а выход схемы 10 сравнения - к входу блока 3, при этом после появления соответствующего состояния магистрали выходной сигнал блока 7 сравнения устанавливает триггер 8, разрешая прохождение через элемент 19 сигналов синхронизации задатчика с линии 20 на вход счетчика 11, В счетчике происходит подсчет количества обменов через магистраль, по совпаден ию этого количества с заданным с блока I сигнал с выхода схемы 10 сравнения поступает на блок 3 и вызывает останов.

В третьем режиме счетчик 11 через элемент И 9 подключен к выходу блока 7, триггер 8 принудительно установлен, т.е. трансляция сигнала элементу И 9 разрешена. При появлении со- ответствукщего состояния магистрали выходным сигналом блока 7 содержимое счетчика 11 наращивается на единицу до тех пор, пока не срабатывает схема 10 сравнения, сигнал с которой вызывает останов.

В четвертом режиме 4 блок 7 сравнения отключен, трансляция сигналов с линии 20 в счетчик 11 разрешена, поэтому происходит останов по заданному с блока 1 количеству циклов обмена по магистрали.

Таким образом, предлагаемое устройство позволяет организовать 16 видов останова, кроме того, можно организовать останов по времени выполнения программы, если таймер добавляет к содержимому определенной ячейки по единице через соответствующий интервал времени, а в блоке сравнения фиксируется состояние в со- ответствии с указанным. Изменяя эталон информации, можно устанавливать любой интервал времени, кратный задаваемому таймером, без вмещательст- ва в основную программу.

Полностью устройство функционирует следующим образом.

Оператор пускает отлаживаемую программу, по магистрали происходят обмены, информация, выдаваемая процессором, сопровождается синхросигналом на входе 20, а информация, выдаваемая внешним устройством, сопровождается сигналом на входе 22, причем истинное состояние магистрали (истинный адрес, истинные информация и направление обмена) начинается раньше и кончается позже совпадения сигналов на входах 20 и 22. По совпадению сигналов на входах 20 и 22 состояние

магистрали записывается в блок 13, в перерыве между обменами происходит подготовка счетчика 12 адреса и блока 13 к записи следующего состояния магистрали. Запись в блок 13 происходит по цикпич ски изменяющимся адресам, причем новая информация заносится на место наиболее старой, что позволяет хранить в блоке 13 последние состояния магистрали. В то же время,

блок 7 сравнения (третий режим останова) анализирует состояние магистрали и в зависимости от подрежима фик сирует одно из ее состояний.

Появление искомого состояния приводит к выработке сигнала на выходе блока 7 сравнения. Этот сигнал проходит через элемент И 9 (Ъ-2) на вход счетчика 11, поскольку триггер 8 установлен подачей низкого уровня

на вход (с-2). Счетчик 11 подсчитывает количество выходныЬс сигналов блока.7 сравнения. По достижении содержимым этого счетчика 11 состояния, задаваемого с клавиатуры на эталонные входы схемы 10 сравнения, вырабатывается сигнал на соответствующий вход блока 3 управляемой задержки, что приводит к срабатыванию триггера 5 приостанова и прерыванию отт

лаживаемой программы. После останова (при необходимости считать ийформа- цию предыдущих состояний магистрали) оператор через блок 1 воздействует одиночными импульсами на вход +1

счетчика 12 адреса, при этом последовательно с каждым импульсом инди- нируется все более раннее состояние магистрали. По окончании чтения блока 13 оператор, если это необходимо, набирает новый режим работы и инициирует с помощью генератора 6 одиночного сигнала дальнейшее исполнение программы. Причем за счет записи по стартовому импульсу информации из регистра 14 в счетчик 12 адреса последовательность состояний магистрали фиксируется в блоке 13 в соответствии с ходом отлаживаемой программы и независимо от действий оператора,

Дпя исключения ложных срабатываний на управляющий вход блока 7 сравнения выдается сигнал с выхода элемента И 16, наличие которого свидетельствует об истинности состояния магистрали.

Формула изобретения

Устройство ДПЯ отладки программ, содержащее триггер приостанова, генератор одиночного сигнала, блок задания .режима отладки, блок оперативной памяти, блок сравнения, три эле- мента И, блок управляемой задержки, регистр и блок индикации, причем выходы установки адреса блока задания режима отладки соединены с первым информационным входом блока сравнения , адресный вход устройства соединен с вторым информационным входом блока сравнения, тактовый вход устройства соединен с первым входом первого элемента И и тактовым входом блока управляемой задержки, выход которого соединен с первым входом второго элемента И, выход второго элемента И соединен с единичным входом

триггера приостанова, выход которого 45 адресный вход устройства соединен с является выходом приостанова устрой- первым информационным входом блока

ства, выход генератора одиночного сигнала соединен р нулевым входом триггера приостанова и первым входом третьего элемента И, .выход которого соединен с первым входо пуска блока управляемой задержки, выход запуска блока задания режима отладки соединен с вторым входом пуска блока управления задержки, выход величины за-55 входом блока сравнения, выходы зада- держки блока задания режима отладки ния информационных кодов и направле- соединен с управляющим входом блока управляемой задержки, первый и втония обмена блока задания режима отладки соединены соответственно с пяO

рой выхОрДы разрешения останова блока задания режима отладки соединены с вторыми входами соответственно второго и третьего элементов И, о т - личающееся тем, что, с целью расширения диагностических возможностей устройства при отладке, в устройство введены триггер, схема сравнения, четвертый элемент И, счетчик, элемент задержки и счетчик адреса, причем информационные выходы блока оперативной памяти соединены

с входами блока индикации, вход признака наличия информации на входе уст5 ройства соединен с вторым входом первого элемента И, выход которого соединен с входом записи блока оперативной памяти, с входом разрешения работы блока сравнения и через элемент задержки с входом записи регистра и счетным входом сложения счетчика адреса, выходы которого соединены с адресными входами блока оперативной памяти и информационными входами регистра, выход генератора одиночного сигнала соединен с нулевым входом триггера, входом записи счетчика адреса и входом начальной установки счетчика, выход которого соединен с первыми входами схемы сравнения, выход регистра соединен с информационными входами счетчика адреса, выход задания количества обменов блока задания режима отладки соединен с вто5 рым входом схемы сравнен1|я, выход которой соединен с первым входом останова блока задания режима отладки, выход блока сравнения соединен с вторым входом останова блока задания ре0 жима отладки, первый выход останова которого соединен с вторым входом четвертого элемента И, выход признака считывания соединен со счетным входом вычитания счетчика адреса.

0

5

0

оперативной памяти, информационный вход устройства соединен с третьим информационным входом блока сравне- ния и вторым информационным входом блока памяти, вход признака направления обмена устройства соединен с третьим информационным входом блока памяти и четвертым информационным

входом блока сравнения, выходы зада- ния информационных кодов и направле-

ния обмена блока задания режима отладки соединены соответственно с пя9131903810

тым и шестым информационными входами дания режима соединены соответствей- блока сравнения, выходы блокировки но с первым и вторым входами блоки-- данных и направления обмена блока за- ровки блока сравнения.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для отладки программ | 1984 |

|

SU1275452A1 |

| Устройство для отладки программ | 1988 |

|

SU1624461A1 |

| Устройство для отладки программно-аппаратных блоков | 1987 |

|

SU1497617A1 |

| Устройство для отладки программно-аппаратных комплексов | 1990 |

|

SU1795464A1 |

| Устройство для отладки программно-аппаратных блоков | 1986 |

|

SU1425683A1 |

| Устройство для отладки многопроцессорных систем | 1988 |

|

SU1541616A1 |

| Устройство для отладки микроЭВМ | 1987 |

|

SU1587514A1 |

| Устройство для отладки микроЭВМ | 1989 |

|

SU1677708A1 |

| Устройство для отладки программно-аппаратных блоков | 1986 |

|

SU1363219A1 |

| Устройство для отладки микроЭВМ | 1987 |

|

SU1553981A1 |

Изобретение относится к вычислительной технике и, позволяет повысить эффективность средств, обеспечивающих отладку программ. Целью изобретения является расширение диагностических возможностей.устройства. Устройство содержит блок задания режимов, элементы И, блок управляемой задержки, триггер приостанова, генератор одиночных сигналов, блок сравнения, триггер, схему сравнения, счетчики и блок оперативной памяти, регистр, элемент задержки и блок индикации. Устройство позволяет организовать до 17 режимов останова отлаживаемой программы и зафиксировать информахщю о ходе программы, которая может быть использована для устранения ошибок в программе. 4 ил. : UD 00 00

направл. обмена

Фиг. 2

55

ж

гх

57

м,

38

и

ч

CV

ет

тт:

W

Й1е

IJrH

iH 9 в

2х

V V Х/ Vs.

U

2

Редактор О. Бугир

Составитель А. Сигалор Техред И.Попович

Заказ 2514/44Тиран 672Подписное

ВНИИПИ Государственного комитета СССР

по делам.изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород,ул. Проектная, 4

Фие.

Корректор А, Обручар

| Устройство для формирования сигнала прерывания при отладке программ | 1983 |

|

SU1124315A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для отладки программ | 1984 |

|

SU1275452A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-06-23—Публикация

1986-01-13—Подача