4

ьо ел

о:) 00

bo

тор 21, схема 40 сравнения, элементы И 38 и 39, элемент ИЛИ 36, элементы НЕ 35, 36 и 41 и элемент 8 задержки. Изобретение обеспечивает на элементной базе отлаживаемого процессора увеличение диапазона допустимых частот отладки в реальном масштабе времени. 1 ил.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для отладки программно-аппаратных блоков | 1986 |

|

SU1363219A1 |

| Устройство для отладки программно-аппаратных блоков | 1987 |

|

SU1497617A1 |

| Устройство для отладки многопроцессорных систем | 1988 |

|

SU1541616A1 |

| Устройство для отладки программно-аппаратных блоков | 1985 |

|

SU1348839A1 |

| Устройство для отладки многопроцессорных систем | 1987 |

|

SU1446624A1 |

| Устройство для отладки программно-аппаратных блоков | 1988 |

|

SU1529228A1 |

| Устройство для отладки программ микроЭВМ | 1989 |

|

SU1815643A1 |

| Устройство для отладки программно-аппаратных блоков | 1984 |

|

SU1282139A1 |

| Устройство для отладки программ | 1988 |

|

SU1624461A1 |

| Устройство для отладки микроЭВМ | 1987 |

|

SU1553981A1 |

Изобретение относится к авто- .матике и вьиислительной технике и может быть использовано при отладке средств вычислительной техники. Целью изобретения является расширение функциональных возможностей устройства за счет повьпцения допустимых частот отладки. В состав устройства входят генератор 3 иьтульсов, дешифраторы 4-14, регистры 15, 16,- 31 и 32, блоки 22-25 памяти, мультиплексоры 29 и 30, триггеры 17, 18, 19, 20, 26, 33 и 34, одновибраSfi

1

Изобретение относится к вычислительной технике и может быть использовано при разработке микроконтроллеров, микроэвм и других средств вычислительной техники на основе однокристальных микропроцессоров.

Цель изобретения - расширение функциональных возможностей за счет повьшения допустимых частот отладки в реальном масштабе времени.

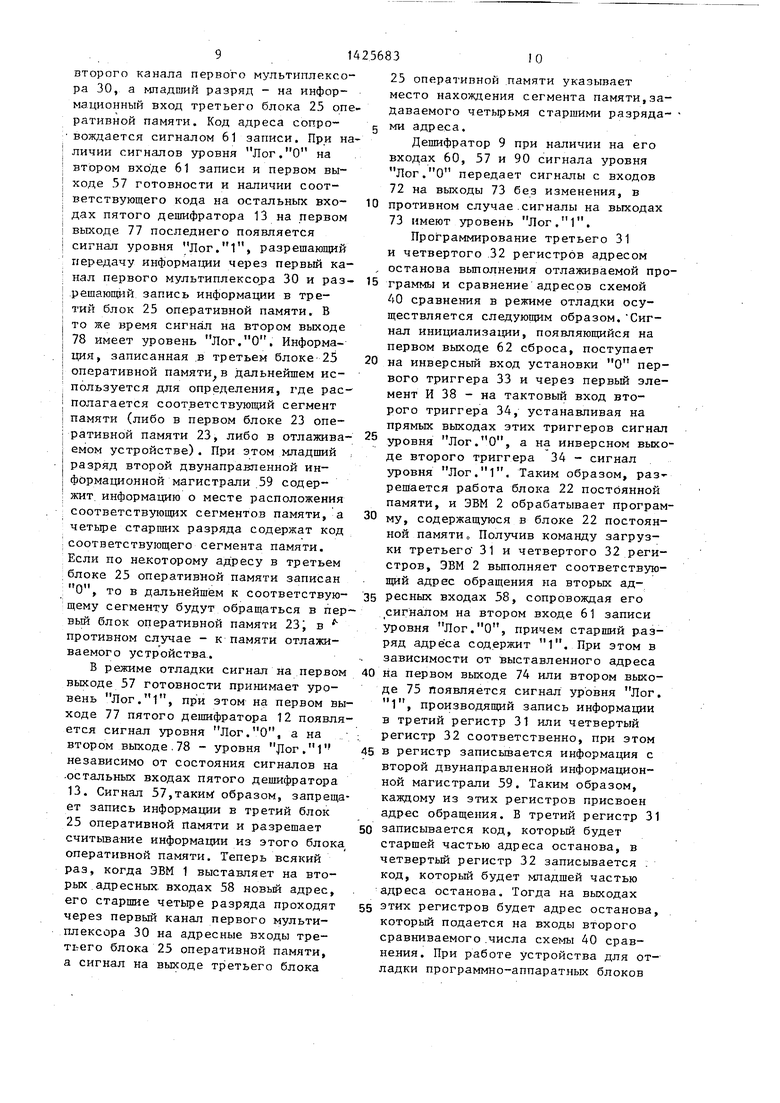

На чертеже показана схема устройства для отладки программно-аппаратных блоков.

Устройство содержит первую 1 и вторую 2 ЭВМ, генератор 3 импульсов, второй 4, третий 5, десятый 6, первый 7 дешифраторы, элемент 8 задержки, восьмой 9, четвертый 10, седьмой 11, девятый -12, пятый 13 и шестой 14 дешифраторы, первый 15 и второй 16 регистры, третий 17, четвертый 18, пятьй 19 и шестой 20 триггеры, одновибратор 2t, блок 22 постоянной памяти, первый 23, второй 24 и третий 25 блоки оперативной памяти, седьмой триггер 26, первый 27 и второй 28 счетчики, второй 29 и первый 30 мультиплексоры, третий 31 .и четвертый 32 регистры, первый 33 и второй 34 триггеры, второй 35 и первьй 36 элементы НЕ, 37, первый 38, второй 39 элементы И,схему 40 сравнения, третий элемент НЕ 41, первые адресные входы 42, первые входы записи 43, чтения 44, сброса 45, третьи инфopIv aциoнныe входы-выходы 46, группу 47 адресных выходов, первые входы чтения 48, записи 49, второй выкод 50 сброса, первый выход 51 строба адреса, первьй 52, второй 53 выходы задания режима, выход 54 признака выборки команды,вход 55 готовности, второй 56 и первый 57 выходы готовности, вторые адресны входы 58, вторую двунаправленную информационную магистраль 59, вход чт&- ния 60 и записи 61, первый выход 62 сброса, вход 63 признака выборки команды, первый 64 и второй 65 входы

задания режима, вход 66 строба адреса устройства, выход 67 генератора импульсов, первый 68, второй 69 и третий 70 выходы второго дешифратора, первый вход 71 третьего элемента И,

0 группу входов 72 и выходов 73 восьмого дешифратора, первый 74, второй 75 и третий 76 выходы четвертого дешифратора, . первьй 77 и второй 78 выходы пятого дешифратора, первые ;

5 информационные входы-выходы 79 уст- i ройства, первый 80, второй 81, третий 82 выходы десятого дешифратора, выход 83. тр-етьего элемента И, первьй 84, второй 85, третий 86, четвертый

0 87, пятый 88 выходы седьмого дешифратора, прямой выход шестого триггера 89, второй вход 90 второго элемента И, прямой выход 91 второго триггера, выходы 92 и 93 переполне5 ния второго и первого счетчиков импульсов, второй 94, третий 95 пятый 96, шестой 97, седьмой.98, восьмой 99, девятьй 100, десятьй 101 входы десятого дешифратора.

0 Устройство работает под управляющей ЭВМ, в качестве которой может быть использована,, например, никро- ЭВМ УВС-01, и обеспечивает отладку устройств на основе микропроцессо5 Р° содержащих встроенную очередь команды, например К181ОВМ86 или К1810ВМ88. Системная .шина управляющей ЭВМ подключается к входным шинам устройства для отладки программно0аппаратных блоков. Выходные шины устройства подключаются к пшнам отлаживаемого устройства. Устройство может работать в одном из двух режимов: режиме управления и режиме отладки.

5

Работа предлагаемого устройства в режиме управления. Сигнал уровня- Лог.О, появляющийся на первом входе 45 сброса устройства при нажатии кнопки сброса на пульте управляющей ЭВМ, проходит через второй дешифратор и с выхода 70 последнего воздействует на ЭВМ 1 и 2, первый триггер 33 и седьмой дешифратор 11, выполняя их начальную установку. Через шестой дешифратор 14 сигнал сброса поступает также на второй выход 50 сброса устройства. После окончания воздействия сигнала сброса на выходе 91 режима второго триггера появляется сигнал уровня Ло1:.0, который через второй элемент И 39 поступает на вход готовности ЭВМ 1, запрещая ее работу. При этом сигнал уровня Лог. М с первого выхода 57 готовности устройства поступает на вход готовности ЭВМ 2, разрешая ее работу ЭВМ 2 начинает отработку программы- монитора, содержащейся в блоке 22 постоянной памяти. В соответствии с этой программой ЭВМ 2 находится в цикле ожидания командj подаваемьк с упраштяющей ЭВМ.

Команда в виде соответствующего кода поступает от управляющей ЭВМ по первым информационным входам-выходам 79 и при определенном адресе, выставляемом на первых адресных входах 42 и при наличии сигнала на первом входе 44 записи запоминается в первом регистре 15. ЭВМ.2 в соответствии с вьтолняемой программой постоянно опрашивает этот регистр, выставляя соответствующий код адреса на вторых адресных входах 58 и сигнал на втором входе 60 чтения, прочитав код с группы выходов 59 третьего дешифратора 5, ЭВМ 2 переходит к вьтолнению программы обработки полученной команды В соответствии с получаемыми командами ЭВМ 2 производит загрузку третьего блока 25 one ративной памяти, третьего 31 и четвертого 32 регистров и при необходимости первого блока 23 оперативной памяти„

Эти операции вьшолняются следую- образом.

На вторых адресных входах 58 ЭВМ 2 устанавливает адрес, соответствующий одному из узлов устройства, а по второй двунаправленной информационной магистрали 59 ЭВМ 2 передает не25683

обходимые коды, сопровоЖ дая их сигналом по второму входу 61 записи. При этом при обра щении ЭВМ 2 к первому с блоку 23 оперативной памяти на старшей адресной линии присутствует сигнал уровня Лог.О, а при обращении к -второму блоку 24 оперативной памяти, четвертому 10, пятому 13 и шес10 тому 14 дешифраторам - сигнал уровня Лог.1. В третий блок 25 оперативной памяти записывается информация о том, будет ли при отладке использоваться память отлаживаемого

5 устройства или будет использоваться первый блок 23 оперативной памяти, в последнем случае ЭВМ 2 загружает в первьй блок. 23 оперативной памяти отлаживаемую программу. В соответст0 ВИИ с информацией, записанной в третьем блоке 25 оперативной памяти,при отладке на выходе 90 будет вьфабаты- ваться соответственно сигнал разрешения работы первого блока 23 опера5 тивной памяти (сигнал 90 уровня Лог. О) или шестого депифратора 14 (сигнал 90 уровня Лог.1).

В третий 31 и четвертый 32 регистры записывается условие окончания от0 ладки, при выполнении которого запрещается вьтопнение отлаживаемой программы подачей на первый выход 62 сброса сигнала начальной установки. Для перехода в (зежим отладки ЭВМ.

- 2, получив соответствуюш ш код коман- .ды через первый регистр 15 и третий дешифратор 5, устанавливает на вторых адресных входах 58 код, состоящий из всех единиц. В этом случае на

0 первом выходе 57 готовности вырабатывается сигнал уровня Лог.О, который отключает блок 22 постоянной памяти и, поступая на вход готовности ЭВМ 2, запрещает ее работу.Этот

5 же сигнал поступает на второй вход пятого дешифратора 13 и сигнал уровня Лог.1 на выходе. 9 1, которым разрешается работа ЭВМ 1 и включается второй блок 24 оперативной памяти.

Q В режиме отладки работает ЭВМ 1, выполняя отлаживаемую программу. ЭВМ 1 состоит из трех блоков: блока управления каналом, блока исполнения .команд и блока очереди команд. Блок

управления каналом организует циклы- канала, выбирает из памяти коды отлаживаемой программы и загружает их в блок очереди команд. Блок исполнения команд последовательно испол5142568

няет команды, выбирая их из блока очереди команд. Если в процессе выполнения команды необходимо обратиться к памяти, то блок исполнения ко- манд делает заявку; блок управления каналом, закончив очередную выборку программного кода из памяти, удовлетворяет эту заявку. Объем запоминающего узла блока очереди команд огра- ю ничен; если он заполнен, то блок управления каналом работает вхолостую, если в блок очереди команд можно поместить байты программного кода, то блок управления каналом выполняет . 15 дики выборки из памяти кода команды.

Таким образом в ЭВМ 1 организована предварительная (заблаговременная) выборка кодов команд, а операции выборки и.исполнения.совмещены , 20 во времени. Поэтому последователь-с ность выборки не соответствует последовательности их исполнения, в частности, команды, которые выбраны из памяти после выборки команды без- 25 условного перехода, в действительности не исполняются. Чтобы восстано- вить реальную картину исполнения ко- манд, необходимо иметь сведения о взаимодействии блока исполнения ко- 30 манд с блоком очереди .команд. Код на выходах 64 и 65 задания режима го- ворит о том, что в предьщущем такте из блока очереди команд ЭВМ 1 выбран первый байт кода команды, либо по- 5 следующий байт кода команды, либо блок очереди команд бьш очищен- в ре- зультат.е выполнения команды перехода, либо в предшествующем такте блок исполнения команд не обращался к бло- 40 ку очереди команд. Также необходимо знать количество -команд, НТаходящихся в блоке очереди команд в определенные моменты времени - эту информацию . вьфабатывает узел, включающий десд- 45 тый дешифратор 6, третий 17, четвертый 18, пятый 19, шестой 20,седьмой 26 триггеры, третий элемент И 37, второй 35 и третий 41 элементы НЕ, элемент 8 задержки.50

Выполняя отлаживаемую программу. ЭВМ 1 производит обращения либо к первому блоку 23 оперативной памяти, либо к памяти отлаживаемого устройства в зависимости от информадаи, gg записанной в третьем блоке 25 оперативной памяти. Обмен информацией .между памятью и ЭВМ 1 производится .через шестой депшфратор 14 следующим

36

образом.В случае передачи информации от ЭВМ 1 в память отлаживаемого .устройства информация на .вторых ад- ресных входах 58 и второй двунаправленной информационной магистрали 59, сопровождающаяся сигналом на втором входе 61 записи, передается через шестой дешифратор 14 при наличии разре щающего сигнала 90 на группу адресны выходов 47 и третьи информационные входы-выходы 46 к памяти отлаживаемого устройства, сопровождаясь при это 1 - сигналом по первому выходу 49 записи

При приеме информации из памяти отлаживаемого устройства ЭВМ 1 устанавливает на втором выходе 60 чтения устройства сигнал чтения данных, который через шестой дешифратор 14 поступает на первьй выход 48 чтения, а на вторых адресных входах 58 - адрес ячейки, к которой производится обращение. Код адреса через шестой дешифратор 14 поступает на группу адресных выходов 47 устройства. Код адреса и сигнал на, первом выходе 48 чтения будет сохраняться до тех пор, пока память отлаживаемого устройства не установит считанную информацию на третьих информационных входах-выходах 64, с которой через шестой дешифратор 14. она поступит на вторую двунаправленную информационную магистраль. 59 ЭВМ 1.

Синхронизация работы ЭВМ 1 и памяти отлаживаемого устройства выполняется с помощью входа 55 готовности. При обращении к памяти последняя устанавливает на входе 55 сигнал уровня Лог.О, которьш через третий вход второго элемента И 39 поступает на второй выход 56 готовности, запрещая работу ЭВМ 1, сигнал этого уровня остается до тех пор, пока память не закончит внутренний цикл (т.е. не произведет запись или вьща- чу информации). После окончания внутреннего цикла на входе 55 готовности память устанавливает сигнал уровня Лог. М, который через второй элемент И 39 поступает на второй выход 56. ЭВМ 1, обратившись к памяти отлаживаемого устройства, приоста- -навливает свою работу на все то время, в течение которого на входе 55 : готовности остается сигнал уровня Лог.О.

В Течение всего времени работы ЭВМ 1 включен втор.ой блок 24 оперативной памяти, в котором по положительному фронту конъюнкции сигналов на вторых входах чтения 60 и записи 61, а также в те периоды тактировки, когда хотя бы один из сигналов на нервом 64 и втором 65 входах задания режима устройства имеет уровень Лог.1, запоминается информация с вторых адресных входов 58, второй двунаправленной информационной магистрали 59, инверсных выходов третьего 17, четвертого 18 и пятого 19 триггеров, а также с первого 64 и второго 65 входов задания режима устройства.

В схеме 40 сравнения в режиме (отладки постоянно происходит сравнение кодов адреса с вторых адресных входов 58 с заданными в качестве условий выхода из режима отладки. При совпадении кодов адреса с заданными на выходе 91 вырабатывается сигнал уровня Лог.О, которьй запрещает запоминание информации во втором блоке 24 оперативной памяти и останавливает ЭВМ 1, а на выходе 57 появляется сигнал уровня Лог.1, который разрешает работу блока 22 по25 Из формулы (1) следует, что д шифратор буферизирует сигнал сбро с первого выхода 62. Сигналы 61, 63,64, 65 и 66 имеют активный низ уровень и проходят сквозь депмфра

стоянной памяти и ЭВМ 2. Одновременно 30 14 только при наличии ..сигнала 90

с этим одновибратор 21 и первый элемент НЕ 36 формируют на линии 62 сигнал начальной установки.

ЭВМ 2 начинает отработку програмразрешения уровня Лог.1, что с детельствует об обращении ЭВМ 1 к мяти отлаживаемого устройства фор лы (2)-(8). Сигналы с второй двун

мы, содержащейся в блоке 22 постоян- 35 правленной информационной магистраной памяти, и остается в цикле ожидания команды от управляющей ЭВМ.Эти команды, в частности, могут инициировать передачу в управляющую ЭВМ информации, содержащейся во втором бло- 40 отлаживаемого устройства проходят

ке 24 оперативной памяти.

Таким образ.ом, устройство для отладки программно-аппаратных блоков позволяет моделировать отлаживаемое устройство на самых ранних зтапах разработки, используя при этом первый блок 23 оперативной памяти, и производить отладку программного обеспечения, необходимого для работы отлаживаемого устройства, с запоминанием информации во втором блоке 24 оперативной памяти. При отладке обеспечивается останов отлаживаемой программы по адресу, задаваемому оператором.

Шестой дешифратор 14 реализует следующие логические функции (индексы у переменных X соответствуют номерам, входов дешифратора, индексы

на вторую двунаправленную информац онную магистраль 59 при наличии ра решающего сигнала 90 и сигнала 60 чтения, что следует из формул (9)

45 (10).

В третьем блоке 25 оперативной памяти содержится информация, упра ляющая обращением ЭВМ 1 к памяти в режиме отладки. Программа загрузки

50 третьего блока 25 оперативной памя содержит адрес обращения к этому у лу: при этом четыре старших разряд адреса подаются на первый канал 30 первого мультиплексора, остальные

55 разряды адреса подсоединены к соот ветствующим входам пятого дешифратора 13, четыре старших разряда вт рой двунаправленной информационной магистрали 59 поступают на входы

у переменных Y соответствуют номерам выходов деЕгифратора)

5

0

ei

144

48

Я

52

г

54

-47

4Ь

вч

X

50

XM Х,„;

Хво

90

М 90

«.4 90 5

Ь5 )о

Х,„

X

8

V X

90

X

59

Х, V X

61

46 Х,„ V Х,о,

(1)

(2) (3) (4) (5) (6) (7) (8) (9) (10)

25 Из формулы (1) следует, что дешифратор буферизирует сигнал сброса с первого выхода 62. Сигналы 61, 60, 63,64, 65 и 66 имеют активный низкий уровень и проходят сквозь депмфратор

30 14 только при наличии ..сигнала 90

разрешения уровня Лог.1, что свидетельствует об обращении ЭВМ 1 к памяти отлаживаемого устройства формулы (2)-(8). Сигналы с второй двунали 59 проходят в отлаживаемое устройство при наличии сигналов разрешения 90 и записи 61. Сигналы с третьих информационных входов-выходов 46 .

на вторую двунаправленную информационную магистраль 59 при наличии разрешающего сигнала 90 и сигнала 60 чтения, что следует из формул (9) и

(10).

В третьем блоке 25 оперативной памяти содержится информация, управ ляющая обращением ЭВМ 1 к памяти в режиме отладки. Программа загрузки

третьего блока 25 оперативной памяти содержит адрес обращения к этому уз- у: при этом четыре старших разряда адреса подаются на первый канал 30 первого мультиплексора, остальные

разряды адреса подсоединены к соответствующим входам пятого дешифратора 13, четыре старших разряда второй двунаправленной информационной магистрали 59 поступают на входы

второго канала первого мультиплексора 30, а младший разряд - на информационный вход третьего блока 25 оперативной памяти. Код адреса сопро- вождается сигналом 61 записи. При на I личии сигналов уровня Лог,О на ; втором входе 61 записи и первом вы- I ходе 57 готовности и наличии соот- : ветствующего кода на остальных вхо- ; дах пятого дешифратора 13 на первом I выходе 77 последнего появляется I сигнал уровня Лог.1, разрешающий

передачу информатщи через первый ка- ; нал первого мультиплексора 30 и раз- I решающий запись информации в тре- i тий блок 25 оперативной памяти. В I то же время сигнал на втором выходе I 78 имеет уровень Лог.О, Информа- I ция, записанная .в третьем блоке 25 I оперативной памяти в дальнейшем ис- ; пользуется для определения, где рас- I полагается соответствующий сегмент памяти (либо в первом блоке 23 one- : ративной памяти 23, либо в отлажива- I емом устройстве). При этом младший I разряд второй двунаправленной ин- I формационной магистрали 59 содер- I жит информацию о месте расположения ; соответствующих сегментов памяти, а четыре старших разряда содержат код ;соответствующего сегмента памяти. Если по некоторому адресу в третьем блоке 25 оперативной памяти записан О, то в дальнейшем к соответствующему сегменту будут обращаться в первый блок оперативной памяти 23 в противном случае - к памяти отлаживаемого устройства.

В режиме отладки сигнал на первом выходе 57 готовности принимает уровень Лог.1, при этом на первом выходе 77 пятого дешифратора 12 появляется сигнал уровня Лог.О, а на втором выходе. 78 - уровня jlor.1 независимо от состояния сигналов на -остальных входах пятого дешифратора 13. Сигнал 57,таки1 образом, запрещает запись информации в третий блок 25 оперативной памяти и разрешает считьшакие информации из этого блока оперативной памяти. Теперь всякий раз, когда ЭВМ 1 выставляет на вторых адресных, входах 58 новый адрес, его старшие четыре разряда проходят через первый канал первого мультиплексора 30 на адресные входы третьего блока 25 оперативной памяти, а сигнал на выходе третьего блока

25 оперативной памяти указывает место нахождения сегмента памяти,задаваемого четырьмя старшими разряда- ми адреса.

Дешифратор 9 при наличии на его входах 60, 57 и 90 сигнала уровня Лог.О передает сигналы с входов

72на выходы 73 без изменения, в

противном случае.сигналы на выходах

73имеют уровень Лог.1. Программирование третьего 31

и четвертого 32 регистров адресом останова вьтолнения отлаживаемой программы и сравнение адресов схемой 40 сравнения в режиме отладки осуществляется следующим образом. Сигнал инициализации, появляющийся на первом выходе 62 сброса, поступает

на инверсный вход установки О первого триггера 33 и через первый элемент И 38 - на тактовый вход второго триггера 34, устанавливая на прямых выходах этих триггеров сигнал

уровня Лог.0, а на инверсном выходе второго триггера 34 - сигнал уровня Лог.1. Таким образом, решается работа блока 22 постоянной памяти, и ЭВМ 2 обрабатывает программу, содержащуюся в блоке 22 постоянной памяти о Получив команду загрузки третьего 31 и четвертого 32 регистров, ЭВМ 2 выполняет соответствующий адрес обращения на вторых адресных входах 58, сопровождая его сигналом на втором входе 61 записи уровня Лог.О, причем старший разряд адреса содержит 1. При этом в зависимости от выставленного адреса

на первом выходе 74 или втором выходе 75 появляется сигнал уровня Лог. 1, производящий запись информации в третий регистр 31 или четвертый

регистр 32 соответственно, при этом

в регистр записывается информация с второй двунаправленной информационной магистрали 59. Таким образом, каждому из этих регистров присвоен адрес обращения. В третий регистр 31

записывается код, который будет старшей частью адреса останова, в четвертый регистр 32 записывается . код, который будет младшей частью адреса останова. Тогда на выходах

этих регистров будет адрес останова, который подается на входы второго сравниваемого .числа схемы 40 сравнения. При работе устройства для отладки программно-аппаратных блоков

в режиме отладки на вторых адресных входах 58 будут проявляться коды ад ресов обращения ЭВМ 1 к первому блоку 23 оперативной памяти или памяти

,отлаживаемого устройства, и как только код адреса совпадет с кодом, заг-. писанным в третьем 31 и четвертом 32 регистрах, схема 40 сравнения сработает и на ее выходе появится сигнал уровня Лог.1, которьй положителъйым фронтом, подаваемым на од- новибратор 21, вызовет на выходе последнего импульс уровня Лог.1, который, пройдя через первый элемент И 38, своим положительным фронтом установит на выходе 91.низкий уровень. Этот же одиночньй импульс, пройдя через первый элемент НЕ 36, поступит на первый выход 62 сброса, производя начальную установку ЭВМ и других узлов. Таким образом, завершен цикл работы: обмен с управляющей ЭВМ - отладка.

Когда ЭВМ 2 закончит подготовку к работе всех узлов устройства для отладки программно-аппаратных блоков,- он вьтолнит цикл записи по адресу, состоящему из всех единиц кода, содержащего все единицы. При появлении этого адреса на вторых адресных входах 58 на третьем выходе 76 четвертого дешифратора 10 появится сигнал уровня Лог.1. Положительным фронтом сигнала на втором входе записи 61 информация с информационного входа первого триггера 33 перепишется на его выход. Логическая 1, появившаяся на выходе первого триггера 33, поступит на вход установки 1 второго триггера 34, и на первом выходе 57 готовности появится сигнал уровня Лог.О. Этот сигнал запретит работу ЭВМ 2, блока 22 постоянной памяти, а одновременно появившийся сигнал уровня Лог.1 на выходе 91 разрешит работу второго блока 24 оперативной памяти ЭВМ 1. Последняя начнет выполнять отлаживаемую программу.

Первый дешифратор 7 передает информацию с выходов второго регистра 16 на первые информационные входы-выходы устройства 79 при наличии сигнала уровня Лог.1 на входе 69, в противном случае на выходах первого дешифратора 7 все сигналы имеют уровень Лог. Ч. При необходимости передать информацию из управляющей

. 2568312

ЭВМ в устройство для отладки программно-аппаратных блоков .ynpaiiUHio- щая ЭВМ выста вляет соответствующий g код адреса обращения на первых адресных входах 42, сопровождая его сигналом на первом входе 43 записи. При этом на первом выходе 68 второго дешифратора 4 появляется сигнал уров10 ня Лог.1, который стробирует загрузку информации в первый регистр 15 с первых информационных входов- выходов 79, ЭВМ 2, обращаясь к третьему дешифратору 5, выставляет со15 ответствующий адрес и сопровождает его сигналом на втором входе 60 чтения. В результате информация с выходов регистра 15 без изменений передается на группу выходов третье20 го дещифратора 5, в противном случае на этих выходах присутствуют сигналы уровня Лог. Ч.

При необходимости передать информацию из устройства для отладки про25 граммно-аппаратных блоков в управляющую ЭВМ ЭВМ 2 выставляет соответст- , вующий код адреса обращения на вторых адресных входах 58, сопровождая его сигналом на втором входе 61 за30 писи. При этом на выходе третьего дешифратора 5 появится сигнал уровня Лог.1, который стробирует загрузку информации во второй регистр 16. Управляющая ЭВМ, обращаясь к

35 первому дешифратору 7, выставляет .соответствующий адрес и сопровождает его сигналом на первом входе 44 чтения. В результате информация с выходов второго регистра 16 без измене40 ния передается на выходы первого дешифратора 7. Сигнал на первом выходе 62 сброса второго дешифратора 4 всегда повторяет сигнал на первом входе 45 сброса.

45 Деп(ифратор 11 реализует следующие

логические функ1дии:

X

93

V X

ei

(11)

50

где сигнал с выхода nepenoj He- ния первого счетчика 27 импульсов;

66

( ( Хгч f X ЛХ„, Л X, V X

30

Хз,)Л

(12)

4t

9

где X

91

- сигнал на прямом выходе второго триггера;

X,, N

13

х

бг

(13)

X

сигнал с выхода перепол- второго счетчика 28 импульсов;

(X

28 29

V X

30

м х,,)л

л х,4 л X

91

При вьщаче сигнала инициализации на первом выходе 62 сброса появляетс сигнал уровня Лог.О, которьм в соответствии с (11) и (12), пройдя через седьмой дешифратор 11, производит начальную установку первого 27 и второго 28 счетчиков импульсов. На выходах обоих счетчиков импульсов устанавливается код, состоящий из всех нулей. При работе ЭВМ 2 по программе, содержащейся в блоке 22 постоянной памяти, запись информации во второй блок 24 оперативной памяти производиться не будет, поскольку в этом режиме сигнал на выходе 91 принимает значение Лог.О, и в соответствии с (14) на пятом выходе 88 седьмого дешифратора 11 появится пас сивньй сигнал уровня Лог.0, который запретит запись информахщи во второй блок 24 оперативной памяти.

В режиме отладки сигнал на выходе 91 принимает значение Лог.1. В дальнейшем, выполняя отлаживаемую программу, ЭВМ 1 сопроволодает адреса и данные одним из управляющих сигналов на втором входе записи 61 или чтения 60, которые принимают значения Лог.О. При этом в соответствии с (|14) на пятом выходе 88 седьмого дешифратора 11 появляется сигнал уровня Лог.1, разрешающий запись во второй блок 24 оперативной памяти. По окончании действия сигнала на входе 60 или 61, а также во всех тактах, когда активен хотя бы один из сигналов, на входах 64 и 65 в соответствии с (12) отрицательный перепад сигнала на третьем выходе 86 седьмого дешифратора 11 производит увеличение кода на единицу на информационных вькодах второго счетчика импульсов 28. Этот код поступает на адресные входы второго блока 24 оперативной памяти и является еле дующим .адресом, по которому производится запись новой информации. При переполнении второго счетчика 28 им

U

-; пульсов на его выходе 92 переполнения появляется импульс, который в соот- ветствии с (13) поступает на вход тановки О второго счетчика 28 им- пульсов. И последующая информация будет записываться с нулевых адресов. После окончания режима отладки сиг- наЛ на выходе 91 принимает значение 10 Лог.О и в соответствии с (14) запись информации во второй блок 24 оперативной памяти 24 производиться не будет.

ЭВМ 2, отрабатывая программу, со15 держащуюся в постоянной памяти 22, получает команду чтения информации из второго блока 24 оперативной памяти и переходит к выполнению соответствующих подпрограмм, выставляя

20 при этом соответствующий адрес обращения и сопровождая его сигналом на втором входе 60.чтения уровня Лог .О..При этом на втором выходе 85 седьмого дешифратора 11 появляет-

25 ся сигнал уровня Лог.1, который поступает,на вход чтения второго блока 24 оперативной памяти. На выходах второго блока 24 оперативной памяти появляется записанн ая ранее

30 информация, которая представлена не.более чем 64 разрядами (два байта - данные, три разряда - с выходов 98, 100 и 101, два разряда - с первого 64 и второго 65 входов зада35 ния режима, остальные разряды - код адреса с вторых адресных входов 58); все разряды разбиты на четыре равные группы, и сигналы с ,них поступают на соответствующие каналы

40 второго мультиплексора 29.

Чтение информации из второго блока 24 оперативной памяти производится по нулевого адресу, так как после окончания режима отладки узел

45 сравнения вырабатывает сигнал начальной установки на первом выходе 62 сброса, которьш в соответствии с (11), (13) производит сброс счетчиков 27 и 28 импульсов, на выходах

50 которых присутствует нулевой код. Нулевой код с выходов первого счетчика 27 импульсов поступает на два управляющих входа второго мультиплексора 29, что соответствует передаче

55 информации с первого канала сквозь девятьш дешифратор 12 на вторую двунаправленную информационную магистраль 59. Девятьм дешифратор 12 передает инфор мацию с выходов второго

мультиплексора 29 на выходы 59 без изменений при наличии сигнала уровня Лог.Г на выходе 91, в противном случае все сигналы на вькодах. девятого дешифратора 12 имеют уровень Лог.1. Сигнал с второго выхода 85 седьмого дешифратора 11 поступает также на счетный вход первого счетчика 27 импульсов и при окон- мании этого сигнала, отрицательным переходом, т.е. при окончании чтения информации с первого канала второго мультиплексора 29, происходит увеличение на единицу кода, присутствующего на выходах первого счетчика 27 импульсов.

Таким образом, на выходе первого счетчика 27 импульсов будет код 01 и при следующем чтении информации из второго блока 24 оперативной памяти передается через второй мультиплексор 29 код с его второго канала. Информация с второго, третьего и четвертого каналов второго мультиплек- сора 29 прочитывается аналогичным образом. При пятом обращении к второму, блоку 24 оперативной памяти на выходе 93 переполнения первого счетчика 27 импульсов появляется сигнал уровня Лог.1, который в соответствии с (11) производит начальную установку первого счетчика 27 импуль

сов, и этот же сигнал в соответствии

с (12) поступает на счетный вход вто- g НЕ 36. Учитывая это, сигнал 89 на

рого счетчика 28 импульсов, увеличивая на единицу код на его информационных выходах, что соответствует следующему адресу обращения к второму блоку 27 оперативной памяти.

Для корректной интерпретации трассировочной информации, содержа- щейся во втором блоке 24 оперативной памяти, в него необходимо записать информацию о глубине очереди команд ЭВМ 1. Эта информация формируется на инверсных выходах третьего 17, четвертого 18 и пятого 19 триггеров.

Функционирование десятого дешифратора 6 описывается следующими выражениями:

выходе шестого триггера 20 будет иметь низкий уровень в такте Т4 ци ла выборки команды (а не в цикле о ращения в память за операндом) в т

4Q чение времени, пока сигнал на выхо 67 генератора импульсов имеет уровень Лог.О. Появление комбинаци сигналов на входах 64 и 65 в такте Т4 свидетельствует о том, что в та

45 же ТЗ блок очереди команд очищен. Эти сигналы, поступая уровнями Ло 1 на входы третьего элемента И 3 приводят к появлению импульса уров Лог.О во втором полупериоде так та Т4, который в третий 17, четвер тый 18 и пятый 19 триггеры записывает единичную и 1формацию, а на их инверсных выходах появляется сигна уровня Лог.О. Согласно формуле (15) состояние третьего триггера 1 необходимо изменять на противополо ное, если глубину очереди команд надо изменять на единицу: плюс оди если в такте Т4 цикла выборки кома

50

Y у

60

X,,;

(15)

8(

- XgjA Xgj, Л

X,, V Х,,7Л

84

.9, л

Х;,

(16)

Л

96

X

1оо

X.,

9

f X.eV

X

96

А Х,(,(, Л X

74

Xg,v

(17)

л

Xqq Л X

7(

Л X

89

,

В текущем такте код на первом 64 и втором 65 входах задания режима свидетельствует о том, что происхо- дит с блоком очереди в предыдущем такте. Цикл шины ЭВМ 1 длится четыре такта сигнала иа выходе 67 генератора импульсов. В тактах Т1 и Т2 каждого цикла шины сигнал на входе 66 строба адреса имеет уровень Лог.О. Если в течение данного цикла шины происходит выборка из памяти кода команды, то сигнал на входе 63 признака выборки команды имеет уровень Лог.О в течение

тактов Т1, Т2 и ТЗ. Нумерация сигналов (на чертеже) соответствует нумерации управляющих линий, на которых эти сигналы появляются. В седьмом триггере 26 по положительному фронту сигнала на входе 66 строба адреса запоминается значение младшего разряда адреса, который был выставлен ЭВМ в текущем цикле шины. Задержка, вносимая элементом 8 задержки,должна быть минимальной, но больше, чем заержка, вносимая вторым, элементом

НЕ 36. Учитывая это, сигнал 89 на

выходе шестого триггера 20 будет иметь низкий уровень в такте Т4 цикла выборки команды (а не в цикле обращения в память за операндом) в те-

чение времени, пока сигнал на выходе. 67 генератора импульсов имеет уровень Лог.О. Появление комбинации сигналов на входах 64 и 65 в такте Т4 свидетельствует о том, что в также ТЗ блок очереди команд очищен. Эти сигналы, поступая уровнями Лог. 1 на входы третьего элемента И 37, приводят к появлению импульса уровня Лог.О во втором полупериоде такта Т4, который в третий 17, четвертый 18 и пятый 19 триггеры записывает единичную и 1формацию, а на их инверсных выходах появляется сигнал уровня Лог.О. Согласно формуле (15) состояние третьего триггера 17 необходимо изменять на противоположное, если глубину очереди команд надо изменять на единицу: плюс один, если в такте Т4 цикла выборки коман

ды быпа информация об исполнении байта команды (в этом такте сигнал на первом входе задания режима 64 имеет высокий уровень), и минус один, если информация об исполнении байта появляется в любом другом такте. В соответствии с (16) состояние четвертого триггера 18 необходимо изменять на противоположное в следующих случаях: глубину очереди команд надо увеличить на два в связи с тем, что производится выборка кода команды по четному адресу - в этом случае ЭВМ 1 выбирает за одно обращение к памяти 2 байта. Увеличение на два производится также в Т4 и только при условии,что в такте ТЗ не вьтол- няется байт команды (т.е. в такте

Т4 сигнал на первом входе задания ре- 20 входов схемы сравнения, с группами жима 64 имеет уровень Лог.О). Со- входов четвертого и пятого дешифра18

стояние второго триггера Its надо также менять, если глубина увеличивается на один и она имеет нечетное значение, надо уменьшить на один, а она имеет четное значение. В соответствии с (17) состояние пятого триггера 19 надо изменять на противоположное, если глубину надо увеличить на один, а она равна трем, если глубину надо уменьшить на один, а она равна четырем, и если глубину надо увеличить на два, а она равна двум или трем. Максимальная глубина очереди равна . шести. Десятый дешифратор 6 выдает единицу на Т-входы тех триггеров, состояние которых надо изменять в текущем такте; изменение происходит по положительному фронту сигнала на выходе 67 генератора импульсов.

Формула и зобретения

Устройство для отладки программно- аппаратных блоков, содержащее девять дешифраторов, генератор тактовых импульсов, первый, второй, третий и четвертый, регистры, блок постоянной памяти, первый, второй и третий блоки оперативной памяти, первый и второй счетчики импульсов, первый и вто- рой мультиплексоры, первый и второй триггеры, первый и второй элементы НЕ, одновибратор, первый и второй , элементы И, схему сравнения,.причем первая группа информационных входов- выходов устройства через первую двунаправленную магистраль соединена с группой информационных входов первоторов, с первой группой информационных входов первого мультиплексора, с первой группой входов шестого де25 шифратора, с группой входов седьмого дешифратора, с первой группой инфор- -мацйонных входов второго блока оперативной памяти и с второй группой входов третьего дешифратора, группа

30 выходов которого через вторую двунаправленную магистраль соединена с группой информационных входов перво го блока оперативной памяти, с груп пой информационных выходов блока по

25 стоянной памяти, с группой выходов восьмого дешифратора, с второй груп пой информационных входов второго блока оперативной памяти, с группами информационных.входов второго, тре40 тьего и четвертого регистров, с вто рой группой информационных входов первого мультиплексора, с второй гр пой входов шестого дешифратора, с группой выходов девятого дешифратора

45 с первой группой выходов шестого дешифратора и с второй группой информационных входов-выходов устройства группа выходов второго регистра соединена с группой входов первого деgQ шифратора, второй вход чтения устройства соединен с входами чтения блока постоянной памяти, первого бл ка оперативной памяти, с первыми вх :дами третьего, шестого, седьмого и

5g восьмого дешифраторов, второй вход записи устройства соединен с первым входом пятого де1Ш1фратора, с вторыми входами третьего, шестого и седь мого дешифраторов, входом четвертог

14) регистра и группой выходов первого дешифратора, первые адресные .входы, первые входы записи, чтения и сбро- .

са устройства соединены с входами второго де Ш1фратора, первый, второй и третий выходы которого соединены соответственно с входом записи пер- Bo. регистра, входом первого дешиф- .

ратора и первым выходом сброса устройства, группа выходов первого регистра соединена с первой группой входов третьего дe ш фpaтopa, выход которого соединен с входом записи

второго регистра, вторая группа адресных входов устройства соединена с группами адресных входов блока постоянной памяти, первого блока оперативной памяти, с первой группой

торов, с первой группой информационных входов первого мультиплексора, с первой группой входов шестого дешифратора, с группой входов седьмого дешифратора, с первой группой инфор- мацйонных входов второго блока оперативной памяти и с второй группой входов третьего дешифратора, группа

выходов которого через вторую двунаправленную магистраль соединена с группой информационных входов первого блока оперативной памяти, с группой информационных выходов блока постоянной памяти, с группой выходов восьмого дешифратора, с второй группой информационных входов второго блока оперативной памяти, с группами информационных.входов второго, третьего и четвертого регистров, с второй группой информационных входов первого мультиплексора, с второй группой входов шестого дешифратора, с группой выходов девятого дешифратора,

с первой группой выходов шестого дешифратора и с второй группой информационных входов-выходов устройства, группа выходов второго регистра соединена с группой входов первого дешифратора, второй вход чтения устройства соединен с входами чтения блока постоянной памяти, первого блока оперативной памяти, с первыми вхо- дами третьего, шестого, седьмого и

восьмого дешифраторов, второй вход записи устройства соединен с первым входом пятого де1Ш1фратора, с вторыми входами третьего, шестого и седьмого дешифраторов, входом четвертого

19

деш1фратора, тактовым входом первог триггера, с входом записи первого блока оперативной памяти, группа информационных выходов первого блока оперативной памяти соединена с группой входов восьмого дешифратора, первьй и второй выходы четвертого дешифратора соединены с тактовыми входами третьего и четвертого регистров, группа информационных выходо которых соединена с второй группой входов схемы сравнения, выход которой через одновибратор соединен с пвым входом первого элемента И и через первый элемент НЕ - с вторым входом первого элемента И, с входом установки нуля первого триггера, с третьими входами шестого и седьмого

дешифраторов и с третьим выходом вто- 20 ройства, выходом признака выборки рого дешифратора, третий выход .чет- команды устройства, выход генерато- вертого дешифратора соединен с информационным входом первого триггера, выход которого соединен с входом

ра тактовьк импульсов соединен с вхо дом второго элемента И, вход признака выборки команды устройства соеди

установки в 1 второго триггера, ин- 25 нен с пятым входом шестого дешифраформационный вход второго триггера Соединен с шиной нулевого потенциала устройства, выход первого элемента .И соединен с тактовьм входом второго триггера, инверсный выход которого соединен с первым входом обращения первого блока оперативной памяти, с входом обращения блока постоянной памяти, с вторыми входами пятого и восьмого дешифраторов и с первым выходом готовности устройства, прямой выход второго триггера соединен с первым входом второго элемента И и с четвертым входом седьмого дешифратора, первый выход пятого дешифратора соединен с входом записи третьего блока оперативной памяти и управляющим входом первого мультиплексора, группа выходов которого соединена с

50

группой адресных входов третьего бло- 45 Р выходы переполнения первого и ка оперативной памяти,второй выход пятого дешифратора соединен с входом чтения третьего блока оперативной памяти, выход которого соединен с третьим входом восьмого дешифратора и вторым входом обращения первого блока оперативной памяти, старший разряд информационных выходов блока постоянной памяти соединен с информационным входом третьего блока оперативной памяти, выход которого соединен с четвертым входом шестого дешифратора и вторым входом второго элемента И, вход готовности устройвторого счетчиков импульсов соедин ны соответственно с пятым и шестым входами седьмого дешифратора,групп информационных выходов первого и второго счетчиков импульсов соедин ны соответственно с группой управл ющих входов второго мультиплексора и группой адресных входов второго блока оперативной памяти, первая, 55 вторая, третья и четвертая группы выходов второго блока оперативной памяти соединены соответственно с первой, второй, третьей н четверто группами информацнонньтх входов вто

5683

20

ства соединен с третьим входом второго элемента И, выход которого соединен с вторым выходом готовности устройства, вторая группа выходов шестого дешифратора соединена с третьей группой входов шестого дешифратора и является третьей группой информационных входов-выходов устройства, третья группа выходов тесто- .то дешифратора является группой адресных выходов устройства, первый, второй, третий, четвертый, пятый, шестой и седьмой выходы шестого де- 5 шифратора являются соответственно первыми выходами чтения, записи, строба адреса устройства, вторым выходом с броса устройства, первым и вторым выходами задания режима уст0

ройства, выходом признака выборки команды устройства, выход генерато-

ра тактовьк импульсов соединен с входом второго элемента И, вход признака выборки команды устройства соедитора, первый вход задания режима .устройства соединен с шестым входом шестого дешифратора,второй вход задан режима устройства соединен с седьмым

30 входом шестого дешифратора, вход строба адреса устройства соединен с восьмым входом шестого дешифратора, первый, второй, третий, четвертый и пятый выходы седьмого дешифратора

35 соединены соответственно с входами установки нуля первого и второго счетчиков импульсов, со счетными входами первого и второго счетчиков импульсов и с первым входом об40 ращения второго блока оперативной памяти, второй выход седьмого дешифратора соединен с вторым входом обращения второго блока оперативной памяти и входом девятого дешифрато

Р выходы переполнения первого и

второго счетчиков импульсов соединены соответственно с пятым и шестым входами седьмого дешифратора,группы нформационных выходов первого и второго счетчиков импульсов соединены соответственно с группой управлящих входов второго мультиплексора и группой адресных входов второго блока оперативной памяти, первая, вторая, третья и четвертая группы выходов второго блока оперативной памяти соединены соответственно с первой, второй, третьей н четвертой группами информацнонньтх входов второго мультиплексора, группы выходов которого соединены с группой входов девятого дешифратора, первый и второй входы задания режима устройства соединены соответственно с первым и вторым информационными входами второго блока оперативной памяти и с седьмым и восьмым входами седьмого дешифратора, выход генератора импульсов соединен с девятым входом седьмого дешифратора, отличающееся тем, что, с целью расширения функциональных возможностей за счет повьшения допустимых частот отладки в реальном масштабе времени, в устройство введены десятый деишфратор, третий элемент И, третий элемент НЕ, элемент задержки, третий, четвертый, пятый, шестой и седьмой триггеры, прич.ем первый вход задания режима устройства соединен с входом третьего элемента НЕ , выход которого соединен с первыми входами третьего элемента И и деся- того дешифратора, второй вход задания режима устройства соединен с вторым входом третьего элемента. И, выход генератора импульсов соединен с третьим входом третьего элемента И, выход которого соединен с входами установки единицы третьего, четвертого и пятого триггеров, вход признака выборки команды устройства через элемент задержки соединен с тактовым входом шестого триггера, информационный вход шестого триггера

соединен с шиной нулевого потенциа-

ла устройства, выход второго элемента НЕ соединен с входом установки единицы шестого триггера и с тактовыми ходами третьего, четвертого и пятого триггеров, мпадший разряд вто- рой группы адресных входов устройства соединен с информационным входом седьмого триггера, вход .строба адреса устройства соединен с тактовым

входом седьмого триггера, первый, второй и третий выходы десятого де- шифратора соединены соответственно с Т-входами третьего, четвертого и пятого триггеров, прямой и инверсный выходы седьмого и шестого триггера соединены соответственно с вто- рьм, третьим, четвертым и пятым вхо-. дами десятого дешифратора, прямые выходы третьего и четвертого триггеров соединены соответственно с шестым и седьмым входами десятого дешифратора, инверсные выходы третьего, четвертого и пятого триггеров соединены соответственно с восьмым,

девятым, десятым входами десятого дешифратора и с первым, вторым и третьим информационными входами второго блока оперативной памяти.

| Микропроцессоры | |||

| Системы программирования и отладки | |||

| / Под ред | |||

| В.А.Мясникова и М | |||

| В.Игнатьева | |||

| М.: Энергоиздат, 1985 | |||

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1988-09-23—Публикация

1986-10-21—Подача