Фиг.1

К отлаживаемому устройств;

Изобретение относится к вычислительной технике и может быть использовано при создании микроЭВМ, микроконтроллеров и других устройств на основе микропроцессоров.

Цель изобретения -повышение быстродействия при отладке прсчрамм.

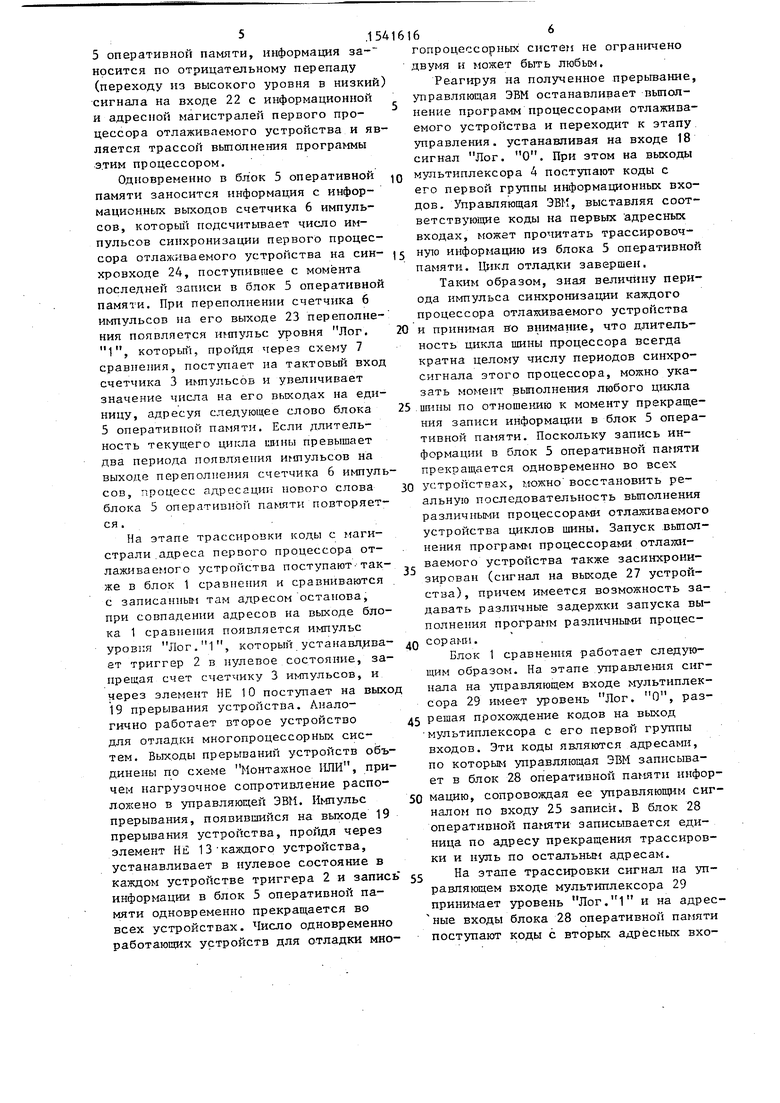

На фиг. 1 приведена схема предлагаемого устройства для отладки много- процессорных систем; на фиг. 2 - схема блока сравнения.

Устройство для отладки многопроцессорных систем состоит из блока 1 сравнения, триггера 2, счетчика 3 им- пульсов, мультиплексора 4, блока 5 оперативной памяти, счетчика 6 импуль сов, схемы 7 сравнения, элемента И 8, счетчика 9 импульсов, элемента НЕ 10, дешифратора 11, элементов НЕ 12 и 13, элемента И 14. Кроме того, устройство содержит группу информационных вхоцов выходов 15, вход 16 чтения, первую группу информационных входов 17, вход i18 задания режима, выход 19 прерыва- ния, группу адресных входов 20, вторую группу информационных входов 21, вход 22 обращения, выход 23 переполнения счетчика 6, синхровход 24, вход 25 записи, выход 26 сброса и выход

27синхро низации запуска. Блок 1 сравнения (фиг. 2) содержит блок

28оперативной памяти и мультиплексор 29.

Устройство работает следующим об- разом.

Цикл отладки состоит из этапов управления и трассировки. На этапе управления сигнал на входе 18 имеет уровень Лог.О, Этот сигнал поступает в блок 1 и разрешает запись в блок 1 адреса, при появлении которого на входах 20 устройства на трассировки будет прекращена запись информации в блок 5 оперативной памяти. Затем программируется третий счетчик 9 импульсов. При выполнении управляющей ЭВМ записи по определенному адресу срабатывает дешифратор 11 и на его выходе появляется сигнал логической 1, по которому в третий счетчик 9 импульсов заносится информация с его информационных входов. Этот счетчик является вычитающим, на его выходе переполнения, допускающем объединение по схеме Монтажное ЮМ появляется сигнал уровня логического О (отсутствие переполнения).

Аналогично программируется второе устройство для отладки многопроцессорных систем. Затем управляющая ЭВМ запускает выполнение программ в отлаживаемом устройстве и выставляет сигнал уровня 1 на входе 18 устройства, что означает переход к эта пу трассировки. По переходу сигнала на входе 18 в состояние 1 триггер

2устанавливается в единичное состояние и разрешает счет п счетчике 3 импульсов.

Управляющая ЭВМ программирует первое и второе устройства для отладки многопроцессорных систем последовательно и на выходе элемента И 12 появится сигнал при условии, когда все устройства для отладки многопроцессорных систем перейдут в режим трассировки,. При этом сигнал на выходе второго элемента И 14 будет повторять сигнал на его синхровходе 24. Предварительно записанная информация в третий счетчик 9 импульсов определяет задержку запуска выполнения отлаживаемой программы, которая задается в единицах периода сигнала тактиров- ки на синхровходе 24 устройства. Отсчитав заданное число импульсов, третий счетчик 9 импульсов выдает на своем выходе 26 единичный сигнал, блокируя прохождение импульсов тактиров- ки через элемент И 14. Выход 26 устройства подключен к входу сброса процессора отлаживаемого устройства и при появлении на нем сигнала уровня Лог.1 процессор начинает выполнение отлаживаемой программы.

На этапе трассировки сигнал на входе 22 имеет уровень Лог. Ч в течение времени, пока длится цикл шины первого процессора отлаживаемого устройства и уройень Лог. О в течение остального времени. Если циклы шины идут непрерывно один за другим, то на входе 22 присутствуют короткие импульсы уровня Лог.О, по положительному перепаду (переходу из низкого уровня в высокий) сигнал на входе 22 значение на выходе счетчика

3импульсов увеличивается на единицу. Присутствующий на управляющем входе мультиплексора 4 сигнал уровня Лог. 1 разрешает передачу информации на выходы мультиплексора 4 с его второй группы информационных входов. Код на выходе счетчика 3 импульсов является адресом занесения информации в блок

5 оперативной памяти, информация за- носится по отрицательному перепаду (переходу из высокого уровня в низкий сигнала на входе 22 с информационной и адресной магистралей первого процессора отлаживаемого устройства и является трассой выполнения программы этим процессором.

Одновременно в блок 5 оперативной памяти заносится информация с информационных выходов счетчика 6 импульсов, который подсчитывает число импульсов синхронизации первого процессора отлахашаемого устройства на син- хровходе 24, поступившее с момента последней записи в блок 5 оперативной памяти. При переполнении счетчика 6 импульсов на его выходе 23 переполнения появляется импульс уровня Лог, 1, который, пройдя через схему 7 сравнения, поступает на тактовый вход счетчика 3 импульсов и увеличивает значение числа на его выходах на единицу, адресуя следующее слово блока 5 оперативной памяти. Если длительность текущего цикла шины превышает два периода полвляенил импульсов на выходе переполнения счетчика 6 импульсов, троцесс адресации нового слова блока 5 оперативной памяти повторяется .

На этапе трассировки коды с магистрали адреса первого процессора отлаживаемого устройства поступают также в блок 1 сравнения и сравниваются с записанным там адресом останова, при совпадении адресов на выходе блока 1 сравнения появляется импульс уровня Лог. М, который устанавлива- ет триггер 2 в нулевое состояние, запрещая счет счетчику 3 импульсов, и через элемент НЕ 10 поступает на выхо 19 прерывания устройства. Аналогично работает второе устройство для отладки многопроцессорных систем. Выходы прерываний устройств объ- динены по схеме Монтажное ИЛИ, причем нагрузочное сопротивление расположено в управляющей ЭВМ. Импульс прерывания, появившийся на выходе 19 прерывания устройства, пройдя через элемент НЕ 13 каждого устройства, устанавливает в нулевое состояние в каждом устройстве триггера 2 и запись информации в блок 5 оперативной памяти одновременно прекращается во всех устройствах. Число одновременно работающих устройств для отладки мно

0

д $ 0 5

5

гопроцессорных систем не ограничено двумя и может быть любым,

Реагируя на полученное прерывание, управляющая ЭВМ останавливает выполнение программ процессорами отлаживаемого устройства и переходит к этапу управления, устанавливая на входе 18 сигнал Лог. О. При этом на выходы мультиплексора 4 поступают коды с его первой группы информационных входов. Управляющая ЭВМ, выставляя соответствующие коды на первых адресных входах, может пропитать трассировочную информацию из блока 5 оперативной памяти. Цикл отладки завершен.

Таким образом, зная величину периода импульса синхронизации каждого процессора отлаживаемого устройства и принимая внимание, что длительность цикла шины процессора всегда кратна целому числу периодов синхросигнала этого процессора, можно указать момент выполнения любого цикла шины по отношению к моменту прекращения записи информации в блок 5 оперативной памяти. Поскольку запись информации в блок 5 оперативной памяти прекращается одновременно во всех устройствах, можно восстановить реальную последовательность выполнения различными процессорами отлаживаемого устройства циклов шины. Запуск выполнения программ процессорами отлаживаемого устройства также засинхрони- зирован (сигнал на выходе 27 устройства), причем имеется возможность задавать различные задержки запуска выполнения программ различными процессорами.

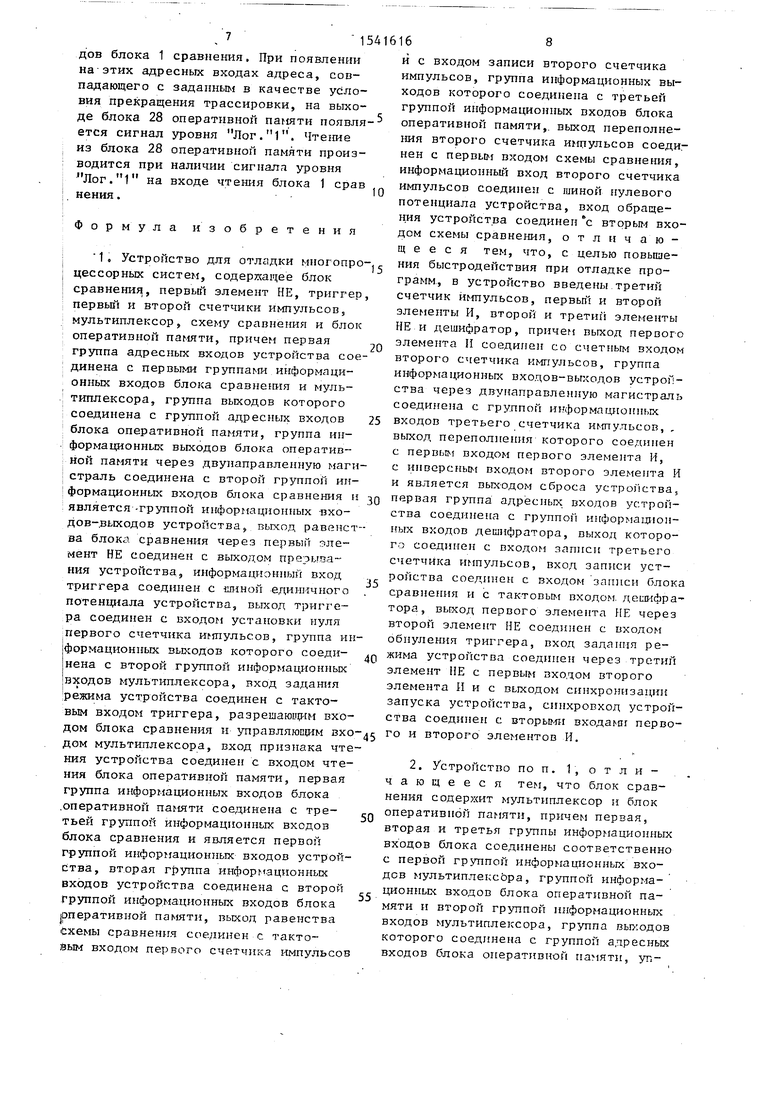

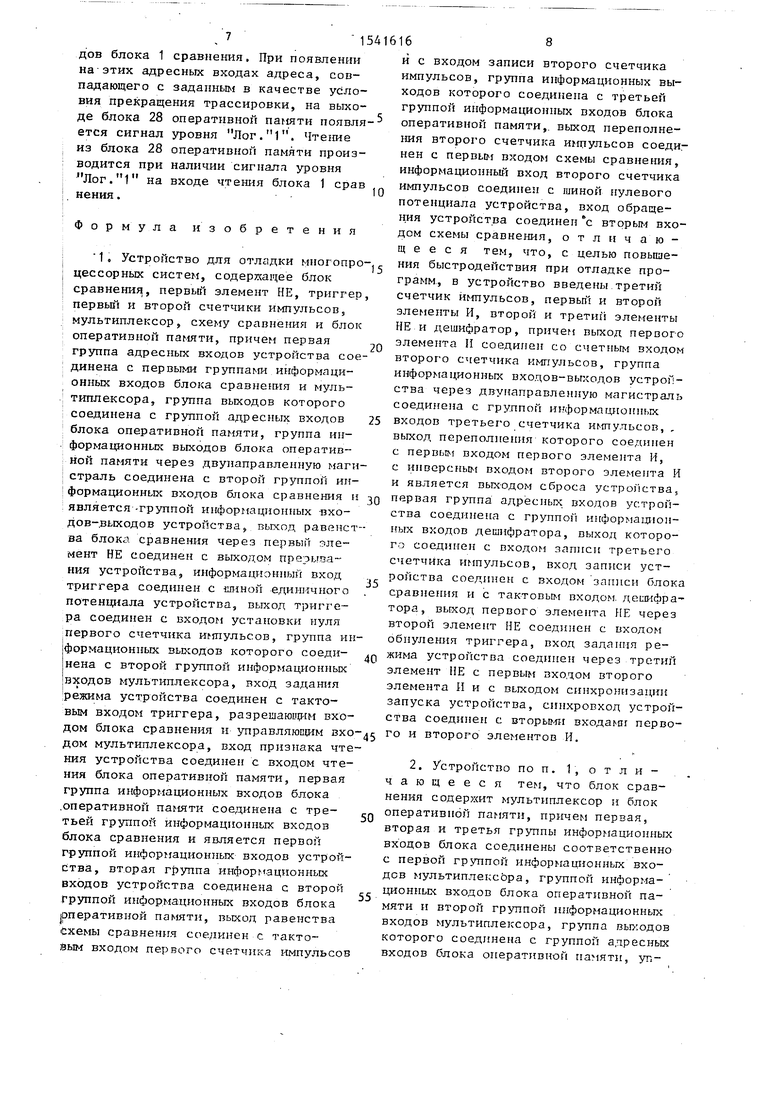

Блок 1 сравнения работает следующим образом. На этапе управления сигнала на управляющем входе мультиплексора 29 имеет уровень Лог. О, разрешая прохождение кодов на выход мультиплексора с его первой группы входов. Эти коды являются адресами, по которым управляющая ЭВМ записывает в блок 28 оперативной памяти информацию, сопровождая ее управляющим сигналом по входу 25 записи, В блок 28 оперативной памяти записывается единица по адресу прекращения трассировки и нуль по остальным адресам.

На этапе трассировки сигнал на управляющем входе мультиплексора 29 принимает уровень Лог. М и на адрес- ные входы блока 28 оперативной памяти поступают коды с вторых адресных вхо, 71541

дов блока 1 сравнения. При появлении на этих адресных входах адреса, совпадающего с заданным в качестве условия прекращения трассировки, на выходе блока 28 оперативной памяти появля-- ется сигнал уровня Лог. М. Чтение из блока 28 оперативной памяти производится при наличии сигнала уровня Лог. М на входе чтения блока 1 срав нения.

Формула изобретения

10

1, Устройство для отладки многопроцессорных систем, содержащее блок сравнения,, первьй элемент НЕ, триггер первый и второй счетчики импульсов, мультиплексор, схему сравнения и блок оперативной памяти, причем первая группа адресных входов устройства соединена с первыми группами информационных входов блока сравнения и мультиплексора, группа выходов которого соединена с группой адресных входов блока оперативной памяти, группа информационных выходов блока оперативной памяти через двунаправленную магистраль соединена с второй группой информационных входов блока сравнения и является -группой информационных входов-выходов устройства, выход равенства блоки сравнения через первьщ элемент НЕ соединен с выходом прерывания устройства, информационный вход триггера соединен с «мной единичного потенциала устройства, выход триггера соединен с входом установки нуля первого счетчика импульсов, группа информационных выходов которого соединена с второй группой информационных входов мультиплексора, вход задания режима устройства соединен с тактовым входом триггера, разрешающим входом блока сравнения и управляющим входом мультиплексора, вход признака чтения устройства соединен с входом чтения блока оперативной памяти, первая группа информационных входов блока оперативной памяти соединена с третьей группой информационных входов блока сравнения и является первой группой информационных входов устройства, вторая группа информационных входов устройства соединена с второй Группой информационных входов блока (рперативной памяти, выход равенства Схемы сравнения соединен с тактовым входом первого счетчика импульсов

8

0

5

0

5

0

5

0

5

и с входом записи второго счетчика импульсов, группа информационных выходов которого соединена с третьей группой информационных входов блока оперативной памяти, выход переполнения второго счетчика импульсов соединен с первым входом схемы сравнения, информационный вход второго счетчика импульсов соединен с шиной нулевого потенциала устройства, вход обращения устройства соединен с вторым входом схемы сравнения, отличающееся тем, что, с целью повышения быстродействия при отладке программ, в устройство введены третий счетчик импульсов, первый и второй элементы И, второй и третий элементы НЕ и дешифратор, причем выход первого элемента И соединен со счетным входом второго счетчика импульсов, группа информационных входов-выходов устроГ- ства через двунаправленную магистраль соединена с группой информационных входов третьего счетчика импутьсов, , выход переполнения которого соединен с первым входом первого элемента И, с инверсным входом второго элемента И и является выходом сброса устропства, первая группа адресных входов устройства соединена с группой информационных входов дешифратора, выход которого соединен с входом записи третьего счетчика импульсов, вход записи устройства соединен с входом записи блока сравнения и с тактовым входом дешифратора, выход первого элемента НЕ через второй элемент НЕ соединен с входом обнуления триггера, вход задания режима устройства соединен через третий элемент НЕ с первым зхоцом второго элемента И и с выходом синхронизации запуска устройства, синхросход устройства соединен с вторыми входами первого и второго элементов И.

2. Устройство по п. 1, отличающееся тем, что блок сравнения содержит мультиплексор и блок оперативной памяти, причем первая, вторая и третья группы информационных входов блока соединены соответственно с первой группой информационных входов мультиплексора, группой информационных входов блока оперативной памяти и второй группой информационных входов мультиплексора, группа выходов которого соединена с группой а есных входов блока оперативной памяти, уп9154161610

равляющий вход, вхоД записи и чтения входами записи и чтения блока опера- блока соединены соответственно с уп- тивной памяти, выход которого являет

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для отладки многопроцессорных систем | 1987 |

|

SU1446624A1 |

| Устройство для запоминания трассы функционирования многопроцессорных систем | 1990 |

|

SU1737454A1 |

| Устройство для отладки программно-аппаратных блоков | 1986 |

|

SU1363219A1 |

| Устройство для отладки программно-аппаратных блоков | 1986 |

|

SU1425683A1 |

| Устройство для отладки программ | 1988 |

|

SU1501102A1 |

| Устройство для отладки программно-аппаратных блоков | 1987 |

|

SU1497617A1 |

| Устройство для отладки программно-аппаратных блоков | 1985 |

|

SU1348839A1 |

| Устройство для отладки программ микроЭВМ | 1989 |

|

SU1815643A1 |

| Устройство для отладки программ | 1988 |

|

SU1511750A1 |

| Устройство для отладки программно-аппаратных блоков | 1988 |

|

SU1529228A1 |

Изобретение относится к области вычислительной техники. Целью изобретения является повышение быстродействия при отладке программ. Устройство позволяет задать последовательность и задержки запуска выполнения программ процессорами отлаживаемого устройства, а после окончания прогона отлаживаемых программ позволяет восстановить реальную последовательность взаимодействия процессоров отлаживаемого устройства. Устройство содержит блок 1 сравнения, элементы НЕ 10, 12 и 13, триггер 2, первый 3, второй 6 и третий 9 счетчики импульсов, мультиплексор 4, схему 7 сравнения и блок 5 оперативной памяти. 2 ил.

равляюцим входом мультиплексора, с

z°{lA

29

ся выходом неравенства блока.

т

w

М

so

ню

гг Фиг.1

| Микропроцессорные системы программирования и отладки | |||

| Под ред | |||

| В.А.Мясникова | |||

| И.: Энергоатомиздат, 1985, с | |||

| Ударно-долбежная врубовая машина | 1921 |

|

SU115A1 |

| Устройство для отладки многопроцессорных систем | 1987 |

|

SU1446624A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1990-02-07—Публикация

1988-02-02—Подача