Изобретение относится к вычислительной технике и может быть использовано для настройки, отладки и проверки работы специализированных мик- роЭВМ на основе микропроцессоров К580ИК80.

Целью изобретения является расширение функциональных возможностей за счет обеспечения контроля внутренних узлов микропроцессора.

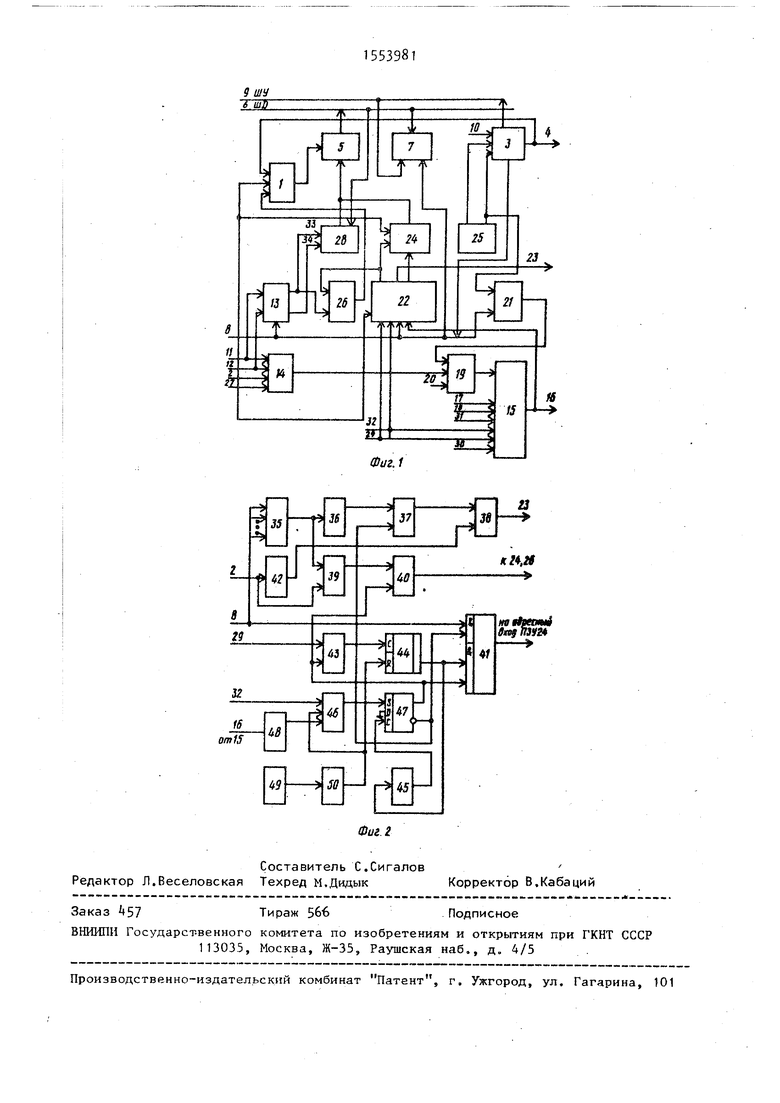

На фиг,1 приведена функциональная схема устройства для отладки микро- ЗВМ; на фиг.2 - функциональная схема блока формирования адреса.

Устройство для отладки микроЭВМ (фиг.1) содержит коммутатор 1, выход 2 разрешения чтения отлаживаемой микроЭВМ, блок 3 прямого доступа к памяти, вход k захвата отлаживаемой микроЭВМ, магистральный усилитель 5, магистраль 6 данных отлаживаемой

микроЭВМ, блок 7 индикации, выход 8 адреса отлаживаемой микроЭВМ, выход 9 управления отлаживаемой микроЭВМ, вход 10 подтверждения захвата отлаживаемой микроЭВМ, выходы 11 и 12 разрешения ввода и вывода соответственно микроЭВМ, дешифратор 13 адреса, блок k режимов останова, блок 15 готовности, вход 16 готовности отлаживаемой микроЭВМ, первый вход 17 задания режима устройства, вход 18 пуска устройства, элемент И 19, вход 20 управления остановом по адресу устройства, схему 21 сравнения, блок 22 формирования адреса, выход 23 разрешения обращения к памяти отлаживаемой микроЭВМ, блок 2 постоянной памяти, блок 25 задания адреса, элемент ИЛИ 26, выход 27 разрешечия записи отлаживаемой микроЭВМ, 6 ок 27 регистров, вход 29 синхронизации устройства,

ел ел

со со

00

315

второй вход 30 задания режима устройства, тактовый выход 31, вход 32 запуска устройства, вход 33 чтения блока регистров, вход 34 записи блока регистров 34

Блок 22 формирования адреса () содержит первый элемент И 35, первый элемент НЕ 36, второй элемент И 37, первый элемент ИЛИ 38, третий элемент И 39, второй элемент ИЛИ 40, блок элементов И-ИЛИ 41, второй элемент НЕ 42, четвертый элемент И 43, счет- чик 44, дешифратор 45, пятый элемент И 46, триггер 4, третий элемент НЕ 48, переключатель 49 режима, генератор 50 одиночного импульса о

Устройство для отладки микроЗВМ обеспечивает следующие аппаратные режимы отладки: общий останов по ад- ресу, останов по адресу при чтении из ОЗУ микроЭВМ, останов по адресу при записи в ОЗУ, останов по адресу при вводе информации из внешнего устройства, останов по адресу при выводе информации во внешнее устройство, шаговый режим поциклового прохождения программы, шаговый режим покомандного прохождения программы, режим прямого доступа к памяти и портам ввода-вывода отлаживаемой микро- ЭВМ, индикацию состояния микропроцессорной системы, чтение и индикацию внутренних узлов микропроцессора от- лаживаемой микроЭВМ.

Останов по адресу происходит при наличии разрешающего сигнала на входе 20 при совпадении адресов, поступающих на схему 21 сравнения с входа 8 и блока 25.

Работа в шаговом режиме отладки программы становится возможной при высоком потенциале на первом входе 17 задания режима. Причем при высоком потенциале на втором входе 30 задания режима останов производится в начале каждого цикла1 выполняемой команды по сигналам, поступающим с входа 29, а при низком только в начале команды по сигналам, поступающим с входа 32. Переход к выполнению нового цикла или команды обеспечивается подачей потенциала на вход 18 устройства.

В режиме прямого доступа к памяти можно производить запись, чтение ин- формации из памяти или портов ввода- вывода отлаживаемой микроЭВМ без участия микропроцессора. Адрес ячейки,

1

куда записывается или считывается информация, набирается в блоке 25.

Блок 3 прямого доступа к памяти выдает на выход 4 сигнал высокого уровня Захват, который, поступая также на коммутатор 1, разрешает выдачу информации на выход 6 через магистральный усилитель 5. По сигналу Захват микропроцессор отлаживаемой микроЭВМ после окончания выполнения очередной команды переводит свои шины в высокоимпедансное состояние и выдает сигнал Подтверждение захвата. После получения сигнала с входа 10 блок 3 управляет записью, чтением информации из памяти или портов ввода- вывода микроЭВМ, выдавая на выход 9 сигналы: Запись, Чтение, Ввод, Вывод. При выводе информации из памяти или портов ввода-вывода микроЭВМ производится только ее индикация с помощью блока 7 Блок 7 индикации, кроме шины данных, позволяет индицировать сигналы на адресном выходе 8 и выходе 9 о

Устройство в режиме чтения внутренних узлов микропроцессора отлаживаемой микроЭВМ работает следующим образом

Работой устройства в этом режиме управляет блок 22 (фиг.2). Предварительно устройство осуществляет останов по адресу в начале команды. При этом на выходе блока 15 готовности устанавливается сигнал низкого уровня, поступающий на вход 16 и на первый вход запуска блока 22, а на входе 32 устанавливается сигнал высокого уровня, который поступает на третий вход блока 22. Микропроцессор отлаживаемой микроЭВМ устанавливается в состояние ожидания и находится в этом состоянии до тех пор, пока на выходе 16 готовности не появится сигнал высокого уровня.

Для осуществления режима чтения внутренних узлов микропроцессора отлаживаемой микроЭВМ включается переключатель 49 режима (фиг„2). При этом на выходе генератора 50 одиночного импульса формируется строб,, который сбрасывает счетчик 44 и через элемент И 46 устанавливает по единичному входу триггер 47. Сигнал высокого уровня с единичного выхода триггера 47 через элемент ИЛИ 40 поступает на вход разрешения доступа блока 24, а сигнал низкого уровня с нулевого

5

выхода триггера 7 на вход элемента И 37, блокируя формирование сигнат ла разрешения обращения к памяти на выходе 23. Таким образом, блокирует- ся чтение команды из ОЗУ микроЭВМ и разрешается обращение к блоку 2k. Сигнал высокого уровня с единичного выхода триггера kf поступает также на вход элемента И 3, разрешая про- хождение сигналов с входа 29 на счетный вход счетчика kk, и на вход блока элементов И-ИЛИ k, коммутируя на адресный вход блока 2k выходы счетчика kk. Так как счетчик kk сбро- шен, то на адресный вход блока 2k поступает нулевой код. В трех начальных адресах блока 2k хранится код команды вызова подпрограммы чтения внутренних узлов микропроцессора отлаживаемой микроЭВМ (CALL a1, a,

15

где at , а 2 - адрес входа в подпрограмму). Таким образом, при подаче сигнала пуска на вход 18 на выходе 16 готовности формируется сигнал высокого уровня и вместо чтения очередной команды из ОЗУ микроЭВМ происходит чтение команды CALL из блока 2k. Команда вызова подпрограммы (CALL af , a2) имеет длину три байта и выполняется за 5 циклов. Первые три цикла используются для чтения команды из памяти, а четвертый и пятый - для загрузки в стек содержимого счетчика команд. Счетчик kk ведет подсчет сигналов начала машинного цикла, которые поступают с входа 29. По каждому импульсу, поступающему с входа 29 синхронизации, содержимое счетчика kk увеличивается на единицу, таким образом формируется код следующего адреса блока 2k. При поступлении третьего сигнала начала машинного цикла с входа 29 синхронизации на выходе счетчика устанавливается код 011. Дешифратор 5 по этому коду формирует сигнал высокого уровня, который сбрасывает триггер kj. На единичном выходе триггера k формируется сигнал низкого уровня, который поступает на вход элемента ИЛИ kO и снимает сигнал разрешения доступа к блоку 2k. Сигнал низкого уровня с единичного выхода триггера kj блокирует прохождение последующих импульсов с входа на счетный вход счетчика kk, а также запрещает прохождение сигналов с выхода счетчика kk на адресный вход блока 2k. Сигнал высокого уровня

т,- ю - 15 5539816

с нулевого выхода триггера 7 поступает на вход элемента И 37, разрешая формирование сигнала на выходе 23 разрешения обращения к памяти микро- ЭВМ, а также на вход блока элементов И-ИЛИ М, коммутируя на адресный вход блока 2k сигналы с входа 8 адреса.

После выполнения команды CALL происходит переход на программу чтения внутренних узлов микропроцессора отлаживаемой микроЭВМ, которая хранится в блоке 2k. Блок занимает конечную зону в адресуемом микроЭВМ поле памяти. Начальный адрес и величина зоны памяти, отводимой под блок

ы

20

выражения А

о

формируемый

30

35

2kt определяются из

п

& А ., где А в - сигнал,

i k

на выходе элемента И 35, А, - сигнал на i-й шине 8 адреса. Например, при , блок 2k размещается в об-

25 ласти адресов F800FFFF/f.

В результате выполнения подпрограммы содержимое внутренних узлов микропроцессора переписывается в блок 28 регистров. Обращение к блоку 28 регистров происходит как к портам ввода-вывода отлаживаемой.микроЭВМ {т.е. используются команды OUT, 1N). Блок 13 формирует сигналы записи в блок 28 регистров.

В процессе выполнения подпрограммы чтения внутренних узлов микропроцессора происходит модификация содержимого счетчика команд, хранящегося в области стека. Это необходимо для

4Q организации возврата в ту точку программы, где был произведен останов. Выход из подпрограммы происходит по команде PET после того, как будет восстановлено содержимое внутренних

45 узлов микропроцессора, затертое в процессе выполнения подпрограммы. После выполнения команды PET в первом цикле следующей команды на входе 8 адреса выставляется адрес, по которому был произведен останов, и на выходе схемы 21 сравнения формируется сигнал высокого уровня (так как в блоке 25 набран тот же код адреса). На входе 20 устройства присутствует сигнал высокого уровня, который с выхода элемента И 19 поступает на вход блока 15 готовности,-после чего на выходе 16 готовности появляется сигнал низкого уровня. Микропроцессор

50

55

715

отлаживаемой микроЭВМ переходит в состояние ожидания.

После этого устройство переводится в режим прямого доступа к памяти и производится вывод и индикация информации из блока 28 регистров, в котором хранится содержимое внутренних узЬов микропроцессора. Каждый регистр

СГП О«

из блока 28 имеет свой фиксированный адрес в области адресов внешних устройств (от 1 до 256) и каждому регистру соответствует определенный вйутренний регистр микропроцессора.

После чтения и индикации содержимого внутренних узлов микропроцессора, хранящегося в блоке 28 регистров, снимается сигнал с входа 20, выключается тумблер задания режима в блоке 2л и снимается сигнал Захват в блоке 3 прямого доступа к памяти. Пфсле этого микропроцессор продолжает выполнение приостановленной программы. I Формула изобретения

1. Устройство для отладки микро- ЭВМ, содержащее коммутатор, магистральный усилитель, блок индикации, блок прямого доступа к памяти, схему сравнения, блок режимов останова, блок постоянной памяти, блок готовно ф-и, элемент ИЛИ и элемент И, причем ЕХОД разрешения чтения устройства соединен с первым информационным входом коммутатора и входом чтения блок гостоянной памяти, выход которого соединен с информационным входом магистрального усилителя, выход захвата блока прямого доступа к памяти является выходом захвата магистрали уст- 0ойства и соединен с вторым информационным входом коммутатора, выход элемента ИЛИ соединен с управляющим входом коммутатора, выход которого соединен с управляющим входом магистрального усилителя, выход которого через двунаправленную магистраль соединен с первым входом блока инди- кации, информационным выходом блока прямого доступа к памяти и является йыходом данных устройства, выход режима блока прямого доступа к памяти Соединен с вторым входом блока индикации и с выходом управления устройства, адресный выход блока прямого доступа к памяти соединен с первым входом схемы сравнения, с третьим

я

5

0

5

0 5 0 д5 50

55

входом блока индикации и является адресным выходом устройства, вход подтверждения захвата устройства соединен с разрешающим входом блока прямого доступа к памяти, выход схемы сравнения соединен с первым входом элемента И, вход управления остановом по адресу устройства соединен с вторым входом элемента И, выход блока режима останова соединен с третьим входом элемента И, выход которого соединен с первым входом блока готовности, входы разрешения ввода, разрешения вывода, разрешения чтения, разрешения записи устройства соединены соответственно с первым, вторым, третьим и четвертым входами блока режимов останова, первый вход задания режима, вход пуска, вход синхронизации, второй вход задания режима, тактовый вход и вход признака начала команды устройства соединены соответственно с вторым, третьим, четвертым, пятым, шестым и седьмым входами блока готовности, выход которого является выходом готовности устройства, отличающееся тем, что, с целью расширения функциональных возможностей устройства за счет обеспечения контроля внутренних узлов микропроцессора, введены блок регистров, блок формирования адреса,дешифратор адреса и блок задания адреса, причем входы разрешения ввода и вывода устройства соединены соответственно с первым и вторым адресными входами дешифратора адреса, первый и второй выходы которого соединены соответственно с входами чтения и записи блока регистров, выход которого соединен с информационным входом магистрального усилителя, информационный выход блока прямого доступа к памяти соединен с информационным входом блока регистров, адресный выход блока прямого доступа к памяти соединен с информационным входом дешифратора адреса и адресным входом блока формирования адреса, выход разрешения доступа которого соединен с входом обращения блока постоянной памяти и первым входом элемента ИЛИ, первый выход дешифратора адреса соединен с вторым входом элемента ИЛИ, выход блока готовности, входы признака начала команды и синхронизации устройства соединены соответственно с первым входом запуска, вторым входом запуска и тактовым

9

входом блока формирования адреса, вход разрешения чтения устройства соединен с входом обращения блока фмирования адреса, выходы разрешения обращения и адресный выход которого соединены соответственно с выходом обращения устройства и адресным входом блока постоянной памяти, первый и второй информационные выходы блок задания адреса соединены соответственно с информационным и адресным входами блока прямого доступа к пам

ти, второй информационный выход блока задания адреса соединен с вторым входом схемы сравнения.

2. Устройство по п.1, о т л и - чающееся тем, что блок формирования адреса содержит пять элементов И, два элемента ИЛИ, три элемента НЕ, элемент 2И-ИЛИ, счетчик, триггер, дешифратор, генератор одиночного импульса и переключатель режима, причем адресный вход блока соединен с первым

входом элемента 2И-ИЛИ и с входами первого элемента И, выход которого через первый элемент НЕ соединен с первым входом второго элемента И, вход обращения блока соединен непосредственно с первым входом третьего элемента И и через второй элемент НЕ - с первым входом первого элемента ИЛИ, выход первого элемента И соединен с вторым входом третьего элемента И, выход которого соединен с первым входом второго элемента ИЛИ, прямой

10

выход триггера соединен с вторым входом элемента 2И-ИЛИ, первым вхо0

5

п

5

0

5

дом четвертого элемента И и вторым входом второго элемента ИЛИ, выход которого является выходом разрешения обращения блока, инверсный выход триггера соединен с третьим входом элемента 2И-ИЛИ, с вторым входом второго элемента И, выход которого соединен с вторым входом первого элемента ИЛИ, выход которого является выходом разрешения обращения к памяти отлаживаемой ЭВМ блока, синхровход блока соединен с вторым входом четвертого элемента И, выход которого соединен с тактовым входом счетчика, информационный выход которого соединен с входом дешифратора и четвертым входом элемента 2И-ИЛИ, выход которого является адресным выходом блока, выход переключателя режимов соединен с входом запуска генератора одиночных импульсов, выход которого соединен С первым входом пятого элемента И и входом сброса счетчика, выход дешифратора соединен с тактовым входом триггера, первый тактовый вход блока через третий элемент НЕ соединен с вторым входом пятого элемента И, выход которого соединен с единичным входом триггера, второй вход запуска блока соединен с третьим входом пятого элемента И, шина нулевого потенциала блока соединена с информационным входом триггера.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для отладки программ микроЭВМ | 1989 |

|

SU1815643A1 |

| Устройство для отладки микроЭВМ | 1985 |

|

SU1247877A1 |

| Устройство для отладки программ | 1987 |

|

SU1462327A1 |

| Устройство для отладки микроЭВМ | 1986 |

|

SU1432531A1 |

| Устройство для отладки микроЭВМ | 1988 |

|

SU1541615A1 |

| Устройство для отладки программно-аппаратных блоков | 1985 |

|

SU1315984A1 |

| Устройство для отладки программно-аппаратных блоков | 1984 |

|

SU1290329A1 |

| Устройство для отладки программ | 1985 |

|

SU1297064A1 |

| Устройство для отладки программно-аппаратных блоков | 1986 |

|

SU1363219A1 |

| Устройство для отладки программно-аппаратных блоков | 1985 |

|

SU1348839A1 |

Изобретение относится к вычислительной технике и может быть использовано для настройки, отладки и проверки работы специализированных микроЭВМ. Цель изобретения - расширение функциональных возможностей за счет обеспечения контроля внутренних узлов микропроцессора отлаживаемой микроЭВМ. Это позволяет сократить время отладки программы, а также повысить оперативность настройки микроЭВМ. Устройство содержит коммутатор, блок прямого доступа к памяти, магистральный усилитель, блок индикации, дешифратор, блок режимов останова, блок готовности, элемент И, элемент ИЛИ, схему сравнения, блок формирования адреса, блок постоянной памяти, блок регистров, блок задания адреса. 1 з.п. ф-лы, 2 ил.

| ВСЕСОЮЗНАЯ IПАТЕНТН9-ТЕХ^;Н^^^^КДЯ' | 0 |

|

SU308581A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Авторское свидетельство СССР № , кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1990-03-30—Публикация

1987-11-02—Подача