1ффек.тпную отладку программ однокон- турных м пвухконгурных СЦВМ и имеет ши- р ;. 1о функциональные возможности: зопись трассы отл живаемсй программы с kO4rtjo,iew команд, адресов, данных и типа цикла, выполнение программы с переменным шагом, диалоговый режим обмена информацией между универсальной ЭВМ и СЦВМ, возможность имитации прерываний, различные возможности пуска и останова программы с любого места, блокировка и слежение за программированными и непрограммированными прерываниями. 4 з.п. ф-лы,5 ил., 1 табл.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для отладки программно-аппаратных блоков | 1984 |

|

SU1290329A1 |

| Устройство для отладки микроЭВМ | 1985 |

|

SU1247877A1 |

| Устройство для отладки программ | 1982 |

|

SU1062708A1 |

| Устройство для отладки программно-аппаратных блоков | 1983 |

|

SU1242965A1 |

| Устройство для отладки программно-аппаратных блоков | 1985 |

|

SU1315984A1 |

| Устройство для отладки микроЭВМ | 1987 |

|

SU1553981A1 |

| Устройство для отладки микроЭВМ | 1985 |

|

SU1410708A1 |

| Устройство для отладки микропроцессорных систем | 1986 |

|

SU1462326A1 |

| Устройство для модификации адреса зон памяти при отладке программ | 1987 |

|

SU1465887A1 |

| Устройство для отладки программно-аппаратных блоков | 1984 |

|

SU1282139A1 |

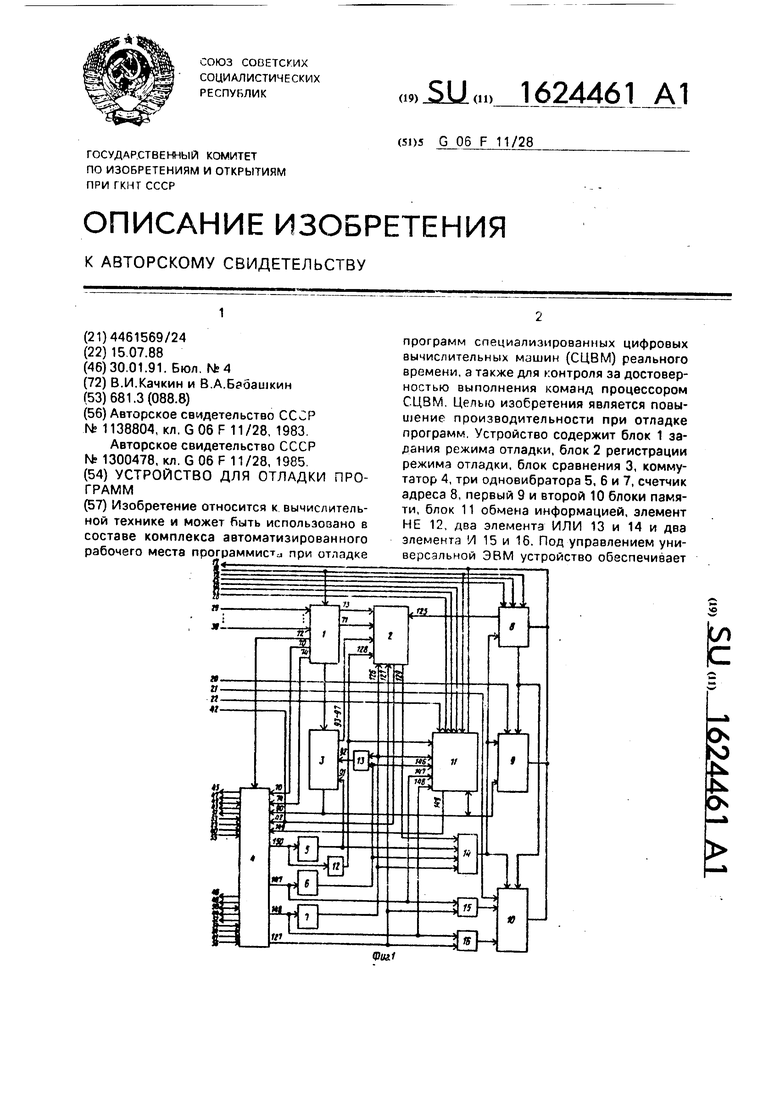

Изобретение относится к вычислительной технике и может быть использовано в составе комплекса автоматизированного рабочего места программист при отладке программ специализированных цифровых вычислительных машин (СЦВМ) реального времени, а также для контроля за достоверностью выполнения команд процессором СЦВМ. Целью изобретения является повышение производительности при отладке программ. Устройство содержит блок 1 за- лания режима отладки, блок 2 регистрации режима отладки, блок сравнения 3, коммутатор 4, три одновибратора 5, 6 и 7, счетчик адреса 8, первый 9 и второй 10 блоки памяти, блок 11 обмена информацией, элемент НЕ 12, два элемента ИЛИ 13 и 14 и два элемента / 15 и 16. Под управлением универсальной ЭВМ устройство обеспечивает

Изобретение относится к вычислительной технике и может быть использовано в составе комплекса автоматизированного рзЬочего места программиста при отладке прогргмм специализированных цифровых вычислительных машин (СЦВМ) реального времени, а также для контроля за достоверностью выполнения команд профессором СЦВМ.

Цель изобретения -- повышение производительности при отладке программ.

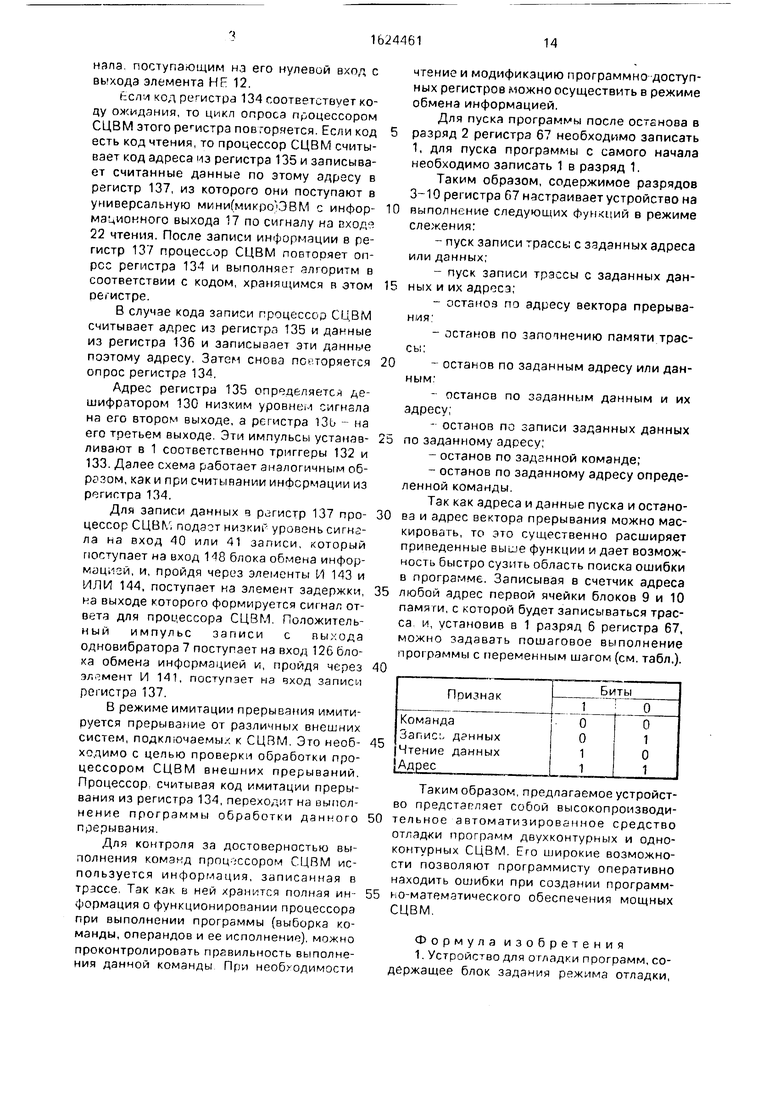

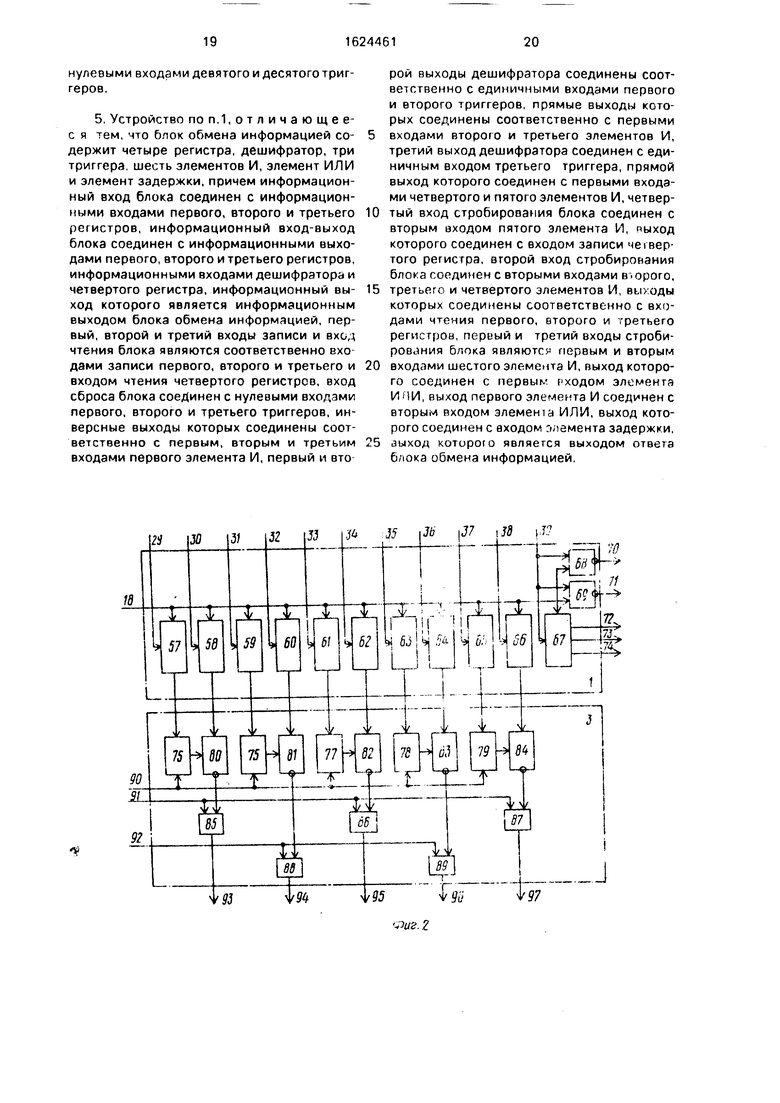

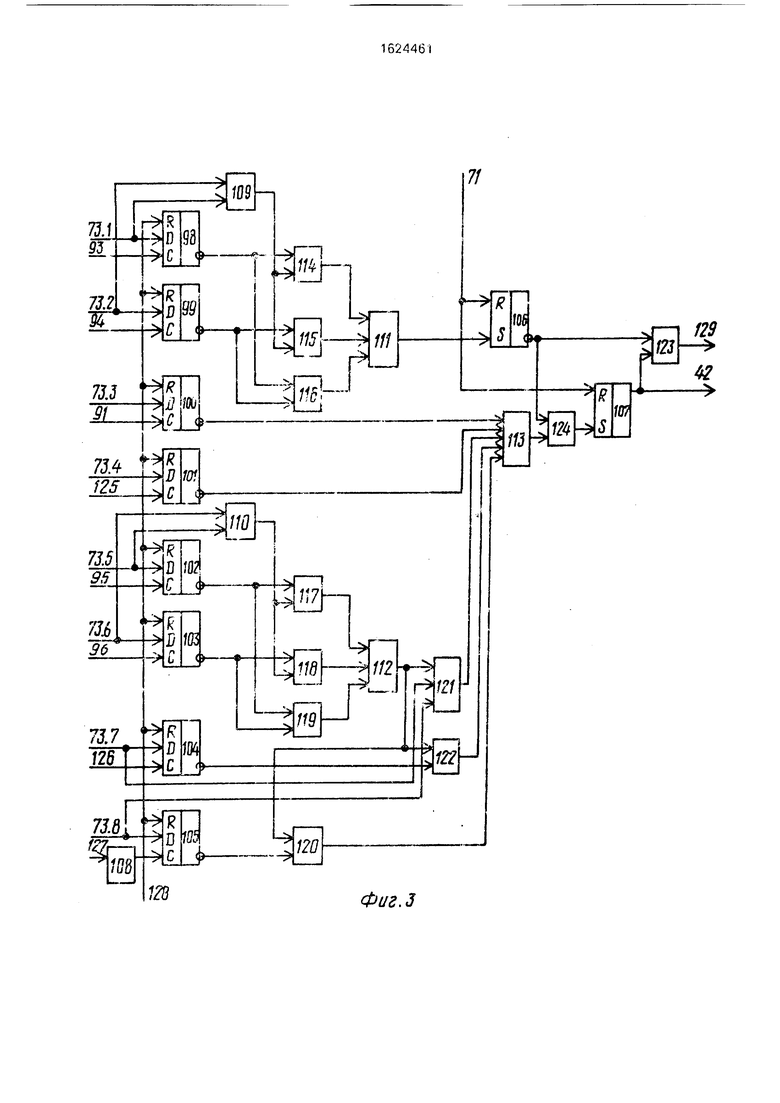

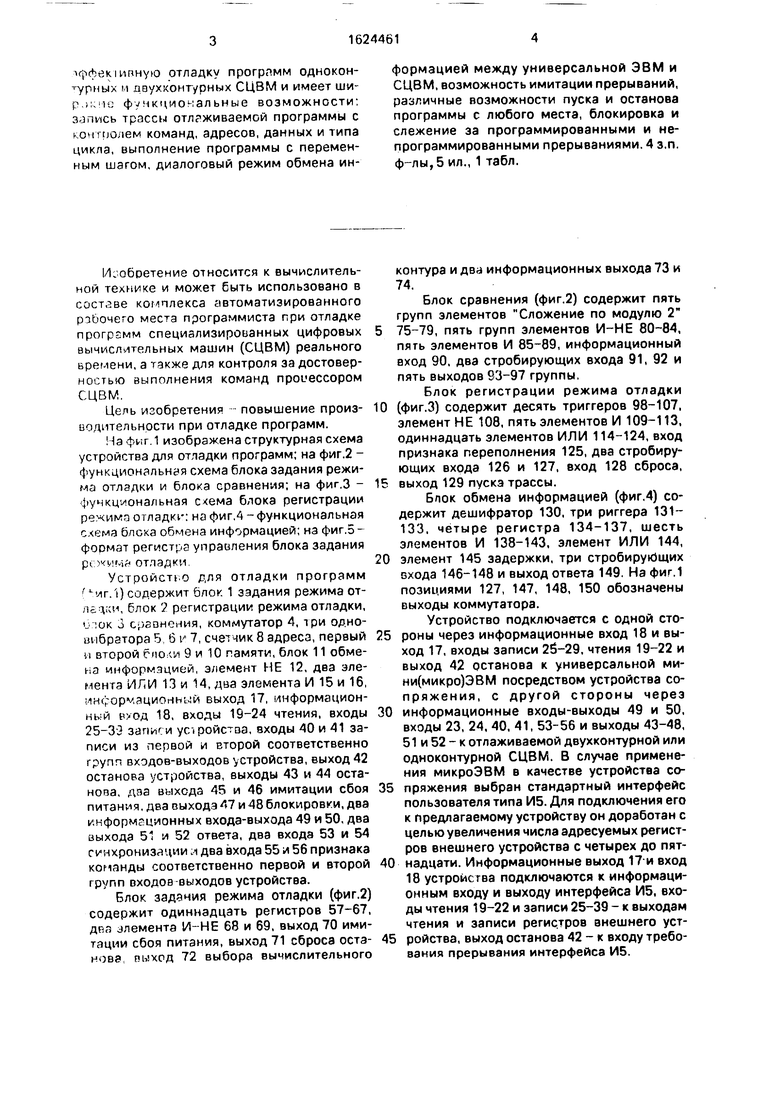

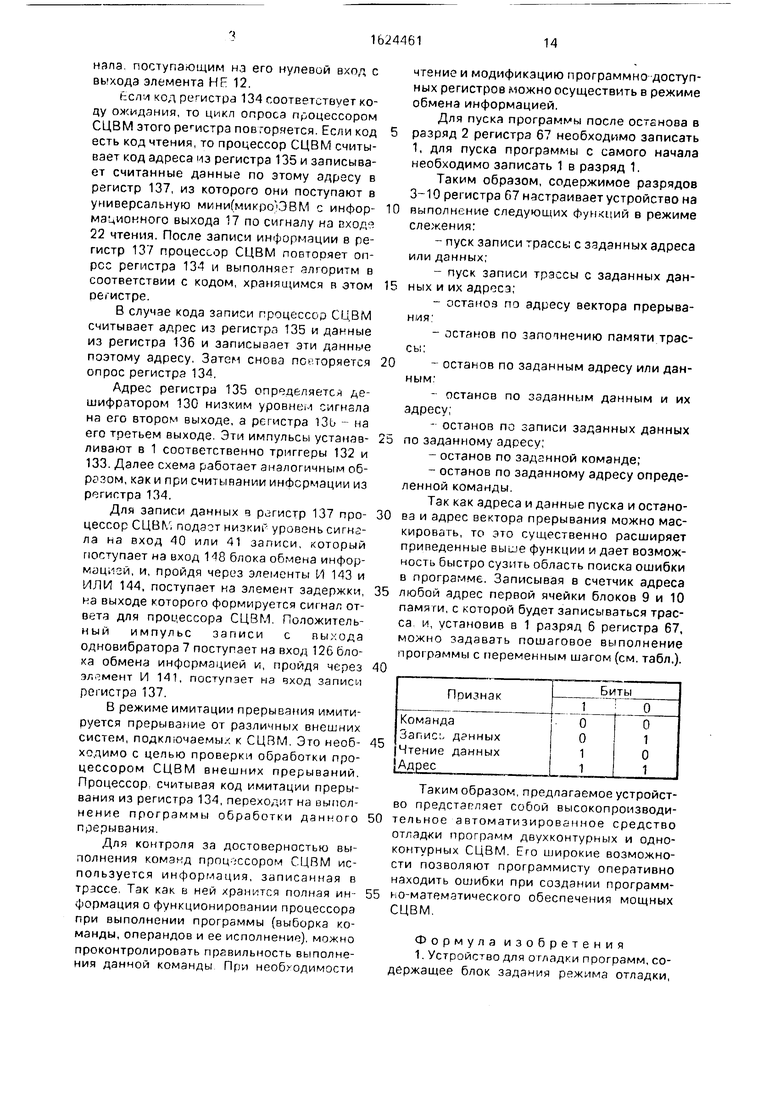

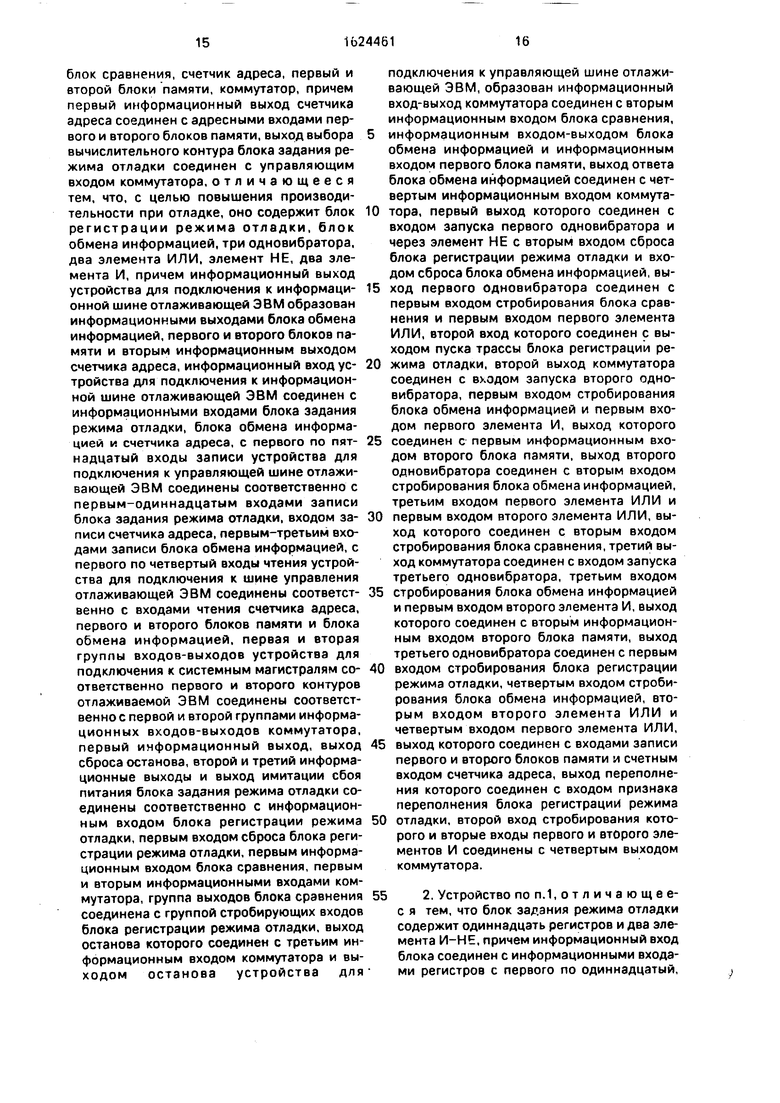

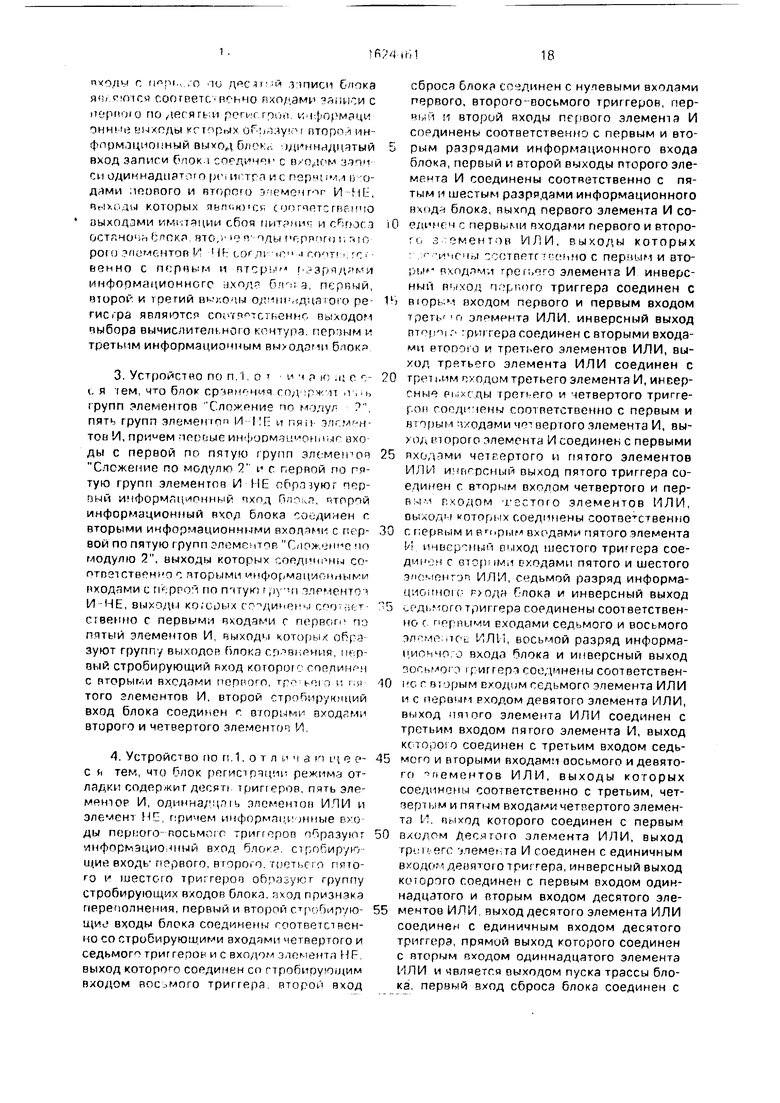

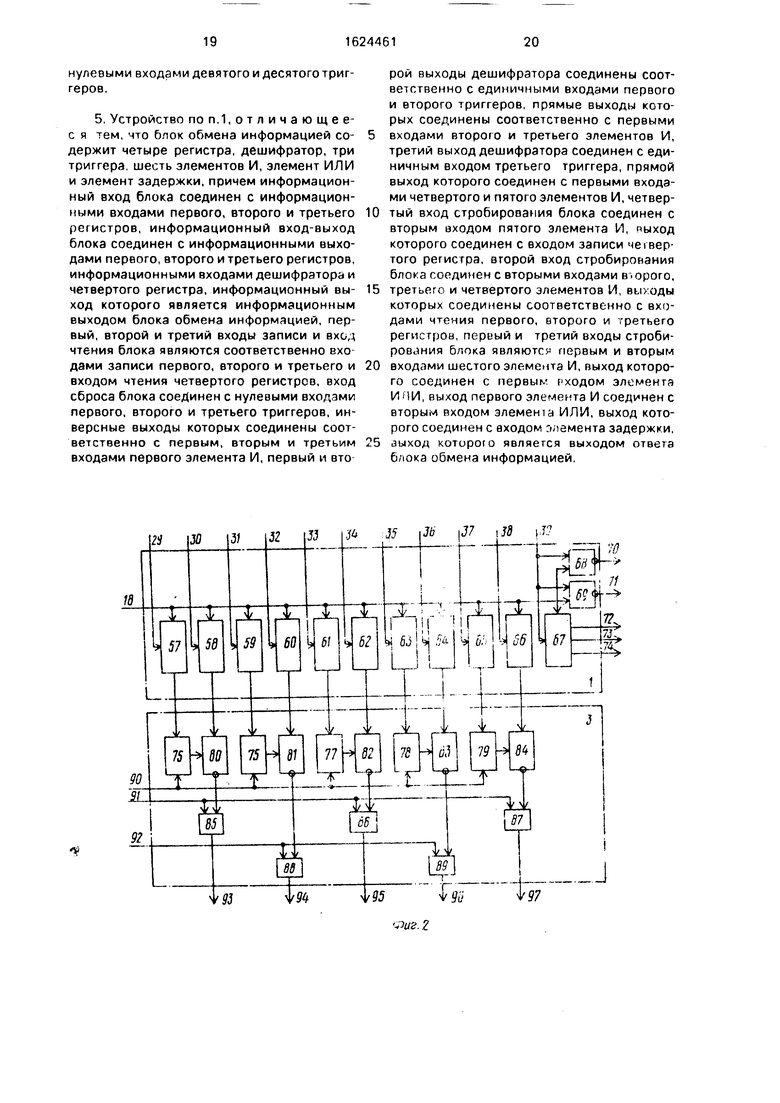

На фиг. 1 изображена структурная схема устройства для отладки программ; на фиг.2 - Функциональная схема блока задания режима отладки и блока сравнения; на фиг.З - Функциональная схема блока регистрации рехима отладки: на фиг.4 - функциональная схема блока обмена информацией; на фиг.5- фоомат регистра управления блока задания pi жи -if отладки

Устройство для отладки программ иг. 1) содержит блок 1 задания режима от- ла };си, блок регистрации режима отладки, и :ок 3 сравнения, коммутатор 4, три одно- вибратора Б б v 7, счетчик 8 адреса, первый и второй г по чИ 9 и 10 памяти, блок 11 обмена информацией, элемент НЕ 12, два элемента ИЛИ 13 и 14, два элемента И 15 и 16, информационней выход 17, информационный 18, входы 19-24 чтения, входы 25-33 записи устройства, входы 40 и 41 записи из первой и второй соответственно групп входов-выходов стройства, выход 42 останова устройства, выходы 43 и 44 останова, дэа выхода 45 и 46 имитации сбоя питания, два выхода47 и48блокировки, два информационных входа-выхода 49 и 50, два выхода 51 и 52 ответа, два входа 53 и 54 синхронизации л два входа 55 и 56 признака команды соответственно первой и второй групп входов-выходов устройства.

Блок задания режима отладки (фиг.2) содержит одиннадцать регистров 57-67, два элемента И-НЕ 68 и 69, выход 70 имитации сбоя питания, выход 71 сброса останова пыход 72 выбора вычислительного

контура и двл информационных выхода 73 и 74.

Блок сравнения (фиг.2) содержит пять групп элементов Сложение по модулю 2

75-79, пять групп элементов И-НЕ 80-84, пять элементов И 85-89, информационный вход 90, два стробирующих входа 91, 92 и пять выходов 93-97 группы,

Блок регистрации режима отладки

(фиг.З) содержит десять триггеров 98-107. элемент НЕ 108, пять элементов И 109-113, одиннадцать элементов ИЛИ 114-124, вход признака переполнения 125, два стробирующих входа 126 и 127, вход 128 сброса,

выход 129 пускэ трассы.

Бпок обмена информацией (фиг,4) содержит дешифратор 130. три риггера 131- 133, четыре регистра 134-137, шесть элементов И 138-143, элемент ИЛИ 144,

элемент 145 задержки, три стробирук)щих входа 146-148 и выход ответа 149. На фиг,1 позициями 127, 147, 148, 150 обозначены выходы коммутатора.

Устройство подключается с одной стороны через информационные вход 18 и выход 17, входы записи 25-29, чтения 19-22 и выход 42 останова к универсальной ми- ни(микро)ЭВМ посредством устройства сопряжения, с другой стороны через

информационные входы-выходы 49 и 50, входы 23, 24, 40, 41, 53-56 и выходы 43-48, 51 и 52 - к отлаживаемой двухконтурной или одноконтурной СЦВМ. В случае применения микроЭВМ в качестве устройства сопряжения выбран стандартный интерфейс пользователя типа И5. Для подключения его к предлагаемому устройству он доработан с целью увеличения числа адресуемых регистров внешнего устройства с четырех до пятнадцати. Информационные выход 17 и вход 18 устройства подключаются к информационным входу и выходу интерфейса И5, входы чтения 19-22 и записи 25-39 - к выходам чтения и записи регистров внешнего устройства, выход останова 42 - к входу требования прерывания интерфейса И5.

Первая группа входов и выходов 45, 47, 49, 43, 51, 53, 23, 40 и 55 коммутатора 4 идентичны по функциональному назначению соответственно его второй группе входов и выходов 46, 48, 50, 44, 52, 54, 24, 41 и 56 и в случае двухконтурной СЦВМ первая группа подключается к одному контуру, вторая - к другому. Интерфейсы контуров выполнены по ОСТ 11.305.903-80. При этом выходы 45 и 46 подключаются к шинам сбоя источника питания первого и второго интерфейсов вычислительных контуров, группы выходов 47 и 48 - к входам сигналов блокировки, информационные входы-выходы 49 и 50 - к шинам адреса/данных, выходы 43 и

44,51 и 52 - соответственно к шинам останова и ответа, входы 53 и 54, 23 и 24, 40 и 41, 55 и 56 - соответственно к шинам синхронизации адреса, чтения данных, записи данных и признака команды.

Коммутатор предназначен для подключения его входов и выходов первой группы

45,47, 49, 43, 51. 53, 23, 40 и 55 или его входов и выходов второй группы 46, 48, 50, 44, 52, 54, 24, 41 и 56 соответственно к его входам и выходам 70, 74, 90; 42, 149, 150, 147, 148 и 127.

Блок 1 задания режима отладки содержит данные об ассоциативных признаках, по которым блок 3 сравнения отслеживает информацию на информационном входе 90. Результаты сравнения поступают с выходов 93-97 в блок регистрации режима отладки.

Блок 2 регистрации режима отладки формирует сигналы пуска 129 и останова 42 в зависимости от результатов сравнения и признаков этих результатов, поступающих с информационного выхода 73 блока задания режима отладки.

Счетчик 8 адреса предназначен для оп ределения адреса ячейки блоков 9 и 10 памяти.

Блок 9 памяти содержит последовательно адреса и данные, имеющие место в процессе выполнения программы.

Блок 10 памяти содержит признаки информации, содержащейся в блоке 9 памяти, а именно признак адреса, признак чтения данных, признак записи данных и признак команды.

Блок 11 обмена информацией предназначен для организации обмена информацией между универсальной мини- (микро)ЭВМ и отлаживаемой СЦВМ.

Устройство работает в четырех режимах: записи информации, слежения за ходом выполнения программы и записи трассы, чтения записанной трассы, обмена информацией между универсальной мини (микро)ЭВМ и СЦВМ.

В режиме записи информация с канала микроЭВМ через интерфейс И5 поступает

0 на информационный вход 18. Интерфейс И5 определяет адрес регистра внешнего устройства и подает сигнал разрешения записи на соответствующий вход записи 29-39 для записи информации с информационного

5 входа 18 в один из регистров 57-67 блока задания режима отладки, на вход записи 26, 27 или 28 для записи в один из регистров 134-136 блока 11 обмена информацией или на вход 25 записи для записи информации в счетчик 8 адреса.

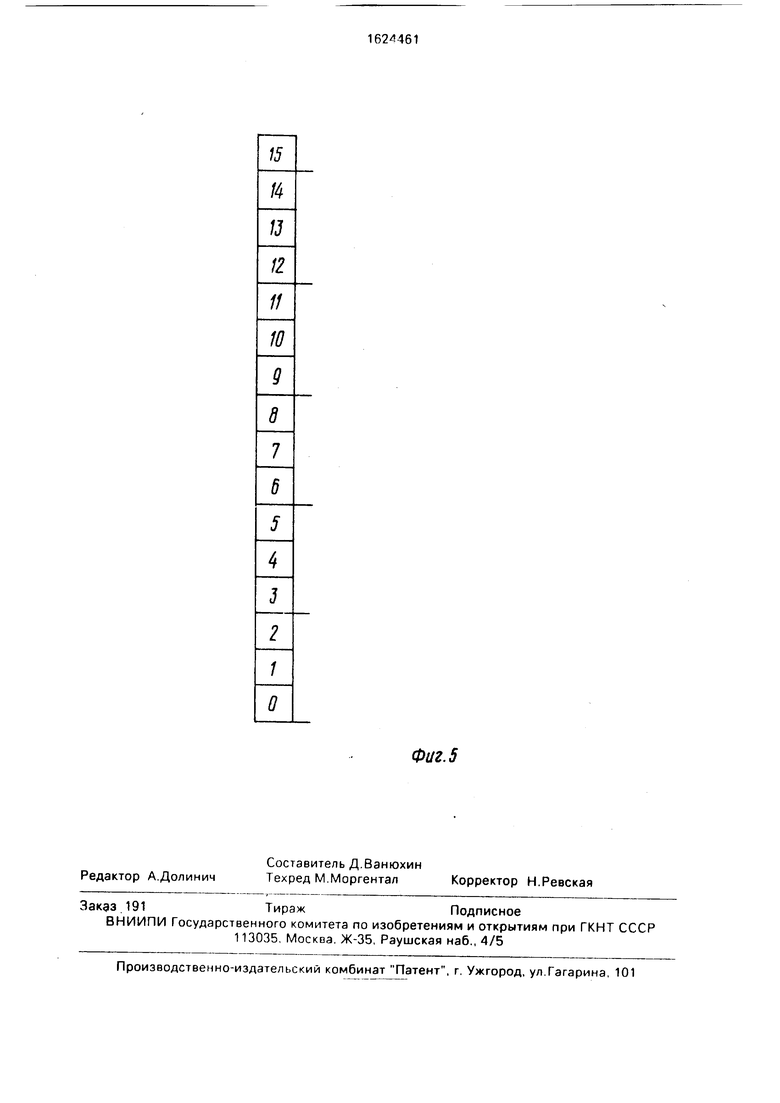

Регистры 57-67 блока задания режима отладки имеют следующее назначение: регистр 57 адреса пуска, регистр 58 маски адреса пуска, регистр 59 данных пуска, ре5 гистр 60 маски данных пуска, регистр 61 адреса останова, регистр 62 маски адреса останова, регистр 63 данных останова, регистр 64 маски данных останова, регистр 65 адреса вектора прерывания, регистр 66 ма0 ски адреса вектора прерывания, регистр 67 управления.

Регистр 67 управления содержит информацию (фиг.5), необходимую для управления работой устройства в режиме

5 слежения. В этом режиме устройство выполняет следующие функции: выбор вычислительного контура СЦВМ, пуск отлаживаемой прс.рзммы, запись трассы с определенного места программы, останов

0 процесса рыполнения отлаживаемой программы по заданному событию, блокировка программированных и непрограммированных прерываний.

Разряд 0 регистра 67 управления со5 держит информацию о выборе вычислительного контура двухконтурной СЦВМ. Сигнал с информационного выхода разряда 0 через выход 72 блока задания режима отладки поступает на управляющий вход коммутато0 ра 4. При этом коммутатор переключает первую группу входов и выходов 45, 47, 49, 43, 51, 53, 23, 40 и 55 или вторую группу входов и выходов 46, 48, 50, 44, 52, 54, 24, 41 и 56 соответственно на выходы и входы 70, 74,

5 90, 42, 149, 150, 147, 148 и 127 коммутатора. Разряды 1 и 2 отведены для формирования сигналов имитации сбоя питания и сброса останова. Это происходит следующим образом. При записи 1 в первый разряд 0 регистра управления на вход записи 39 подается высокий уровень сигнала записи, который поступает на первый вход элемента И-НЕ 68. Уровень лог. 1 формируется на шине первого разряда информационного 5 входа 18, который поступает на второй вход элемента И-НЕ 68. Так как продолжительность сигналов на входах элемента И-НЕ 68

ограничена ц 1клом записи в канале микро- ЭВМ, о в результате на выходе 70 формируется кратковременный нулевой уровень сигнала. Этот сигнал поступает с выхода 45 или 46 на шину сбоя источника питания. Процессор вычислительного контура, г случая этот сигнал, переходит на выполнение микропрограммы обслуживания сбоя писания. Длительность сигнала достаточна для того, чтобы процессор начал выполнение программы с начала. Таким образом, выполнится функция пуска программы. Аналогично формируется сигнал сброса останова на выходе элемента И-НЕ 69, который с выхода 71 б юка задания режима отладки поступает ия нулевой вход триггера 107 блока оегистрации режима отладки, образовывая сигнал останова на выходе 42.

Разряды 3 и 4 регистра 67 содержат признаки пуг.-а записи трассы программы в 9м 10 памяти с определенного места отлаживаемой поограммы. При установке Разряд 3 в 1 трасса начнет записываться г, адреса, определяемого содержимым реги- огрз 57 и регистре 58 блока задания режима отладки. При установке разрлда 4 в 1 грасса -«а нет записываться с момента поступления на информационный вход 90 коммутатора 4 данных, определяемых содержимым регистре 59 и 60, а при установке обоих разрядов 3 и 4 в 1 - с момента поступления канального цикла обмана с адресом и данными определенными в соответС|вующих Регистрах 57-60. Это происходит следующим образом Информация с регистра 57 поступает пеовый вход группы эпемен- тов Сложение по модулю 2 75. На другой вход этой группы непрерывно в ходе выполнения отлаживаемой программы поступают коды адррсов и дачных с информационного входа 90 Результаты поразрядного сравнения по модулю 2 поступают с выхода группы элементов 75 на вход группы элементов И-НЕ 80 с OT-|jMT.-iM коллектором. Эта группа элементов выполняет логическую конъюнкцию над каждым результатом поразрядного сравнения и содержимым соответствующего рчзряда регистра 53 и конъюнкцию над инвертированными результатами предыдущей опорации по всем разрядам. Таким об- ррзом при отрицательном результате сравнения хотя бы по одному разряду посту- па огей информации с информационного входа SO с содержимым соответствующего разряде регистра 57, на который не установлена маска п соответствующем разряде регистра 58 (разряд установлен в 1), на выходе группы элементов И-НЕ 80 с открытым коллзктором будет низк ий уровень сиг нала. При положительном результате сравнения

высокий уровень сигнала синхронизируется на элементе И 85 положительным импульсом признака адреса со стробирующего входа 91. Этот импульс формируется одновибратором 5 при поступлении на его вход отрицательного фронта синхросигнала адреса с выхода 150 коммутатора 4. Импульс признака адреса пуска с выхода 93 блока задания режима отладки поступает на син0 хровход триггера 93 блока регистрации режима отладки. На информационный вход этого триггера поступает уровень сигнала с выхода 73, соответствующий состоянию разряда 3 регистра 67 управления. По поло5 жительному фронту сигнала на выходе 93 блока сравнения записывается информация с выхода 73 блока задания режима отладки в триггер 98. Аналогично формируется высокий уровень сигнала на выходе группы эле0 ментов И-НЕ 81, синхронизирующейся на элементе И 88 положительным импульсом признака данных со стробирующего входа 92, который формируется одновибраторами 6 или 7 по отрицательному фронту соответ5 ственно сигналов синхронизации чтения и записи данных, поступающих с выходов 147 и 148 коммутатора 4. Импульс с выхода 94 блока сравнения устанавливает триггер 99 блока регистрации режима отладки в состо0 яние, определяемое состоянием разряда 4 регистра 67.

Группа элементов И 109, 111, ИЛИ 114- 116 выполняет логическую функцию по формированию сигнала пуска в зависимости от

5 состояния входов и выходов триггеров 98 и 99. При установке в 1 разрядов 3 и 4 регистра 67 на выходе элемента И 109 будет высокий уровень сигнала, который блокирует прохождение низкого уровня сигнала с

0 инверсных выходов триггеров 98 и 99 через элементы ИЛИ 114 и 115 на входы элемента И 111. Только при одновременной установке в 1 триггеров 98 и 99 в одном цилкле обмена на интерфейсе СЦВМ низкий уро5 вень сигналов с их инверсных выходов поступает на входы элемента ИЛИ 116, что приведет к появлению на его выходе низкого уровня, который, проходя через элемент И 111, поступит на единичный вход триггера

0 106 и установит его в 1. После окончания цикла обмена информацией на шине адреса данных очного из вычислительных контуров, который определяется низким уровнем сигнала синхронизации адреса на выходе

5 150 коммутатора 4, триггеры 98 и 99 сбрасываются низким уровнем сигнала, поступающего на вход сброса 128 блока регистрации режима отладки с выхода элемента НЕ 12. Низкий уровень с инверсного выхода триг- iepa 106 поступает на выход пуска 129 через

элемент ИЛИ 123, так как на его втором входе присутствует низкий уровень, посту пающий с прямого выхода триггера 107 Сигнал с выхода 129 поступает на вход элемента ИЛИ 14, открывает его и в результате положительные импульсы с его выхода поступают на входы записи блоков 9 и 10 па мяти и счетный вход счетчика 8 адреса

Если установлен в 1 только третий или только четвертый разряд регистра 67, на выходе элемента И 109 будет нгзкий уро вень сигнала и при положительном резуль тате сравнения в блоке сравнения установится соответствующий триггер 98 и 99 Сигнал с инвертирующею выхода одно го триггеров, пройдя через один из элементов ИЛИ 114, 115 и элемент И 111 установит трипер 106 в единичное состоя ние и на выходе 129 появится низкий уровень

В блок 9 памяти записываются последо вательно адреса и данные, имеющие место на одном из информационных входов выхо дов 49 ил.и 50 Коды адресов и дянгых поступают с информационного 90 коммутатора 4 на информационный вход блока 9 памяти Наличие кода адоеса на информационном входе вылоде 19 или О синхронизируется отррц гг iч

сигнала на входах синлроншг.ции соответственно Наличие к од л д ,- - 1 хронизируется отрица ге/п ныг Ф; и. о,и сигнала на входе 23 или 24 ITPHII , ь нальном цикле чтения или на i U i- и 41 записи при канальном цик л чзпис i i и синхросигналы адреса чтения и ч,ти ид ных поступают соотретственно ни вхо,ч д новибраторов 5 6 и 7, на пыхол л- формируется положитепьны ч игп отрицательному фронту ВУД io c игн

ИмПулЬСЫ С ВЫХОДОП ЭТИХ O,j,nfH4| i , i

поступают на входы элемент н ИПИ 14 с выхода которого поступают на вльф| 1 си блоков 9 и 10 памяти, и на счетньи ixo счетчика адреса, наращивая сг / cr net сч- мое на 1 по заднему фронту cv ы/п Гчким образом, определяется дрес очррс мной яиейки блоков 9,10 памяти для зчпиг и ,i дую,ней информации

Каждая я (ейка бтокч 10 памяш v - емкость 2 бита Кодировка информант v держащейся в зтом блоке па / ч и и . т ся таблицей В бит 0 ин } ормдцич чач и и с выхода элеменгз 11 15 в бит I с и ixu i элемента И 16

Код комчнды нэ информаиипнк JM нхг де-выходе 49 или 50 сопрсмождлртг - при знаком команды на входах 5cj гли Г Ь соответстврнно Низкий уровеш пгнт i признака команд i г ыходс. КОММ,ТР пгн 1

через элементы И 15 и 16 поступает на первый и второй информационные входы блока 10 памяти, и в текущий адрес ячейки этого блока памяти будет записан код признака

5 команды 00(2) В случае кода адреса на выходах 147 148 и 127 коммутатора 4 присутствует высокий уровень сигнала, и в блок 10 памчти с выходов элементов И 15 и 16 записывается код признака адреса 11(2) по им10 пульсу записи с выхода элемента ИЛИ 14, который поступил на его вход с выхода од- новибратора 5 При чтении или записи данных низкий уровень присутствует на входах 147 или 148 соответственно и в блок 10

15 памяти записывается код 10(2) или 01(2).

Информация в разрядах 5 10 регистра 67 определяет условия выдачи сигнала останова блоком регистрации режима отладки Уровень сигналов на информационных вхо0 дах триггеров 100 105 соответствует состоянию разрядов 5 10 регистра 67 При поступлении на С входы триггеров 100-105 высокого уровня соответственно сигналов признака адреса вектора прерывания, приlj знака nepei юлнения счетчика 8 адреса, признака адреса останова, признака данных огт.жова признака записи данных и при- eooi Слчструющие триггеры

г 1 i Т г 31- } Г ( ТОЯН 1 Г.П , i f -ля ifl их i14 i1 ( П Ж i -

nil ц ч t обм i ) на i , и г са ,( MIV ши , 8 J5 ыктюи ir- M,in )f . po a i n it н 12 и процег.1

и 9 I l Г)Ч 1| П т i Чн 1Г 1

IH j/u v if ipri t т еа ия r . о,;н r , ь i мобрэ ом Код л/,ро

k. 1 I 10(1 J I ) M )CK3 , 1Н П СЯ , pf ГИСТ p1 ) и ( H p, -5 i,; 5 ppr иотрг упраг тенпя i положительном ре

J ii ( | Ч1-1 В iP1- С( -ЧН1 iU14 г Э

/гi nf F i Hhnr v вектора npeiinB ин i iMjrp/ дг }7 выгокии уровень nj 11 а г нт гтиобир идии вход

р геи i 00 уст т пилимая его в единичное cot т чипе С cut но го ьыходт этот о триг- repri - изкии уров -нь CHI на/а поступает на ихо/5 элем1 |тп И 113 г его выход - нл -од э/имснгн till 124 Гг in триггер 10f оыл

) уст ; оглр| те имел т i с о словие пуска ( i тртги н т вой уровень сигнала, npt t,,q u,ipt ЭП МРНТ ИЛИ 1 14 поступает t i едини i ипчол ри i ера 1J 7 устанавливая его i един. inoe состояние Высокий

5 урс ень гигнала с прямого вылода этого

тои(гег по vn-3t ня пыход 42 останова,

Уi итре- - вание на прерывание п

jh me ми- через интерфейс пользоi f ля ,1 H,J из выходов 43 или 44

ч id О I дЛЧ Ч I 1НОВЛ f ЫПОЛНС11И О1ЛЭЖИi

pn . ,ia входе 21 чтения - из блока 10 I мг iп ияги ее м||И нак на информационный вы i iv 7 со,зрч;имое счетчика адреса

и /врличииается на 1 для допуска к следую 1дси ячейке блоков 9 и 10 памяти Это про- - г it. л )лжается до тех пор пока содержимое л счетчика адреса не будет равно значению, ( при котором запись трассы была прекраще1 лin LH4ia/iQM останова

1 i Обмрн информацией междг унивср1г /иной мини(микро)ЭВМ и CUBM харак р

П|-З РГОЯ четырьмя режимами ожидания,

а , записи и имитэцли прерываний

vКаждому .ожиму соответствует опредегснныи код в регистре 134 Ьлока 11 обмена

иинформацией Регистр 135 содержит адрес

iii -чпрограммного доступного интерфейс или

i i г«, u г-, эг еячейки памяти, из которого или в который

1 П еслинеобходимо считать или записать информа1 .(,(. ir1 0 цию соответстг знно в режиме чтения или

i - v 41,or записи Записываемые данные содержатся

рлО f РИХПДЗ в регистре 136, а считанные данные - в f i и i i - погистре 137

i ц-iu jИнформация в регистры 134-136 запи, MS nr с.-чется с информационного входа 18 соот- ьисгпрнно по сигналам на входах 26-28 Р f 7таписи

тПри г о тупленписигнапа останова с вы , . i ifvij чт 41 i ./ и 44 останоаа ь процессор СЦВМ

1|4 он оидаег на информационный вход - выход

ii i1.19 ли ЗО адрес регистра 134 Этот адрес,

f,,u т-тая о информационного входа 90 блои -,11 оЬменз информацией на вход дешиф

in ( .tn i ч-iрчюра 130 определяется низким уровнем

г ц лм 1 сигi-тла на его первом выходе, который, по мг - r i 7ступяя нп единичный вход триггера 131, уг г1;,тананяипает его в 1. Низкий уровень сигнала

м т г , m инверсного выхода поступает на вход

ir темги а И 142, а с его выхода - на вход

i и И О п.чечта ИЛИ 114 Далее процессор СЦВМ

i n усмнавлигает сигнал синхронизации чтеiнин данных на входе 23 или 24 Этот сиг нал

п отусге на вход элемента И 143 с выхода

r i - 117, а с ею выхода поступает через элемент

i i 4Ъ ИЛИ 144 на вход элемента 145 задержки На

(чг ею выходе формируется задержанный n , i г- н лЛ синхронизации чтения данных, который

гсс упяет с выхода 149 блоса обмена ин

i и /и чфоомэциеи через коммутатор 4 на выход 51

i i, ,voi ч SO или 52 ответа Положительный импульс v1 нияданни РЫХОПЯ одновибратора бчэрез

i4 i . ti .K i пход 146 ока обмена информацией постуг г ( тг imei на tur цемента И 138, а с его выхода

Mf-мн so Mci ыход IT чия регистра 134. Инфопмация

i , - i 5 с г ыхода этого регистра поступает на ii - (j.r | мационный вход 90 коммутатора 4 и даi м i, oc i ня информационный вход-выход 49 или

. ,i i i ns.oi r ccop СЦВМ. По завершении цик t ч-, ь 4 па ohMena в интерфейсе СЦВМ триггер 131

ч 11 ч-i ч устанавливается в О низким уровнем сигнала поступающим на его нулевой вход с выхода элемента HF 12.

f-.сп л код регистра 134 соответствует коду ожидания, то цикл опроса процессором СЦВМ этого регистра повторяется. Если код есть код чтения, то процессор СЦВМ считывает код адреса из регистра 135 и записывает считанные данные по этому адресу в регистр 137, из которого они поступают в универсальную мини(микро ЭВМ с информационного выхода 17 по сигналу на сходч 22 чтения. После записи информации в регистр 137 процессор СЦВМ повторяет опрос регистра 134 и выполняет алгоритм в соответствии с кодом, хранящимся в этом регистре.

В случае кода записи процессор СЦВМ считывает адрес из регистра 135 и данные из регистра 136 и записывает эти данные поэтому адресу. Затем снова повторяется опрос регистра 134,

Адрес регистра 135 определяется дешифратором 130 низким уровнем сигнала на его втором выходе, а регистра 131 - на его третьем выходе. Эти импульсы устанавливают в 1 соответственно триггеры 132 и 133. Далее схема работает аналогичным образом, как и при считывании информации из регистра 134.

Для записи данных в регистр 137 процессор СЦВК , подаст низкиг уровень сигнала на вход 40 или 41 записи, который поступает на вход 148 блока обмена инфор- Мсщизй, и, пройдя через элементы И 143 и ИЛИ 144, поступает на элемент задержки, на выходе которого формируется сигнал ответа для процессора СЦВМ. Положительный импульс записи с выхода одновибратора 7 поступает на вход 126 блока обмена информацией и, пройдя через элемент И 141, поступает на вход записи регистра 137.

В режиме имитации прерывания имитируется прерывание от различных внешних систем, подключаемых к СЦВМ. Это необходимо с целью проверки обработки процессором СЦВМ внешних прерываний. Процессор считывая код имитации прерывания из регистра 134, переходит на выполнение программы обработки данного прерывания.

Для контроля за достоверностью выполнения команд процессором СЦПМ используется информация, записанная в трассе. Так как в ней хранится полная информация о функционировании процессора при выполнении программы (выборка команды, операндов и ее исполнение), можно проконтролировать правильность выполнения данной команды При необходимости

чтение и модификацию программно доступных регистров можно осуществить в режиме обмена информацией.

Для пуска программы после останова в 5 разряд 2 регистра 67 необходимо записать 1, для пуска программы с самого начала необходимо записать 1 в разряд 1.

Таким образом, содержимое разрядов 3-10 регистра 67 настраивает устройство на 0 выполнение следующих Функций в режиме слежения:

-пуск записи трассы с заданных адреса или данных;

-пуск записи трэссы с заданных дан- 5 ных и их адреса;

-останоз по адресу вектора прерывания

-останов по запопнению памяти трассы;

0 - останов по заданным адресу или данным1

-останов по заданным данным и их адресу;

-останов по записи заданных данных 5 по заданному адресу;

-останов по заданной команде;

-останов по заданному адресу определенной команды.

Так как адреса и данные пуска и остано- 0 ва и адрес вектора прерывания можно маскировать, то это существенно расширяет приведенные выие функции и дает возможность быстро сузить область поиска ошибки в программе. Записывая в счетчик адреса 5 любой адрес первой ячейки блоков 9 и 10 памя ги, с которой будет записываться трасса и, установив в 1 разряд 6 регистра 67, можно задавать пошаговое выполнение программы с переменным шагом (см. табл.). 0

Таким образом, предлагаемое устройство предстагляет собой высокопроизводительное автоматизированное средство отладки программ двухконтурных и одноконтурных СЦВМ. Его широкие возможности позволяют программисту оперативно находить ошибки при создании программно-математического обеспечения мощных СЦВМ.

Формула изобретения 1. Устройство для отладки программ, содержащее блок задания режима отладки,

блок сравнения, счетчик адреса, первый и второй блоки памяти, коммутатор, причем первый информационный выход счетчика адреса соединен с адресными входами первого и второго блоков памяти, выход выбора вычислительного контура блока задания режима отладки соединен с управляющим входом коммутатора, отличающееся тем, что, с целью повышения производительности при отладке, оно содержит блок регистрации режима отладки, блок обмена информацией, три одновибратора, два элемента ИЛИ, элемент НЕ, два элемента И, причем информационный выход устройства для подключения к информаци- онной шине отлаживающей ЭВМ образован информационными выходами блока обмена информацией, первого и второго блоков памяти и вторым информационным выходом счетчика адреса, информационный вход ус- тройства для подключения к информационной шине отлаживающей ЭВМ соединен с информационными входами блока задания режима отладки, блока обмена информацией и счетчика адреса, с первого по пят- надцатый входы записи устройства для подключения к управляющей шине отлаживающей ЭВМ соединены соответственно с первым-одиннадцатым входами записи блока задания режима отладки, входом за- писи счетчика адреса, первым-третьим входами записи блока обмена информацией, с первого по четвертый входы чтения устройства для подключения к шине управления отлаживающей ЭВМ соединены соответст- венно с входами чтения счетчика адреса, первого и второго блоков памяти и блока обмена информацией, первая и вторая группы входов-выходов устройства для подключения к системным магистралям со- ответственно первого и второго контуров отлаживаемой ЭВМ соединены соответственно с первой и второй группами информационных входов-выходов коммутатора, первый информационный выход, выход сброса останова, второй и третий информационные выходы и выход имитации сбоя питания блока задания режима отладки соединены соответственно с информационным входом блока регистрации режима отладки, первым входом сброса блока регистрации режима отладки, первым информационным входом блока сравнения, первым и вторым информационными входами коммутатора, группа выходов блока сравнения соединена с группой стробирующих входов блока регистрации режима отладки, выход останова которого соединен с третьим информационным входом коммутатора и выходом останова устройства дляподключения к управляющей шине отлаживающей ЭВМ, образован информационный вход-выход коммутатора соединен с вторым информационным входом блока сравнения, информационным входом-выходом блока обмена информацией и информационным входом первого блока памяти, выход ответа блока обмена информацией соединен с четвертым информационным входом коммутатора, первый выход которого соединен с входом запуска первого одновибратора и через элемент НЕ с вторым входом сброса блока регистрации режима отладки и входом сброса блока обмена информацией, выход первого одновибратора соединен с первым входом стробирования блока сравнения и первым входом первого элемента ИЛИ, второй вход которого соединен с выходом пуска трассы блока регистрации режима отладки, второй выход коммутатора соединен с входом запуска второго одно- вибратора, первым входом стробирования блока обмена информацией и первым входом первого элемента И, выход которого соединен с первым информационным входом второго блока памяти, выход второго одновибратора соединен с вторым входом стробирования блока обмена информацией, третьим входом первого элемента ИЛИ и первым входом второго элемента ИЛИ, выход которого соединен с вторым входом стробирования блока сравнения, третий выход коммутатора соединен с входом запуска третьего одновибратора, третьим входом стробирования блока обмена информацией и первым входом второго элемента И, выход которого соединен с вторым информационным входом второго блока памяти, выход третьего одновибратора соединен с первым входом стробирования блока регистрации режима отладки, четвертым входом стробирования блока обмена информацией, вторым входом второго элемента ИЛИ и четвертым входом первого элемента ИЛИ, выход которого соединен с входами записи первого и второго блоков памяти и счетным входом счетчика адреса, выход переполнения которого соединен с входом признака переполнения блока регистрации режима отладки, второй вход стробирования которого и вторые входы первого и второго элементов И соединены с четвертым выходом коммутатора.

пходи г, .о iiu ДРСЯГ Й з шиси Блока

flf i с1 ОТ С Я СООГРеТС. Rr h40 РХОДЭМИ С

перн ло по десять п ррп/ч roui и i {юрмаци онн its ЧЫХРДЫ кгторых оГьг иу i пторп i информационный выход . )диннндцатый вход записи TVIOK i спгдин н с в огк-м з-эом си одиннадцатого pn ш тг л и с перчим,1 ь о- длми леопого и второго эчрменрт И НЬ,

ЧНХчДЫ КОТОрЫХ ЯВП(,Ю О COnrqPTCTFif I MO

выходами иммяции сбоя и з

ОСТЯЧО )Г1 tnCKfl ВТО,), ОДЫ РГррмго I, ЧЮ РОЮ ЛОМСНТОВ Ь 1 HhtOrni .Г -I ГП 1Т i ГС

венно с первым и пгср1-1 r инфоомационнсгс нхпдр Огг i а, парный, торой и шегий вьч .о-ш одчт ,дцагот ре

ГИСГра ЯВЛЯЮТСР , В0 лОДОМ

выбора вычислитель ного контура первым и третьим информационным выходами блокр

ды с первой по пятую групп элементов Слежение по модулю Т и г нерпой по гя- тую групп элементов И НЕ обртуюг пер- онй информационный пход . второй информационный вход блока соединен г вторыми информационными входами с пор- вой по пятую i рупп элемс imp, чо модулю 2. выходы которых СОРДИМ, со- ПТПЭТСТВРН О г, аторыми информацигиными иход-тми с гк.ррлй по пчтую г,} -MI элемечто j И ЧЕ, выходи ко. срых с ДИИРНЧ г,о ..г т сгвенно с первыми входами г первой1 по пятый элементов И выходм которых оРрл зуют групп/ ВЫХОДОР Плокэ СГПВЬРНИЯ, IK- р- аый стробирующий вход которого ГОРЛИНР.Ч с вторыми входами neptioro, тр.- - ч г j., того элементов И, второй стробирующий вход блока соединен г вторыми входами второго и четвертого элементоп И

ды nepfjoro посьмшг триггороо образуют информационный блок стробирую щие входь первого, Bropoi о гиетьсю Г РТО- го и шестого три:геро з образуют группу стробирующих входогз блока, пход признчкэ переполнения, первый и второй cTpr 6npvio- входы блока соединены соответственно со стробируюшими входами четвертого и седьмог триггеров и с входом элемент, HF выход которого соединен со гтробиоуо.дим входом восьмого триггера второй вход

сброса блока соединен с нулевыми входами первого, второго-восьмого триггеров, пер- «i,i i i второй входы первого элемента И соединены соответственно с первым и вторым разрядами информационного входа блока, первый и второй выходы пторого элемента И соединены соответственно с пятым и шестым разрядами информационного вчодн блока, выход первого элемента И со- единс ч с первыми входами первого и второго j «ментов ИЛИ, выходы которых

ИЧСЧЫ 70ТВРТГ ff C FiHO С ПврЧЫМ И BTQры пчпдлми pei;,nro элемента И инверсный пчход парного триггера соединен с вюрым входом первого и первым входом треть о ЭЛРМРНТЭ ИЛИ. инверсный выход птпр ц с- -рщ гера соединен с вторыми входами ртоотю и третьего элементов ИЛИ, выход третьего элемента ИЛИ соединен с третьим третьего элемента И, инвер- гные Р1млг ды и четвертого трите- rof) горд1 чрны соотпетственно с первым и вторым ч/одзми чр-1 вергого элемента И, вы- ПА РТ орого элемента И соединен с первыми входами четгертого и пятого элементов ИЛИ импгрсный выход пятого триггера соединен с вторым входом четвертого и пер- RMM гходом гсстого элементов ИЛИ, оылодч которых соединены соответственно с г;ервым и вторым входами пятого элемента И ичЕ) выход шестого триггера сое- дим- н с стер )ми с-ходами пятого и шестого э 1оменгэп ИЛИ, седьмой разряд информационной Г-лока и инверсный выход седьмого триггера соединены соответственно г пррпыми входами седьмого и восьмого лог. ИЛИ, восьмой разряд информа- ииончо о входа блока и инверсный выход п,огьмо( э (риггерт соодмнены соответствен- i C г вюрым входим седьмого элемента ИЛИ и с первым РХОДОМ девятого элемента ИЛИ, выход итого элемента ИЛИ соединен с третьим входом пятого элемента И, выход кс торою соединен с третьим входом седьмого и вторыми входами оосьмого и девятого пемеитов ИЛИ, выходы которых соединены соответственно с третьим, чет- черт им и пятым входами четвертого элемента I пнход которого соединен с первым входом Десятого элемента ИЛИ, выход гр . п егс лемв та И соединен с единичным ВУОДО деолтоготриггера, инверсный выход которого соединен с первым входом одиннадцатого и вторым входом десятого элементов ИЛИ выход десятого элемента ИЛИ соединен с единичным входом десятого триггера, прямой выход которого соединен с вторым входом одиннадцатого элемента ИЛИ и чвляетгя выходом пуска трассы блока, первый вход сброса блока соединен с

нулевыми входами девятого и десятого триггеров.

рой выходы дешифратора соединены соответственно с единичными входами первого и второго триггеров, прямые выходы которых соединены соответственно с первыми

входами второго и третьего элементов И, третий выход дешифратора соединен с единичным входом третьего триггера, прямой выход которого соединен с первыми входами четвертого и пятого элементов И, четвер0 тый вход стробирования блока соединен с вторым входом пятого элемента И, пыход которого соединен с входом записи того регистра, вгорой вход стробирования блока соединен с вторыми входами в-.орого, третьего и четвертого элементов И, выходы которых соединены соответственно с входами чтения первого, второго и третьего регистров, первый и третий входы стробирования блока являются первым и вторым входами шестого элемента И, выход которого соединен с первым РХОДОМ элемента И ПИ, выход первого элемента И соединен с вторым входом элемента ИЛИ, выход которого соединен с входом о/чемента задержки, аыход которого является выходом ответа блока обмена информацией.

5

0

5

1

//41

HL

jvj1

A№-

7U Л

r

111

Фиг.З

Фиг. 5

| Устройство для отладки программ | 1983 |

|

SU1138804A1 |

| Авторское свидетельство СССР N 1300478, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1991-01-30—Публикация

1988-07-15—Подача