Изобретение относится к импульсной технике и предназначено для преобразования ТТЛ-уровней в КМОП-уровне логических сигналов.

Целью изобретения является уменьшение паразитных статических токов путем введения во входную цепь последовательно соединенных двунаправленного управляемого ключа и асинхронного )-триггера.

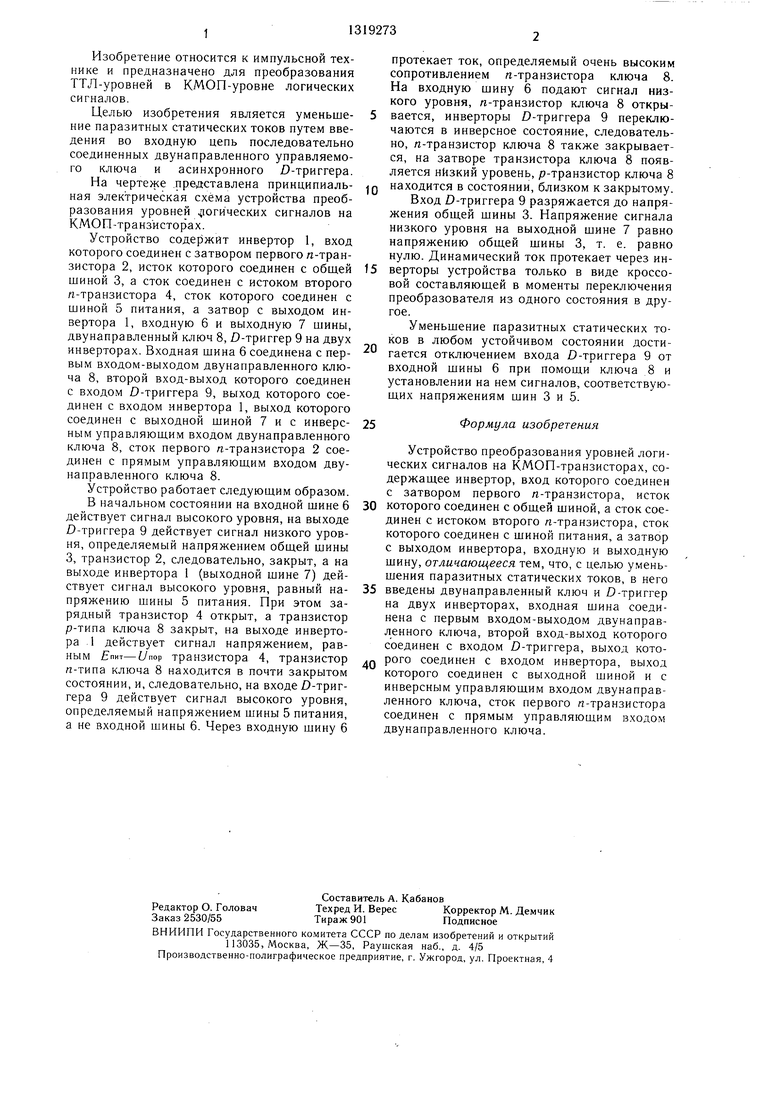

На чертеже .представлена принципиальная электрическая схема устройства преобразования уровней 41оги ческих сигналов на КМОП-транзисторах.

Устройство содержит инвертор 1, вход которого соединен с затвором первого л-тран- зистора 2, исток которого соединен с общей шиной 3, а сток соединен с истоком второго п-транзистора 4, сток которого соединен с шиной 5 питания, а затвор с выходом инвертора 1, входную 6 и выходную 7 шины, двунаправленный ключ 8, )-триггер 9 на двух инверторах. Входная шина 6 соединена с первым входом-выходом двунаправленного ключа 8, второй вход-выход которого соединен с входом D-триггера 9, выход которого соединен с входом инвертора 1, выход которого соединен с выходной шиной 7 и с инверсным управляющим входом двунаправленного ключа 8, сток первого «-транзистора 2 соединен с прямым управляюшим входом двунаправленного ключа 8.

Устройство работает следующим образом.

В начальном состоянии на входной шине 6 действует сигнал высокого уровня, на выходе D-триггера 9 действует сигнал низкого уровня, определяемый напряжением общей шины 3, транзистор 2, следовательно, закрыт, а на выходе инвертора 1 (выходной шине 7) действует сигнал высокого уровня, равный напряжению шины 5 питания. При этом зарядный транзистор 4 открыт, а транзистор р-типа ключа 8 закрыт, на выходе инвертора .1 действует сигнал напряжением, равным (Упор транзистора 4, транзистор п-типа ключа 8 находится в почти закрытом состоянии, и, следовательно, на входе D-триггера 9 действует сигнал высокого уровня, определяемый напряжением шины 5 питания, а не входной шины 6. Через входную шину 6

0

протекает ток, определяемый очень высоким сопротивлением «-транзистора ключа 8. На входную шину 6 подают сигнал низкого уровня, rt-транзистор ключа 8 открывается, инверторы D-триггера 9 переключаются в инверсное состояние, следовательно, rt-транзистор ключа 8 также закрывается, на затворе транзистора ключа 8 появляется низкий уровень, р-транзистор ключа 8

Q находится в состоянии, близком к закрытому. Вход D-триггера 9 разряжается до напряжения общей шины 3. Напряжение сигнала низкого уровня на выходной шине 7 равно напряжению общей шины 3, т. е. равно нулю. Динамический ток протекает через ин5 верторы устройства только в виде кроссовой составляющей в моменты переключения преобразователя из одного состояния в другое.

Уменьшение паразитных статических токов в любом устойчивом состоянии достигается отключением входа D-триггера 9 от входной шины 6 при помощи ключа 8 и установлении на нем сигналов, соответствующих напряжениям шин 3 и 5.

5Формула изобретения

Устройство преобразования уровней логических сигналов на КМОП-транзисторах, содержащее инвертор, вход которого соединен с затвором первого п-транзистора, исток

0 которого соединен с общей шиной, а сток соединен с истоком второго «-транзистора, сток которого соединен с шиной питания, а затвор с выходом инвертора, входную и выходную шину, отличающееся тем, что, с целью уменьшения паразитных статических токов, в него

5 введены двунаправленный ключ и D-триггер на двух инверторах, входная шина соединена с первым входом-выходо.м двунаправленного ключа, второй вход-выход которого соединен с входом D-триггера, выход котоQ рого соединен с входом инвертора, выход которого соединен с выходной шиной и с инверсным управляющим входом двунаправленного ключа, сток нервого «-транзистора соединен с прямым управляющим входом двунаправленного ключа.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство преобразования уровней логических сигналов на КМОП-транзисторах | 1989 |

|

SU1775853A1 |

| УСТРОЙСТВО ПРЕОБРАЗОВАНИЯ УРОВНЕЙ ЛОГИЧЕСКИХ СИГНАЛОВ НА КМОП-ТРАНЗИСТОРАХ | 1993 |

|

RU2085030C1 |

| D-триггер на КМДП-транзисторах | 1990 |

|

SU1728963A1 |

| Адресный регистр | 1979 |

|

SU832726A1 |

| ДИНАМИЧЕСКИЙ D-ТРИГГЕР | 2018 |

|

RU2679220C1 |

| СТАТИЧЕСКАЯ ЗАПОМИНАЮЩАЯ ЯЧЕЙКА С ДВУМЯ АДРЕСНЫМИ ВХОДАМИ | 2011 |

|

RU2470390C1 |

| АДРЕСНЫЙ ФОРМИРОВАТЕЛЬ | 1991 |

|

RU2010361C1 |

| Входной усилитель-формирователь с запоминанием информации | 1980 |

|

SU903970A1 |

| Логический элемент сравнения комплементарной металл-оксид-полупроводниковой структуры ассоциативного селектора запоминающего устройства | 2016 |

|

RU2621011C1 |

| @ - @ -Триггер на МДП-транзисторах | 1985 |

|

SU1262697A1 |

Изобретение относится к имнульсно технике и может быть использовано для преобразования ТТЛ-уровней в КМОП-уров- не логических сигналов. Цель изобретения - снижение паразитных статических токов. Устройство содержит инвертор 1, н-транзисторы 2, 4. Для достижения поставленной цели в устройство введены двунаправленный управляемый ключ 8, D-триггер 9. 1 ил. О У (Л оо ;о гч:) оо

| Мкртчян С | |||

| О | |||

| Преобразователи уровней логических элементов | |||

| Сер | |||

| Электроника, вын | |||

| Способ сопряжения брусьев в срубах | 1921 |

|

SU33A1 |

| М.: Радио и связь, 1982, с | |||

| Пишущая машина | 1922 |

|

SU37A1 |

| Видоизменение прибора с двумя приемами для рассматривания проекционные увеличенных и удаленных от зрителя стереограмм | 1919 |

|

SU28A1 |

| Патент США № 4258272 кл | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1987-06-23—Публикация

1986-01-07—Подача