I

Изобретение относится к запоминающим устройствам и может быть использовано при построении микромощных ин-. тегральных запоминающих устройств на КМДП-транзисторах в качестве элемента адресного или информационного буферного регистра, согласующегося с . ТТЛ-схемами.-,

Известны входные усилители-формирователи с запоминанием информации, содержащие два инвертора на КИДП-транзисторах и транзистор р-типа, причем к входу схемы подключен сток транзистора р-типа и входы.инверторов 1 .

Недостаток устройств - невысокое быстродействие и низкое входное сопротивление в динамическом режиме.

Наиболее близким техническим решением к предлагаемому является усилитель-формирователь с запоминанием информации на КМДП-транзисторах, согласующийся с ТТЛ-схемами, содержащий триггер на транзисторах р-типа и п-типа, истоки транзисторов р-типа под- (

ключены к шине источника питания, а истоки транзисторов п-типа - к стоку ключевого транзистора п-типа, исток которого соединен с шиной нулевого потенциала, два установочных транзис тора р-типа, истоки которых подключв ны к шине источника питания, а стоки соответственно к объединенным стокам транзисторов триггера, стоки первых транзисторов р-типа и п-тйпа триггеtoра соединены с затворами вторых транзисторов р-типа и п-типа, стоки ко-торых соединены с затворами первых транзисторов р-типа и п-типа тригге-, ра, затворы установочных транзисторов

15 и ключевого транзистора соединены с управляющей шиной; два инвертора на транзисторах р-типа и п-типа, причем истоки транзисторов п-типа инверторов соединены с шиной нулевого поЮтенциала, а стоки транзисторов р-типа инверторов - с шиной источника питания, затворы транзисторов п-типа и р-типа первого инвертора подключены (с

стокам первого транзистора р-типа триггера и первого транзистора обрат- ной связи, затвор которого подключен к стокам транзисторов первого инвертора и прямому выходу устройства, затворы транзисторов второго инвертора подключены к стоку второго транзистора р-типа триггера и стоку второго транзистора обратной связи р-типа, которого подключен к стокам транзисторов второго инвертора и инверсному выходу устройства, а исток соединен со стоком опорного транзистора р-типа, исток которого подключен к шине источника питания,а затвор к шине источника опорного напряжения, jicTOK первого транзистора обратной связи соединен со стоком информационного транзистора р-типа, исток которого подключен к тине источника питания, а затвор - ко входу устройства 21,

Недостаток этого устройства заключается D его сложности, так как оно содержит большое число элементов и нуждается в стабильном источнике опорного напряжения, который в интегральных схемах должен выполняться в виде отдельной схемы на том же кристалле .

Цель изобретения - упрощение усипителя-формирователя.

Поставленная цель достигается тем, Мто во входной усилитель-формирователь с запок 1нанием информации, содержа1ций КМДП-транзисторы р-типа и И-типа, причем истоки первого и второго нагрузочных транзисторов р-типэ соединены с питания, истоки первого и второго переключающих транзис;TopOBVt-тйпа подключены к стоку ключевого транзистора и-типа, нагрузочНые и переключающие Транзисторы соединены по триггерной схеме, исток ключевого транзистора подключен к 4иине нулевого потенциала, а затвор соединен с шиной управления и затвоЬами первого и второго установочных транзисторов р-типа, истою которых Подключены к шине питания, сток первого установочного транзистора соединен со стоком первого нагрузочного транзистора и является инверсным выходом, а сток второго установочного транзистора подключенк стоку второго нагрузочного транзистора и является прямым выходом устройства, управляющий транзистор и-типа и информационный транзистор и-типа,

Причем сток управляющего транзистора соединен со стоком первого установоч Иого транзистора, затвор - со стоком второго установочного транзистора,

а исток - со стоком информационного транзистора, исток которого подключен к стоку ключевого транзистора, а затвор является входом усилителя-формирователя.

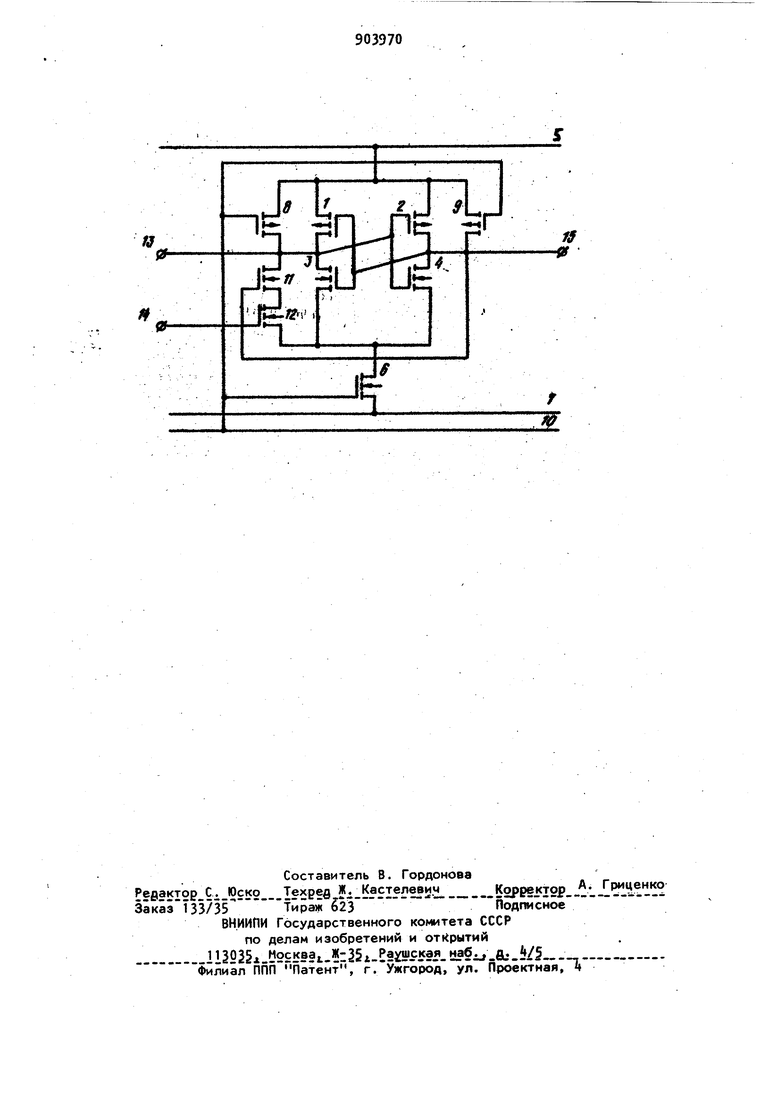

На чертеже изображена принципиальная схема предлагаемого устройства.

Усилитель-формирователь содержит первый 1 и второй 2 нагрузочные тран:3исторы р-типа, первый 3 и второй Ц переключающие транзисторы и-типа, шиНУ 5 питаний, ключевой транзистор 6 fi-типа, шину 7 нулевого потенциала, первый 8 и второй 9 установочные

транзисторы р-типа, шину 10 управле;ния, управлящий транзистор lih-тиVia и информационный транзистор 12 п-типа. На чертеже обозначены инверсный выход 13, информационный вход 14

и прямой выход 15 усилителя-формирователя. Ширина канала транзистора 4 выбрана большей, чем у транзистора 3 (сопротивление транзистора 4 меньше сопротивления транзистора 3) Размеры транзисторов 1, 2 и 8, 9 попарно одинаковые. Размеры транзисторов и 12 выбираются так, чтобы суммарное сопротивление транзисторов 3, 11 и .12 было меньше сопротивления транзистора i.

Усилитель-формирователь работает следующим образом.

В исходном состоянии (режим хранения) потенциал на шине 10 соответствует О, Транзистор 6 закрыт, а открытые транзисторы 8 и 9 на выходах 13 и 15 схемы устанавливают 1, При этом транзисторы 1 и 2 закрываются, а транзисторы 3 и открываются. Транзистор 11 Открыт. В зависимости от

логического уровня на входе l транзистор 12 может быть либо открыт, либо закрыт, причем в любом случае состояние транзистора 12 не влияет на состояние усилителя-формирователя,

в поскольку транзистор 6 закрыт. В режиме хранения на входе k должна быть установлена информация.

В режиме приема и запоминания входной информации (.режим обращения)

S на входе 4 устанавливается 1. Транзисторы 8 и 9 закрываются, а транзистор 6 открывается. Паразитные емкости в узлах схемы, связанных с выходами 13 и 15, начинают разряжаться чере открытые транзисторы 3, и 6. Если на входе 1 установлен О (транзистор 12 закрыт), ток разряда, проходящий через транзисторы + и 6, больше тока, проходящего через транзисторы 3 и 6.Транзисторы I-, соединенные по триггерной схеме, устанавливаются в состояние, когда на выходе 15 имеа на выходе 13 - 1 (транетсязисторы 1 и Ц открыты, транзисторы 2 и 3 закрыты). По цепи обратной связи транзистор 11 закрывается и усилитель формирователь сохраняет установившееся состояние при любых изменениях информации на входе 1. В случае подачи в исходном состоянии на вход Т 1 открывается транзистор 12 и суммарный ток разряда, проходящий через транзисторы 11, 12, 3 и 6, больше тока, проходящего через транзисторы и 6, и транзисторы I- триггера устанавливаются в состояние, при котором на выходе 15 устанавливается 1, а на выходе 13 - О тран13исторы 2 и 3 открыты, транзисторы V и А закрыты). В этом состоянии транзистор 11 остается открытым, но, поскольку на выходе 13 установлен О, изменение информации на входе Н не влияет на состояние усилителя-формирователя. Таким образом, усилитель-формирователь запоминает поданную на вход k информацию. При этом входная информация подается на вход 1 до перехода к режиму обращения и удерживается в этом режиме на время, определяемое быстродействием транзисторбв l-k триггера, после чего информация на входе Н может изменяться. Уровень срабатывания усилителяформирователя по входу Vk определяется пороговым напряжением транзистора 12 и составляет при существующем технологическом процессе 1-2 В, что обеспечивает стыковку усилителя-формирователя с ТТЛ-схемами. Технико-экономическое преимущестпредлагаемого усилителя-формирователя заключается в его упрощении по сравнению с известным. Формула изобретения Входной усилитель-формирователь с запоминанием информации, содержащий КМДП-транзисторы р-типа и п-типа, причем истоки первого и второго нагрузочных транзисторов р-типа соединены с шиной питания, истоки первого и второго переключающих транзисторов п-типа подключены к стоку ключевого транзистора п-типа, нагрузочные и переключающие транзисторы соединены по триггерной схеме, исток ключевого транзистора подключен к шине нулевого потенциала, а затвор соединен с шиной управления и затворами первого и второго установочных транзисторов р-типа, истоки которых подключены к шине питания, сток пер-, вого установочного транзистора соединен со стоком первого нагрузочного транзистора и является инверсным выходом, а сток второго установочного транзистора подключен к стоку второго нагрузочного транзистора и является прямым выходом устройства, о тличающийся тем, что, с целью упрощения усилителя-формирователя, он содержит управляющий транзистор п-типа и информационный транзис ОР п-типа, причем сток управлящегр транзистора соединен со стоком первого установочного транзистора, затвор - со стоком второго установочис го транзистора, а исток - со стоком информационного транзистора, исток которого подключен к стоку ключевого транзистора, а затвор является входом усилителя-формирователя. Источники информации, принятые во внимание при экс1эертизе 1.Патент Великобритании If , кл. Н 03 К 17/60, опублик. 19792.Electronics, 1978, т. 51,. 06-111 (прототип).

E

8

ii- r-i

IK тзГ

5 3U

| название | год | авторы | номер документа |

|---|---|---|---|

| Усилитель на кмдп-транзисторах | 1979 |

|

SU862236A1 |

| Усилитель-формирователь для оперативного запоминающего устройства на КМДП транзисторах | 1981 |

|

SU999104A1 |

| Усилитель для запоминающего устройства | 1981 |

|

SU999103A1 |

| Усилитель считывания на кмдп-транзисторах | 1978 |

|

SU771716A1 |

| Усилитель считывания на КМДП-транзисторах | 1986 |

|

SU1377910A1 |

| Усилитель считывания на КМДП транзисторах | 1986 |

|

SU1376117A1 |

| Триггер | 1989 |

|

SU1674262A1 |

| Усилитель считывания на КМДП транзисторах | 1984 |

|

SU1241285A1 |

| Усилитель считывания на КМДП-транзисторах | 1986 |

|

SU1345258A1 |

| Усилитель считывания на КМОП-транзисторах | 1983 |

|

SU1149310A1 |

Авторы

Даты

1982-02-07—Публикация

1980-06-27—Подача