1

Изобретение относится к полупроводниковой электронике, электронной и вычислительной технике и может использоваться при построении запоминающих устройств на КМОП-транзисторах.

Известен адресный регистр, содержащий входной ключ, тактируемый RSrf триггер, цепи восстановления исходного состояния и источник опорного напряжения

Недостатком данного устройства является сложность конструкции, свя занная с необходимостью использования генератора опорного напряжения.

Цель изобретения - упрощение конструкции и повышение надежности работы.

Поставленная цель достигается тем что в устройство, содержащее входной ключевой МОП-транзистор, триггер на КМОП-транзисторах, установочный МОП-транзистор, включенный между одним входом триггера и общей шиной.

введены инвертор и тактируемый элемент ИЛИ-НЕ на КМОП-транзисторах, причем вход инвертора подключен к ши .не сигналов выбора, а выход - к тактовому входу тактируемого элемента ИЛИ-НЕ, один вход которого подключен к прямому, второй - к инверсному выходу триггера, а выход - к затвору входного ключевого МОП-транзистора.

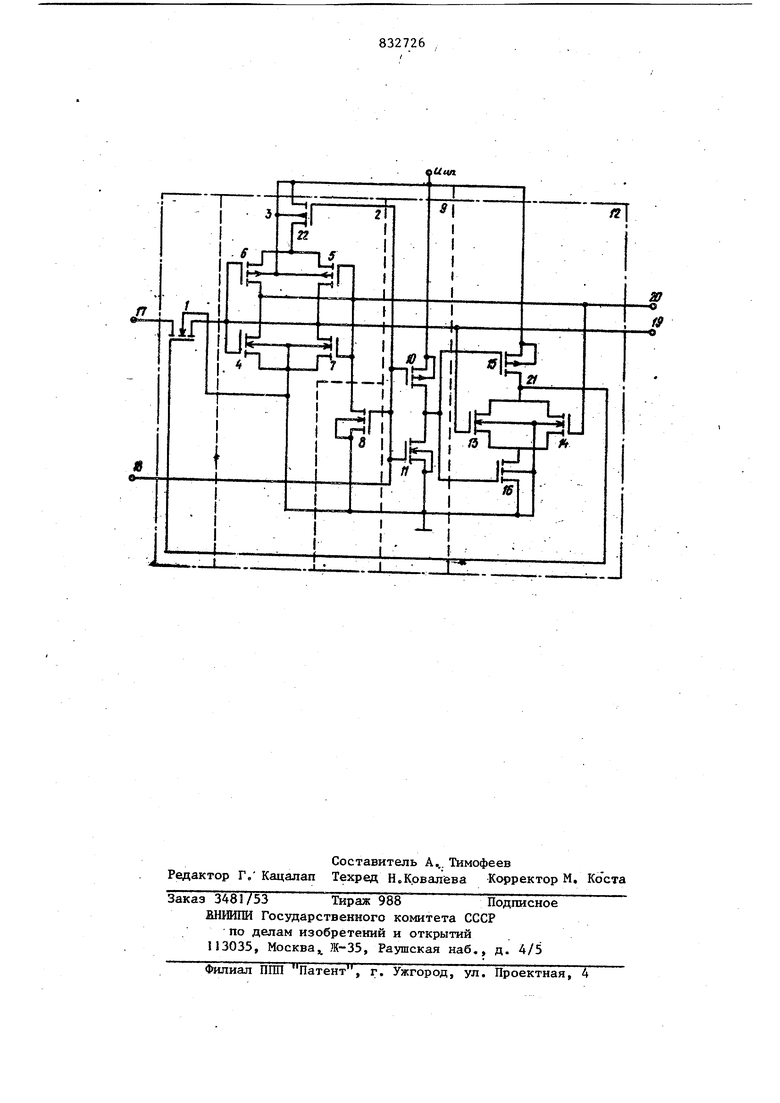

На чертеже приведена принципиальная электрическая схема адресного регистра на КМОП-транзисторах.

Адресный .pjerHCTp на КМОП-транзисторах содержит входной ключ на транзрсторе 1, тактируемый RS-триггер 2

5 на транзисторах 3-7, цепь восстановления исходного состояния на транзисторе 8, синхронизирующее устройство, состоящее из последовательно соединенных инвертора 9 на транзисторах 10 и П и тактируемого элемента 12 ИЛИНЕ на транзисторах 13-16, вход I7 сигнала адреса (совместимый с ТТЛ), вход сигнала выбора 18 (КМОП-уровня),

прямой 19 и инверсньш 20 вьжоды сигнала адреса.

Вход 17 сигнала адреса через тран-зистор 1 входного ключа подключен к правому плечу (выход 19) RS-TpHrrg-i pa, являющемуся прямым выходом сигнала адреса, и первому входу тактируемого элемента ИЛИ-НЕ (затвор транзистора 13), второй вход которого (затвор транзистора 14) соединен с левым плечом (выход 20) триггера, являющимся инверсным выходом сигнала адреса. Затвор транзистора 1 входного ключа подключен к выходу 21 тактируемого элемента ИЛИ-НЕ, соединенному со стоками транзисторов 13-15, причем исток р-канального транзистора 15 подключен к источнику питания Uj , а истоки п-канальных транзисторов 13 и 14 соединены со.стоком п-канального транзистора 16, исток которого подключен к общему выводу. Вход инвертора 9 затворы транзисторов 3 (RS-Триггера) и 8 (цепи восстановления) подключены к входу сигнала выбора, а выход 21 инвертора соединен с тактовым входом элемента ИЛИ-НЕ затворами транзисторов 15-16.

Адресный регистр работает следующим образом.

В исходном состоянии входной ключ на транзисторе 1 открыт, так как сигнал выбора имеет высокий уровень, следовательно, на выходе инвертора 9 низкий уровень, транзистор 15 открыт и напряжение на выходе тактируемого элемента ШШ-НЕ (выход 21) равно нап ряжению источника питания.

Напряжение на выходе 22 RS-триггера 2 и прямом выходе инвертора 9 равно напряжению на входе 17 сигнала адреса. Транзистор 8 цепи восстановления открыт, и напряжение на левом пле че В5 триггера, являющемся инверсным выходом 20 сигнала адреса равно ОБ.

При подаче низкого уровня на вход 18 сигнала выбора микросхемь закрывается транзистор 8 цепи восстановления и открывается транзистор. 3 RSтриггера. При этом выход 22 RS-TpHr Гера через открытый транзистор 3 под ключается к источнику питания. При прохождении сигнала выбора через инвертор 9 закрывается транзистор 15 и открывается транзистор 16«

Если на вход 18 сигнала выбора подан сигнал высокого уровня, открытый транзистор 4 ограничивает заряд паразитной емкости (выход 20),а па-

разитная емкость в адресе 19 заряжается через открытый транзистор 5,

ИЛ до напряжения источника питания U Одновременно с появлением сигнала

высокого уровня на прямом выходе 19 сигнала адреса открывается транзистор 13, и на выходе 21 тактируемого элемента ИЛИ-НЕ устанавливается напряжение О В, в р)езультате чего выходной

0 ключ закрывается, и адресный регистр отключается по входу 17 адреса.

Если в исходном состоянии на вход 17 подан сигнал адреса низкого уровня, при подаче на вход 18 сигнала

5 выбора низкого уровня напряжение на выходе 19 удерживается на низком уровне через открытый входной ключ на транзисторе 1, а на выходе 20 через открытый транзистор 6 устанавд ливается напряжение, равное напряжению источника питания . Одновременно с появлением сигнала высокого уровня на инверсном выходе сигнала 1 адреса. 20 открывается транзистор 14, и на выходе 2 тактируемого элемента ИЛИ-НЕ устанавливается напряжение О В, в ре;зультате чего входной ключ закрывается, и адресньй регистр отключается по входу 17 адреса.

Изобретение обеспечивает упрощение конструкции адресного регистра и схемы памяти в целом, так как позволяет уменьшить число сигналов, Необходимых/ для работа адресного регистра,а следовательно,число щин металлизации и площадь кристалла памяти

Формула изобретения Адресный регистр, сс)держащий входной ключевой МОП-транзистор и уриггер на- КМОП-транзисторах, ус0 {ановочньп 1 МОП-транзистор, включенный между одним входом триггера и общей шиной, о т л и ч а ю щ и йс я тем, что, с целью упрощения устройства и повьшения надежности,

5 в него дополнительно введены инвертор и тактируе1Мый элемент ШШ-НЕ на КМОП-транзисторах, причем вход инвертора подключен к шине сигналов выбора, выход - к тактовому входу

0 тактируемого элемента ИЛИ-НЕ, один вход которого подключен к прямому, второй - к инверсному Е|ркоду триггера, а выход - к затвору входного ключевого МОП-транзистора.

5 Источники информации,

принятые во внимание при экспертизе 1. Электроника, 1978, № 14, с. 38 (прототип.

| название | год | авторы | номер документа |

|---|---|---|---|

| ЯЧЕЙКА ПАМЯТИ СТАТИЧЕСКОГО ОПЕРАТИВНОГО ЗАПОМИНАЮЩЕГО УСТРОЙСТВА | 2012 |

|

RU2507611C1 |

| СТАТИЧЕСКАЯ ЗАПОМИНАЮЩАЯ ЯЧЕЙКА С ДВУМЯ АДРЕСНЫМИ ВХОДАМИ | 2011 |

|

RU2470390C1 |

| Постоянное запоминающее устройство | 1986 |

|

SU1388950A1 |

| АДРЕСНЫЙ ФОРМИРОВАТЕЛЬ | 1991 |

|

RU2010361C1 |

| ДЕШИФРАТОР | 2005 |

|

RU2307405C2 |

| Устройство обнаружения смены адресного сигнала в интегральном исполнении на МОП-транзисторах | 1984 |

|

SU1249695A1 |

| ЭЛЕМЕНТ ВХОДНОГО РЕГИСТРА | 2021 |

|

RU2771447C1 |

| ЭНЕРГОЭФФЕКТИВНЫЙ НИЗКОВОЛЬТНЫЙ КМОП-ТРИГГЕР | 2015 |

|

RU2611236C1 |

| ЭЛЕМЕНТ ВХОДНОГО РЕГИСТРА | 2022 |

|

RU2787930C1 |

| ДВУХТАКТНЫЙ СДВИГАЮЩИЙ РЕГИСТР | 2014 |

|

RU2549136C1 |

Авторы

Даты

1981-05-23—Публикация

1979-07-04—Подача