(54) УСТРОЙСТВО ДЛЯ ДЕКОДИРОВАНИЯ СВЕРТОЧНОГО

КОДА

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство декодирования сверточного кода | 1981 |

|

SU1005322A1 |

| Устройство для декодирования сверточного кода | 1973 |

|

SU510803A1 |

| Декодер сверточного кода | 1984 |

|

SU1319283A1 |

| УСТРОЙСТВО ВЫЧИСЛЕНИЯ МЕТРИК ПУТЕЙ ДЕКОДЕРА ВИТЕРБИ | 1990 |

|

RU2022473C1 |

| УСТРОЙСТВО ДЛЯ ДЕКОДИРОВАНИЯ СВЕРТОЧНОГО КОДА | 1991 |

|

RU2015621C1 |

| Устройство для декодирования сверточного кода | 1989 |

|

SU1612378A1 |

| Устройство для декодирования сверточного кода | 1991 |

|

SU1839281A1 |

| Устройство для декодирования сверточного кода | 1986 |

|

SU1467753A1 |

| Декодер сверточного кода | 1988 |

|

SU1660178A1 |

| УСТРОЙСТВО ДЛЯ ДЕКОДИРОВАНИЯ СВЕРТОЧНОГО КОДА | 1991 |

|

RU2035124C1 |

I

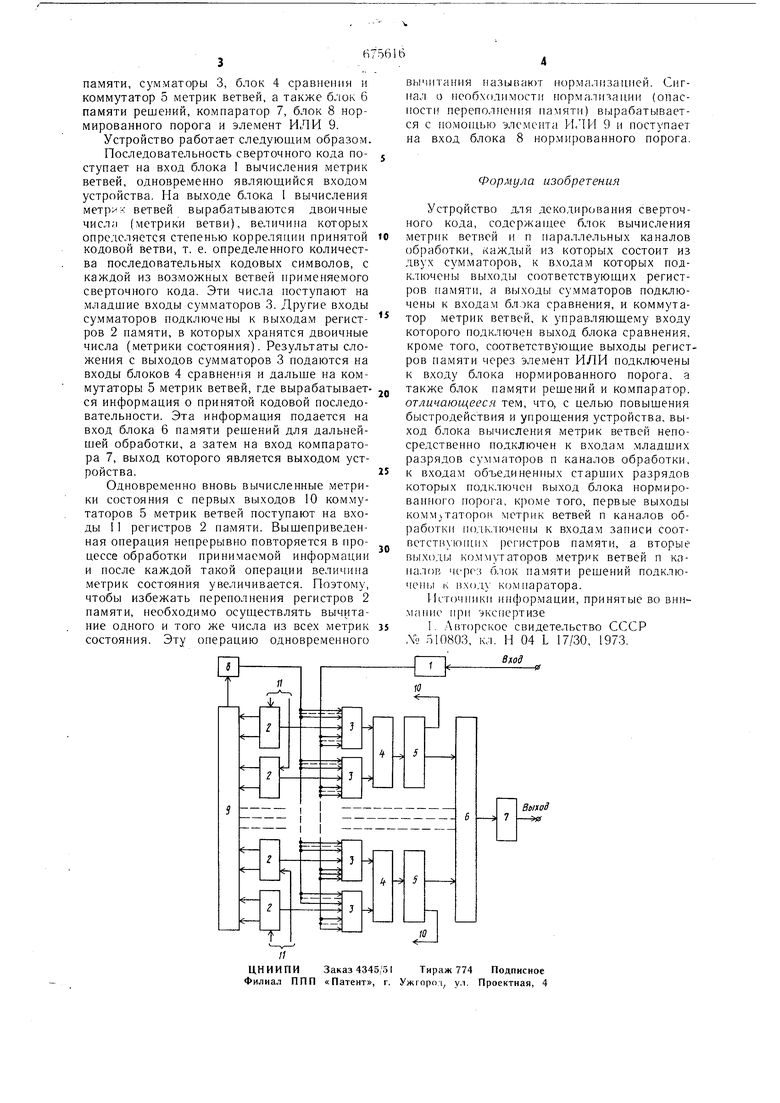

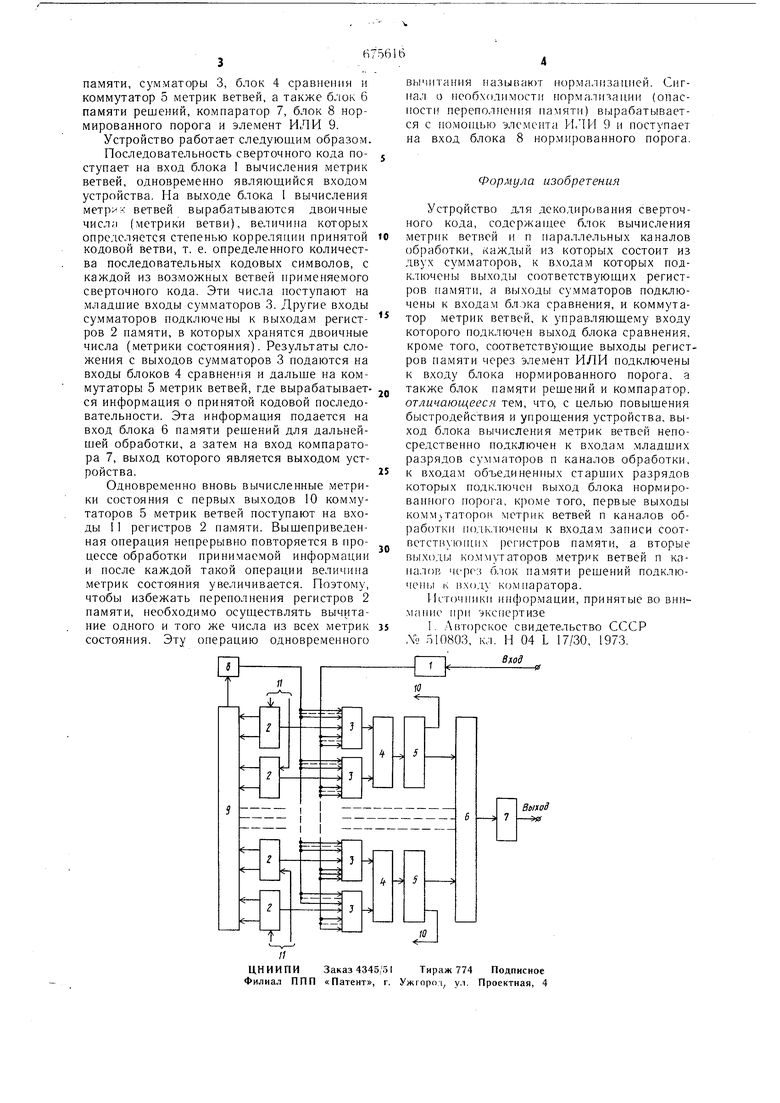

Изобретение относится к телеграфной сг5язи и может быть использовано в системах связи для повышения помехоустойчивости и эффективности.

Известно устройство для декодирования сверточного кода, содержащее блок вычисления метрик ветвей, п параллельных каналов обработки, каждый из которых состоит из двух сумматоров, к входам которых подключены выходы соответствующих регистров памяти, коммутатор метрик ветвей, блок памяти ре1пений и компаратор I. Выходы сумматоров по;1К.- ючены к входам блока сравнения, выход которого подключен к входу коммутатора метрик ветвей. Соответствующие выходы регистров памяти подключены через элемент И,1И к 15ход блока нормированного порога.

Однако это устройство обладает недостаточно высоким бь стродек(.ТВи:.

Целью изобретения является повыщение быстродействия и упрощение устройства.

Для этого в устройстве для декодирования сверточного кода, содержащем блок вычисления метрик ветвей н п параллельных каналов обработки, каждый из которых состоит из двух сумматоров, к входам которых

подключены выходы соответствующих регистров памяти, а выходы сумматоров подключены к входам блока сравнения, и коммутатор метрик ветвей, к управляющему входу которого подключен выход блока сравнения, кроме того, соответствующие выходы регистров памяти через элемент И.ПИ подключены к входу блока нормированного порога, а также блок памяти рещений и компаратор, выход блока вычисления метрик ветвей непосредственно подключен к входам м.1ад1иих разрядов сумматоров п каналов обработки.к входам объединенных старших разрядов которых подключен выход блока нормированного порога, при этом первые выходы коммутаторов метрик ветвей п каналов обработки подключены к входам записи соответствующих регистров памяти, а вторые выходы коммутаторов метрик ветвей п каналов через блок памяти решений подключены к входу компаратора.

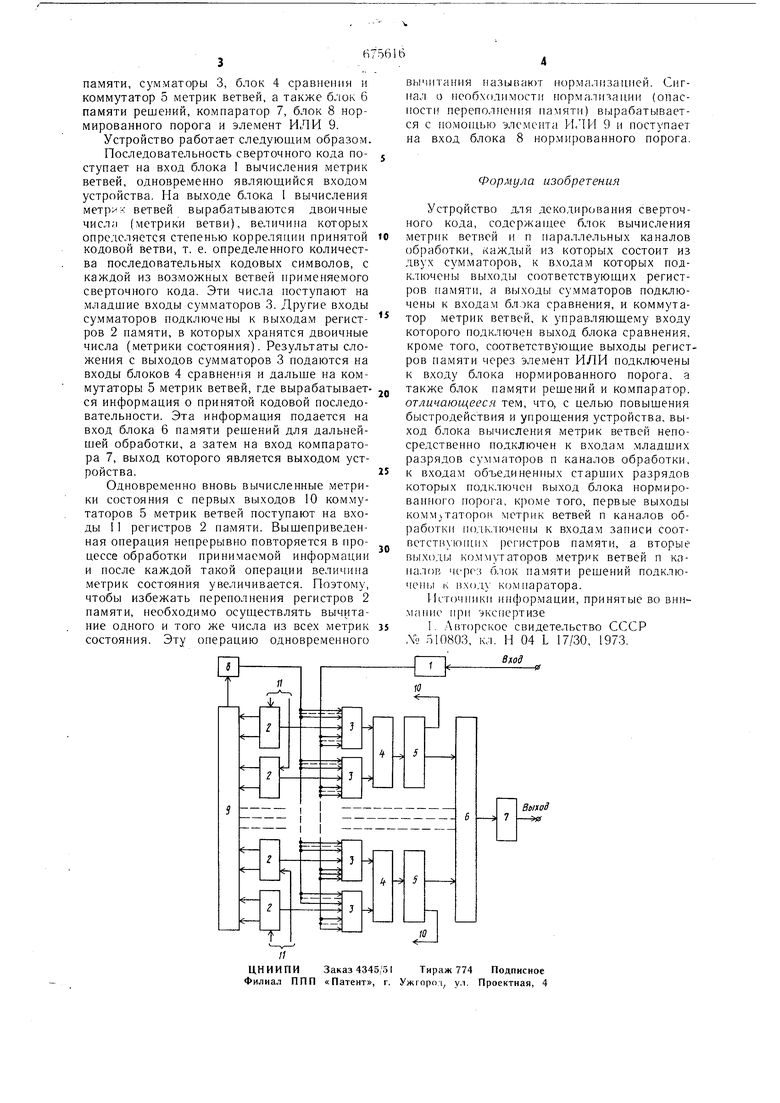

На чертеже представлена структурная

электрическая схема предлагаемого устройства.

Оно содержит блок 1 вычисления метрик ветвей п параллельных каналов обработки, каждый из которых содержит регистры :

Авторы

Даты

1979-07-25—Публикация

1977-10-26—Подача