ПИи9

fae. f

1А2

; ованной из частичных комбинаций, Случайно выбираемых из алфавитов. Цель изобретения - повышение информативности устройства путем уменьшения объема данных, загружаемых в устройство для приема и обнаружения комбинации двоичных сигналов, за счет программирования таблиц корреляционных кодов в блоке памяти 6 программатором 17. Для настройки уст- |ройства на прием и обнаружение сос- Iтавной комбинации двоичных сигналов, I образованной из частичных комбинаций, I случайно выбираемых из алфавитов Комбинаций известного вида, от внешнего устройства требуется загрузка только алфавитов частичных комбинаций в блок памяти, 16, объем которых существенно меньше объема корреляционных таблиц. Таблицы корреляционных кодов формируются программатором 17 путем сравнения методом максимально- го правдоподобия всех разрядных дво8

ичных наборов слова выборочной комбинации с эталонами алфавита частичной комбинации. В рабочем режиме коды слов выборочной комбинации, формируемых из потока принимаемых двоичных сигналов О, 1.блоком памяти 1, регистром 2, триггером 3 и коммутатором 4 поступают через коммутатор 5 вместе с кодом номера слова выборочной комбинации из счетчика 8 на адресные входы блока памяти 6 и считывают на его выходы корреляционное число, равное числу информационных позиций, на которых слово выборочной комбинации совпадает с наиболее близким эталоном соответствуюш,его алфавита частичной комбинации. Решение об обнаружеми составной комбинации принимается пороговым элементом 12, если сумма корреляционных чисел для всех слов выборочной комбинации, накопленная сумматором 10,не меньше заданного порога. 1 з.п. ф-лы,7 ил.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для приема и обнаружения комбинации двоичных сигналов | 1987 |

|

SU1413656A1 |

| Устройство для приема и обнаружения комбинации двоичных сигналов | 1984 |

|

SU1156110A1 |

| Устройство для приема информации | 1983 |

|

SU1088051A1 |

| Логическое запоминающее устройство | 1981 |

|

SU1014036A1 |

| Обнаружитель комбинации двоичных сигналов | 1985 |

|

SU1506463A1 |

| Выделитель составной комбинации двоичных сигналов | 1984 |

|

SU1223411A1 |

| Устройство для сопряжения вычислительной машины с каналом связи | 1985 |

|

SU1291994A1 |

| Устройство приема двоичных сигналов | 1984 |

|

SU1197116A1 |

| Устройство для преобразования форматов слов двоичной последовательности | 1988 |

|

SU1513436A1 |

| АВТОМАТИЗИРОВАННОЕ УСТРОЙСТВО КОНТРОЛЯ И ДИАГНОСТИРОВАНИЯ РАДИОЭЛЕКТРОННЫХ ИЗДЕЛИЙ | 1998 |

|

RU2174699C2 |

Изобретение относится к связи и может быть использовано в устройствах обработки дискретных сообщений для обнаружения составной комбинации при независимом моменте ее прихода в потоке двоичных сигналов и обрй

1

Изобретение относится к связи и может использоваться в устройствах обработки дискретных сообщений для обнаружения составной комбинации при неизвестном моменте ее прихода в по- токе двоичных сигналов и образованной из частичных комбинаций, случайно выбираемых из алфавито1 комбинаций известного вида, и. является усовершенствованием устройства по авт.св. № 1156110.

Целью изобретения является повышение информативности устройства путем уменьшения объема загружаемых данных.

Основное устройство анализирует поток двоичных сигналов, сопровождаемых тактовыми импульсами и в каждом тактовом интервале вычисляет число информационных позиций, на которых выборочная комбинация совпадает с эталоном, т.е. с подлежащей обнаружению комбина1у1ей. Принимаемые двоичны сигналы записываются в первый блок памяти таким образом, что последний в каждом тактовом интервале содержит

N-разрядную выборочную комбинацию, образованную двоичными сигналами,принятыми в данном и в N-1-M предыдущих тактовых интервалах (N - длина эталона). Выборочная комбинация хра- нип-ся в первом блоке памяти qm-раз- рядными словами, причем N qm.

В течение тактового интервала (интервал между соседними тактовыми импульсами) слова выборочной комбинации последовательно считываются на выход первого блока памяти и через второй коммутатор поступают на младшие адресные входы второго блока памяти, на старшие адресные входы которого через второй коммутатор поступает код номера слова выборочной комбинации с выходов первого счетчика адреса. Ячейки второго блока памяти разбиты на q таблиц корреляционных кодов, при этом адрес таблицы задается кодом номера слова выборочной комбинации, а адрес ячейки внутри таблицы - кодом самого слова.

Выбираемая таким образом ячейка второго блока памяти содержит код

испа информационных позиций, на которых слово выбор.очной комбинации совпадает с соответствующим словом эталона. Сумматор совместно с вторым регистром накапливает сумму этих чисел. После обработки в течение тактового интервала q слов выборочной комбинации второй регистр содержит

число, равное числу ин формационных позиций, на которых выборочная комбинация совпадает с эталоном. Если это число не меньше порогового числа в третьем (пороговом) регистре, на выходе порогового элемента формируется сигнал обнаружения комбинации

Аналогичным образом в следующем тактовом интервале производится сравнение эталона с новой выборочной комбинацией и формирование сигнала обнаружения. Образование, хранение и считывание слов выборочной комбинации осуществляется первым блоком памяти с помощью первого регистра,триггера, первого коммутатора и первого счетчика адреса под управлением выходных сигналов хронизатора. Данные элементы устройства в совокупности эквивалентны регистру сдвига.

Дпя обнаружения составной комбина ции,. образованной Lm-разрядными частичными комбинациями, случайно выбираемыми из алфавитов комбинаций известного вида, число разрядов ячеек первого блока памяти задается равным числу разрядов частичной комбинации, а в каждую ячейку второго блока памяти записывается число, равное числу информационных позиций, на которых слово выборочной комбинации, соответствующее ячейке второго блока памяти, совпадает с наиболее сходной с ним комбинацией (эталоном) алфавита. .При этом обнаружение составной комбинации осуществляется принятием решения о приеме частичных комбинаций по методу максимального правдоподобия.

Данные для настройки устройства н другую комбинацию загружаются внешним устройством по алгоритму: начальная установка в ноль второго счетчика адреса; установка слова данных на входе данных второго блока памяти; запись слова данных во второй блок . памяти подачей импульса на его вход записи. Далее при последовательном ; наращивании содержимого второго счет чика адреса .аналогичным образом за

0

5

0

25

0

35

0

45

50

55

писываются остальные слова данных во второй блок п амяти.

Недостатком данного устройства является большой объем данных, загружаемых в него из внешнего устройства, Объем загружаемых данных для комбинации, состоящей из Lm-разрядных час-i тичных комбинаций, равен SLZ бит (S - число разрядов двоичного кода числа т), так как для каждой частичной комбинации требуется хра-нить во втором блоке памяти результаты сравнения эталона частичной комбинации со всеми 2 двоичными наборами слова вьН борочной комбинации.Например,для L|, m 8 (практически не очень большая длина составной комбинации) объем загружаег-5ых данных равен 8192 бита. Внешнее устройство, на- пример микроэвм, должно иметь допап- нительную память для хранения указанного объема данных и затрачивать машинное время для загрузки последних в устройство приема и обнаружения комбинации двоичных сигналов.

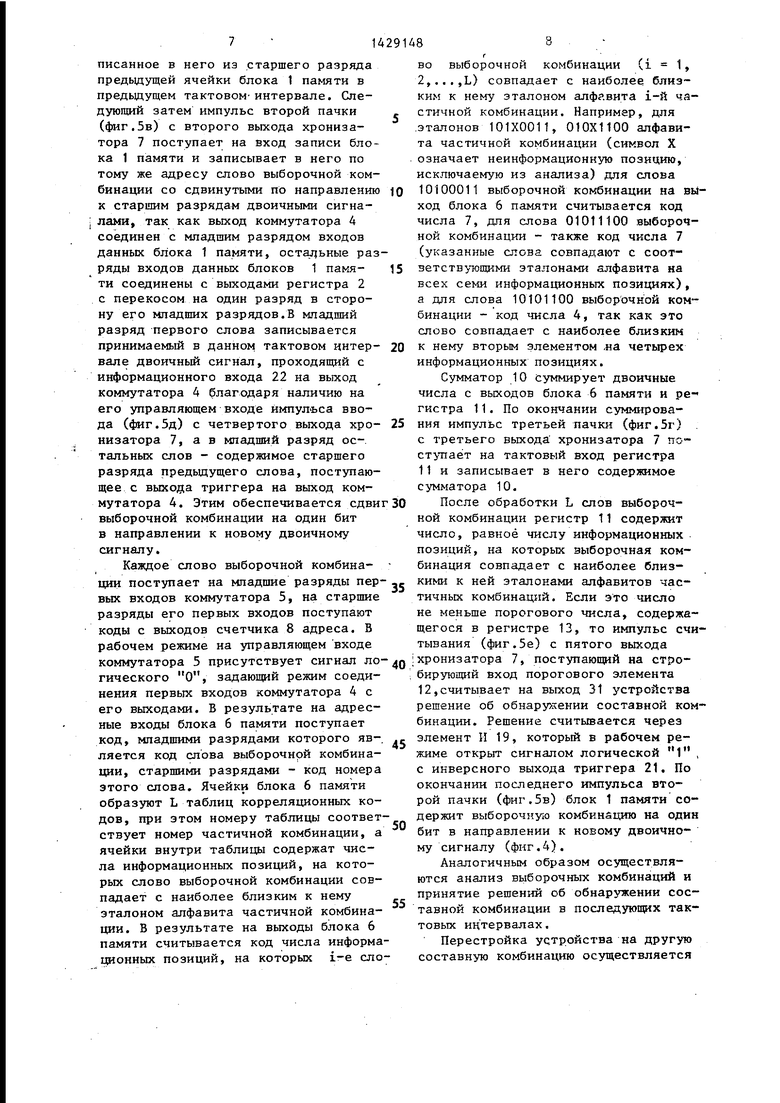

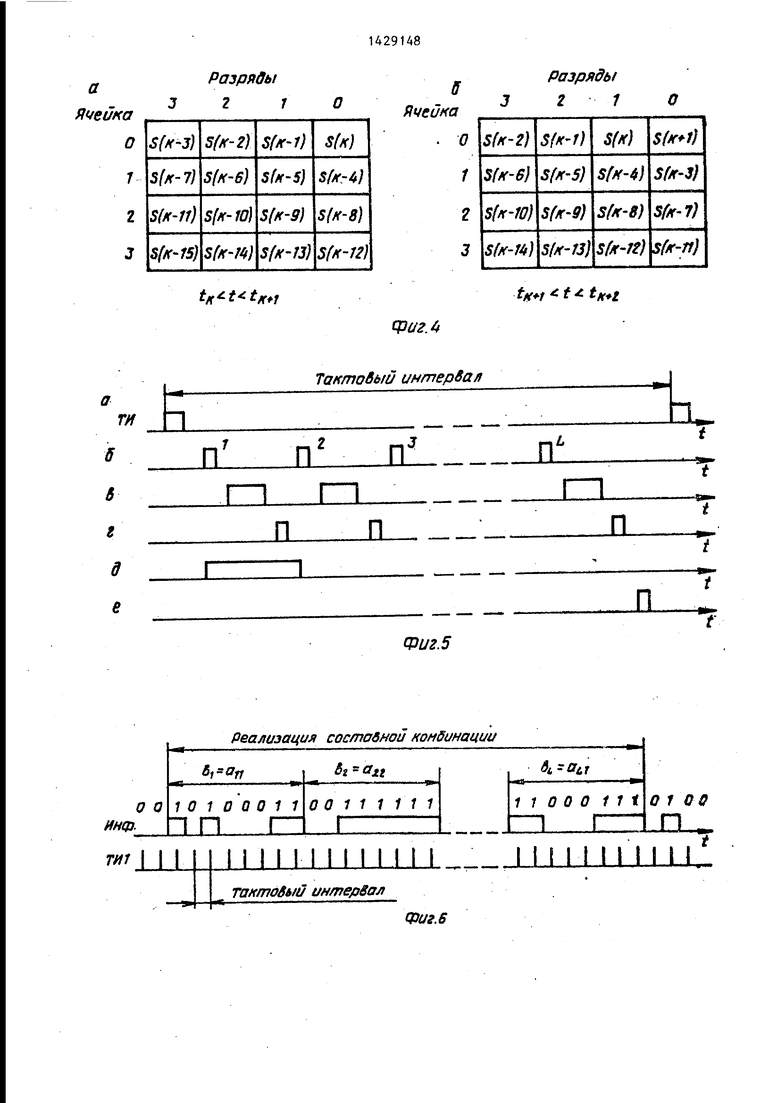

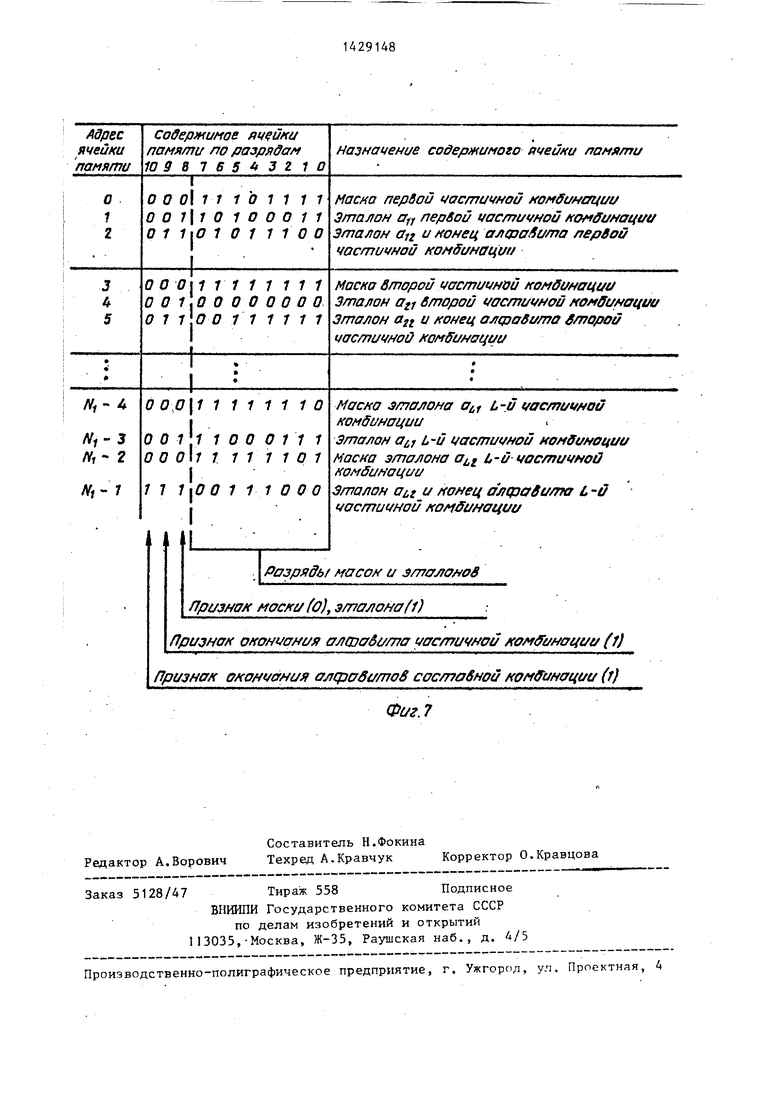

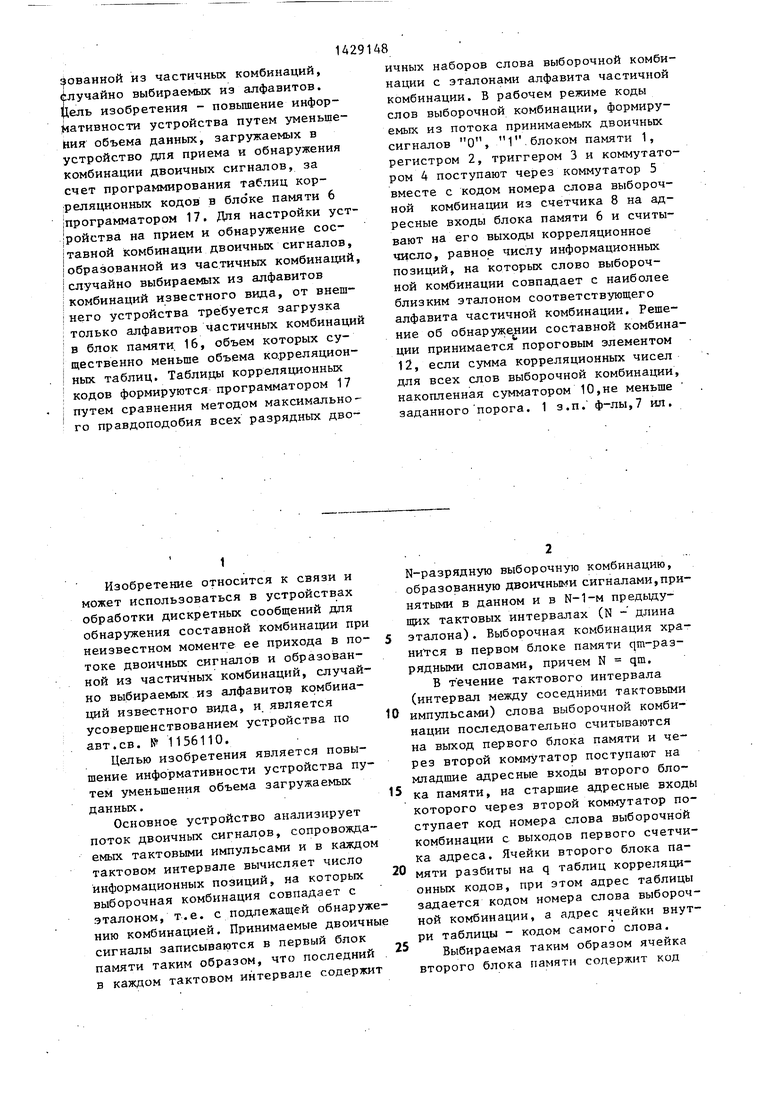

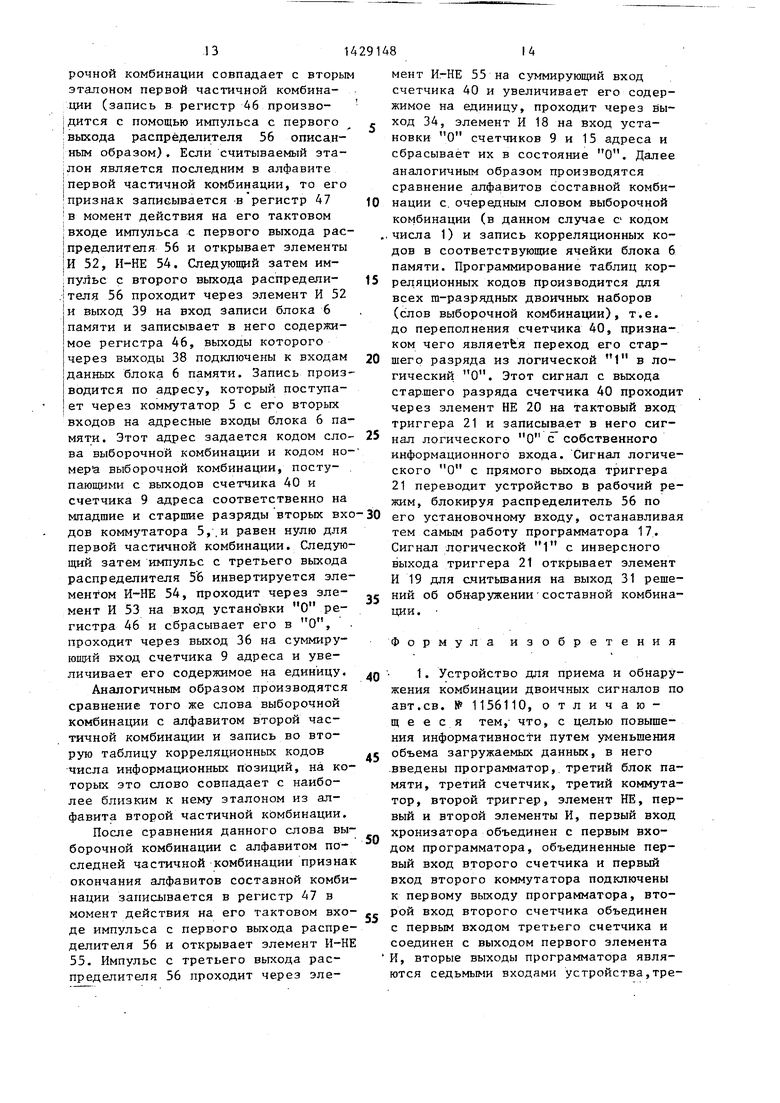

На фиг.1 приведена структурная схема предлагаемого устройства; на фиг.2 - структурная схема программатора; на фиг.З - временные диаграммы входных двоичных сигналов и тактовых импульсов; на фиг.4. - пример содержимого ячеек блока 1 памяти;на фиг,5- временные диаграммы управляющих сигналов хронизатора; на фиг.6 - пример реализации составной комбинации двоичных сигналов; на фиг.7 - расположение масок и эталонов частичных комбинаций в блоке 16 памяти,

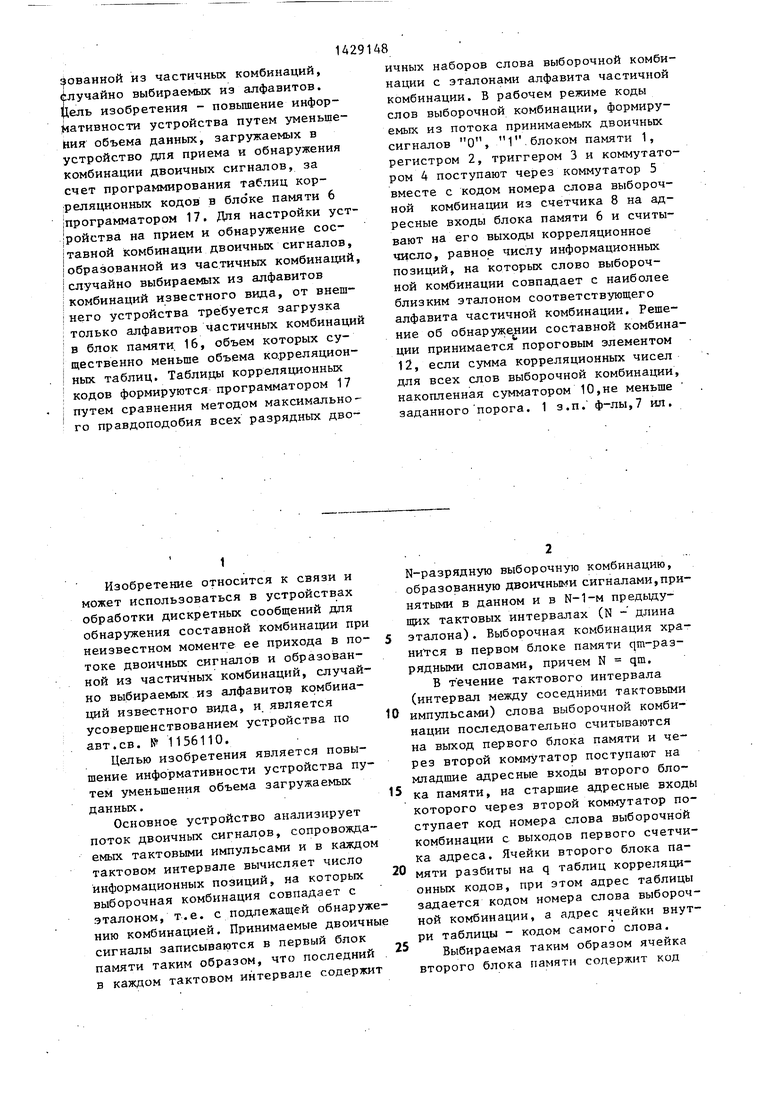

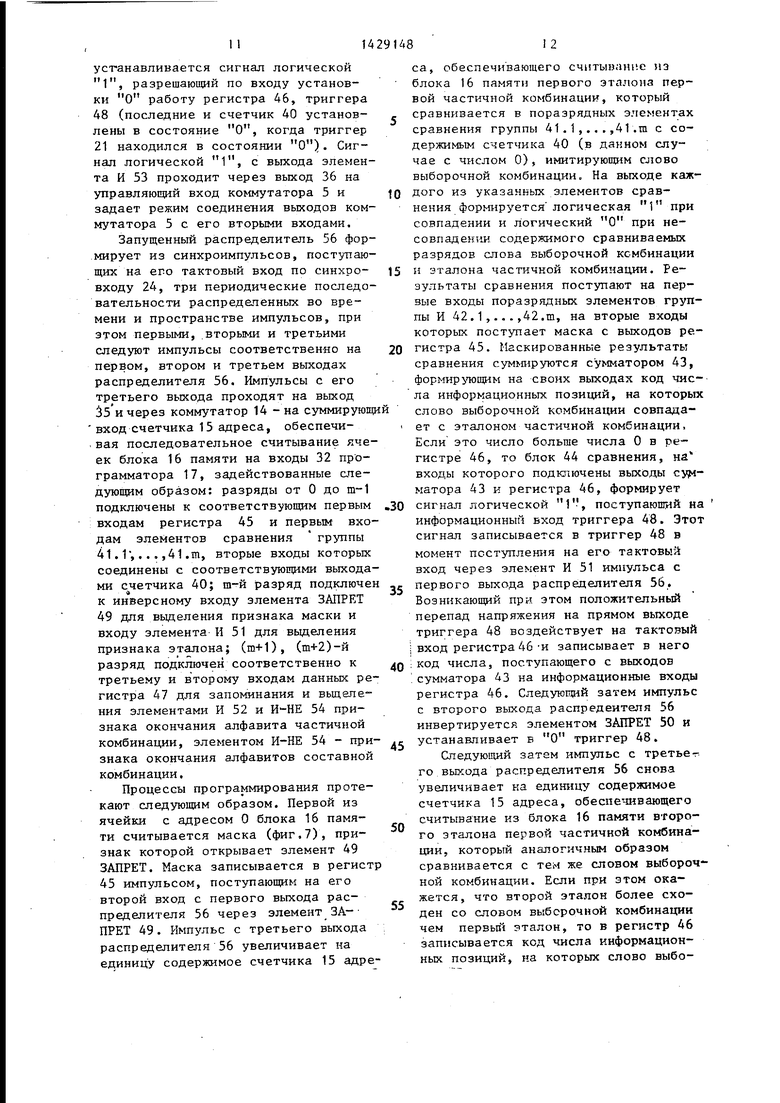

Устройство для приема и обнаружения комбинации двоичных сигналов (фиг.1) содержит блок 1 памяти, регистр 2,, триггер 3, коммутаторы 4 и 5, блок 6 памяти, хронизатор 7,счетчики 8 и 9 адреса, сумматор 10, регистр 11, пороговый элемент 12, ;регистр 13, коммутатор 14, счетчик 15 адреса, блок 16 памяти, программатор 17, элементы И 18 и 19, элемент НЕ 20, триггер 21, входы 22-30 устройства, выход 31 устройства, а также входы 32 и 33, выходы 34-39 программатора 17.

Программатор 17 (фиг.2) содержит счетчик 40, группу элементов 41.1,,..,41.т сравнения, группу элементов И 42.1,... ,42.1П, сумматор 43, блок 44 сравнения, регистры 45 - 47, триггер 48, элементы ЗАПРЕТ 49 и

50, элементы И 51-53, элементы И-НЕ 54 и 55, распределитель 56.

Устройство для приема и обнаружения комбинации двоичных сигналов работает следующим образом.

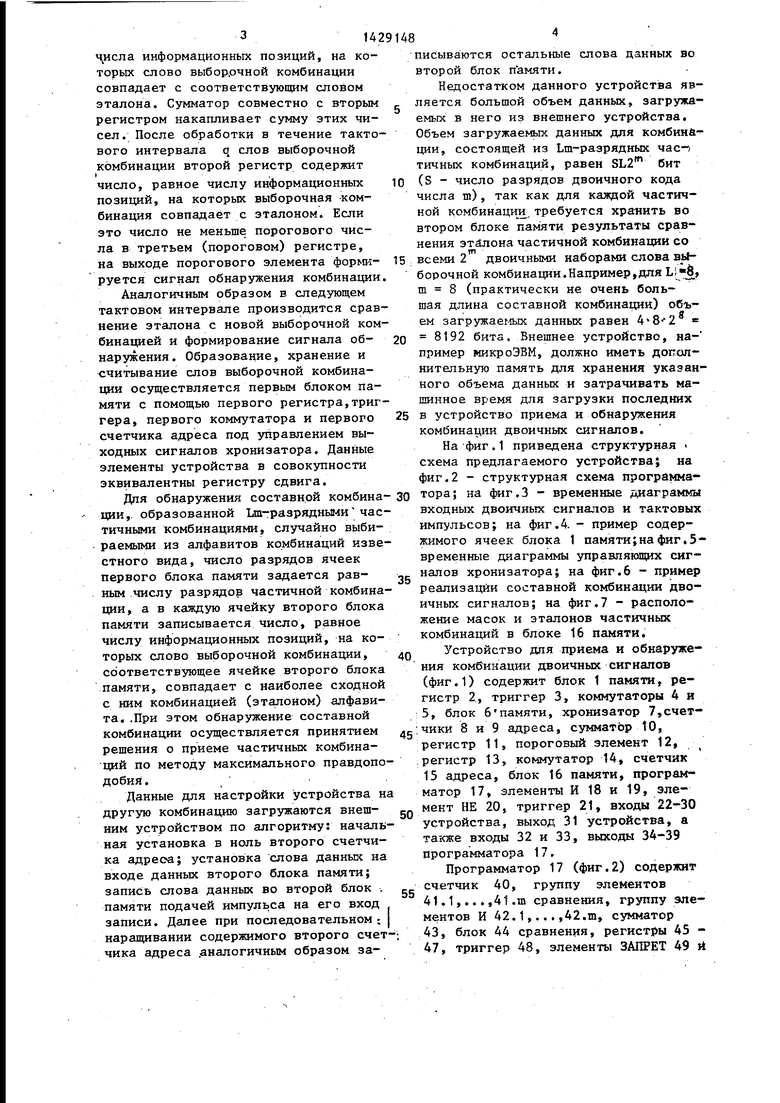

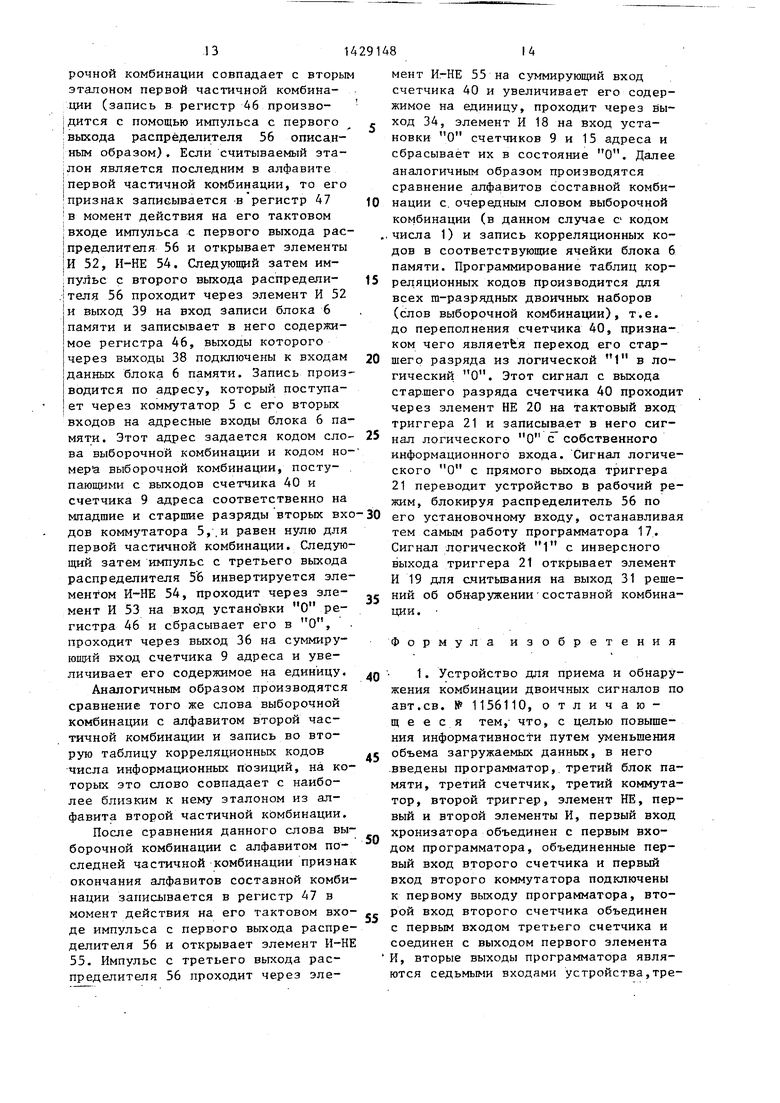

В рабочем режиме устройство анализирует поток принимаемых двоичных сигналов (фиг,За), сопровождаемых тактовыми импульсами (фиг.Зб), в каждом тактовом интервале (интервал между соседними тактовыми импульсами) вычисляет корреляционное число, , равное числу информационных позиций, на которых выборочная комбинация совпадает с эталоном (вариантом составной комбинации), и формирует ре- .шение об обнаружении комбинации, если это число не меньше порога. При этом обнаружение составной комбинации осуществляется путем сравнения слов выборочной комбинации с алфа- витом частичньрс комбинаций и принятия решения о приеме каждой частичной комбинации по методу .максимального правдоподобия..

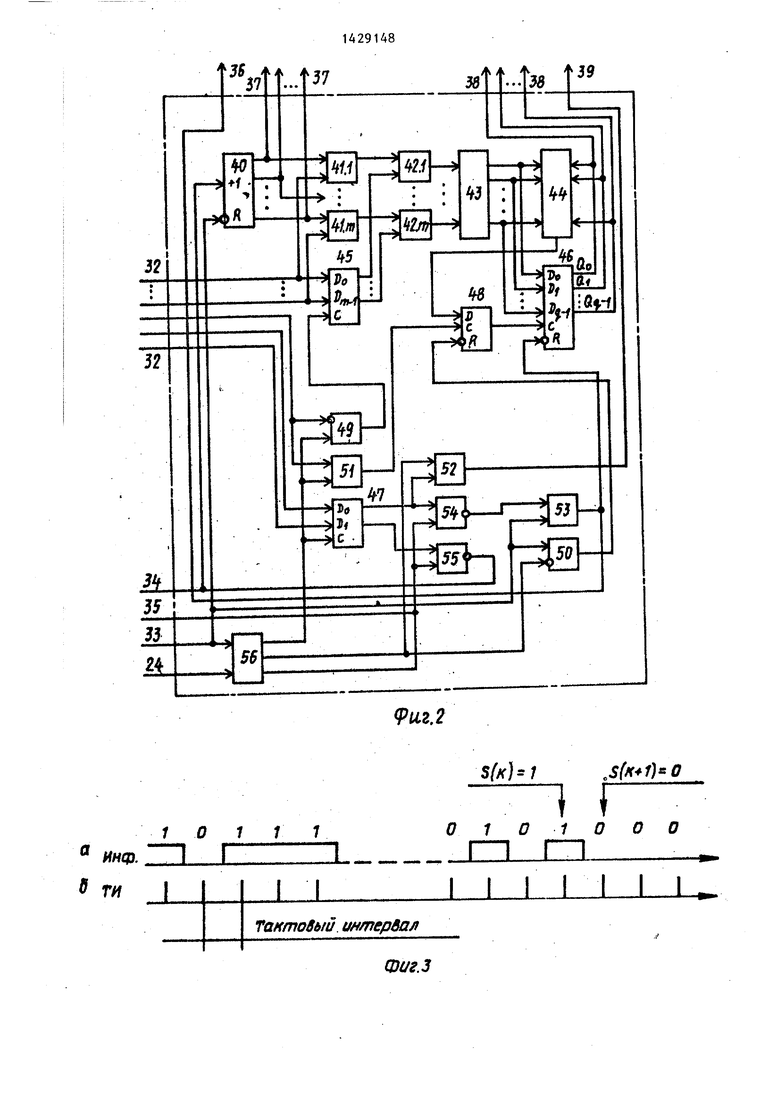

Составная комбинация на передающей стороне представляет собой последовательность Ь,, частичных комбинаций (фиг.6), при этом i-я частичная комбинация (i 1, 2,...,L), случайным о.бразом выбирается из алфавита а., а., ....,а . объемом j .

частичных комбинаций известного вида, т.е. Ь; е

11 i i i J1 J

Все частичные комбинации имеют одинаковую длину (число разрядов) т, поэтому все реализации (варианты) составной комбинации имеют одинаковую дпину N . mL. Часть из m позиций (разрядов) может быть неинформационной для устройства и должна исклю- чаться из анализа.

Принимаемые двоичные сигналы в виде последовательности элементарных яосыпок О, 1 (фиг.За) поступают по входу 22 на вход коммутатора 4. По входу 23 на вход хронизатора 7, вход установки О счетчика адреса 8 и регистра 11 поступают синхронизированные с двоичными сигналами тактовые импульсы (фиг.Зб). Очередной тактовый импульс устанавливает в ноль счетчик адреса 8, регистр 11 и запускает хро- низатор 7, который в ответ на тактовый импульс вырабатывает в интервале между соседними тактовыми импульса0

5

0

5

ми (фиг.Зб, 5а) следующие управляющие сигналы: первую пачку из L импульсов (фиг.56); вторую пачку из L импульсов (фиг.5в), задержанную относительно первой пачки; третью пачку из L импульсов (фиг.5г), задержанную относительно второй пачки; импульс ввода принимаемого двоичного сигнала (фиг . 5д) ;импульс считывания (фиг. 5е) . Указанные управляющие сигналы формируются соответственно на первом-пя- том выходах хронизатора 7 из синхроимпульсов, поступающих по синхро- входу 24.

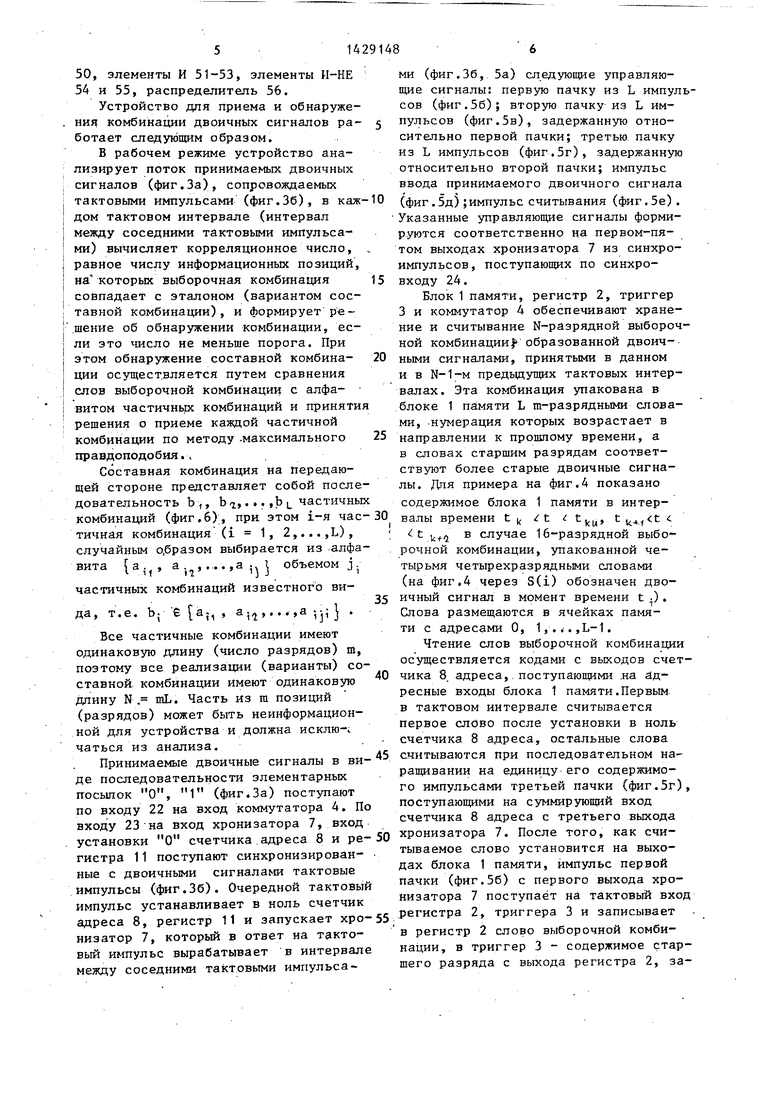

Блок 1 памяти, регистр 2, триггер 3 и коммутатор А обеспечивают хранение и считывание N-разрядной выборочной комбинации образованной двоичными сигнапами, принятыми в данном и в N-1-M предьиущих тактовых интервалах. Эта комбинация упакована в блоке 1 памяти L m-разрядными словами, нумерация которых возрастает в направлении к пропшому времени, а в словах старшим разрядам соответствуют более старые двоичные сигналы. Для примера на фиг.4 показано

содержимое блока 1 памяти в интервалы времени t | t t,, с t t в случае 16-разрядной выборочной комбинации, упакованной четырьмя четырехразрядными словами (на фиг.4 через S(i) обозначен дво- 5 ичный сигнал в момент времени t .). Слова размещаются в ячейках памяти с адресами О, 1,...,L-1.

Чтение слов выборочной комбинации осуществляется кодами с выходов счетчика 8, адреса,. поступающими .на адресные входы блока 1 памяти.Первым в тактовом интервале считывается первое слово после установки в ноль счетчика 8 адреса, остальные слова снитываются при последовательном наращивании на единицу его содержимого импульсами третьей пачки (фиг.5г), поступающими на суммирующий вход счетчика 8 адреса с третьего выхода хронизатора 7. После того, как считываемое слово установится на выходах блока 1 памяти, импульс первой пачки (фиг.56) с первого выхода хронизатора 7 поступает на тактовый вход регистра 2, триггера 3 и записывает в регистр 2 слово выборочной комбинации, в триггер 3 - содержимое старшего разряда с выхода регистра 2, за0

0

5

0

5

писанное в него из старшего разряда предыдущей ячейки блока 1 памяти в предьщущем тактовом-интервале. Следующий затем импульс второй пачки (фиг.Зв) с второго выхода хрониза- тора 7 поступает на вход записи блока 1 памяти и записывает в него по тому же адресу слово выборочной комбинации со сдвинутыми по направлению jQ к старшим разрядам двоичными сигна- лами, так как выход коммутатора 4 соединен с младшим разрядом входов данных блока 1 памяти, остадьные разряды входов данных блоков 1 памя- 15 ти соединены с выходами регистра 2 с перекосом на один разряд в сторону его младших разрядов.В младший разряд первого слова записывается принимаемый в данном тактовом интер- 20 вале двоичный сигнал, проходящий с информационного входа 22 на выход коммутатора 4 благодаря наличию на его управляющем входе ймпулъса ввода (фиг.Зд) с четвертого выхода хро- 25 низатора 7, а в младший разряд остальных слов - содержимое старшего разряда предыдущего слова, поступающее с выхода триггера на выход коммутатора 4. Этим обеспечивается сдвиг 30 выборочной комбинации на один бит в направлении к новому двоичному сигналу.

Каждое слово выборочной комбина- - дни поступает на младшие разряды пер- ,, вых входов коммутатора 5, на старшие разряды его первых входов поступают коды с выходов счетчика 8 адреса. В рабочем режиме на управляющем входе коммутатора 5 присутствует сигнал ло- Q гического О, задающий режим соединения первых входов коммутатора 4 с его выходами. В результате на адресные входы блока 6 памяти поступает код, младшими разрядами которого яв- ., ляется код слова выборочной комбинации, старшими разрядами - код номера этого слова. Ячейки блока 6 памяти образуют L таблиц корреляционных кодов, при этом номеру таблицы соответствует номер частичной комбинации, а ячейки внутри таблицы содержат числа информационных позиций, на которых слово выборочной комбинации совпадает с наиболее близким к нему зталоном алфавита частичной комбинации. В результате на выходы блока 6 памяти считывается код числа информационных позиций, на которых i-e слово выборочной комбинации (, 2,...,L) совпадает с наиболее близким к нему зталоном алфавита i-й частичной комбинации. Например, для эталонов 101X0011, 010X1100 алфавита частичной комбинации (символ X означает неинформационную позицию, исключаемую из анализа) для слова 10100011 выборочной комбинации на выход блока 6 памяти считывается код числа 7, для слова 01011100 выборочной комбинации - также код числа 7 (указанные слова совпадают с соответствующими эталонами алфавита на всех семи информационных позициях), а для слова 10101100 выборочной комбинации - код числа 4, так как это слово совпадает с наиболее близким к нему вторым элементом ла четырех информационных позициях.

Сумматор 10 суммирует двоичные числа с выходов блока 6 памяти и ре- гистра 11. По окончании суммирования импульс третьей пачки (фиг.Зг) . с третьего выхода хронизатора 7 поступает на тактовый вход регистра 11 и записывает в него содержимое сумматора 10.

После обработки L слов выборочной комбинации регистр 11 содержит число, равное числу информационных позиций, на которых выборочная комбинация совпадает с наиболее близкими к ней эталонами алфавитов частичных комбинаций. Если это число не меньше порогового числа, содержащегося в регистре 13, то импульс считывания (фиг.Зе) с пятого выхода хронизатора 7, поступающий на стро- бирующий вход порогового элемента 12,считывает на выход 31 устройства решение об обнаружении составной комбинации. Решение считывается через элемент И 19, который в рабочем режиме открыт сигналом логической 1 , с инверсного выхода триггера 21. По окончании последнего импульса второй пачки (фиг.Зв) блок 1 памяти содержит выборочную комбинацию на один бит в направлении к новому двоичному сигналу (фиг.4).

Аналогичным образом осуществляются анализ выборочных комбинаций и принятие решений об обнаружении составной комбинации в последующих тактовых интервалах,

Перестройка устройства на другую составную комбинацию осуществляется

программированием блока 6 памяти.Дл . этого сначала,не прерывая рабочий ; режим устройства, в блок 16 памяти загружают маски и эталоны алфавитов частичных комбинаций, затем программатор 17 формирует таблицы корреляционных кодов и загружает их в блок 6 .памяти (маска стужит для указания информационны х позиций час : тичной комбинации: на информационной позиции разряд маски содержит логическую 1, на неинформационной позиции - логический О).

. Для загрузки масок и эталонов частичных комбинаций внешнее устройство (не показано) устанавливает на управляющем входе 30 команду загрузки в виде импульса логического О, которая .поступает на вход

30

35

установки О триггера 21 непосредственно и счетчика 15 адреса через элемент И 18 (последний для сигналов логического О выполняет функцию элемента ИЛИ), устанавливая их 25 в состояние 0. Сигнал логического О с прямого выхода триггера 21 поступает на управляющий вход коммутатора 14 и переводит последний в режим связи его выхода с первым управ ляющим входом 27. После этого внешнее устройство осуществляет загрузку данных в блок 16 памяти по алгоритму : установка данных на входах 25 данных, соединенных с входами данных блока 16 памяти; запись в блок 16 памяти подачей на его вход записи импульса записи по второму управляющему входу 28 (данные записываются в ячейку с адресом, равным содержимому счетчика 15 адреса, выходами соединенного с адресными вхоами блока 16 памяти); увеличение на единицу адреса ячейки блока 16 паяти подачей импульса по управляюему входу 27 коммутатор 14 суммирующий вход счетчика 15 адреса. Далее указанные шаги алгоритма пой- торяются до окончания загрузки.

Структура и формат данных, содер- „ жащихся в блоке 16 памяти, приведены на фиг.7 для m 8 (для сравнения на фиг.6 показана соответствующая иг.7 составная комбинация а, а.,,,,а в потоке принимаемых дво- ичных сигналов). Данные располагаются в ячейках с адресами от О до N,-1, где N - сумма чисел масок и эталонов алфавитов частичных комбинаций. Раз40

45

5 0

0

5

5

ряды 0-7 (в общем случае от О до т-1) являются разрядами масок и эталонов, разряд 8 (в общем случае, т) е содержит признак маски (в разряде

логический О) или эталона (в разряде логическая 1). Разряд 9 (в общем случае т+1) содержит признак продолжения (в разряде логический О) или окончания (в разряде логическая 1) алфавита частичной комбинации. Разряд 10 (в общем случае т+2) содержит признак продолжения или окончания алфавитов составной комбинации (в разряде соответственно логический О или 1). Для каждой частичной комбинации первой следует маска, затем эталоны ее алфавита. Возможен случай, когда отдельным эталонам может предшествовать своя маска (содержимое для L-й частичной комбинации на фиг.7), или маска может быть одна для всех частичных комбинаций. Разряды маски, отвечающие информационной или неинформационной позициям, содержат соответственно логическую 1 или логический О. Число входов данных (выходов) блока 16 памяти равно т+3, число его адресных входов равно числу разрядов двоичного кода числа т. Для программирования таблиц корреляционных кодов внешнее устройство устанавливает на управляющем входе 29 команду пуска в виде импульса логического О, которая поступает на вход установки 1. триггера 21 непосредственно, устанавливая его в со0

5

стояние 1, и на вход установки О счетчиков 9 и 15 адреса через элемент И 18, устанавливая счетчики 9 и 15 адреса в состояние О. Сигнал логической 1 с прямого выхода триггера 21 поступает на управляющий вход коммутатора 14. и переводит последний в режим связи его выхода с выходом 35 программатора 17. Сигнал логического О с инверсного выхода триггера 21 закрывает элемент И 19, бло- кируя в этом случае считывание на вы-, ходе 31 ложных решений об обнаружении составной комбинации. Сигнал логической 1 с прямого выхода триггера 21 поступает также по входу 33 в программатор 17 и запускает распределитель 56 по его установочному входу, разрешает работу счетчика 40 по его входу установки О, открывает элементы ЗАПРЕТ 50 и И 53. При этом на выходе элементов 50 и 53

усганавливается сигнал логической 1, разрешающий по входу установки О работу регистра 46, триггера

48(последние и счетчик 40 установлены в состояние О, когда триггер 21 находился в состоянии О). Сигнал логической 1, с выхода элемента И 53 проходит через выход 36 на управляющий вход коммутатора 5 и задает режим соединения выходов коммутатора 5 с его вторыми входами.

Запущенный распределитель 56 формирует из синхроимпульсов, поступающих на его тактовый вход по синхро- входу 24, три периодические последовательности распределенных во времени и пространстве импульсов, при этом первыми,.вторыми и третьими следуют импульсы соответственно на первом, втором и третьем выходах распределителя 56. Импульсы с его третьего выхода проходят на выход З5 и через коммутатор 14 -на суммирующ вход счетчика 15 адреса, обеспечивая последовательное считывание ячеек блока 16 памяти на входы 32 программатора 17, задействованные следующим образом: разряды от О до т-1 подключены к соответствующим первым входам регистра 45 и первым входам элементов сравнения группы 41.1,..., 41. т, вторые входы которых соединены с соответствующими выходами счетчика 40; ш-й разряд подключен к инверсному входу элемента ЗАПРЕТ

49для выделения признака маски и входу элемента И 51 для вьщеления признака эталона; (т+1), (т+2)-й разряд подключен соответственно к третьему и второму входам данных регистра 47 для запоминания и выделения элементами И 52 и И -НЕ 54 признака окончания алфавита частичной комбинации, элементом И-НЕ 54 - при- знака окончания алфавитов составной комбинации,

Процессы программирования протекают следующим образом. Первой из ячейки с адресом О блока 16 памя

ти считывается маска (фиг,7), признак которой открывает элемент 49 ЗАПРЕТ. Маска записывается в регистр 45 импульсом, поступающим на его второй вход с первого выхода распределителя 56 через элемент ЗА- ПРЕТ 49. Импульс с третьего выхода распределителя 56 увеличивает на единицу содержимое счетчика 15 адре

5 0 0

Q г

5

0

5

са, обеспечивающего считыванр.с из блока 16 памяти первого эталона первой частичной комбинации, который сравнивается в поразрядных элементах сравнения группы 41.1,...,41.т с содержимым счетчика 40 (в данном случае с числом 0), имитирующим слово выборочной комбинации. На выходе каждого из указанных элементов сравнения формируется логическая 1 при совпадении и логический О при не- совпаден11И содержимого сравниваемых разрядов слова выборочной комбинации и эталона частичной комбинации. Результаты сравнения поступают на первые входы поразрядных элементов группы И 42.1,.,.,42.т, на вторые входы которых поступает маска с выходов регистра 45. Маскированные результаты сравнения суммируются сумматором 43, формир1тощим на своих выходах код числа информационных позиций, на которых слово выборочной комбинации совпадает с эталоном частичной комбинации, Если это число больше числа О в регистре 46, то блок 44 сравнения, на входы которого подключены вькоды матора 43 и регистра 46, формирует сигнал логической 1., поступающий на информационный вход триггера 48. Этот сигнал записывается в триггер 48 в момент поступления на его тактовый вход через элемент И 51 импульса с первого выхода распределителя 56, Возникающий при этом положительный перепад напряжения на прямом выходе триггера 48 воздействует на тактовый вход регистра 46 -и записывает в него ; код числа, поступающего с выходов сумматора 43 на информационные входы регистра 46. Следующий затем импульс с второго выхода распредеителя 56 инвертируется элементом ЗАПРЕТ 50 и устанавливает Б О триггер 48.

Следующий затем импульс с третьет го выхода распределителя 56 снова увеличивает на единицу содержимое счетчика 15 адреса, обеспечивающего считывание из блока 16 памяти второго эталона первой частичкой комбинации, который аналогичным образом сравнивается с тем же словом выборочной комбинации. Если при этом окажется, что второй эталон более сходен со словом выборочной комбинации чем первьш эталон, то в регистр 46 записывается код числа информационных позиций, на которых слово выборочной комбинации совпадает с вторым эталоном первой частичной комбинации (запись в регистр 46 произво- Iдится с помощью импульса с первого - выхода распределителя 56 описан- ;ным образом). Если считываемый эта- |лон является последним в алфавите I первой частичной комбинации, то его признак записывается в регистр 47 о I в момент действия на его тактовом ;входе импульса с первого выхода рас- |пределитепя 56 и открывает элементы |И 52, И-НЕ 54. Следующий затем им- |пуЛьс с второго выхода распредели- 15 .|теля 56 проходит через элемент И 52 и выход 39 на вход записи блока 6 I памяти и записывает в него содержи- |мое регистра 46, выходы которого через выходы 38 подключены к входам 20 Iданных блока 6 памяти. Запись произ- I водится по адресу, который поступа- Iет через коммутатор 5 с его вторых входов на адресные входы блока 6 памяти. Этот адрес задается кодом ело- 25 ва выборочной комбинации и кодом но- мера выборочной комбинации, посту- . пающими с выходов счетчика 40 и счетчика 9 адреса соответственно на

мент И-НЕ 55 на суммирующий вход счетчика 40 и увеличивает его содержимое на единицу, проходит через выход 34, элемент И 18 на вход установки О счетчиков 9 и 15 адреса и сбрасывает их в состояние О. Далее аналогичньм образом производятся сравнение алфавитов составной комбинации с. очередным словом выборочной комбинации (в данном случае е кодом .числа 1) и запись корреляционных кодов в соответствующие ячейки блока 6 памяти. Программирование таблиц корреляционных кодов производится для всех т-разрядных двоичных наборов (слов выборочной комбинации), т.е. до переполнения счетчика 40, признаком чего является переход его старшего разряда из логической 1 в логический О. Этот сигнал с вьшода старшего разряда счетчика 40 проходит через элемент НЕ 20 на тактовый вход триггера 21 и записыва.ет в него сигнал логического О с собственного информационного входа. Сигнал логического О с прямого выхода триггера

21 переводит устройство в рабочий режим, блокируя распределитель 56 по мпадшие и старшие разряды вторых вхо-30 его установочному входу, останавливая дов коммутатора 5,.и равен нулю для тем самым работу программатора 17.

35

40

первой частичной комбинации. Следующий затем и тульс с третьего выхода распределителя 56 инвертируется элементом И-НЕ 54, проходит через элемент И 53 на вход устано вки О регистра 46 и сбрасывает его в О, проходит через выход 36 на суммирующий вход счетчика 9 адреса и увеличивает его содержимое на единицу.

Аналогичным образом производятся сравнение того же слова выборочной комбинации с алфавитом второй частичной комбинации и запись во вторую таблицу корреляционных кодов числа информационных позиций, на которых это слово совпадает с наиболее близким к нему эталоном из алфавита второй частичной к эмбинации.

После сравнения данного слова выборочной комбинации с алфавитом последней частичной комбинации признак окончания алфавитов составной комбинации записывается в регистр 47 в момент действия на его тактовом вхо- , де импульса с первого выхода распределителя 56 и открывает элемент И-НЕ 55. Импульс с третьего выхода распределителя 56 проходит через эле45

50

Сигнал логической 1 с инверсного выхода триггера 21 открывает элемент И 19 для ечитьшания на выход 31 решений об обнаружении составной комбинации.

Формула изобретения

5

0

5

0

Сигнал логической 1 с инверсного выхода триггера 21 открывает элемент И 19 для ечитьшания на выход 31 решений об обнаружении составной комбинации.

Формула изобретения

0 и первым входом первого элемента И-НЕ, второй выход третьего регистра подключен к первому входу второго элемента И-НЕ, выходы первого элемента И- НЕ и первого элемента ЗАПРЕТ со5 единены соответственно с вторыми входами второго элемента И и триггера, третий вход которого подключен к выходу блока сравнения, выход второго элемента И соединен с первым входом

0 второго регистра и является первым выходом программатора,выходы элементов сравнения группы подключены к первым входам соответствующих элементов И группы, вторые входы которых

5 соединены с соответствующими выходами первого регистра, выходы элементов И группы подключены к соответствующим входам сумматора, выходы которого соединены с соответствующ ми первыми

0 входами блока сравнения и вторыми

входами второго регистра, третий вход которого подключен к выходу триггера, выходы второго регистра соединены с соответствующими вторыми входа5 ми блока сравнения и являются вторыми выходами программатора, выход третьего элемента И является третьим выходом программатора, выходы счетчика соединены с соотзетствутощими вторыми входами элементов сравнения группы и являются четвертыми выходами программатора, выход второго элемента И-НЕ подключен к второму входу счетчика и является пятым выходом программатора, третий выход распределителя подключен к вторым входам пер- вого и второго элементов К-НЕ и является шестым выходом программатора.

0

5

ННф,

1 О 1 1 1

I

9UZ.2

.s(f(r)o

1 I

01 01 о 00

r-i

ч тн I

Тактовый интерВад

I I I I I I I

Фиг.З

а Ячейка

Разряды г 1

tt(

ТантоВый интервая

I I

i М I I I i i I I i I i

тактов ш инте/овал

Разряды

г 1

о

.

Фиг.5

I I M I I M I i {

Фиг. 6

| Устройство для приема и обнаружения комбинации двоичных сигналов | 1984 |

|

SU1156110A1 |

| Топка с несколькими решетками для твердого топлива | 1918 |

|

SU8A1 |

Авторы

Даты

1988-10-07—Публикация

1987-01-08—Подача