Изобретение относится к импульсной технике и может быть использовано в качестве базового логического элемента цифровых микросхем.

Цель изобретения - уменьшение потребляемой мощности и расширение функ циональных возможностей путем обеспечения расщепления выходных напряжений .

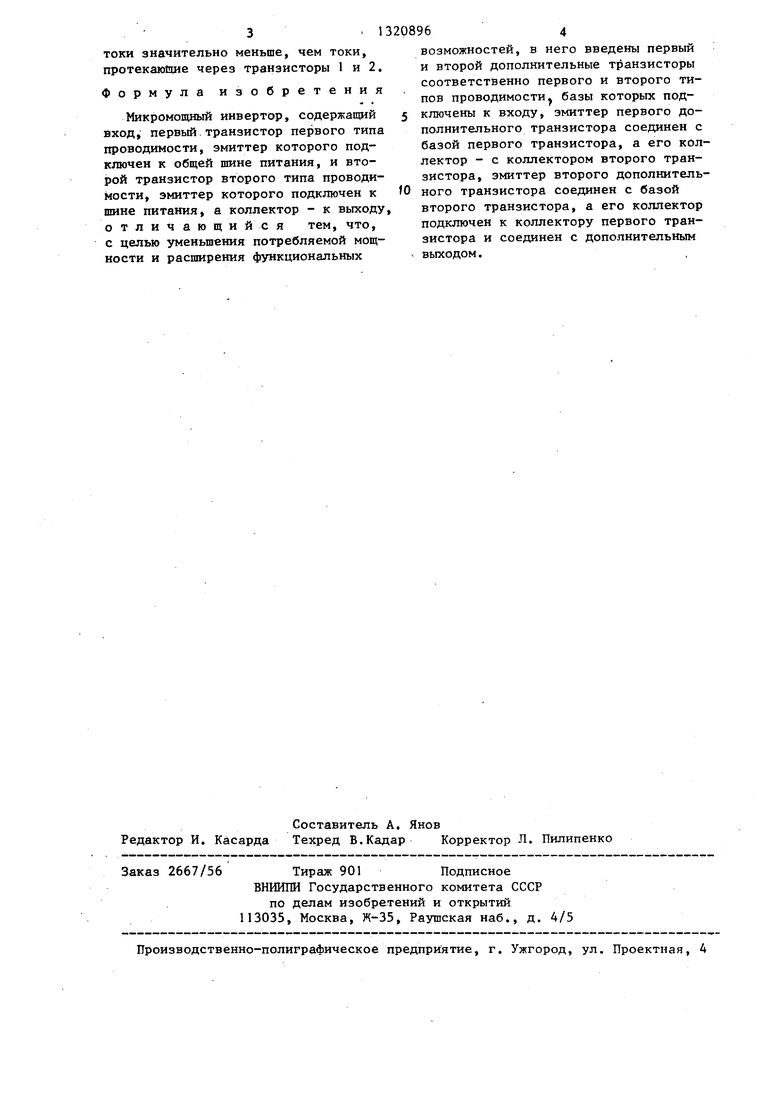

На чертеже представлена электрическая принципиальная схема микромощного инвертора.

Микромощный инвертор содержит первый транзистор 1 первого типа про- водимости, эмиттер которого соединен с общей шиной питания, второй транзистор 2 второго типа проводимости, эмиттер которого подключен к шине 3 питания, первый и второй дополнитель ные транзисторы А и 5 соответственно первого и второго типов проводимости, базы которых подключены к входу 6, Эмиттер первого дополнительног транзистора А соединен с базой перво

го транзистора 1, а коллектор - с коллектором второго транзистора 2 и подключен к выходу 7„ Эмиттер второго дополнительного транзистора 5 соединен с базой второго транзистора 2, а его коллектор - с коллектором первого транзистора 1 и подключен к дополнительному выходу 8.

Микромощный инвертор работает следующим образом.

В статическом режиме работы возможны два логические состояния инвертора зазксятще от величины входного уровня напряжений. При поступлении .уровня О на вход 6, транзис- торы 4 и 1 находятся в закрытом состоянии, а транзисторы 5 и 2 - в открытом. Тогда на выходе 7 устройства будет высокий уровень напряжения 1, Причем по этому выходу данное состояние обеспечивается током, протекающим через транзистор 2. На выходе 8 устройства - высокий уровень напряжения 1, несколько меньший

по величине, чем первый. Причем это состояние по этому выходу током не обеспечивается, так как через транзистор 5 протекает значительно меньший ток, чем через транзистор 2. При поступлении уровня 1 на вход 6, транзисторы А и 1 находятся в открытом состоянииJ а транзисторы 5 и 2 - в закрытом. Тогда на дополнительном выходе В устройства - низ

кий уровень напряжения О, обеспеченный протеканием тока через транзистор 1. На первом выходе 7 устройства - низкий уровень напряжения О, несколько больший (на величину напряжения эмиттер-база транзистора 1), чем предыдущий. Причем это состояние .по этому выходу током не обеспечивается, поскольку через тран- зистор А протекает ток значительно меньший, чем через транзистор 1.

Таким образом, предлагаемое устройство реализует функцию расщепления выходных напряжений, которые могут обеспечиваться токами или.нет. Так, например, к выходу 7 следует подключать базу транзистора с типом проводимости, совпадающим с типом проводимости транзисторов 1 и А, а к выходу В - базу транзистора с типом проводимости, совпадающим с типом проводимости транзисторов 5 и 2.

В режиме переключения с одного логического состояния в другое исключена ситуация прохождения сквозного тока через открытые транзисторы 1 и 2, что уменьшает потребление i энергии в режиме переключения.

Предлагаемый инвертор имеет малое потребление по входу, поскольку транзисторы А и 5 включены по схеме Дар- лингтона с транзисторами 1 и 2, т.е. по существу он управляется потенциально. К напряжению питания V.. предъявляетс51 требование, чтобы оно не превьш ало суммарную величину порогового напряжения V транзисторов 1, 2, А и 5

,,

+ V + + V,, 2 В,

когда эти транзисторы еще работают на экспоненциальном участке БАХ.

40 45

50

Предлагаемый инвертор предназначен для изготовления по планарной полупроводниковой технологии или тонкопленочной технологии. Топология изготовления транзисторов - гребенчатая. Геометрические размеры транзисторов 1 и 2 могут быть равны друг другу или отличаться при различных концентрациях легирующих примесей в 55 полупроводнике областей баз. В то же время геометрические размеры транзисторов А и 5 можно сделать в 5-10 раз меньше, чем размеры транзисторов 1 и 2, поскольку протекающие через них

3 13208964

токи значительно меньше, чем токи, возможностей, в него введены первый протекающие через транзисторы 1 и 2. и второй дополнительные транзисторы

соответственно первого и второго ти- Формулаизобретения.

. .пов проводимости базы которых под- Микромощный инвертор, содержащий 5ключены к входу, эмиттер первого до- вход, первый транзистор первого типаполнительного транзистора соединен с проводимости, эмиттер которого под-базой первого транзистора, а его кол- ключен к общей шине питания, и вто-лектор - с коллектором второго трак- рой транзистор второго типа проводи-зистора, эмиттер второго дополнительности, эмиттер которого подключен к Оного транзистора соединен с базой шине питания, а коллектор - к выходу,второго транзистора, а его коллектор отличающийся тем, что,подключен к коллектору первого тран- с целью уменьшения потребляемой мощ-зистора и соединен с дополнительным ности и расширения функциональных выходом.

| название | год | авторы | номер документа |

|---|---|---|---|

| Мультивибратор | 1986 |

|

SU1408523A1 |

| RS-триггер | 1986 |

|

SU1370732A1 |

| Автоколебательный мультивибратор | 1986 |

|

SU1319251A1 |

| Микромощный логический инвертор | 1986 |

|

SU1365352A1 |

| Элемент памяти | 1986 |

|

SU1388947A1 |

| Логический элемент | 1986 |

|

SU1413720A1 |

| МИКРОМОЩНЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ С ВЫСОКОЙ НАГРУЗОЧНОЙ СПОСОБНОСТЬЮ | 1999 |

|

RU2172064C2 |

| Интегральный транзисторно-транзисторный логический элемент | 1980 |

|

SU902261A1 |

| НИЗКОВОЛЬТНЫЙ БЫСТРОДЕЙСТВУЮЩИЙ БИПОЛЯРНЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ НА КОМПЛЕМЕНТАРНЫХ СТРУКТУРАХ | 1999 |

|

RU2173915C2 |

| Высоковольтный логический элемент | 1979 |

|

SU864571A1 |

Изобретение.относится к импульсной технике и может быть использовано в качестве базового логического элемента цифровых микросхем. Цель изобретения - уменьшение потребляемой мощности и расширение функциональных возможностей инвертора путем расщепления выходных напряжений. Устройство содержит транзисторы 1 и 2 первого и второго типов проводимости соответственно, шину 3 питания, дополнительные транзисторы 4 и 5 соответственно первого и второго типов проводимости, вход 6, выходы 7 и 8. Транзисторы 4 и 5 включены по схеме Дарлингтона с транзисторами 1 и 2. Инвертор может быть изготовлен по планарной полупроводниковой технологии или тонкопленочной технологии. Геометрические размеры транзисторов 4 и 5 могут быть в 5-10 раз меньше, чем размеры транзисторов 1 и 2, так как протекающие через них токи значительно меньше, чем токи, протекающие через транзисторы 1 и 2. 1 ил. S |СЛ 00 ю о ОО О5

| Валиев К | |||

| А | |||

| и др | |||

| Микромощные интегральные схемы | |||

| М,; Советское радио, 1975, с | |||

| Способ изготовления звездочек для французской бороны-катка | 1922 |

|

SU46A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Игумнов Д | |||

| В., Николаевский И | |||

| Ф | |||

| Транзисторы в микрорежиме | |||

| М,; Советское радио, 1978, с | |||

| Облицовка комнатных печей | 1918 |

|

SU100A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1987-06-30—Публикация

1986-01-10—Подача