сл

со сх 00 со

4

| название | год | авторы | номер документа |

|---|---|---|---|

| Микромощный инвертор | 1986 |

|

SU1320896A1 |

| Автоколебательный мультивибратор | 1986 |

|

SU1319251A1 |

| Мультивибратор | 1986 |

|

SU1408523A1 |

| Микромощный логический инвертор | 1986 |

|

SU1365352A1 |

| RS-триггер | 1986 |

|

SU1370732A1 |

| Оперативное запоминающее устройство | 1988 |

|

SU1573472A1 |

| Постоянное запоминающее устройство | 1978 |

|

SU752482A1 |

| Запоминающее устройство | 1976 |

|

SU597006A1 |

| НАКОПИТЕЛЬ ИНФОРМАЦИИ | 1991 |

|

RU2020614C1 |

| Запоминающее устройство | 1990 |

|

SU1751816A1 |

Изобретение относится к вычислительной технике и может быть использовано в оперативных запоминающих устройствах. Цель изобретения - снижение потребляемой мощности. Поставленная цель дчостига- ется тем, что в элемент памяти введен второй элемент выборки на ключевом I1 и усилительном 12 транзисторах с соответствующими связями. Введение второго элемента выборки обеспечивает исключение сквозного тока через элемент памяти в режиме записи, т. к. один из транзисторов 1 или 4 всегда закрыт. Кроме того, предложенный элемент работоспособен при напряжении питания менее 2 В, что тоже способствует снижению потребляемой мощности. 2 з. п. ф-лы, I ил.

g 6

Изобретение относится к цифровой схемотехнике и предназначено для приема, хранения и выдачи цифровой информации, записанной в двоичном коде.

Цель изобретения - уменьшение потребляемой мощности элемента памяти.

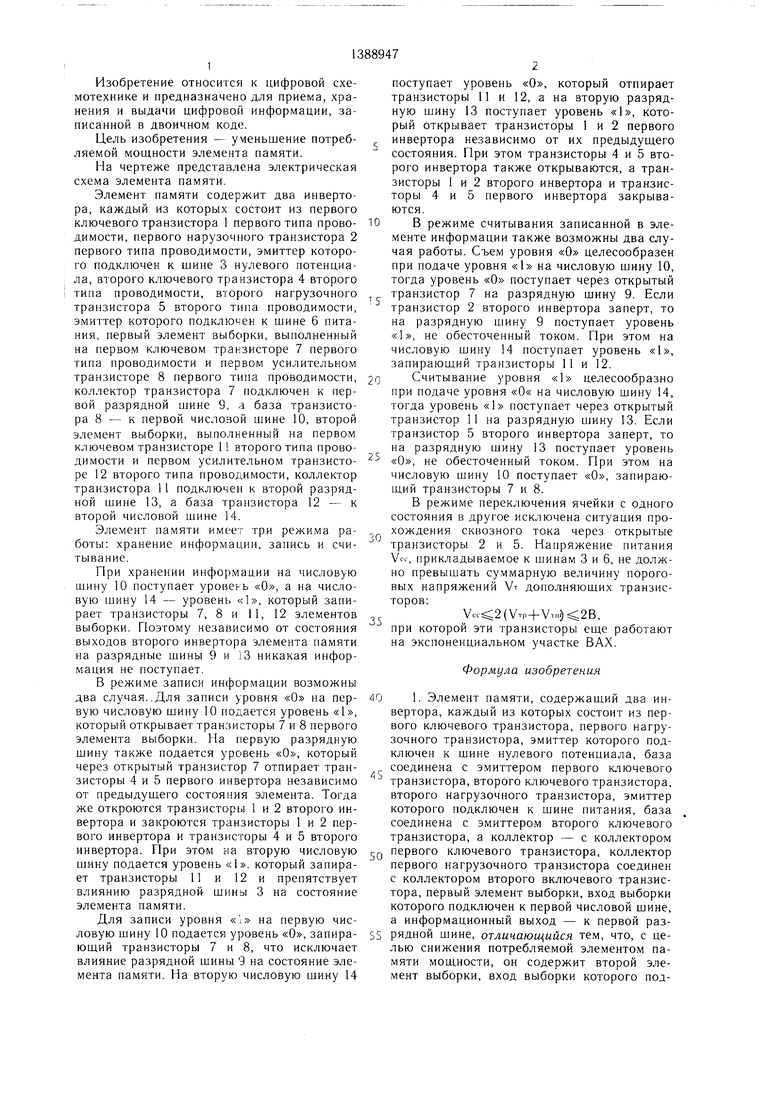

На чертеже представлена электрическая схема элемента памяти.

Элемент памяти содержит два инвертора, каждый из которых состоит из первого ключевого транзистора 1 первого типа проводимости, первого нарузочного транзистора 2 первого типа проводимости, эмиттер которого подключен к шине 3 нулевого потенциала, второго ключевого транзистора 4 второго типа проводимости, второго нагрузочного транзистора 5 второго типа проводимости, эмиттер которого подключен к шине 6 питания, первый элемент выборки, выполненный на первом ключевом транзисторе 7 первого типа проводимости и первом усилительном транзисторе 8 первого типа проводимости, коллектор транзистора 7 подключен к первой разрядной шине 9, а база транзистора 8 - к первой числовой шине 10, второй элемент выборки, выполненный на первом ключевом транзисторе 11 второго типа проводимости и первом усилительном транзисторе 12 второго типа проводимости, коллектор транзистора 11 подключен к второй разрядной шине 13, а база транзистора 12 - к второй числовой шине 14.

Элемент памяти имеет три режима работы: хранение информации, запись и считывание.

При хранении информации на числовую шину 10 поступает уровень «О, а на числовую шину 14 - уровень «1, который запирает транзисторы 7, 8 и 11, 12 элементов выборки. Поэтому независимо от состояния выходов второго инвертора элемента памяти на разрядные шины 9 и 13 никакая информация не поступает.

В режиме записи информации возможны два случая..Для записи уровня «О на первую числовую шину 10 подается уровень «1, который открывает транзисторы 7 и 8 первого элемента выборки. На первую разрядную шину также подается уровень «О, который через открытый транзистор 7 отпирает транзисторы 4 и 5 первого инвертора независимо от предыдушего состояния элемента. Тогда же откроются транзисторы 1 и 2 второго инвертора и закроются транзисторы 1 и 2 первого инвертора и транзисторы 4 и 5 второго инвертора. При этом на вторую числовую шину подается уровень «1. который запирает транзисторы И и 12 и препятствует влиянию разрядной шины 3 на состояние элемента памяти.

Для записи уровня «1 на первую числовую шину 10 подается уровень «О, запирающий транзисторы 7 и 8, что исключает влияние разрядной шины 9 на состояние элемента памяти. На вторую числовую щину 14

0

поступает уровень «О, который отпирает транзисторы 11 и 12, а на вторую разрядную шину 13 поступает уровень «1, который открывает транзисторы 1 и 2 первого инвертора независимо от их предыдущего состояния. При этом транзисторы 4 и 5 второго инвертора также открываются, а транзисторы 1 и 2 второго инвертора и транзисторы 4 и 5 первого инвертора закрываются.

В режиме считывания записанной в элементе информации также возможны два случая работы. Съем уровня «О целесообразен при подаче уровня «1 на числовую шину 10, тогда уровень «О поступает через открытый транзистор 7 на разрядную шину 9. Если транзистор 2 второго инвертора заперт, то на разрядную шину 9 поступает уровень «1, не обесточенный током. При этом на числовую щину 14 поступает уровень «1, запирающий транзисторы 11 и 12.

Считывание уровня «1 целесообразна при подаче уровня «0« на числовую шину 14, тогда уровень «1 поступает через открытый транзистор II на разрядную шину 13. Если транзистор 5 второго инвертора заперт, то на разрядную шину 13 поступает уровень «О, не обесточенный током. При этом на числовую шину 10 поступает «О, запирающий транзисторы 7 и 8.

В режиме переключения ячейки с одного состояния в другое исключена ситуация прохождения сквозного тока через открытые транзисторы 2 и 5. Напряжение питания Vcc, прикладываемое к шинам 3 и 6, не должно превышать суммарную величину пороговых напряжений VT дополняющих транзисторов:

(Утр + Утм;Х2В,

при которой эти транзисторы еще работают на экспоненциальном участке ВАХ.

Формула изобретения

S

первого ключевого транзистора, коллектор первого нагрузочного транзистора соединен с коллектором второго включевого транзистора, первый элемент выборки, вход выборки которого подключен к первой числовой шине, а информационный выход - к первой разрядной шине, отличающийся тем, что, с целью снижения потребляемой элементом памяти мощности, он содержит второй элемент выборки, вход выборки которого под

ключей к второй числовой шине, информационный выход - к второй разрядной шине, информационный вход соединен с коллектором второго нагрузочного транзистора второго инвертора, информационный вход первого элемента выборки соединен с коллектором первого нагрузочного транзистора второго инвертора, коллекторы и базы первых ключевых транзисторов первого и второго инверторов соединены перекрестными связями, коллекторы и базы вторых ключевых транзисторов первого и второго инверторов соединены перекрестными связями.

0

5

подключен к шине питания, оаза является входом выборки первого элемента выборки, а эмиттер соединен с базой первого ключевого транзистора, эмиттер которого является информационным входом, а коллектор - информационным выходом первого элемента выборки.

| Игумнов Д | |||

| В., Николаевский И | |||

| Ф | |||

| Транзисторы в микрорежиме | |||

| М.: Сов | |||

| радио, 1978, с | |||

| Облицовка комнатных печей | 1918 |

|

SU100A1 |

| Машина для изготовления проволочных гвоздей | 1922 |

|

SU39A1 |

| Преобразователь кода системы остаточных классов в позиционный код | 1986 |

|

SU1343553A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1988-04-15—Публикация

1986-08-18—Подача