Изобретение относится к импульсной технике, а именно к логи еским элементам на биполярных транзисторах

Цель изобретения - расширение функциональных возможностей логического элемента, а именно реализация функции ИЛИ-НЕ.

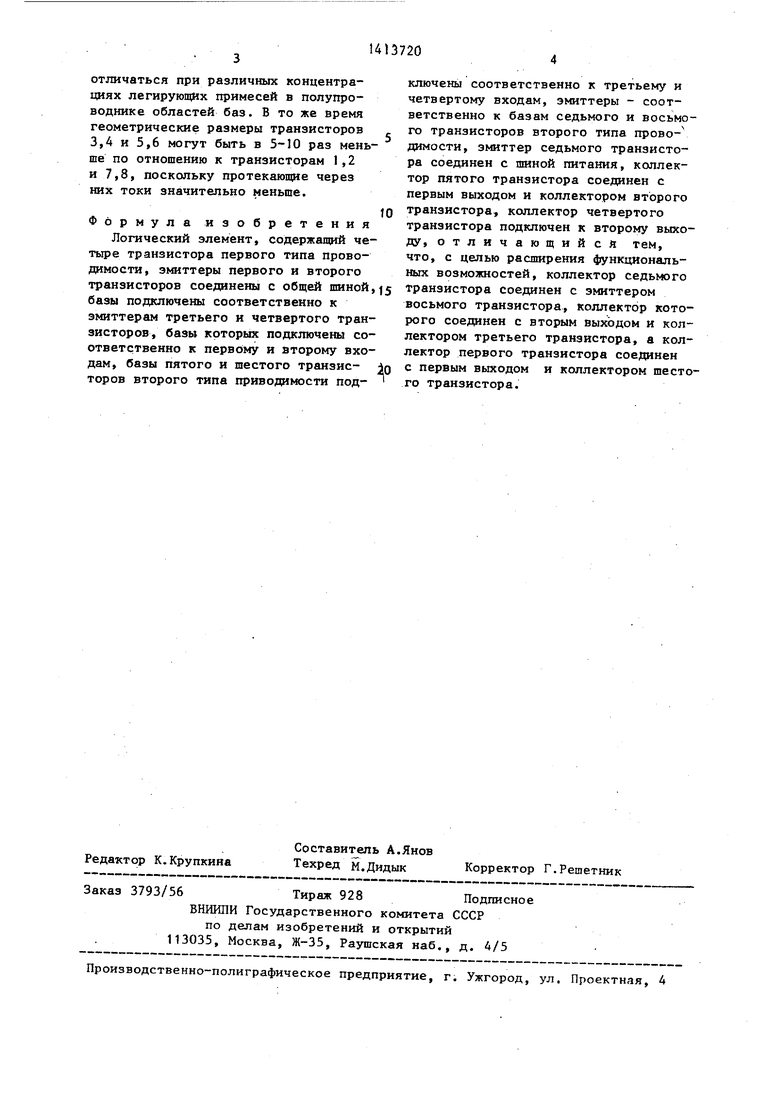

На чертеже представлена принципиальная схема логического элемента.

Логический элемент содержит первый, второй, третий и четвертый транзисторы 1-4 первого типа проводимости, пятьй, шестой, седьмой и восьмой транзисторы 5-8 второго типа про- Ьодимости, эмиттеры транзисторов 1 и 2 -соединены с общей шиной, базы соответственно с эмиттерами транзисторов J3 и 4, базы которых соединены соответственно с первым и вторым входами |9 и 10, коллекторы - с вторым выхо- |дом 11, коллекторы транзисторов 1 и соединены с первым выходом 12 и коллекторами транзисторов 5 и 6, базы которых соединены соответственно с третим и четвертым входами 13 и 14, эмиттеры - соответственно с базами транзисторов 7 и 8, эмиттер транзистора 7 соединен с шиной питания 15, коллектор - с эмиттером транзистора 8, коллектор которого соединен с выходом 11.

Логический элемент работает следу шдм образом.

Логический элемент имеет четыре состояния (режимы нормальной работы)

В первом состоянии на входы 9,10, 13 и 14 подается уровень напряжения О (при этом входы 9 и 10 могут быт не обеспечены входными токами, а вхо ды 13 и 14 должны быть обеспечены токами, хотя и малыми). Тогда транзис- ,торы 1-4 .будут находиться в запертом состоянии (на выходе 12 устройства будет уровень 1, не обеспеченный током), а транзисторы 5-8 - в открытом (на выходе 11 устройства будет уровень 1, обеспеченный током, поскольку ток коллекторов транзисторов 7 и 8 значительно больше тока коллекторов транзисторов 5 и 6).

Во втором состоянии на входы 10 и 13 подается уровень О, а на входы 9 и 14 - уровень 1. Тогда транзисторы 2,4 и 8,6 будут находиться в закрытом состоянии, а транзисторы 1,3 и 7,5 - в открытом. Открытый транзистор 1 обеспечивает уровень о на выходе 12 устройства (током

обеспечен), а на выходе 11 устройства будет потенциальное состояние О, поскольку ток транзистора 3 значительно меньше, чем у транзистора 1.

В третьем состоянии на входы 10 и 13 подается уровень 1, а на входы 9 и 14 - уровень О. Тогда транзисторы 254 и 8,6 будут открыты, а транзисторы 1,3 и 7,5 - закрыты. Открытый транзистор 2 обеспечивает уровень О на выходе 12 (обеспеченный током), а открытьй транзистор 4 обес- пе тавает уровень О на выходе 11 (потенциальный).

В четвертом состоянии на все входы 9,10,13 и 14 подается высокий уровень 1. Тогда транзисторы 1-4 будут открыты, а транзисторы 5-8 - зак0

0

5

о 5

рыты. Очевидно, что на выходе 12 устройства будет уровень О (обеспеченный током), на выходе 11 - уровень О (не обеспеченный током).

Таким образом, логический элемент 5 выполняет функцию 2ИЛИ-НЕ. Очевидно, что количество логических входов может быть увеличено за счет увеличения количества параллельно-последовательно включенных транзисторов. В ре;киме переключения устройства с одного логического состояния на выходе в другое исключена ситуация прохождения сквозного тока через открытые транзисторы 1,2 и 7,8, что уменьшает потребление энергии в режиме переключения.

К напряжению питания прикла- дашаемого к шине 15, предьявляется одно требование, чтобы оно не превышало суммарную величину пороговых напряжений Ur транзисторов противоположного типа проводимости:

( итр),2В,

при котором эти транзисторы еще работают на экспоненциальном участке ВАХ.

Очевидно, что входы 9,13 и 10,14 могут быть попарно объединены, если управляющие напряжения О и 1 обеспечень: токами в обоих состояниях (симметричньй вход).

Данный логический элемент предназначен для изготовления по планарной (тонкопленочной) полупроводниковой технологии. Топология изготовления транзисторов - гребенчатая. Геометрические размеры транзисторов 1,2 и 7,8 могут .быть равны друг другу или

50

55

отличаться при различных концентрациях легирующих примесей в полупроводнике областей баз. В то же время геометрические размеры транзисторов 3,4 и 5,6 могут быть в 5-10 раз меньше по отношению к транзисторам I,2 и 7,8, поскольку протекающие через них токи значительно меньше.

Формула изобретения Логический элемент, содержащий четыре транзистора первого типа проводимости, эмиттеры первого и второго транзисторов соединены с общей шиной базы подключены соответственно к эмиттерам третьего и четвертого тран зисторов, базы которых подключены со ответственно к первому и второму вхо дам, базы пятого и шестого транзисторов второго типа приводимости под10

15

ключены соответственно к третьему и четвертому входам, эмиттеры - соответственно к базам седьмого и восьмого транзисторов второго типа прово- димости, эмиттер седьмого транзистора соединен с шиной питания, коллектор пятого транзистора соединен с первым выходом и коллектором второго транзистора, коллектор четвертого транзистора подключен к второму выходу, отличающийся тем, что, с целью расширения функциональных возможностей, коллектор седьмого транзистора соединен с эмиттером восьмого транзистора, коллектор которого соединен с вторым выходом и коллектором третьего транзистора, а коллектор первого транзистора соединен с первым выходом и коллектором шестого транзистора.

| название | год | авторы | номер документа |

|---|---|---|---|

| Микромощный логический инвертор | 1986 |

|

SU1365352A1 |

| Источник вторичного электропитания для сети постоянного напряжения | 1990 |

|

SU1786476A1 |

| Транзисторный инвертор | 1991 |

|

SU1815775A1 |

| Импульсный понижающий стабилизатор постоянного напряжения | 1990 |

|

SU1786477A1 |

| Высоковольтный логический элемент | 1984 |

|

SU1176449A1 |

| Устройство задержки | 1989 |

|

SU1793535A1 |

| Формирователь одиночных импульсов | 1986 |

|

SU1358077A1 |

| ТРИГГЕРНЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ 2И-ИЛИ/2И-ИЛИ-НЕ | 2024 |

|

RU2829649C1 |

| Транзисторный инвертор | 1988 |

|

SU1818673A1 |

| Дешифратор | 1986 |

|

SU1336251A1 |

Изобретение относится к импульсной технике и может быть использовано при построении логических элементов на биполярных транзисторах. Цепь изобретения - расширение функциональных возможностей, достигается за счет возможности реализации функции ИЛИ-НЕ. Логический элемент собран на транзисторах 1-4 первого типа проводимости и транзисторах 5-8 второго типа проводимости и может выполнять логическую функцию 2ИЛИ-НЕ. При этом количество выходов может быть увеличено за счет увеличения количества параллельно-последовательно включенных транзисторов. Предложенный логический злемент предназначен для изготовления по Планерной (тонкоштеноч- ной) полупроводниковой технологии. Топология изготовления транзисторов - гребенчатая. 1 ил. 15 с ю о // 00 Ч tc о 12

| Микромощный инвертор | 1986 |

|

SU1320896A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Микромощный логический инвертор | 1986 |

|

SU1365352A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1988-07-30—Публикация

1986-08-18—Подача